# T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

# 論文 / 著書情報 Article / Book Information

| Title             | S-parameter-based modal decomposition of multiconductor transmission lines and its application to de-embedding                                                                                                                                                                                                                                    |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Author            | S. Amakawa, K. Yamanaga, H. Ito, T. Sato, N. Ishihara, K. Masu                                                                                                                                                                                                                                                                                    |  |  |  |

| Journal/Book name | International Conference on Microelectronic Test Structures (ICMTS), , , pp. 177-180                                                                                                                                                                                                                                                              |  |  |  |

| 発行日 / Issue date  | 2009, 4                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 権利情報 / Copyright  | (c)2009 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. |  |  |  |

# **ICMTS 2009**

Proceedings of the

# 2009 IEEE INTERNATIONAL CONFERENCE ON MICROELECTRONIC TEST STRUCTURES

March 30-April 2, 2009 Embassy Suites Mandalay Beach Resort Oxnard, CA

Sponsored by the IEEE Electron Devices Society

# **TABLE OF CONTENTS**

# **SESSION 1: Device Characterization**

Co-chairs: Michael Cresswell, NIST and Colin McAndrew, Freescale Semiconductor

| 1.1 | Using High Precision On-Wafer Backend Capacitor Mismatch<br>Measurements using a Benchtop Semiconductor Characterization<br>System, H. Tuinhout and F. van Rossem*, NXP-TSMC Research<br>Center, Eindhoven, The Netherlands and *University of Twente,<br>Enschede, The Netherlands | 3  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Static Noise Margin Evaluation Method Based on Direct<br>Polynomial-Curve-Fitting with Universal SRAM Cell Inverter TEG<br>Measurement, K. Nakamura, K. Noda and H. Koike*, Kyushu Institute<br>of Technology, and *Fukuoka Industry, Science & Technology<br>Foundation, Japan     | 9  |

| 1.3 | Addressable Arrays Implemented with One Metal Level for MOSFET and Resistor Variability Characterization, M.B. Ketchen, M. Bhushan* and G. Costrini*, IBM Research, T.J. Watson Research Center, Yorktown Heights, NY and *IBM Systems & Technology Group, Hopewell Junction, NY    | 13 |

| 1.4 | Accurate Time Constant of Random Telegraph Signal Extracted by a Sufficient Long Time Measurement in Very Large-Scale Array TEG, T. Fujisawa, K. Abe, S. Watabe, N. Miyamoto, A. Teramoto, S. Sugawa, and T. Ohmi, Tohoku University, Japan                                         | 19 |

|     | SESSION 2: MEMS/Sensors Co-chairs: Yoshio Mita, University of Tokyo and Anthony Walton, University of Edinburgh                                                                                                                                                                     |    |

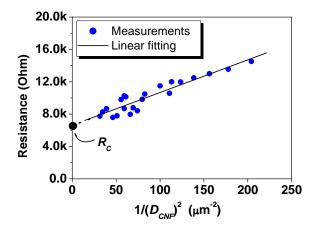

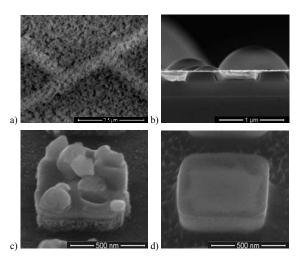

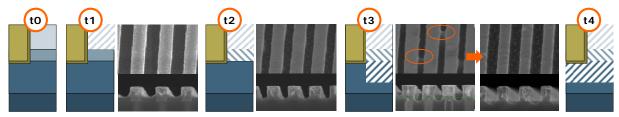

| 2.1 | Extracting Resistances of Carbon Nanostructures in Vias, W. Wu, S. Krishnan, K. Li, X. Sun, R. Wu and C.Y. Yang, Santa Clara University, Santa Clara, CA                                                                                                                            | 27 |

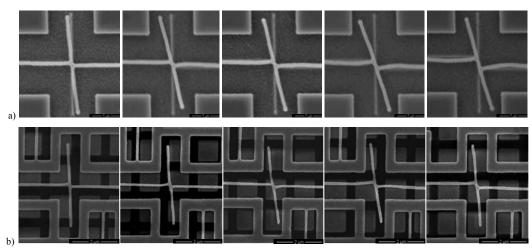

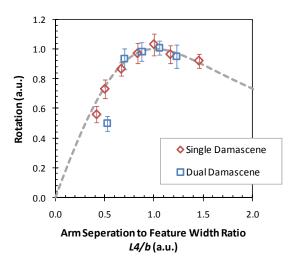

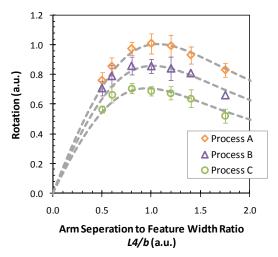

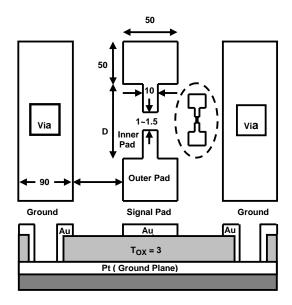

| 2.2 | Demonstration of a Submicron Damascene Cu/Low-k Mechanical Sensor to Monitor Stress in BEOL Metallisation, C.J. Wilson, K. Croes*, Z. Tokei*, G.P. Beyer*, A.B. Horsfall, and A.G. O'Neill, Newcastle University, Newcastle, United Kingdom and *IMEC, Leuven, Belgium              | 31 |

| 2.3 | Test Structure to Extract Circuit Models of Nanostructures Operating at High Frequencies, F.R. Madriz, S. Krishnan, X. Sun, and C.Y. Yang, Santa Clara University, Santa Clara, CA                                                                                                  | 36 |

| 2.4 | Test Chip to Evaluate Measurement Methods for Small Capacitances, J.J. Kopanski, M. Yaqub Afridi, C. Jiang, and C.A. Richter, National Institute of Standards and Technology, Gaithersburg, MD                                                                                      | 39 |

SESSION 3: Matching

Co-chairs: Hans Tuinhout, NXP

and Mark Poulter, National Semiconductor Corp.

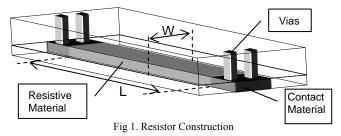

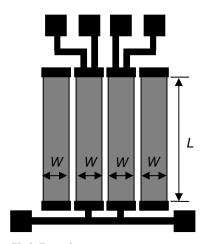

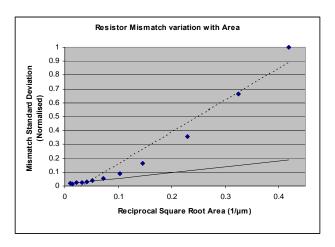

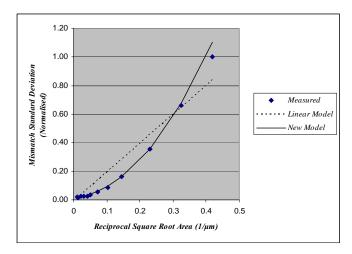

| 3.1 | <b>An Enhanced Model for Thin Film Resistor Matching,</b> T.G. O'Dwyer and M.P. Kennedy*, Analog Devices B.V., Limerick, Ireland and *University College, Cork, Ireland                                                                                                                                                                                                                                  | 45 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Application of Matching Structures to Identify the Source of Systematic Dimensional Offsets in GHOST Proximity Corrected Photomasks, S. Smith, A. Tsiamis, M. McCallum*, A.C. Hourd**, J.T.M. Stevenson, and A.J. Walton, The University of Edinburgh, Edinburgh, United Kingdom, *Nikon Precision Europe, Livingston, United Kingdom and **Compugraphics International Ltd., Glenrothes, United Kingdom | 50 |

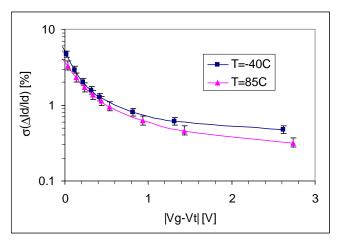

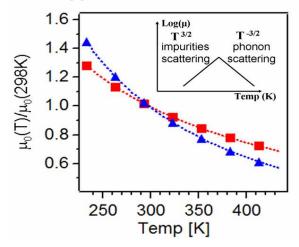

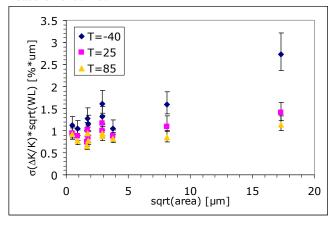

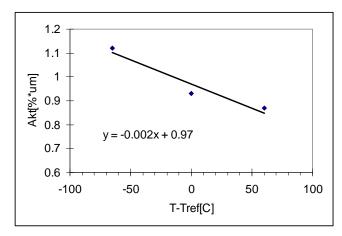

| 3.3 | An Analysis of Temperature Impact on MOPSFET Mismatch, S. Mennillo, A. Spessot, L. Vendrame, and L. Bortesi, Numonyx, Agrate Brianza, Italy                                                                                                                                                                                                                                                              | 56 |

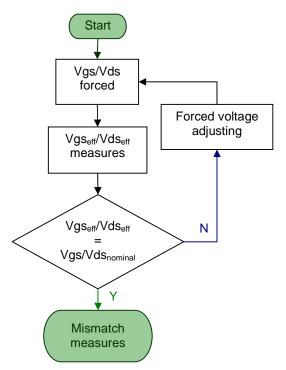

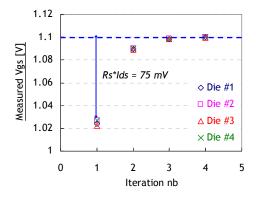

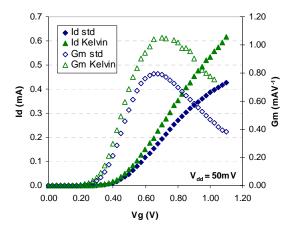

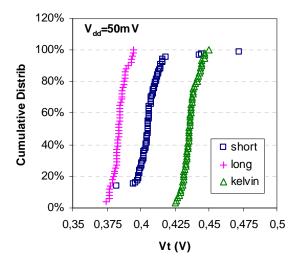

| 3.4 | MOSFET Mismatch Measure Improvement Using Kelvin Test Structures, C.M. Mezzomo, M. Marin and G. Ghibaudo*, STMicroelectronics, Crolles, France and *IMEP-LAHC, Grenoble, France                                                                                                                                                                                                                          | 62 |

|     | SESSION 4: Poster Presentations 2:50 p.m 3:30 p.m. Co-chairs: Willie Sansen, KU Leuven and Richard Allen, NIST                                                                                                                                                                                                                                                                                           |    |

| 4.1 | Withdrawn                                                                                                                                                                                                                                                                                                                                                                                                |    |

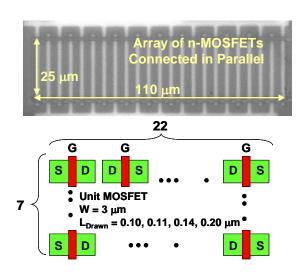

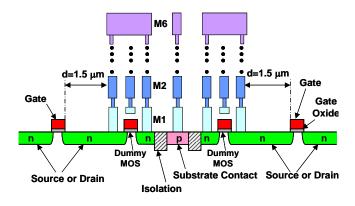

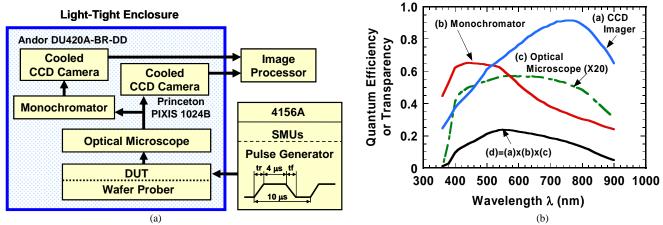

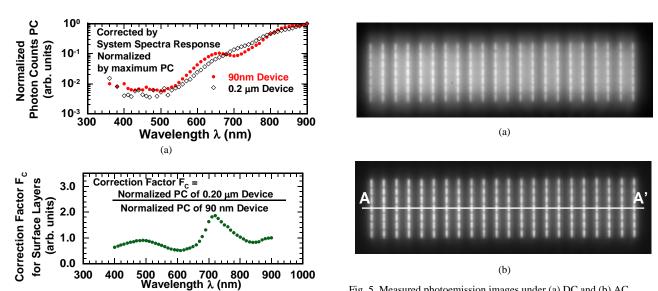

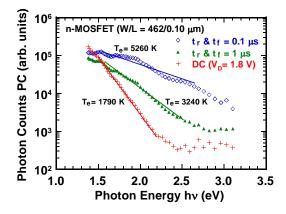

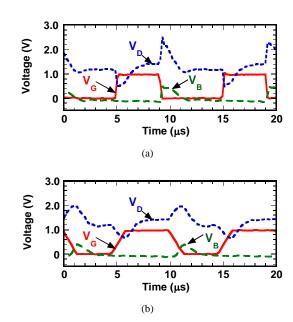

| 4.2 | A Test Structure for Spectrum Analysis of Hot-Carrier-Induced Photoemission from Scaled MOSFETs under DC and AC Operations, T. Matsuda, T. Maezawa, H. Iwata, and T. Ohzone*, Toyama Prefectural University and *Dawn Enterprise, Japan                                                                                                                                                                  | 71 |

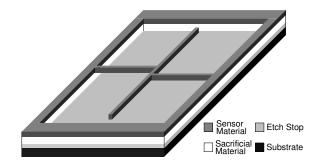

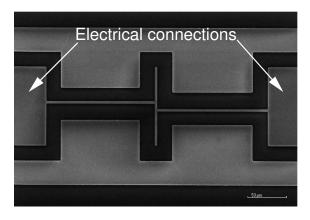

| 4.3 | Application of a Micromechanical Test Structure to the Measurement of Stress in an Electroplated Permalloy Film, S. Smith, N. Brockie, J.G. Terry, A.B. Horsfall*, G. Pringle**, A. O'Hara**, and A.J. Watson, The University of Edinburgh, Edinburgh, United Kingdom, *Newcastle University, Newcastle, United Kingdom and **Memsstar Technology, Livingston, United Kingdom                            | 75 |

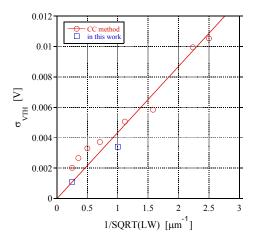

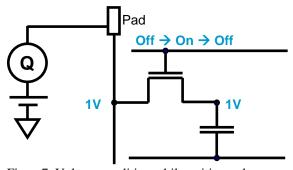

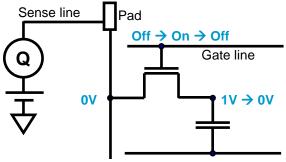

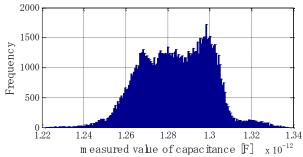

| 4.4 | Measurement of MOSFET C-V Curve Variation using CBCM Method, K. Tsuji, K. Terada, T. Tsunomura*, and A. Nishida*, Hiroshima City University, Hiroshima, Japan and *MIRAI-Selete, Tsukuba, Japan                                                                                                                                                                                                          | 81 |

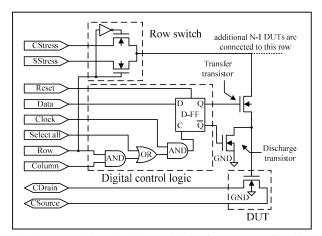

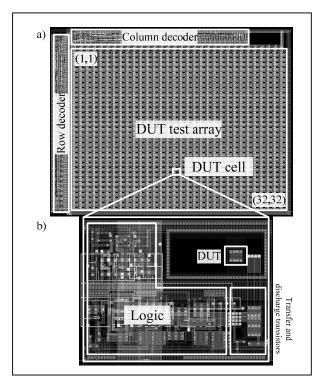

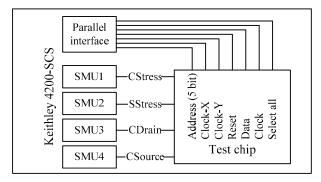

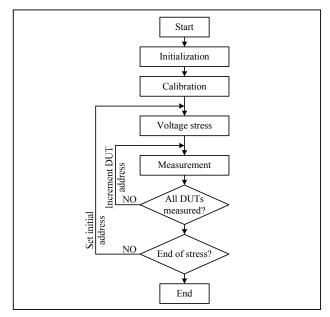

| 4.5 | Array Test Structure for Ultra-Thin Gate Oxide Degradation Issues, K.M. Hafkemeyer, A. Domdey, D. Schroeder and W.H. Krautschneider, Hamburg University of Technology, Hamburg, Germany                                                                                                                                                                                                                  | 85 |

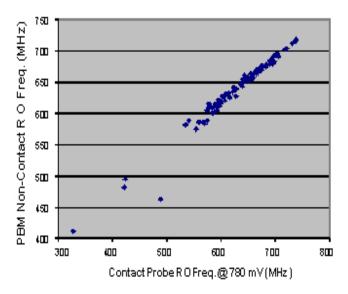

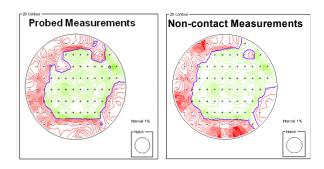

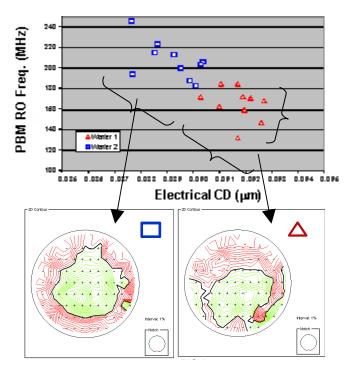

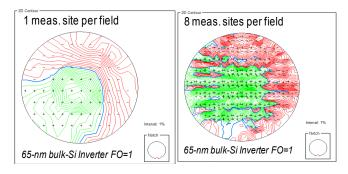

| 4.6 | Non-Contact, Pad-less Measurement Technology and Test<br>Structures for Characterization of Cross-Wafer and In-Die Product<br>Variability, G. Steinbrueck, J.S. Vickers, M. Babazadeh, M. Pelella,<br>and N. Pakdaman, tau-Metryx, Inc., Santa Clara, USA          | 91  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.7 | Test Structure for High-Voltage LD-MOSFET Mismatch<br>Characterization in 0.35 um HV-CMOS Technology, W. Posch, M.<br>Christian and E. Seebacher, austriamicrosystems AG,<br>Unterpremstatten, Austria                                                             | 96  |

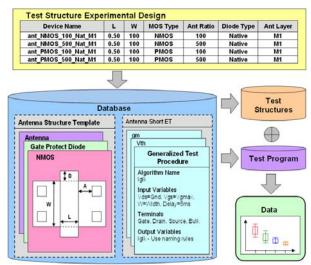

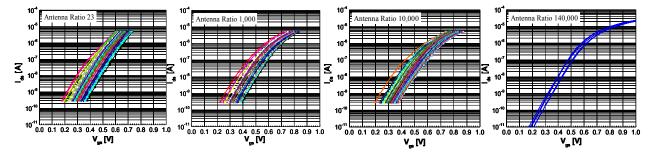

| 4.8 | Automated Test Structure Generation for Characterizing Plasma-<br>Induced Damage in MOSFET Devices, T. Zwingman, A.J. West and<br>A. Gabrys, National Semiconductor Corp., Santa Clara, CA                                                                         | 102 |

|     | SESSION 5: Process Characterization I Co-chairs: Christopher Hess, PDF Solutions and Kelvin Doong, TSMC                                                                                                                                                            |     |

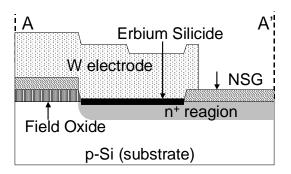

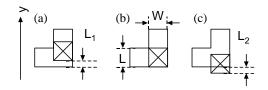

| 5.1 | Advanced Method for Measuring Ultra-Low Contact Resistivity between Silicide and Silicon based on Cross-Bridge Kelvin Resistor, T. Isogai, H. Tanaka, A. Teramoto, T. Goto, S. Sugawa, and T. Ohmi, Tohoku University, Sendai, Japan                               | 109 |

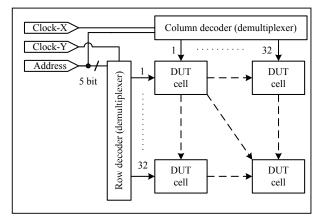

| 5.2 | A Test Structure for Statistical Evaluation of Characteristics<br>Variability in a Very Large Number of MOSFETs, S. Watabe, S.<br>Sugawa, K. Abe, T. Fujisawa, N. Miyamoto, A. Teramoto, and T. Ohmi,<br>Tohoku University, Sendai, Japan                          | 114 |

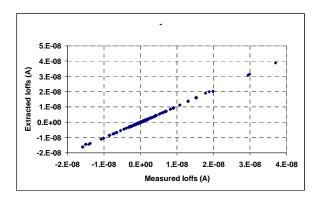

| 5.3 | Estimating MOSFET Leakage from Low-cost, Low-resolution Fast Parametric Test, T. Uezono, R. Lindley, A. Swimmer, S. Winters, R. Vallishayee, S. Saxena, PDF Solutions, Richardson, TX                                                                              | 119 |

| 5.4 | Test Structures Utilizing High-Precision Fast Testing for 32nm Yield Enhancement, M. Karthikeyan, L. Medina and E. Shiling, IBM Systems and Technology Group, Hopewell Junction, NY                                                                                | 124 |

|     | SESSION 6: Parameter Extraction Co-chairs: Larg Weiland, PDF Solutions and Hi-Deok Lee, Chungham National University                                                                                                                                               |     |

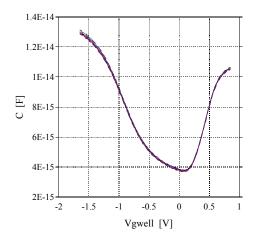

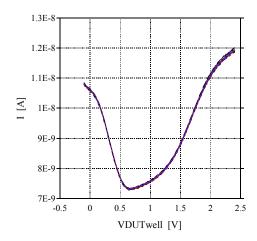

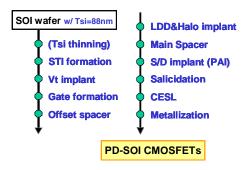

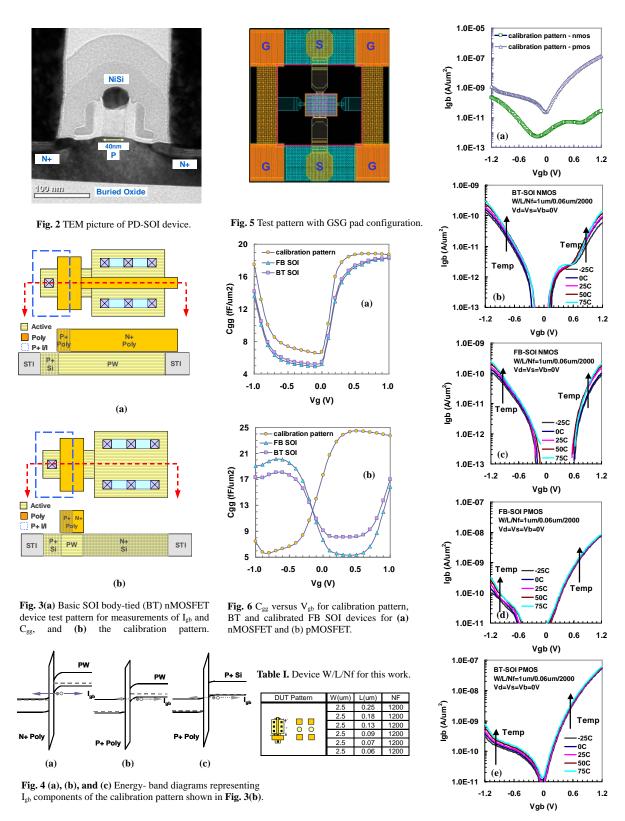

| 6.1 | Efficient Characterization Methodology of Gate-Bulk Leakage and Capacitance for Ultra-Thin Oxide Partially-Depleted (PD) SOI Floating Body CMOS, D. Chen, R. Lee, U.C. Liu, G.S. Lin, M.C. Tang, C.S. Yeh, and S.C. Chien, United Microelectronics Corp., Hsinchu, | 133 |

| 6.2 | Taiwan, Parameter Extraction for the PSP MOSFET Model by the Combination of Genetic and Levenberg-Marquardt Algorithms, Q. Zhou, W. Yao, W. Wu, X. Li, Z. Zhu, and G. Gildenblat, Arizona State University, Tempe, AZ                                              | 137 |

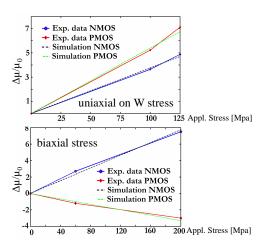

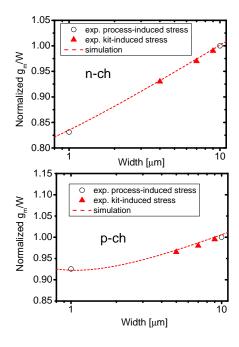

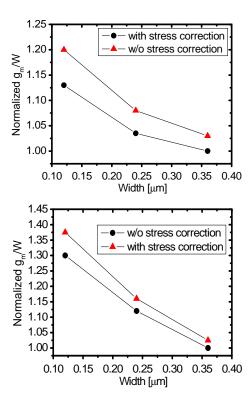

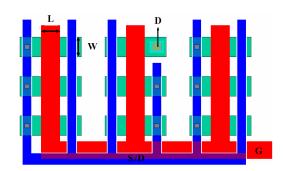

| 6.3 | Characterization and Modeling of Mechanical Stress in Silicon-                                                                                                                                                                                                                                                                                                                                                      | 143 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | based Devices, A. Spessot, A. Colombi, G.P. Carnevale, and P. Fantini, Numonyx, Agrate Brianza, Italy                                                                                                                                                                                                                                                                                                               |     |

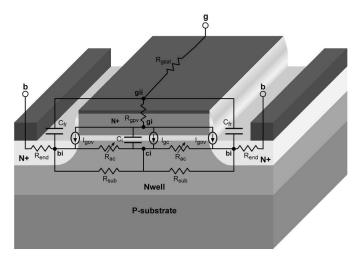

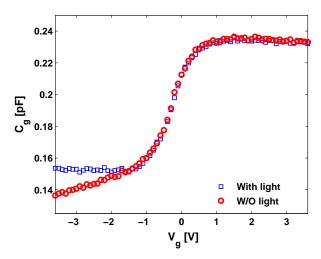

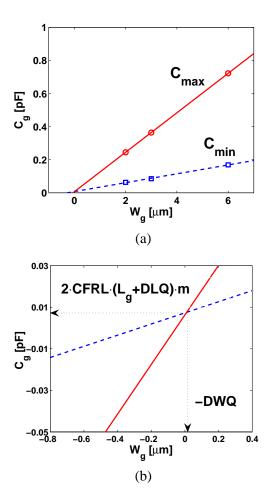

| 6.4 | Improved Parameter Extraction Procedure for PSP-Based MOS Varactor Model, Z. Zhu, J. Victory*, S. Chaudhry**, L. Dong**, Z. Yan**, J. Zheng**, W. Wu, X. Li, Q. Zhou, P. Kolev^, C. McAndrew^^, and G. Gildenblat, Arizona State University, Tempe, AZ, *Sentinel IC Technologies, Irvine, CA, **Jazz Semiconductor, Newport Beach, CA, ^formerly with RFMD, San Diego, CA and ^^Freescale Semiconductor, Tempe, AZ | 148 |

|     | SESSION 7: CD Metrology Co-chairs: Loren Linholm                                                                                                                                                                                                                                                                                                                                                                    |     |

|     | and Dieter Schroder, Arizona State University                                                                                                                                                                                                                                                                                                                                                                       |     |

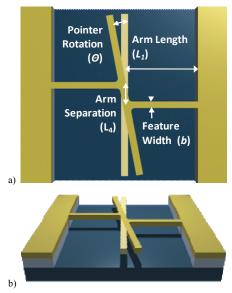

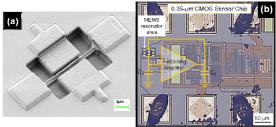

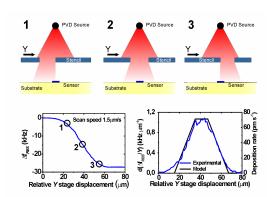

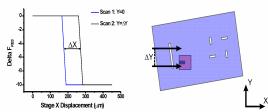

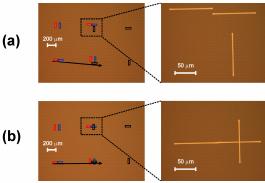

| 7.1 | Nanomechanical Test Structure for Optimal Alignment in Stencil-Based Lithography, M. Sansa, J. Arcamone, J. Verd*, A. Uranga*, G. Abadal*, E. Lora-Tamayo, N. Barniol*, M.A.F. van den Boogaart**, J. Brugger**, and F. Perez-Murano, Institute de Microelectronica de Barcelona CNM-IMB, Barcelona, Spain, *ETSE-UAB, Barcelona, Spain and **EPFL, Lausanne, Switzerland                                           | 157 |

| 7.2 | Electrical Test Structures for Investigating the Effects of Optical Proximity Correction, A. Tsiamis, S. Smith, M. McCallum*, A.C. Hourd**, J.T.M. Stevenson, and A.J. Walton, The University of Edinburgh, Edinburgh, United Kingdom, *Nikon Precision Europe, Livingston, United Kingdom and **Compugraphics International Ltd., Glenrothes, United Kingdom                                                       | 162 |

| 7.3 | Mapping the Edge-Roughness of Test Structure Features for Nanometer-Level CD Reference-Materials, M.W. Cresswell, M. Davidson*, G.I. Mijares, R.A. Allen, J. Geist, and M. Bishop**, National Institute of Standards and Technology, Gaithersburg, MD, *Spectel Research Corp., Palo Alto, CA and **International SEMATECH, Austin, TX                                                                              | 168 |

|     | SESSION 8: RF Co-chairs: Franz Sischka, Agilent Technologies and Kevin McCarthy, University College, Cork                                                                                                                                                                                                                                                                                                           |     |

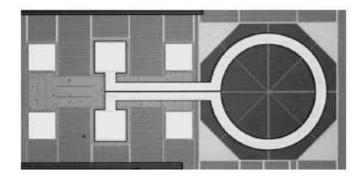

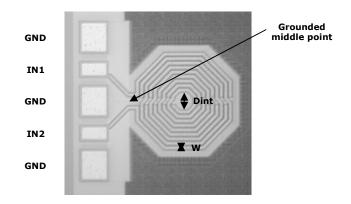

| 8.1 | S-Parameter-based Modal Decomposition of Multiconductor<br>Transmission Lines and its Application to De-Embedding, S.<br>Amakawa, K. Yamanaga, H. Itoh, T. Sato, N. Ishihara, and K. Masu,<br>Tokyo Institute of Technology, Yokohama, Japan                                                                                                                                                                        | 177 |

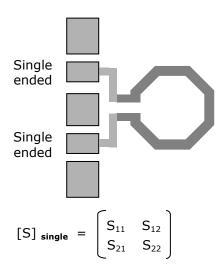

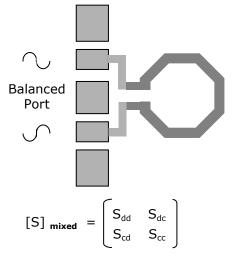

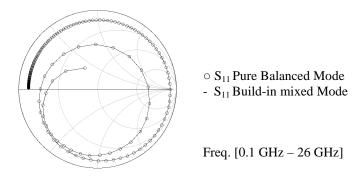

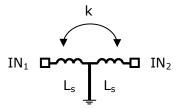

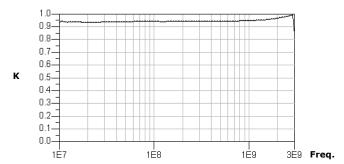

| 8.2 | Characterization and Model Parameter Extraction of Symmetrical Centre Tapped Inductor using Build in Mixed Mode and Pure Differential S-Parameters, F. Gianesello, Y. Morandini, S. Boret, and D. Gloria, STMicroelectronics, Crolles, France                                                                                                                                                                       | 181 |

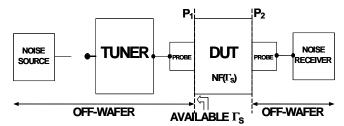

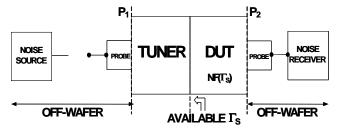

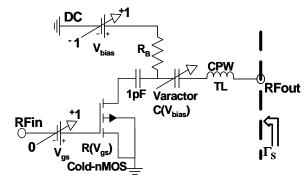

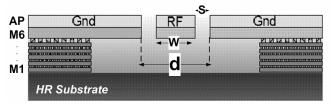

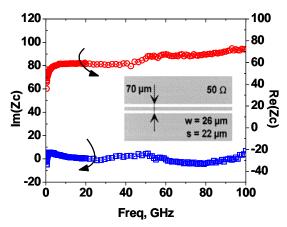

| 8.3  | In-Situ Silicon Integrated Tuner for Automated on-Wafer MMW Noise Parameters Extraction of Si HBT and MOSFET in the Range of 60 - 110GHz, Y. Tagro, D. Gloria, S. Boret, Y. Monandini, and G. Dambrine*, STMicroelectronics, Crolles, France, and *IEMN, Villeneuve d'ascq, France | 184 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | SESSION 9: Process Characterization II Co-chairs: Brad Smith, Freescale Semiconductor and Hugues Brut, STMicroelectronics                                                                                                                                                          |     |

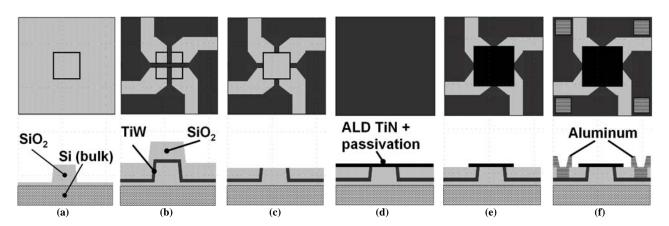

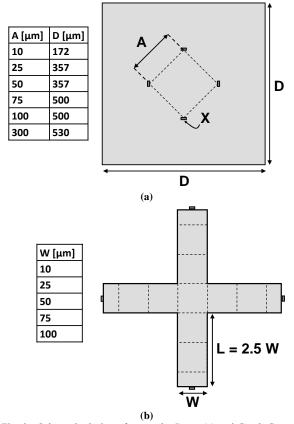

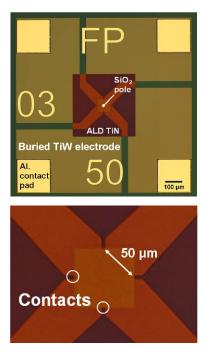

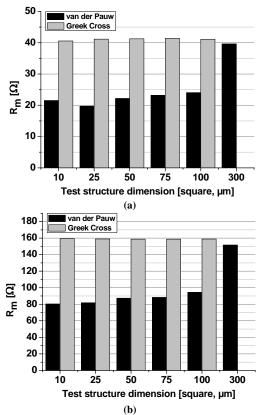

| 9.1  | Four Point Probe Structures with Buried Electrodes for the Electrical Characterization of Ultrathin Conducting Films, A.W. Groenland and. R.A.M. Wolters, A.Y. Kovalgin, and J. Schmitz, University of Twente, Enschede, The Netherlands and *NXP-TSMC, Eindhoven, The Netherlands | 191 |

| 9.2  | Metal and Dielectric Thickness: A Comprehensive Methodology for Back-End Electrical Characterization, L. Bortesi and L. Vendrame, Numonyx, Agrate Brianza Agrate, Italy                                                                                                            | 196 |

| 9.3  | A Test Structure for Assessing Individual Contact Resistance, F. Liu and K. Agarwal, IBM Austin Research Lab., Austin, TX                                                                                                                                                          | 201 |

| 9.4  | Fast Embedded Characterization of FEO Variations in MOS Devices, F. Rigaud, STMicroelectronics, Rousset, France                                                                                                                                                                    | 205 |

|      |                                                                                                                                                                                                                                                                                    |     |

|      | SESSION 10: Capacitance Lee Stauffer, Keithley Instruments and Satoshi Habu, Agilent Technologies Japan, Ltd.                                                                                                                                                                      |     |

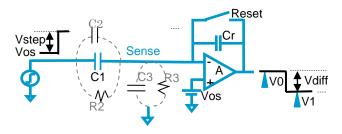

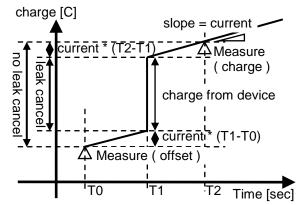

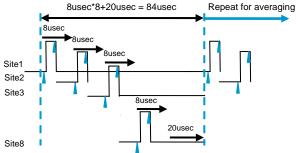

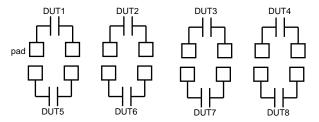

| 10.1 | Benefit of Direct Charge Measurement on Interconnect<br>Capacitance Measurement, Y. Miyake and M. Goto, Agilent<br>Technologies International Japan, Ltd., Tokyo, Japan                                                                                                            | 211 |

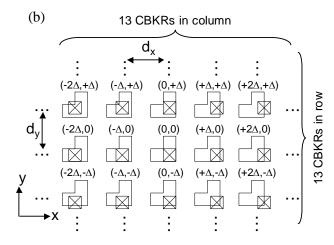

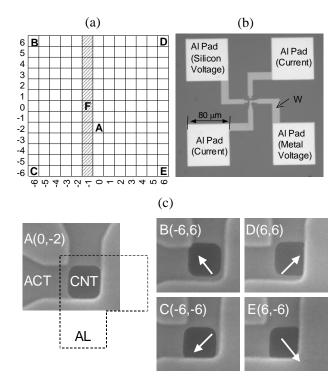

| 10.2 | 4K-cells Resistive and Charge-Base-Capacitive Measurement Test Structure Array (R-CBCM-TSA) for CMOS Logic Process Development, Monitor and Model, K.Y.Y. Doong, L.J. Hung, SC. Lin, H.C. Tseng, A. Dagonis, and S. Pan, Taiwan Semiconductor Manufacturing Co., Hsinchu, Taiwan   | 216 |

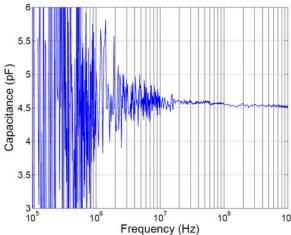

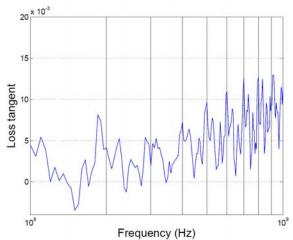

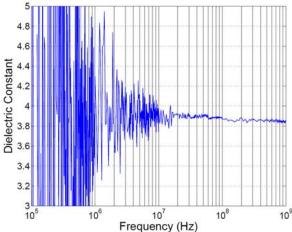

| 10.3 | Practical Considerations for Measurements of Test Structures for Dielectric Characterization, W. Chen, K.G. McCarthy, and A. Mathewson, University College, Cork, Ireland                                                                                                          | 221 |

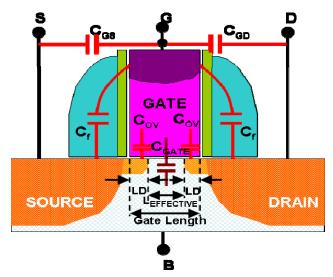

| 10.4 | Test Structure Design, Extraction, and Impact Study of FEOL Capacitance Parameters in Advanced 45nm Technology, S. Ekbote, P. Sadagopan, W. Sy, R. Zhang, Y. Chen and M. Han, Qualcomm, Inc., San Diego, CA                                                                        | 226 |

# High precision on-wafer backend capacitor mismatch measurements using a benchtop semiconductor characterization system

Hans Tuinhout, Fleur van Rossem<sup>f</sup> and Nicole Wils.

NXP semiconductors

High Tech Campus 37, 5656 AE Eindhoven, the Netherlands, hans.tuinhout@nxp.com

# **Abstract**

This paper discusses a sophisticated backend capacitor mismatch characterization technique based on direct capacitance measurements with a standard C-V meter, wafer prober subsite moves to measure the two capacitors of each pair sequentially and monitor the measurement noise, and statistics to take this noise appropriately into account. We describe requirements, capabilities and limitations of this approach. It is concluded that this technique proves excellently suited for assessing the matching performance of backend capacitors in the most relevant range of 10 fF to 10 pF.

# Introduction

Backend (fringe) capacitors are relatively novel integrated passive components, based on the vertical and/or lateral capacitance between stacked metal plates and/or adjacent lines (combs). The introduction of 6 to 10 layers of metallization in contemporary technology nodes, combined with aggressive shrinking of lateral dimensions make backend capacitors relatively efficient in terms of silicon area consumption (0.1 to 10 fF/ $\mu$ m<sup>2</sup>). This, coupled to small voltage dependences, makes backend capacitors suitable for a wide range of analog and mixed-signal applications.

High precision mixed-signal applications such as high resolution analog-to-digital converters and filters are often based on the availability of accurately defined ratios of (switched) capacitors. Such ratios are usually realized by building arrays of unit cell capacitors [1,2,3,4], typically spanning a range of the order of 10 fF (1 unit cell) up to 10 pF (e.g. 1000 parallel unit cells). Good identicalness (matching) of these unit cells is indispensable for such applications.

For closely spaced integrated circuit devices, the matching performance is generally described in terms of the so-called Pelgrom-factor  $A_{\Delta P/P}$ , representing the relation between the relative mismatch fluctuation standard deviation  $\sigma_{\Delta P/P}$  of parameter P and the square-root of the effective area in %µm [5]. The (stacked layers!) backend capacitor mismatch fluctuation standard deviation  $\sigma_{\Delta C/C}$ , is more suitably normalized relative to the population's capacitance value median, as the effective area in square microns is not the most characteristic layout quantity for a stack of metal layers. Consequently, capacitor mismatch area scaling factors ( $A_{\Delta C/C}$ ) are generally expressed in terms

of  $\%\sqrt{(fF)}$ . A typical benchmark number for  $A_{\Delta C/C}$  is  $1\%\sqrt{(fF)}$ .

For analog signal processing applications, parametric mismatch fluctuation standard deviations are required to be of the order of  $10^2$  to  $10^4$  ppm (0.01 to 1 %) to meet linearity specifications. At  $1\%\sqrt(fF)$ , the  $\sigma_{\Delta C/C}$  for a 10 fF capacitor pair should be expected to be around 0.3 % (or 30 aF), while for a population of 10 pF pairs the  $\sigma_{\Delta C/C}$  could very well be 0.01 % or better. Characterization of such small capacitance mismatches places heavy demands on the Short Term Repeatability (STR) or measurement noise, to assure that mismatches are measured with sufficient precision.

Capacitor mismatch values can either be derived (indirectly) by circuit or building block designers through performance evaluation of the electronic systems that are based on them (e.g. the INL in ADCs or frequency fluctuations of loaded ring-oscillators), or they can be measured up front during process development in a parametric test environment. In the latter category, three well-known techniques are available for capacitor mismatch characterization, namely

- Direct capacitance measurements using a standard ABB (auto-balance bridge) LCR meter.

- CBCM; (charge based) capacitor load and unload currents measurements with non-overlapping clocked CMOS inverters [6]

- FGCM; floating gate capacitor matching measurement using an integrated PMOS source follower to sense the midpoint of a capacitive DC voltage divider [7].

Of these three, the first is generally considered too insensitive and/or noisy to characterize the matching of sub 100 fF capacitors with sufficient precision. CBCM was reported by the author of [6] to be prone to accuracy limitations associated with mismatch of the inverter's transistors, while the FGCM method struggles with plasma processing induced charges and damage and/or gate leakage of the source follower transistor [8,9].

This paper challenges the first supposition, namely that capacitor measurements with a standard C-V meter are too noisy and hence not suitable for high precision capacitor mismatch characterization. The outcome of this work is a new measurement algorithm that is based on multiple measurement repetitions and individual device measurements through prober subsite stepping, which proves this assumption wrong. In the following

f Fleur van Rossem is from the University of Twente, the Netherlands. She contributed to this work during an MSc internship assignment at NXP research.

sections we summarize test structure requirements, the measurement algorithm, some outstanding results and a discussion on limitations and possible pitfalls. We conclude that this technique proves excellently suited for assessing the matching performance of backend capacitors in the most relevant range from 10 pF down to as low as 10 fF.

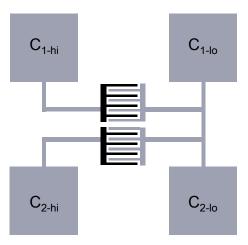

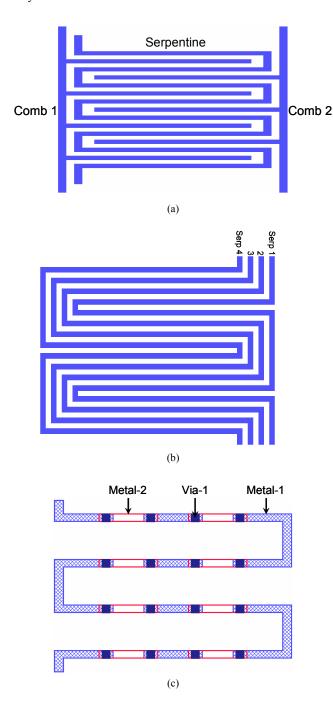

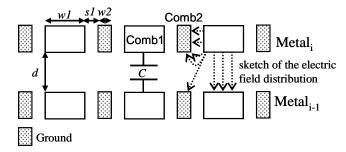

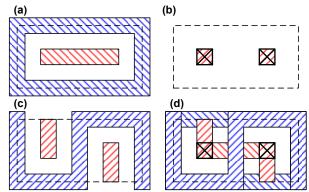

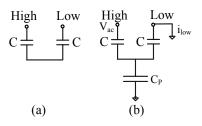

Figure 1. Schematic representation of capacitor matched pair test structure suited for DUT1-2-1-2 characterization. The low and high sides of the capacitors in this example are drawn schematically as intertwined combs. Note however, that there are many alternatives to create backend capacitors.

# **Test Structure Requirements**

The characterization technique described in this paper is based on keeping the measurement system (and hence the test structures) as simple and consistent as possible. Backend capacitor matched pair test structures should be laid out according to the following guidelines:

- 1. Place the two identically designed capacitors as symmetrical as possible between the two sets of probe pads (Figure 1).

- 2. The connection frames between the DUTs (Device Under Test) and their pads should be as symmetrical and as consistent as possible.

- 3. The size of high precision matched backend capacitors should be adjusted by placing multiple minimum capacitor unit cells in parallel in a cross coupled and common centroid layout. Make sure that connections, crossings and via's do not disturb the symmetry of the layout.

- 4. Maintain the metal density symmetry in and around arrays of matched capacitor cells. Use grounded dummy cells around the DUTs when possible.

- 5. Assure that the dummy tiling (metal density homogeneity improvement to facilitate chemical mechanical polishing of backend layers) is symmetrical on AND near matched capacitors. Use the 'no-tile' mask and/or manually placed metal dummy features to adhere to metal density design rules while maintaining test structure layout symmetry. Automatic chip-finishing tiling placement tools can and will result in undesirable (uncontrollable) asymmetries. This was shown to seriously affect

matching of MOS transistors [10], but it needs no arguing that uncontrolled placement of floating metal tiles is bound to have even more devastating effects on the matching of high precision backend capacitors (we are looking for mismatches as low as 0.01 %!).

- 6. Probe pads and connection frames should be laid out only in the upper (two) metal layers to reduce parasitic capacitances.

- 7. Add a test module with just the pads and the frame for optimal zero-ing (open compensation) of the C-meter.

The matching measurements discussed in this paper were obtained from two different backend capacitor types fabricated in two different foundry technologies. The measurement method development and measurement noise impact assessments were mainly done using (MiM) parallel plate capacitors from a 0.18 µm technology, while the proof of the pudding results are based on backend fringe capacitor matched pairs realized in a 45 nm CMOS technology.

# Measurement Method

The test structures are measured with a Keithley 4200-SCS benchtop semiconductor characterization system with the Model 4200-CVU Integrated C-V Option and probed with 200 and 300 mm atto-guarded Cascade-Microtech wafer probers. The C-V option provides easy tailoring of DC and AC measurement conditions and functions, through the standard interactive user interface. DC Coaxial DCP100 Kelvin probes, more than adequate for C-V measurements up to 10 MHz, are used for all experiments. The C-V meter's high and low 'Cur and Pot' cables are directly connected to the SSMC 50 (Kelvin) connectors on the probe holders. For small signal capacitance measurements, the choice of the AC source signal frequency and level as well as the meter settings (measurement speed / filtering) should be chosen to fit DUT and system. Obviously a higher AC frequency and a larger AC signal level make it easier to measure (small) capacitance values. Backend capacitors are practically bias voltage independent and have relatively low resistances in the plates (fingers), allowing large AC signals and fairly high frequencies for the mismatch measurements. Unless mentioned explicitly, the AC signals were set at 99 mV at 1 MHz in all examples discussed in this paper.

Data analysis is done with MS Excel spreadsheets. Macros collect the measurement data from the hundreds of (Excel compatible) Keithley data files (one for each capacitor on each sub-site position), after which median selection, parametric position dependence evaluation and robust statistical analysis are executed and displayed in graphs.

The crux of the high precision capacitor mismatch measurement method presented in this paper is based on the following three key elements:

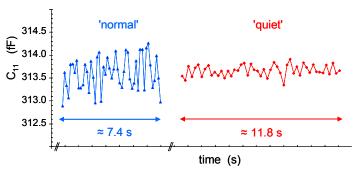

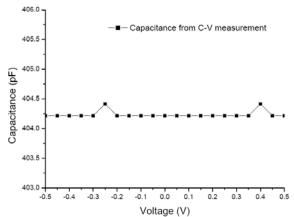

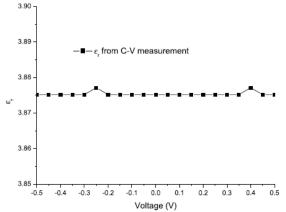

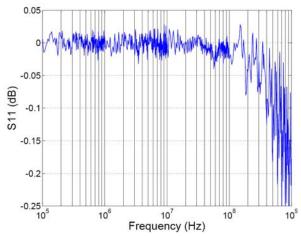

**1. Multiple observations.** To achieve optimum measurement performance with the highest precision, the C-V meter is set to 'quiet'. Under these conditions, the meter yields excellent low measurement noise at an average measurement speed of 0.24 s

per measurement point (Figure 2).

Figure 2. Example of measurement noise of 49 capacitance observations for two meter settings for a 313.6 fF capacitor. Normal: 0.12 s/obs &  $\sigma$ =0.15 %; Quiet: 0.24 s/obs &  $\sigma$ =0.04 %.

However, as indicated in the introduction, the expected capacitor mismatch standard deviations are in the range of 0.01 to 0.3 %, so this performance may not be sufficient for high precision capacitor mismatch studies. From elementary undergrad measurement classes we know that to collect more precise measurement data than those obtainable under standard meter settings, multiple observations can be used. In a white noise dominated system, the uncertainty of the C-measurement is expected to reduce with  $1/\sqrt{N_{\rm obs}}$ , where  $N_{\rm obs}$  is the number of observations used for a single measurement.

The capacitor mismatch measurement algorithm used in this study was built up under the assumption that each capacitance measurement would be repeated anywhere between 9 and 999 times using the sampling mode of the measurement system. Of these multiple observations the median value (the middle value of the low-to-high sorted observations) is then used as the best guess for the capacitance.

This approach was shown before for other types of high precision mismatch measurements [7,11]. Previous studies have not shied away from increasing the number of observations up to several hundreds of measurements to reach sub 100 ppm STR levels. As this obviously results in time consuming measurement sessions for large populations of matched pairs, one should always try to limit  $N_{\rm obs}$  to such a number that the 'real' parametric mismatch fluctuation is limited by the statistical uncertainty associated with the population size, rather than by the measurement noise. As a rule of thumb, one can assume that this is generally the case when the measurement noise is less than one third of the real parametric mismatch fluctuations when the population size is of the order of 60 to 100 samples (typically the number of test dies available on one full wafer).

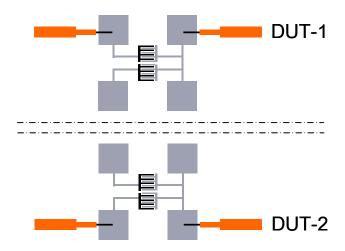

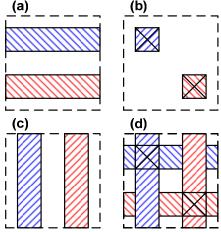

**2. Sub-site moves.** The two capacitors of each pair are measured sequentially by stepping from the first to the second device after the  $(N_{obs})$  measurements on the first capacitor are completed. This is done with the wafer prober through a sub-site move (Figure 3). The main advantage of this is that both capacitors of the pair are measured in exactly the same way, with the same probes, cables and meter (offset).

Figure 3. The principle of DUT-1-2 prober sub-site moves for matched pair measurements: both capacitors of the pair are measured with exactly the same measurement set-up.

**3. DUT-1-2-1-2 measurement noise correction.** The main novelty of the currently described algorithm is that each pair is measured **twice** to quantify the impact of the measurements noise. This is done by stepping backwards and forward again and re-measuring both capacitors. This so-called DUT-1-2-1-2 method allows separating the measurement noise from the true device mismatch. This is done as follows:

The relative capacitance mismatch for the **first** measurement of a particular pair i of the population is defined as

$$\Delta C/C_{1i} = 2x (C_{11i} - C_{21i}) / (C_{11i} + C_{21i}),$$

where  $C_{11i}$  and  $C_{21i}$  represent the **first** time capacitors 1 and 2 are measured for pair i. The total population of matched pair measurements then yields a relative capacitor mismatch fluctuation standard deviation estimator  $\sigma_{\Delta C/C1}$ . Likewise, with  $C_{12i}$  and  $C_{22i}$  representing the **second** measurement for each capacitor, one obtains:

$$\Delta C/C_{2i} = 2x (C_{12i} - C_{22i}) / (C_{12i} + C_{22i}),$$

with  $\sigma_{\Delta C/C2}$  as estimator for the standard deviation of the matching for the set of second measurements. The impact of the measurement noise on the mismatch estimation for pair i is now sampled in the STR of the mismatch measurements

$$\Delta\Delta C/C_i = \Delta C/C_{1i} - \Delta C/C_{2i}$$

giving  $\sigma_{\Delta\Delta C/C}$  as an estimator for its standard deviation. The essence of this is that although only one measurement noise (STR) observation is sampled for each pair, the collection STR observations resulting from the entire population (60 to 100 pairs) of these DUT-1-2-1-2 double mismatch measurements allows very reliable estimation of the measurement system noise.

If the differences between the two subsequent mismatch measurements for each pair are statistically independent from each other as well as from their actual mismatch value (which is more than likely since we are looking at measurement noise), the short-term repeatability standard deviation for a particular measurement can be estimated as

$$\sigma_{STR} = \sigma_{\Delta\Delta C/C} / \sqrt{2}$$

and the variance of the STR can be subtracted from the measured mismatch variance to obtain a noise corrected estimator for the mismatch standard deviation  $\sigma_{\Delta C/C\ cori}$  through

$$\sigma^2_{\Delta C/C\_cor1} = \sigma^2_{\Delta C/C1} - \sigma^2_{STR} \ \, \text{or} \ \, \sigma^2_{\Delta C/C\_cor2} = \sigma^2_{\Delta C/C2} - \sigma^2_{STR}$$

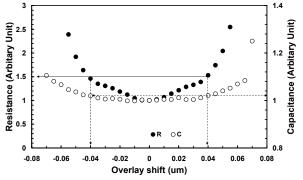

# Results

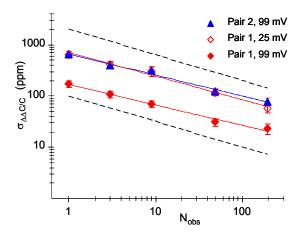

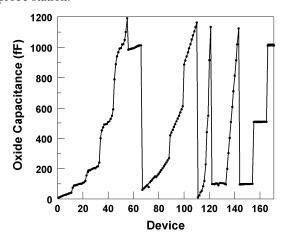

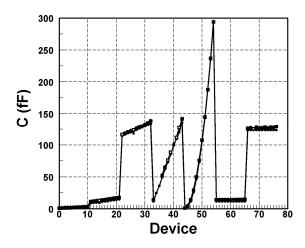

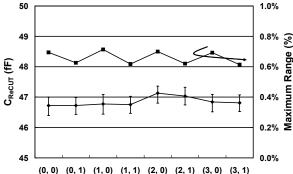

1. Measurement algorithm characterization. The performance of the noise corrected DUT-1-2-1-2 technique as described above is first demonstrated by an example based on two high density MiM parallel plate capacitor matched pairs built in an 0.18  $\mu$ m analog & mixed signal process. The populations consist of 98 pairs spread out across a 200 mm wafer. Pair 1 is a 1.24 pF (40x40  $\mu$ m²) pair and pair 2 a 313 fF (20x20  $\mu$ m²) pair. Note that the second pair's capacitors are a factor four smaller in area and capacitance. These pairs were measured with different numbers of N<sub>obs</sub>'s ranging from 1 to 195, and two AC signal levels. Some of the results are summarized in figures 4, 5 and 6.

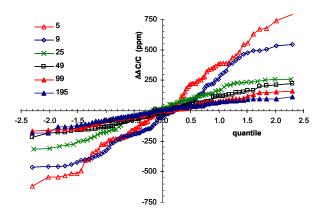

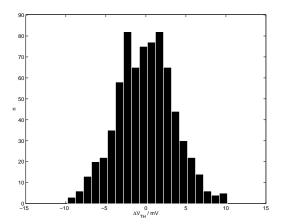

Figure 4. Example of normal scaled cumulative probability plot of  $\Delta\Delta C/C$  for different  $N_{obs}$ , varying between 5 and 195. Pair 2 (313 fF); AC signal: 99 mV @ 1 MHz.

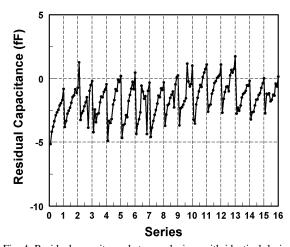

Figure 4 shows an initial sanity check for the method, namely whether the STR is normally distributed. The figure shows normal scaled cumulative probability plots of the mismatch short term repeatability  $\Delta\Delta C/C_i$  for different numbers of  $N_{obs}$  for the 313 fF pair 2. Straight lines confirm normal distributions and the slopes represent the standard deviations. As expected,  $\sigma_{\Delta\Delta C/C}$  reduces with  $N_{obs}$ .

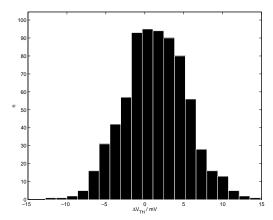

Figure 5 summarizes the scaling of  $\sigma_{\Delta\Delta C/C}$  with  $N_{obs}$  for both pairs. The repeatability indeed scales with  $N_{obs}$ , albeit that the expected  $1/\sqrt{N_{obs}}$  behavior (dashed lines) is not fully met. It is important to note however, that the four times larger capacitors of pair 1, measured with a proportionally lower signal level yields a comparable STR at the same  $N_{obs}$  as the smaller pair with the full 99 mV signal. This implies that one has two independent knobs ( $N_{obs}$  and AC level) to adjust the STR to reach the required

precision for a capacitor mismatch measurement. Note that for pair 2 one would need at least 200 observations to bring the STR down to a level of 100 ppm that would seem appropriate according to the rule of thumb suggested in the previous section.

Figure 5. STR of capacitance mismatch measurements vs.  $N_{obs}$  for different capacitor sizes and AC signal levels

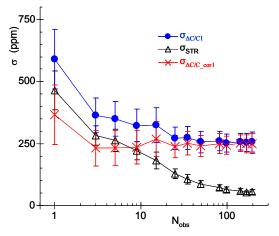

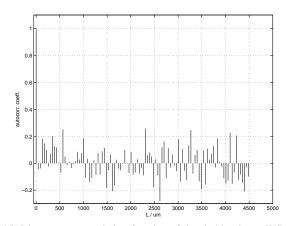

Figure 6.  $\sigma_{AC/CI}$ ,  $\sigma_{STR}$  and  $\sigma_{AC/C\_cori}$  vs  $N_{obs}$  for pair 2 (313 fF); AC signal: 1 MHz, 99 mV; error bars represent  $3\sigma$  statistical uncertainty from bootstrap analyses.

The real strength of the noise corrected DUT-1-2-1-2 mismatch measurement method is depicted in figure 6, where  $\sigma_{\Delta C/C_1}$ ,  $\sigma_{STR}$  and  $\sigma_{\Delta C/C\_Corl}$  are all plotted versus  $N_{obss}$ . For this population, the 'real' mismatch standard deviation estimator ( $\sigma_{\Delta C/C\_Corl}$ ) is apparently about 250 ppm. The 3 $\sigma$  uncertainty bars in figure 6 were obtained from bootstrap statistical uncertainty analyses on the measured populations of  $\Delta C/C_1$ 's and  $\Delta \Delta C/C$ 's. It is clear from this figure that a substantial number of observations is required before  $\sigma_{\Delta C/C_1}$  reaches its saturation level. The most striking conclusion from this experiment is however, that although one would expect that at least 50 to 100 observations would be required to obtain sufficient STR (according to the reasoning given above), already by as few as 25 observations, the mismatch fluctuation estimator is well within the statistical

uncertainty that is calculated for this population. For the brave even 3 or 9 observations would probably suffice. This means that statistics and subsequent noise correction really helps to estimate the true mismatch fluctuation standard deviation, even when the measurement noise is substantial.

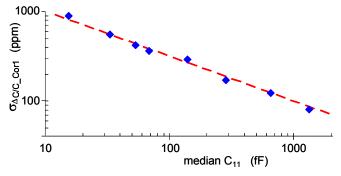

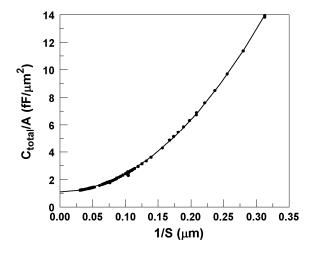

Figure 7. Pelgrom plot of  $\sigma_{AC/C\_corl}$  vs. the medians of  $C_{11}$  for a collections of populations of cross coupled unit cell matched capacitors. Dashed line represents 0.32 %/fF area scaling.

**2.** The proof of the pudding. The encouraging results of the noise corrected DUT-1-2-1-2 measurement method of the previous section are very convincingly enhanced by figure 7. This example of the backend capacitor relative mismatch fluctuation area scaling was measured using a set of 8 properly laid-out stacked metal comb (fringe cap) matched capacitors fabricated in a 45 nm CMOS technology. Population size on the 300 mm wafers is 98 pairs for each layout. The median C-value for this example ranges from 1.33 pF for the largest capacitor (144 unit C-cells) to a minimum of only 15 fF for a pair consisting of 2 (2x2 cross-coupled) unit cells, see table 1. Both the textbook-like mismatch fluctuation area scaling behavior, as well as the very acceptable 0.32 % \( \sqrt{fF} \) (dashed line in figure 7) for this type of devices, while going all the way down to sub 20 fF capacitors took away all reservations that stake holders in the field had against using direct C-V measurements for high precision capacitor mismatch measurements. This example indeed proves quite convincingly that the measurement noise corrected DUT-1-2-1-2 technique is very well suited for high precision backend capacitor mismatch characterization.

# Discussion

A perhaps counter-intuitive observation from figure 5 is that mismatch measurements for large capacitors are less affected by measurement noise than for small capacitors. This means that it is apparently 'easier' to measure the mismatch of large capacitor pairs than for small pairs, even though the matching of large capacitors is much better (100 ppm or lower). This is due to the larger signal that is measured in the AC meter (detector), which is proportional to the product of the capacitance value and the AC voltage level. While the mismatch standard deviation of smaller capacitor pairs increases with the inverse of the square root of the median capacitance value, the measurement noise increases inversely with its median (as the measured signal decreases linearly). This behavior is fundamentally different from

mismatch characterization of for instance resistors or transistors, where the currents generally remain constant or even increase with smaller dimensions. In combination with an inverse square-root area increase of the mismatch standard deviations, parametric mismatch standard deviations of **small** devices are generally easier to measure.

Table 1. Details and results of an example of noise corrected DUT-1-2-1-2 capacitor mismatch characterization.

| med_C <sub>11</sub> (fF) | # cells | σ <sub>ΔC/C_cor1</sub> (ppm) | σ <sub>STR</sub><br>(ppm) | N <sub>obs</sub> |

|--------------------------|---------|------------------------------|---------------------------|------------------|

| 1330                     | 144     | 80                           | 23                        | 49               |

| 655                      | 72      | 125                          | 44                        | 49               |

| 286                      | 32      | 170                          | 90                        | 49               |

| 140                      | 16      | 290                          | 190                       | 49               |

| 68                       | 8       | 360                          | 330                       | 99               |

| 54                       | 6       | 424                          | 360                       | 99               |

| 33                       | 4       | 560                          | 620                       | 99               |

| 15                       | 2       | 890                          | 1370                      | 99               |

With this in mind we can look back at figure 7 and table 1. Note that both on the 'low' precision side ( $\sigma_{\Delta C/C} < 0.1$  %) as well as on the high precision side ( $\sigma_{\Delta C/C} < 0.01 \%!!$ ), there is no evidence of significant deviation from the expected physical  $1/\sqrt{fF}$  behavior. This becomes even more striking when the data of table 1 are taken into consideration. Prior to this study we (kind of arbitrarily) decided that 49 observations would probably be enough for capacitors larger than 100 fF, while the number of observations was increased to 99 for the smaller ones. After analyzing the results, one cannot but conclude that statistics helps fantastically in this case! Table 1 reveals that the STRs for the smallest pairs are even significantly larger than their mismatch standard deviations. The largest pairs on the other hand come out with a fantastic low STR of 23 ppm with only 49 observations. This implies that there is a lot more room for measurement precision improvement on this side. Although such devices did not form part of the examples in this paper, it must be deemed more than likely that for capacitors larger then 10 pF, STRs below 10 ppm are attainable.

The reason why figure 5 does not follow a perfect  $1/\sqrt{N_{obs}}$  trend is believed to be related to slow measurement system drift and/or 1/f noise in the system. Extremely long measurements (up to 1000 observations) have so far not yielded sub 10 ppm STRs for single digit pF capacitors due to an apparent saturation of the STR. Note that for 1000 observation the system takes about 4 minutes per capacitor or 16 minutes per pair, or over 26 hours for an entire population of 98 pairs, opening up plenty of room for temperature and equipment drifts and other disturbances.

As the essence of the noise corrected DUT-1-2-1-2 method lies in taking the measurement noise into account, it is obviously not

really necessary to **step back** to the capacitors after collecting multiple observations on each capacitor the first time. Theoretically as well as practically it will suffice to collect a certain number of observations for both capacitors (DUT-1-2) and then divide this number into two equal groups to calculate  $\Delta C/C_{1i},$   $\Delta C/C_{2i}$  and  $\Delta\Delta C/C_{i}.$  The only difference between a DUT-1-2 method and the DUT-1-2-1-2 version lies in possible effects of probe-to-pad resistance variations that may affect the double stepped version more as this involves more probe-downs.

To avoid probing twice on exactly the same 'scratch' of the pad, we applied a minor (5 μm) offset in the landing positions when stepping back to DUTs 1 and 2. Due to a relatively large capacitive coupling between the probe needles and the test structure in that particular case (clumsy layout of test structure and pads, in combination with wrong orientation of the probe needles), a small systematic offset in  $\Delta\Delta C/C_i$  was encountered, corresponding to a small but significant capacitive mismatch offset of as small as 13 aF due to the 5 µm different location of the second probe landing. In this context it must be mentioned that it proves important to assure that probe needles are always placed as good as possible in an identical orientation relative to both capacitors of the pair. Beware that the placement of the probe needles is such that they do not cross either of the two devices during either of the probe downs, giving rise to a different parasitic coupling to DUT1 compared to DUT2. A meager 100 aF offset is easily picked up due to direct cross-talk between DUT and probe.

The final remark on the limitations of the technique is related to the total measurement time that it consumes. It should be realized that a figure like Figure 7 is based of in total more than 216 thousand capacitance measurements. At 0.24 s per observation this corresponds to about 15 hours measurement system / prober time for 8 populations of one capacitor type on one wafer. From a device research as well as a process characterization / modeling standpoint this should be deemed quite acceptable, given the superb quality of the resulting mismatch fluctuation area scaling graph.

# **Conclusions**

This paper demonstrates that it is quite well possible to characterize high precision backend capacitor mismatch using a standard benchtop semiconductor characterization system. Test structure requirements to assure suitability for a prober sub-site stepping based measurement approach were summarized. The new measurement approach is based on combining multiple observations, prober sub-site stepping and measurement noise assessment during the mismatch measurements. By taking measurement noise properly into account, reliable and realistic estimators for the relative capacitor mismatch standard deviations can be determined. This was demonstrated on different types of matched backend capacitor pair implementations from different technologies. The method proves effective for small capacitor pairs down to values as low as 10 fF, albeit that one must use sufficiently large populations of matched pairs and rely

on the help of statistics, as the measurement noise for such small capacitors can easily be larger than the mismatch fluctuation standard deviation. Although larger capacitance pairs (1 to 20 pF) may have very small mismatch standard deviations (well below 100 ppm), their mismatch characterization turns out to be relatively easy, due to the larger AC signal levels in the meter. A few points of attention and limitations of the technique are worth paying attention to, but it can be concluded that the noise corrected DUT-1-2-1-2 capacitor mismatch characterization technique proves excellently suited for assessing the matching performance of backend capacitors in the 10 fF to 10 pF range which is relevant for most high precision mixed signal applications.

# References

- [1] J. McCreary and D.A. Sealer, "Precision Capacitor Ratio Measurement Technique for Integrated Circuit Capacitor Arrays", IEEE Transactions on Instrumentation and Measurement, Vol 28, No 1, pp 11-17, 1979.

- [2] J. McCreary, "Matching Properties, and Voltage and Temperature Dependence of MOS Capacitors", IEEE Journal of Solid State Circuits, Vol 16, No 6, pp 608-616, 1981.

- [3] R. Singh and A.B. Bhattacharyya, "Matching Properties of Linear MOS Capacitors", Solid State Electronics, Vol 32, No 4, pp 299-306, 1989.

- [4] M.J. McNutt, S. LeMarquis and J.L. Dunkley, "Systematic Capacitance Matching Errors and Corrective Layout Procedures", IEEE Journal of Solid State Circuits, Vol 29, No 5, pp 611-616, 1994. [5] M.J.M. Pelgrom, A.J. Duinmaijer and A.P.G. Welbers, "Matching Properties of MOS Transistors", IEEE Journal of Solid State Circuits, Vol 24, No 5, pp 1433-1440, 1989.

- [6] J.C. Chen, D. Sylvester, C. Hu, H. Aoki, S. Nakagawa and S-Y. Oh, "An On-Chip, Interconnect Capacitance Characterization Method with Sub-Femto-Farad Resolution", ICMTS97 Proceedings of the IEEE International Conference on Microelectronic Test Structures, Vol. 10, pp. 77-80, 1997.

- [7] H.P. Tuinhout, H. Elzinga, J.T. Brugman and F. Postma, "The Floating Gate Measurement Technique for Characterization of Capacitor Matching", IEEE Transactions on Semiconductor Manufacturing, Vol 9, No 1, pp 2-18, 1996.

- [8] O. Roux dit Buisson, G. Morin, F. Paillardet and E. Mazaleyrat, "A New Characterization Method for Accurate Capacitor Matching Measurements using Pseudo-Floating Gate Test Structures in Submicron CMOS and BiCMOS Technologies", ICMTS98 Proceedings of the IEEE International Conference on Microelectronic Test Structures, Vol. 11, pp. 223-227, 1998.

- [9] Weidong Tian et al, "Gate Oxide Leakage and Floating Gate Capacitor Matching Test", ICMTS07 Proceedings of the IEEE International Conference on Microelectronic Test Structures, pp. 120-123, 2007.

- [10] H.P. Tuinhout and M. Vertregt, "Characterization of Systematic MOSFET Current Factor Mismatch Caused by Metal CMP Dummy Structures", IEEE Transactions on Semiconductor Manufacturing, Vol 14, No 4, pp 302-310, 2001.

- [11] T. Ewert, H.P. Tuinhout, N.A.H. Wils and J. Olsson "Design and implementation of an ultra high precision parametric mismatch measurement system", ICMTS05 Proceedings of the IEEE International Conference on Microelectronic Test Structures, pp. 149-154, 2005.

# Static Noise Margin Evaluation Method Based on Direct Polynomial-Curve-Fitting with Universal SRAM Cell Inverter TEG Measurement

Kazuyuki Nakamura, Kazunori Noda, and Hiroki Koike\*

Center for Microelectronic Systems, Kyushu Institute of Technology

\*Fukuoka Industry, Science & Technology Foundation

680-4 Kawazu, Iizuka, Fukuoka 820-8502, Japan

Tel: +81-948-29-7584, Fax: +81-948-29-7586, Email: nakamura@cms.kyutech.ac.jp

### ABSTRACT

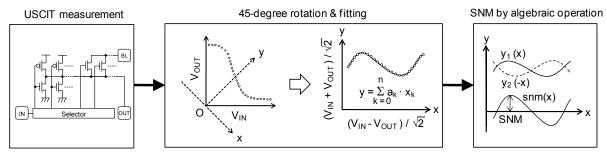

A new method to evaluate the Static Noise Margin (SNM) for leading-edge CMOS SRAM development is proposed. This method includes: (1) direct measurement of the inverter DC transfer curves using a "Universal SRAM Cell Inverter TEG (USCIT)" with arbitrary transistor ratios, (2) curve-fitting of the measured data to polynomial functions in a 45-degree rotated space, and (3) a database of the polynomial coefficients to evaluate and optimize the SNM by a simple algebraic operation. The SNM values obtained using this method are in good agreement with the measured SRAM operations.

### INTRODUCTION

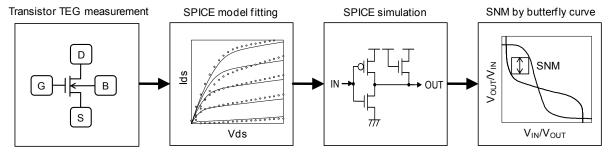

In the development of SRAMs for the 45-nm technology generation and beyond, it is difficult to maintain a sufficient static noise margin (SNM) in the SRAM because of supply voltage scaling and device variability [1][2]. Historically SNM analysis using classical MOSFET Id-Vd expressions has been used, but it has been shown that this cannot fit the scaled CMOS technologies. A method that uses SPICE simulation is now more widely used; the procedure for this is depicted in Fig. 1 [3][4]. This method comprises the following steps: (i) measuring I-V characteristics for a single transistor TEG, (ii) extracting the SPICE model parameters, (iii) simulating DC transfer curves of the inverter in an SRAM cell, and (iv) drawing the butterfly curves by combining the two inverter characteristics and reading off the SNM value. This method is, however, inadequate in several aspects, such as fitting errors in the SPICE model parameter extraction and the accuracy limit of the SPICE simulation. This imposes considerable restrictions on the design of highly scaled CMOS SRAM.

# **NEW SNM EVALUATION METHOD**

The proposed method, illustrated in Fig. 2, comprises the following steps: (1) direct measurement of inverter DC transfer curves using an USCIT that can realize arbitrary transistor ratios, (2) fitting of the measured data to polynomial functions in a 45-degree rotated space, and (3) storing the coefficients of the polynomial functions in a

database to evaluate and optimize the SNM by a simple algebraic operation. Since this method is based on measured data and directly curve-fitted polynomials, neither SPICE model extraction nor other accuracy degradation steps are included. In addition, the SNM can be obtained simply by subtracting the coefficients of two polynomials which can be stored in a database based on the measured data. This method requires neither SPICE simulation nor drawing butterfly curves, therefore, it is suitable for statistically aware memory cell optimizations.

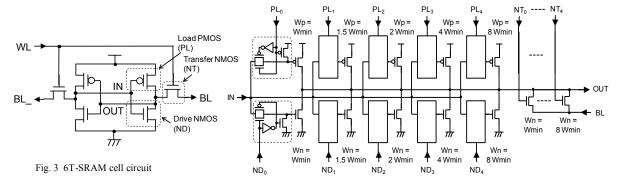

# DESIGN OF UNIVERSAL SRAM CELL INVERTER TEG (USCIT)

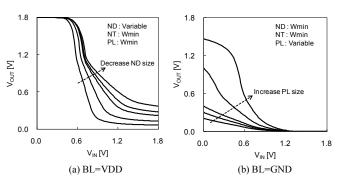

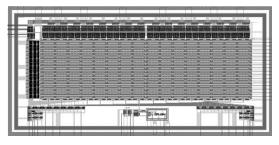

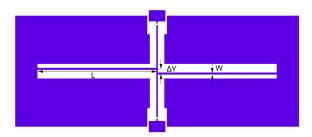

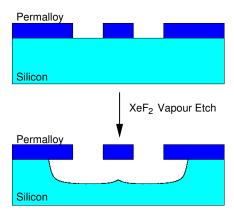

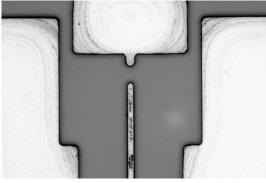

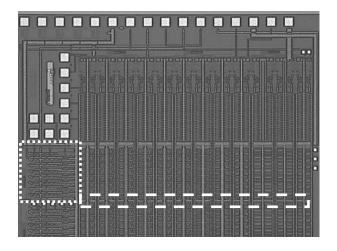

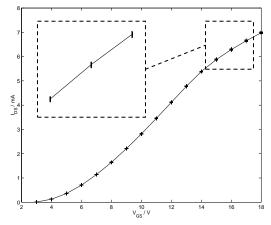

A typical 6-transistor SRAM cell circuit is shown in Fig. 3. To calculate the SNM, the DC transfer characteristics of the inverter with three transistors, namely Load PMOS (PL), Driver NMOS (ND), and Transfer NMOS (NT), must be evaluated. We have developed the USCIT that can evaluate arbitrary transistor ratios for these three transistors with selectable binary-weighted transistor arrays as shown in Fig. 4. The gate width (W) can be set by 5-bit signals for PLi, NDj, and NTk (where i, j, k=0~4), respectively. We design the five gate widths for the weighted transistor array: 1/1.5/2/4/8 x Wmin, instead of a simple binaryweighted array using Wmin as the base. Wmin is the minimum transistor gate width determined by process technology. By combining these widths, we can successfully achieve any transistor size covering  $1.0 \sim 15.5$ times the value of Wmin with a minimum resolution of half the value of Wmin. As a result, about 30,000 design combinations can be examined with this USCIT. Fig. 5 shows the layout of an USCIT using 0.18-um technology. The macro size is 17 x 108 um<sup>2</sup>. The measured DC transfer characteristics for the USCIT are shown in Fig. 6. By setting the level of the BL terminal to VDD or GND, we obtain the DC transfer curves (Fig.6 (a) and (b)) corresponding to the SRAM READ/WRITE operations, respectively.

# POLYNOMIAL-CURVE-FITTING IN A 45-DEGREE ROTATED SPACE

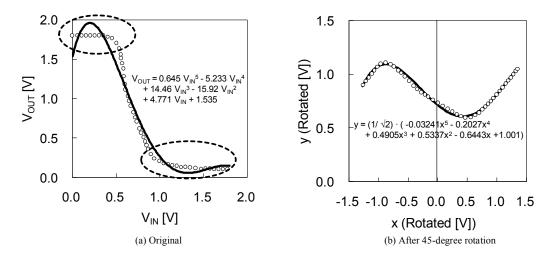

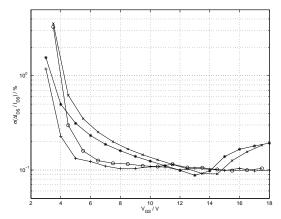

A method that utilizes Butterworth filter function for DC transfer curve fitting was proposed [5]. However, we tried

to fit the DC transfer curves measured by the USCIT to simpler polynomial functions. Since parts of the curve are parallel to the X- or Y-axis as shown within the dotted area in Fig. 7(a), it would be difficult to fit the curve accurately even if the degree of the polynomial were increased. In order to solve this issue, we rotate the measured curve by 45 degrees in the X-Y coordinates before the polynomial curve fitting. Table 1 compares the accuracy of the curve fitting between the original and rotated curves. Rotating the curve improves the accuracy significantly. The error can be suppressed down below 1% by extending the polynomial to the degree of 4. The results of fitting a curve to a polynomial function of degree of 5 are shown in Fig. 7(b).

# SNM CALCULATION WITH POLYNOMIAL DATABASE

The SNM of an SRAM cell is calculated from the polynomial functions of the 2 inverters that compose the SRAM cell. Here we assume that the 2 characteristics are expressed by the following polynomial functions;

$$y_1(x) = (1/\sqrt{2}) \sum_{k=0}^{n} (a_{1k} \cdot x^k) \quad ... (1)$$

$$y_2(x) = (1/\sqrt{2}) \sum_{k=0}^{n} (a_{2k} \cdot x^k) \quad ... (2)$$

The SNM function, snm(x), is defined by subtracting  $y_2(-x)$  from  $y_1(x)$ . Using Eqs. (1) and (2), we obtain

$$snm(x) = y_1(x) - y_2(-x)$$

$$= (1/\sqrt{2}) \sum_{k=0}^{n} [\{a_{1k} - (-1)^k \cdot a_{2k}\} \cdot x^k] \dots (3)$$

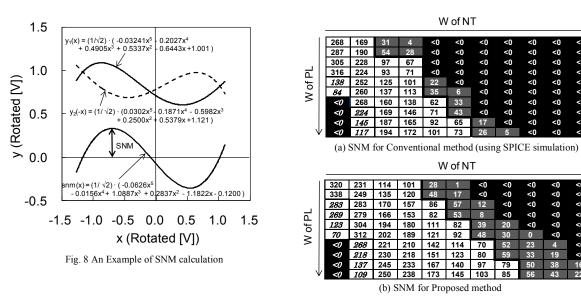

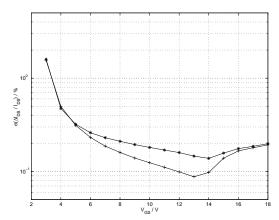

An example of function snm(x) is plotted in Fig. 8. The SNM is the smaller of the absolute values of the 2 extrema (maximum and minimum values) in Eq. (3). Note that if the polynomial functions are fitted into 5-degrees or less, the algebraic solution can be used to find the extrema. As a result, the corresponding SNM value can be calculated instantly by a simple algebraic operation on the polynomial coefficients in the fitted-curve database.

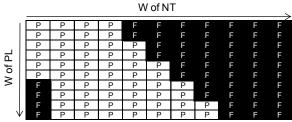

# EXPERIMENTAL RESULTS

We have fabricated a 256-bit SRAM chip, in which the unit cell is composed of two USCITs as shown in Fig. 4. The chip layout is shown in Fig. 9. Figs. 10(a), (b), and (c) show correlations between the SNM values calculated from the conventional SPICE simulation method, SNM values obtained from the measurement results of the USCIT, and PASS/FAIL values of an entire 256-bit SRAM TEG chip operation, respectively. The horizontal and vertical axes denote the gate widths for Transfer NMOS (NT) and Load PMOS (PL), respectively. The Drive NMOS (ND) size is fixed in all cases. In Figs. 10(a) and (b) the smaller of the Write or Read SNM values [in mV] is written in each block, with Write SNM values appearing in a Italic font and Read SNM values in a solid font. Each black and hatched block denotes the region where SNM < 0 and  $0 \le$ SNM < 60mV, respectively. In Fig. 10(c), 'P' and 'F' indicate Pass and Fail operations, respectively. According to these results, the measured operational margin of a 256 bit SRAM (Fig.10(c)) is in good agreement with the SNM evaluation from the USCIT measurement (Fig.10(b)), when taking into account the cell transistor mismatch (i.e., 60mV for this measurement).

# CONCLUSION

We have developed a new SNM evaluation method based on the measurement results of an USCIT, polynomial curve fitting with a 45-degree rotation, and a polynomial coefficients database. This method has demonstrated greater accuracy than the conventional method that uses SPICE simulation, and is suitable for data processing covering the comprehensive conditions such as transistor-sizes, voltage, temperature, etc. The proposed method is, therefore, especially effective in establishing reliable guidelines for the early-stage development of highly scaled CMOS SRAM cells.

# ACKNOWLEDGMENTS

The VLSI chip design and fabrication were supported by the VLSI Design and Education Center (VDEC), University of Tokyo, in collaboration with Rohm Corporation and Toppan Printing Corporation. This research was supported by funds from the Japanese Ministry: MEXT via the Kyushu knowledge-based cluster project. The authors thank NEC Micro Systems, Ltd. for their useful suggestions.

# REFERENCES

- [1] S. Inaba H. Kawasaki, K. Okano, T. Izumida, A. Yagishita, A. Kaneko, K. Ishimaru, N. Aoki, and Y.Toyoshima, "Direct evaluation of DC characteristic variability in FinFET SRAM cell for 32 nm node and beyond," *IEDM Tech. Digest*, pp. 487 490, Dec. 2007.

- [2] M. Miyamura, T. Fukai, T. Ikezawa, R.Ueno, K.Takeuchi, and M. Hane, "SRAM critical yield evaluation based on comprehensive physical / statistical modeling, considering anomalous non-Gaussian intrinsic transistor fluctuations," *Symposium on VLSI Technology Tech. Digest*, pp. 22 23, Jun. 2007.

- [3] E. Seevinck, F. J. List, and J. Lohstroh, "Static-noise margin analysis of MOS SRAM cells," *IEEE J. Solid-State Circuits*, vol. SC-22, no. 5, pp. 748-754, Oct. 1987.

- [4] A. J. Bhavnagarwala, X. Tang, and J. D. Meindl, "The impact of intrinsic device fluctuations on CMOS SRAM cell stability," *IEEE J. Solid-State Circuits*, vol. 36, no. 4, pp. 658-665, Apr. 2001.

- [5] Q. Chen, A. Guha and K. Roy, "An accurate analytical SNM modeling technique for SRAMs based on Butterworth filter function," *Proc. of the 20th International Conference on VLSI Design*, pp. 615-620, Jan. 2007.

Fig. 1 Conventional method for calculating SNM values

Fig. 2 The proposed method for calculating SNM values

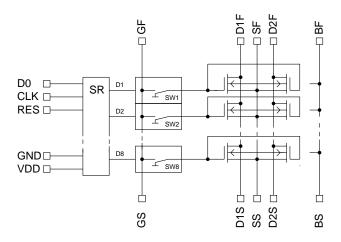

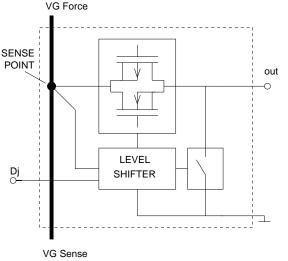

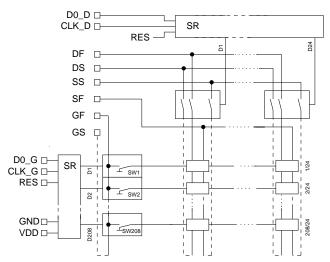

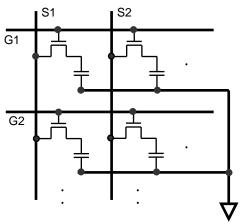

Fig. 4 USCIT circuit to measure inverter DC transfer characteristics

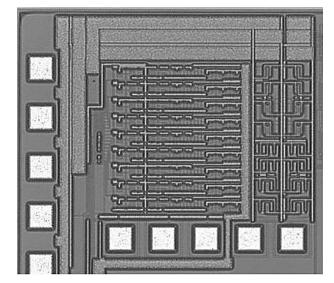

Fig. 5 Layout of the USCIT

TABLE I FITTING ERROR VERSUS THE DEGREE OF THE POLYNOMIAL USED FOR FITTING

| Degree of polynomial                | 3    | 4   | 5   | 6   | 7   | 8   | 9   |

|-------------------------------------|------|-----|-----|-----|-----|-----|-----|

| Original curve fitting [%]          | 10.4 | 5.7 | 5.6 | 4.0 | 2.8 | 2.8 | 2.1 |

| 45-degree rotated curve fitting [%] | 2.0  | 0.7 | 0.7 | 0.6 | 0.6 | 0.2 | 0.2 |

Fig. 6 Measured inverter DC transfer characteristics

Fig. 7 Examples of DC curve fitting to a polynomial of degree of 5 (Circles indicate measured data, while the solid line is the fitted curve.)

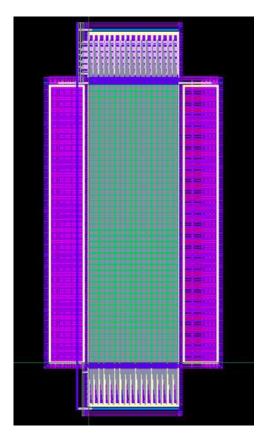

Fig. 9 256-bit SRAM TEG layout using 0.18-um technology

(c) Measured PASS/FAIL with 256-bit SRAM Operation

Fig. 10. Experimental results

# Addressable Arrays Implemented with One Metal Level for MOSFET and Resistor Variability Characterization

Mark B. Ketchen, Manjul Bhushan\* and Greg Costrini\*

IBM Research, T. J. Watson Research Center, Route 134, Yorktown Heights NY 10598, USA \*IBM Systems and Technology Group, 2070 Route 52, Hopewell Junction, NY 12533, USA

### ABSTRACT

Addressable array test structures for rapid collection of statistical distributions of MOSFET parameters and parasitic resistances are described. A unique feature of these designs is that they require only one level of metal, yet are compact for placement in the scribe line for early process learning. MOSFET measurements are made over full range of I-V characteristics including leakage currents of individual devices in the sub-threshold region. A modular approach for test structure integration and parallel testability enables high efficiency in design and data acquisition.

# INTRODUCTION

With CMOS scaling, there is an increasing need for characterization and modeling of statistical variations in MOSFET characteristics [1]. Such variations arise from, for example, random dopant fluctuations, line-edge roughness and systematic spatial effects. It is important to model and manage such variability early in the technology development cycle as we transition from 45 nm to 32 nm technology nodes and beyond. Test structure designs comprising arrays of devices reported earlier are typically complex with several metal layers and best suited for a mature technology or occupy a large area [2-11]. Another approach, that uses compact designs with two levels of metal, does not allow accurate measurement of sub-threshold currents [12].

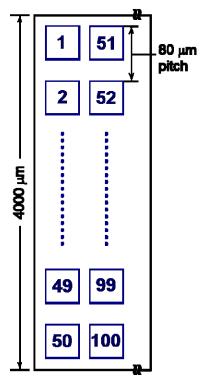

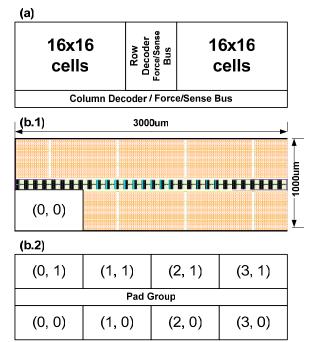

In this work, we describe very compact test structure designs for collecting modest statistics on the full range of MOSFET characteristics as well as resistive elements such as metalsilicon contacts and metal wires. The design of an entire test structure macro, comprising 6 to 8 arrays, each of 30 Devices Under Test (DUTs), is accomplished with only a single metal level and is suitable for placement in the scribe line for early learning in the technology development or manufacturing cycle. Macros are assembled in a modular fashion to facilitate design of experiments. Multiple arrays within a macro can be tested in parallel for rapid data collection. The design flexibility and data integrity has been demonstrated in the 45 nm and 32nm technology nodes. Both PD-SOI (Partially-Depleted Silicon on Insulator) and bulk versions of these designs are currently in use at IBM.

# DESCRIPTION OF TEST STRUCTURES AND METHODOLOGY

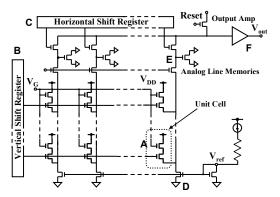

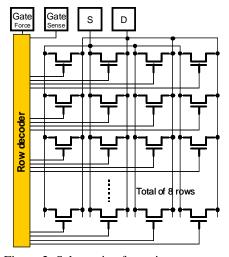

The basic building block of our test structures comprises an electrically one-dimensional array of 30 DUTs, circuitry for supplying appropriate currents and voltages and a 5 bit decoder to select any one, all, or none of the DUTs for measurement. This building block, or array-unit, is placed within a 60  $\mu m$  x 40  $\mu m$  area between two contact pads which provide connections to all 30 DUTs in parallel. For MOSFET array-units, the source and drains of all DUTs are connected to these common adjacent pads and the decoder outputs activate the voltages applied to the individual gates of the DUTs. For resistor array-units, the voltage apply/current measure leads of all DUTs are connected to the common adjacent pads and the decoder outputs activate the current through the DUT and the voltage readout across the DUT.

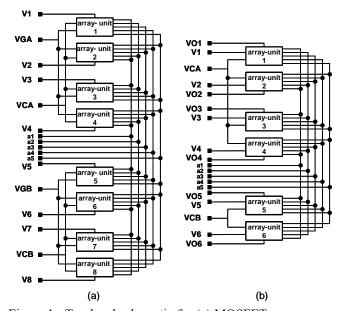

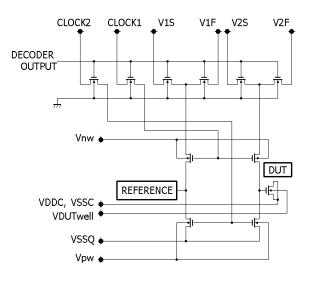

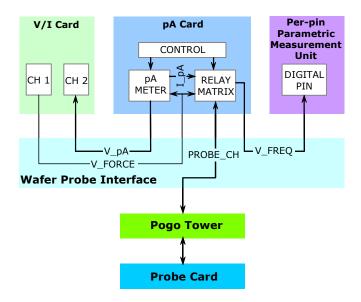

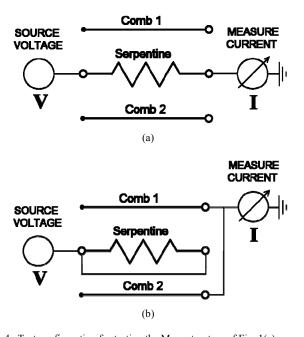

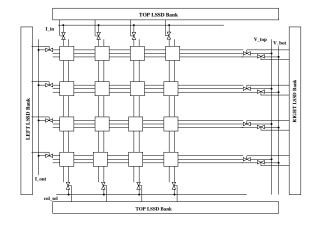

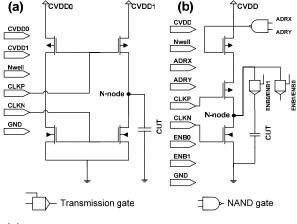

Figure 1: Top level schematic for (a) MOSFET array macro and (b) resistor macro. Decoder inputs are a1 – a5, and VCA and VCB are clamp voltages that reduce background currents from unselected DUTs. In (a) V1 – V8 are drain inputs and VGA and VGB are gate voltages. In (b) V1 –V6 are drive voltages and VO1 – VO6 are output voltages. In both macros multiple shared connections such as MOSFET source pads and decoder power supply pads are not shown.

Multiple array-units with shared decoder inputs and decoder power supplies are placed within one macro. The assembly of array-units in a macro is illustrated in Fig. 1(a) for MOSFETs and Fig. 1(b) for resistors. A MOSFET macro comprises 4 n-FET and 4 p-FET array-units while a resistor macro comprise 6 array-units. Each macro employs 25 I/O pads for testing on a standard DC parametric tester in the manufacturing line. The macro dimensions are 80 µm x 2500  $\mu m$  (or 2000  $\mu m$ ) including the 25, 60  $\mu m$  x 60  $\mu m$  (or 40 μm x 40 μm) pads. The designs are multi-port, allowing test of multiple arrays within a macro in parallel. For testing on a parallel tester with 100 or more channels, the macros may be stacked or assembled to share more pads, thereby increasing the test efficiency. Many macros with a standard template are generated by populating the array-units with different DUTs defined as parameterized cells. The DUTs may differ in device type, dimensions and layout style for Design for Manufacturing (DFM) or modeling applications. A number of identical DUTs are grouped within an array or across arrays within the same macro to get random statistical variations. The variations in a parameter mean of a group of identical DUTs across wafer, wafer-to-wafer and lot-to-lot give information related to systematic process variations.

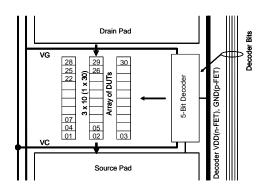

The physical layout of the MOSFET array-unit is indicated in Fig 2. The DUTs are arranged in a 3 x 10 matrix powered (drain to source) by interdigitated combs emanating from the adjacent I/O pads. The parasitic voltage drop is negligible just as for a discrete DUT placed between two pads. Vertical metal wires traverse a significant fraction of the macro height for shared decoder VDD (n-FET) and decoder GND (p-FET), decoder input bits and low current (< 1μA) DC voltage inputs to the DUTs. The decoder shares the DUT source pad, but draws only a few uA after settling from a selection transient, and does not impact DUT current measurements that are made on the drain side after the settling transient. The most challenging part of the design is the decoder which through subsequent circuitry sets gate voltages of all DUTs in the array. Wire cross-overs and much of the data-flow wiring is done in horizontal sections

Figure 2: Physical representation of an n-FET array-unit showing the DUT locations in the 3x10 matrix, the decoder, the nearby source and drain pads, and associated I/O wiring.

of the high resistance (silicided) polysilicon (poly) gate layer, while vertical metal wire segments are placed within split VDD and GND busses or adjacent to these busses. The decoder logic is implemented with inverters and two-way NAND gates comprised of single finger low-leakage devices. The gate poly is unidirectional and on a fixed pitch for both 45 nm and 32 nm technologies. In the case of 32 nm technology the metal-to-Si contacts are also gridded. The physical size of this highly customized decoder sets an upper limit of 5 decode input bits and 30 DUTs per array-unit. The remaining 2 of 32 decoder output signals are used to activate all DUTs in parallel under different bias conditions, facilitating background current correction.

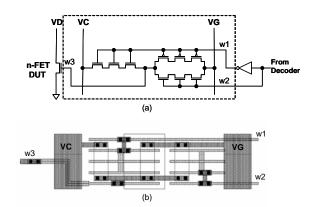

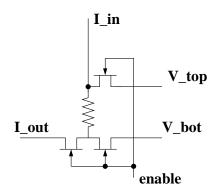

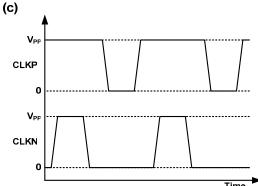

In the MOSFET array-unit, the outputs of the decoder feed directly into low leakage bias circuits that steer the appropriate voltages to the DUT gates [8], as shown in Figs. 3 for n-FET DUTs. The layout depicted in Fig. 3(b) exemplifies how the wiring is accomplished with a combination of one level of metal and silicided gate polysilicon. A voltage VG is applied to the gate of a selected n-FET while the gates of the other 29 n-FETs are biased at a clamp voltage VC. By setting VC at a small negative voltage, the leakage current of the unselected MOSFETs is greatly reduced, although this reduction is ultimately limited by Gate-Induced Drain Leakage, GIDL [13]. The drain-tosource leakage currents through the bias circuits are minimized by using groups of three pass-transistors in series rather than single pass-transistors. These currents are of some concern because they ultimately flow through the VG and VC supply lines and any voltage drop in the VG line would be directly reflected as an error in the VG applied to the DUTs. The same VG bus services four array-units and utilizes resistive poly underpasses to cross the VD busses evident in Fig. 2. By keeping the leakage currents low and taking care with the VG bus design, the VG bus voltage drop is kept below 1mV. The bias circuits shown in Fig. 3 are for n-FET DUTs where the negative clamp voltage VC is typically set at -0.1 to -0.2V. In the case of p-FET DUTs the

Figure 3: Low-leakage n-FET gate bias circuit. Voltage VG is applied to the selected gate and VC to the unselected gates.

bias circuits are configured differently (p-FET pass-transistors substituted for n-FET pass-transistors) to allow for a positive VC, which is typically set at 0.1 to 0.2V.

With an appropriate value of VC applied, the error in a drain-source current, Ids, measurement due to the background current from the unselected MOSFETs is negligible when the selected MOSFET is in the on-state. However, to get the selected MOSFET's Ids in the subthreshold region, a correction must be applied to the measured current. Two additional measurements are made to facilitate this correction. The I<sub>ds</sub> for all DUTs is measured in parallel with an applied gate-drain voltages of VC, I<sub>all VC</sub>, and with an applied gate-drain voltage of VG,  $I_{\text{all VG}}$  for all MOSFETs. For nominally identical DUTs, this correction, which is subtracted from the measured current, is 29/30\*  $I_{all\ VC}$ . For example, assuming the ratio  $I_{k\_VC}/I_{all\ VC}$  is < 0.1, where I<sub>k VC</sub> is the drain-source current of a selected DUT k with its gate at VC, this approach should give individual DUT current values with a maximum error of about 5% of the true values. The situation is more complicated if the DUTs are by design significantly different from each other. Let the true drain-source current flowing through selected DUT k with gate voltage VG be  $I_{k}$  VG, expressed as

$$I_{k\_VG} = (I_{k\_VG} - I_{k\_VC}) / (1 - \eta_k)$$

(1)

where  $\eta_k = I_{k\_VC}/I_{k\ VG}$ .

Because of the background current of the 29 unselected MOSFETs, neither  $I_{k\_VC}$  nor  $I_{k\_VG}$  can be directly measured. However, the difference  $(I_{k\_VG}-I_{k\_VC})$  is identically equal to the measured current difference  $(I_{k\_VG\_VC}-I_{all\_VC})$  where  $I_{k\_VG\_VC}$  is the measured  $I_{ds}$  of DUT k at VG, with the gates of all other 29 DUTs biased at VC. Furthermore, if all DUTs have identical I-V curves or more generally have similar slope in the sub-threshold region, then  $\eta_k=\eta_{all}=I_{all\_VC}/I_{all\_VG}$ . Under these conditions it then follows that  $I_{k\_VG}$  can be determined as

$$I_{k\_VG} = (I_{k\_VG\ VC} - I_{all\ VC}) / (1 - \eta_{all})$$

(2)

for all DUTs over the entire sub-threshold region, where the value of  $\eta_{all}$  must be determined for each value of VG.

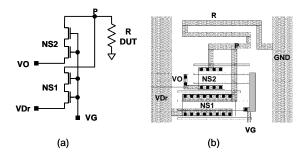

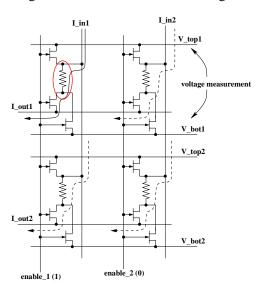

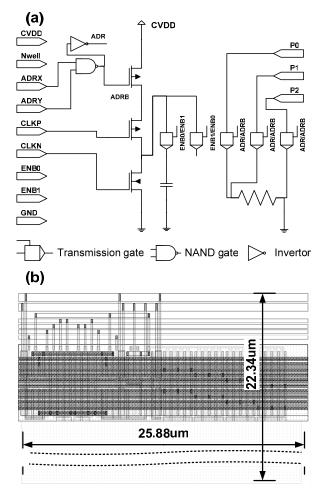

For resistance measurements, the array-unit is configured similar to the MOSFET array-unit with the DUTs arranged in a 3x10 matrix. Additional circuitry, shown in Fig. 4, for resistance measurements is also placed between the interdigitated drive (VDr) and GND fingers. The GND contact for all resistor DUTs is common and current is supplied via the VDr bus only to the decoder selected DUT through two series pass-transistors (NS1). Unselected DUTs are each isolated by their NS1 pass-transistors with gates at a negative clamp voltage, VC. The voltage VO across the selected DUT is read through two additional pass-transistors

(NS2) with the unselected DUTs isolated from the common VO output lead by their NS2 pass-transistors with gates also set at VC. In this three terminal measurement, a correction for the GND lead resistance can be determined by shorting DUT locations #1 and #30 to GND and assuming that this resistance increases linearly with DUT number.

Figure 4: (a) Circuit schematic (b) and physical layout showing resistor measurement scheme for a selected DUT consisting of a segment of wire between point P and GND.

# EXPERIMENTAL RESULTS AND DISCUSSION

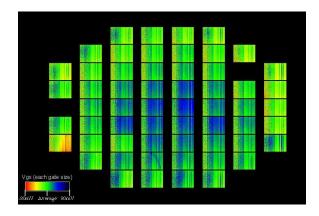

These array test structures are currently in use at IBM with 45 nm and 32 nm bulk and PD-SOI technologies. The validity of the macro designs was verified by simulations with full parasitic extraction. DUT sizes were selected to keep the maximum drain current to be measured  $< 1 \ \text{mA}.$  For 30 identical DUTs in an array-unit, the maximum simulated spread for an  $I_{\rm ds}$  value of 1 mA was 0.3 %. In the base macro design, arrays were populated with a variety of DUTs to check for any systematic variations across the array. Multiple copies of the macros were designed to cover different DUT types and configurations for DFM applications. Representative data are presented for experimental hardware in the 45 nm PD-SOI technology node to demonstrate measurement integrity.

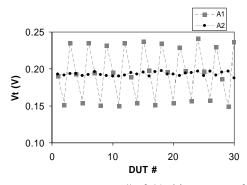

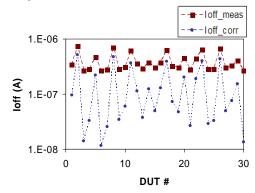

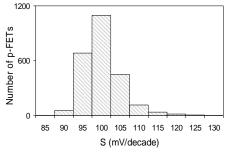

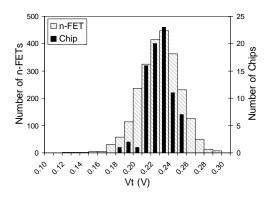

All measurements reported here were made on IBM's standard in-line Agilent 4073A parametric tester. For MOSFET measurements, VC was typically set at -0.2V for the n-FETs and +0.2V for the p-FETs. For a given drain voltage, the threshold voltage,  $V_t$  was determined as the gate voltage to achieve a fixed drain current equal to  $I_{sv}^*$  W/L where W and and L are MOSFET widths and channel-length respectively and  $I_{sv}$  is in the range of 20 nA to 300 nA. By measuring  $V_t$  at two different values of drain currents, the sub-threshold slope, S, was calculated as

$$S = (V_{t1} - V_{t2}) / Log_{10}(I_{t1}/I_{t2})$$

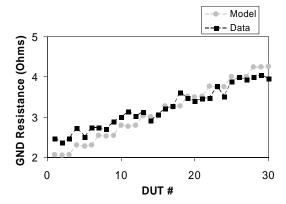

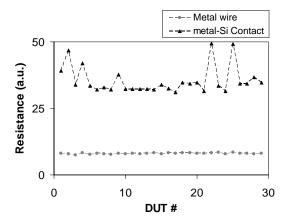

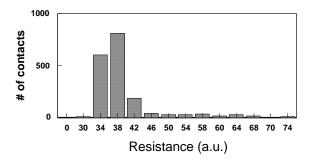

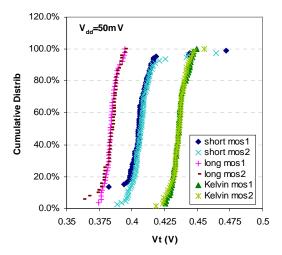

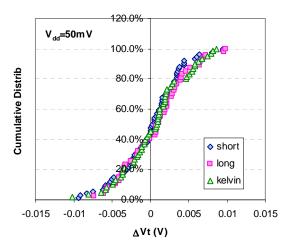

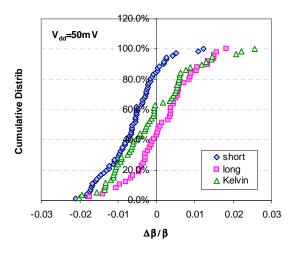

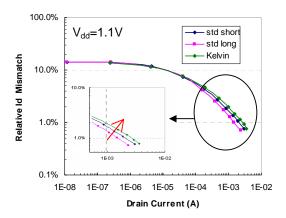

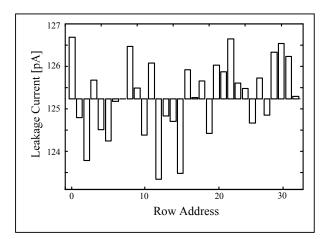

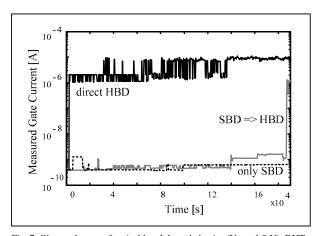

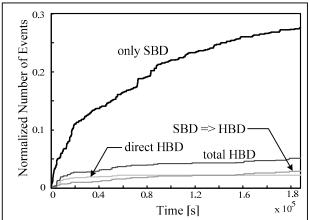

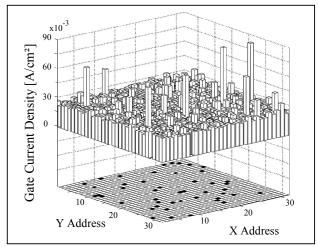

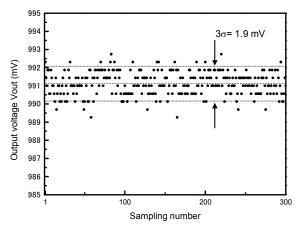

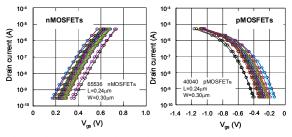

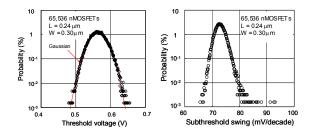

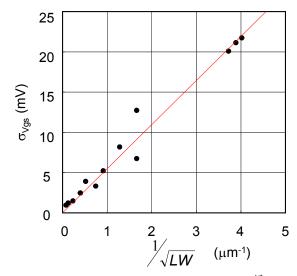

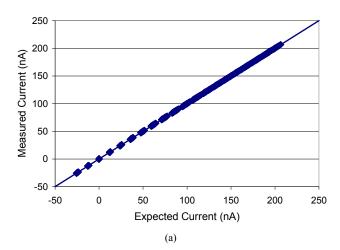

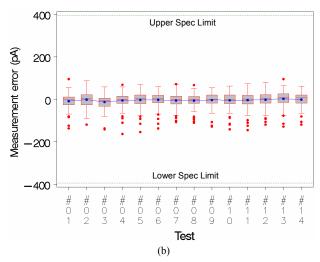

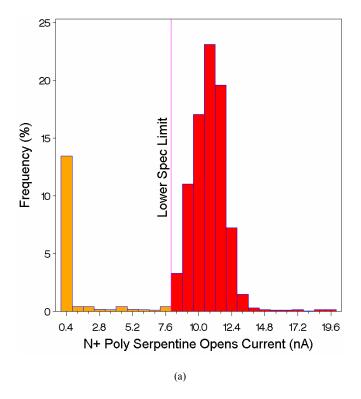

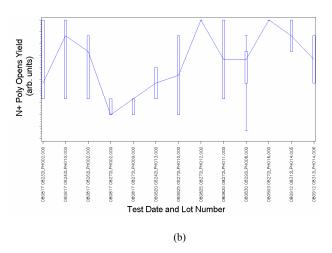

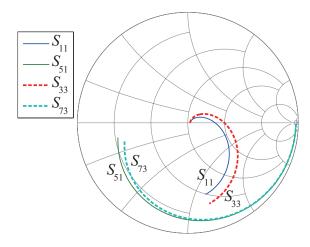

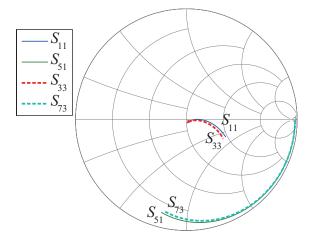

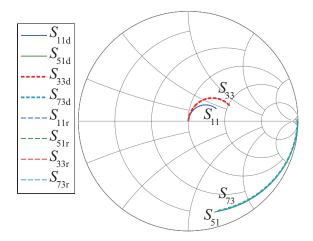

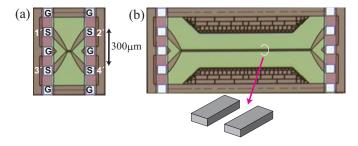

(3)