## T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

## 論文 / 著書情報 Article / Book Information

| 論題               |                                                                                                                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title            | Loss Reduction of Si Wire Waveguide Fabricated by Edge-<br>Enhancement Writing for Electron Beam Lithography and Reactive Ion<br>Etching Using Double Layered Resist Mask with C60 |

| 著者               | 井上 敬太, PLUMWONGROT DHANORM, 西山 伸彦, 阪本 真一, 榎本<br>晴基, 田村 茂雄, 丸山 武男, 荒井 滋久                                                                                                            |

| Authors          | Keita Inoue, Dhanorm Plumwongrot, Nobuhiko Nishiyama, Shinichi<br>Sakamoto, Haruki Enomoto, Shigeo Tamura, Takeo Maruyama,<br>Shigehisa Arai                                       |

| 出典               | , vol. 48, no. 3, p. 030208                                                                                                                                                        |

| Citation         | Jpn. J. Appl. Phys., vol. 48, no. 3, p. 030208                                                                                                                                     |

| 発行日 / Pub. date  | 2009, 3                                                                                                                                                                            |

| DOI              | http://dx.doi.org/10.1143/JJAP.48.030208                                                                                                                                           |

| URL              |                                                                                                                                                                                    |

| 権利情報 / Copyright | 本著作物の著作権は(公社)応用物理学会に帰属します。<br>(c) 2009 The Japan Society of Applied Physics                                                                                                        |

| Note             | このファイルは著者(最終)版です。<br>This file is author (final) version.                                                                                                                          |

## Loss Reduction of Si Wire Waveguide Fabricated by Edge-Enhancement Writing for Electron Beam Lithography and Reactive Ion Etching using Double layer Resist Mask with C<sub>60</sub>

Keita INOUE<sup>1</sup>, Dhanorm PLUMUWONGROT<sup>1</sup>, Nobuhiko NISHIYAMA<sup>1</sup>, Shinichi SAKAMOTO<sup>1</sup>, Haruki ENOMOTO<sup>1</sup>, Shigeo TAMURA<sup>3</sup>, Takeo MARUYAMA<sup>4</sup>, and Shigehisa ARAI<sup>2</sup>

<sup>1</sup>Dept. of Electrical and Electronic Engineering, Meguro-ku, Tokyo 152-8552, Japan

<sup>2</sup>Quantum Nanoelectronics Research Center, Tokyo Institute of Technology, Meguro-ku, Tokyo 152-8552, Japan

<sup>3</sup>Technical Department Tokyo Institute of Technology, Meguro-ku, Tokyo 152-8552, Japan

<sup>4</sup> School of Electrical and Computer Engineering, College of Science and Engineering, Kanazawa University Kakuma-machi, Kanazawa, Ishikawa 920-1192, Japan (Received ??? ??, 2008; accepted ???? ??, 2008; published online ???? ??, 2008)

Loss reduction methods of single-mode photonic wire in Silicon on Insulator have been investigated. with Si core  $200 \times 440$  nm size, fabricated with electron beam lithography and dry etching using double layer of EB resist mask. The propagation loss of TE mode measured at a wavelength of 1550 nm was 4.5 dB/cm, which is, to the best of our knowledge, the lowest value among the Si wire waveguides fabricated by parallel plate RIE method.

[DOI:

KEYWORDS: silicon photonics, reactive ion etching, electron beam lithography, silicon on insulator, fullerene(C<sub>60</sub>), line

edge roughness

A silicon on Insulator (SOI) substrate is of prime importance for optoelectronic integrated circuits as it offers potentiality for monolithic integration of optical and electronic functions on a single substrate<sup>1)</sup>. The silicon is transparent at wavelengths longer than 1.1 µm and can be used for waveguide at telecommunication wavelengths. A Si wire waveguide based on the SOI has the high refractive index difference between the silicon core (the refractive index is 3.45) and the buried oxide (BOX) layer (the refractive index is 1.44), inducing strong optical confinement in the silicon core layer. It allows to reduce the waveguide size to sub-micrometer to provide single-mode propagation at a wavelength of 1.55 um. Therefore, Si wire waveguides enable us to make smaller and high density optical circuits. In such narrow waveguides, a scattering loss due to sidewall roughness is severe. Therefore, fabrication processes providing very smooth surface as well as a high accuracy in lithography and etching are crucial. Recently Si wire waveguide with very low loss (1.7 dB/cm) and the bending radius of  $2\mu m$ with 0.01 dB/90° scattering loss have been realized using high density plasma etching such as inductivly coupled plasma (ICP) and electron cycrotron resonance (ECR)<sup>2),3)</sup>. However, there are not so many reports about the characteristics of Si wire waveguide by conventional parallel plate reactive ion etching (RIE) due to poor etching selectivity between photoresist and Si.

In this letter, we propose the fabrication method of Si wire waveguides using conventional parallel plate RIE and double layered EB resists containing  $C_{60}$ . Moreover, we introduced an edge enhancement writing method in the electron beam lithography (EBL) process to suppress the sidewall roughness of Si wire waveguides.

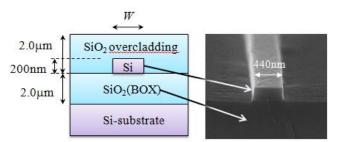

Figure 1 shows the cross sectional structure of the silicon wire waveguide fabricated on a SOI substrate. The BOX layer serves as an undercladding layer. An overcladding layer was 2- $\mu$ m-thick SiO<sub>2</sub> layer, which was deposited by plasma enhanced chemical vapor deposition (PECVD). A SOI wafer consists of 200 nm-thick surface Si layers and a 2- $\mu$ m-thick BOX layer, which is enough thick to prevent light leakage to the Si substrate side. The core size was 440 nm-wide and 200 nm-thick to provide the single-mode condition at the wavelength of 1.55 $\mu$ m.

The fabrication processes are the followings. After cleaning a SOI substrate by typical RCA solution <sup>4)</sup>, ZEP520 EB positive resist was spin coated at a speed of 2000 rpm. Then it was prebaked in an oven at 180 °C for 20 min followed by coating micro-composite of ZEP520 and  $C_{60}^{5}$  (10% weight), to be called ZEP- $C_{60}$  hereafter at 2000 rpm and baking on a hotplate at 200 °C for 2min. The thicknesses of ZEP 520 and ZEP-C<sub>60</sub> are 550 nm and 60 nm, respectively. EBL exposure was carried out with a JEOL JBX-5FE EBL system operating at 50 kV accelerating voltage and 100 pA beam current. The EB dosage was  $138\mu$ C/cm<sup>2</sup>. After the EB patterning, samples were developed in ZED-N50 developer, followed by rinsing in isopropyl alcohol (IPA). A magnetic stirrer was used to obtain a constant developing rate for good re-productivity<sup>6)</sup>. Next, Si waveguide was formed by RIE

Present address: Furukawa Electric Co. Ltd.

Present address: Fujikura Ltd.

<sup>\*</sup>E-mail address: inoue.k.aa@m.titech.ac.jp

with  $CF_4$  (gas pressure: 0.3 Pa, bias power: 20 W, gas flow: 10 sccm, etching time: 26 min). After removing the EB resist, a 2µm-thick SiO<sub>2</sub> layer was deposited by PCVD for coated Si wire waveguide.

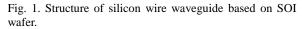

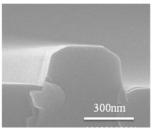

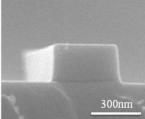

The cross sectional SEM view of the Si wire waveguide using ZEP520/ZEP-C<sub>60</sub> is shown in Fig.2 (b). For comparison, that by using ZEP520 resist is also shown in Fig. 2(a). The micro-composite ZEP520 resist due to C<sub>60</sub> molecules which act as a highly resistant agent <sup>7)-9)</sup>. Double layered resist could achieve a better anisotropic waveguide shape than that using single layered resist. When only ZEP-C<sub>60</sub> was used, several time spin coating and baking were needed to coat enough thickness and the bottom resist degraded due to over baking. Therefore, one conventional ZEP layer and one ZEP-C<sub>60</sub> is suit combination to obtain good waveguide shape.

(a) Single layer of ZEP100%

(b) Double layer of ZEP resists

Fig. 2. Cross sectional SEM images of Si waveguide shape using ZEP.

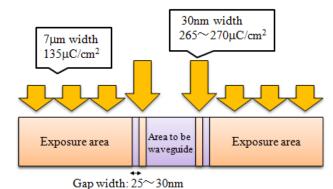

Fig. 3. The exposure design of edge enhancement writing for the reduction of sidewall roughness and proximity effects.

To achieve low optical loss in Si waveguides, reducing the sidewall roughness is the other important factor. We introduced edge enhancement writing EBL method. This method means that high exposure dose breaks up aggregates of resist polymer at the edge in order to reduce roughness of resist patterns, though inner area was dosed uniformly <sup>10),11</sup>. Figure 3 shows how the edge enhancement writing was carried out by our process. Exposure dose conditions were optimized at the pattern edge to obtain both the reduction of proximity effects and the reduction of sidewall roughness. The exposure dose of

fine lines along the pattern edges needed twice as much as that used for wide exposure of the inner area. Its dosage is  $266\mu$ C/cm<sup>2</sup> with the width of 30 nm. Moreover, we made non exposure gap between the edge writing and the inner exposure area to reduce influence of proximity effects. The gap width was around 25 nm as shown in Fig. 3 and it was actually gone after the development.

The top cross sectional SEM views of the resist patterns for conventional (uniform writing in inner area) and improvement (edge-enhancement writing) are shown in Fig. 4 (a) and (b), respectively. The sidewall roughness was measured by commercial critical dimension (CD) measurement software. The sidewall roughness ( $3\sigma$  value) of the resists was reduced from 8.4 nm to 4.8 nm by the improvement of the EBL. Figure 5 (a) and (b) show the top cross sectional SEM view of Si waveguide after CF<sub>4</sub>-RIE for these exposures, respectively. The sidewall roughness of the Si waveguides was reduced from 5.1 nm to 3.2 nm after the dry etching processes.

(a) conventional (b) edge enhanced Fig. 5. Si waveguide after CF<sub>4</sub>-RIE.

The reduction of propagation loss was expected by the reduction of sidewall roughness. The calculated scattering loss is smaller than 4.5 dB/cm with the measured  $3\sigma$  value of 3.2 nm for Si waveguide <sup>12), 13)</sup>.

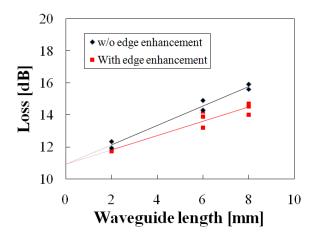

Figure 6 shows the measured propagation loss of the fabricated Si wire waveguides with the size of  $200 \times 440$  nm. The loss for TE mode was measured using Si wire waveguides of various lengths (2 mm, 6 mm, and 8 mm) at the wavelength of 1550 nm. A spherical lensed optical polarization maintaining fibers (PMF) with a 4.5 µm radius core size was used to couple the light from cleaved facets of the Si waveguide. The polarimeter and controller was used to control the polarization of the input light. As mentioned above, the side wall roughness of Si waveguide was reduced from 5.1 nm to 3.2 nm ( $3\sigma$  value)

by introducing the edge enhancement writing, and the propagation loss of Si waveguide was reduced from 6.0 dB/cm to 4.5 dB/cm for TE mode at 1550 nm as shown in Fig. 6. The propagation loss of the waveguide fabricated by using single ZEP520 layer (Fig. 2(a)) could not be measured because of its bad shape. As a result, we achieved the reduction of propagation loss due to reduction of sidewall roughness. As can be seen in Fig. 6, the coupling loss was around 11 dB of both facets, hence that between with the sample and the optical spherical lensed PMF was around 5.5 dB/facet for TE mode.

Fig. 6. Propagation loss and coupling loss of Si wire waveguide for TE mode at 1550nm using conventional writing and edge enhancement writing.

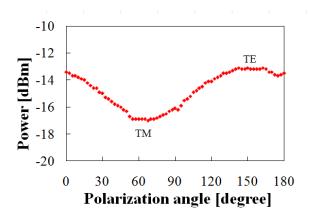

Fig. 7. The polarization characteristics of Si waveguide with  $200{\times}440$  nm core.

Figure 7 shows the polarization characteristic of Si waveguide of 6 mm length measured at 1550 nm. The polarization dependence of propagation loss was obtained due to difference of optical field distribution of TE/TM mode. The polarization characteristics show sinusoidal wave-like as shown in Fig. 7. TE/TM polarization dependent loss was about 4 dB.

In conclusion, the technique for coating the micro-composite ZEP520 resist with 10%  $C_{60}$  onto the ZEP520 resist is better for vertical shaping with  $CF_4$ -RIE. The propagation loss of the Si waveguide using the

double layer resist was measured to be 6.0 dB/cm at 1550 nm. Moreover, we achieved the reduction of the sidewall roughness of Si core using edge enhancement EBL method. The sidewall roughness was 3.2nm ( $3\sigma$  value) for Si core, and then the propagation loss of Si waveguide with  $200 \times 440$  nm was reduced to 4.5 dB/cm for TE mode at wavelength of 1550 nm. This is the lowest value of Si waveguide loss realized by parallel plate RIE etching and technologies proposed in this letter can be applicable to achieve other etching methods.

## Acknowledgments

We would like to thank Professor Emeritus Y. Suematsu and President K. Iga for continuous encouragement, and Professors T. Mizumoto, K. Furuya, M. Asada, Y. Miyamoto, M. Watanabe of the Tokyo Institute of Technology for fruitful discussions. This research was partially supported by Grants-in-Aid for Scientific Research (#19002009, #19760231) from the Ministry of Education, Culture, Sports, Science and Technology (MEXT), Japan. This research was also supported by Takahashi foundation.

- R. A. Soref and J. P. Lorenzo, *IEEE J. Quantum Electron.*, Vol. QE-22, No. 6, pp. 873-879, Jun. 1986.

- F. Xia, L. Sekaric, and Y. Vlasov, *Nature Photonics*, Vol.1, pp. 65-71, No. 1, Jan. 2007.

- Y. A. Vlasov and S. J. McNab, *Opt. Express.*, Vol. 12, No. 8, pp. 1622-1631, Apr. 2004.

- T. Ohmi, J. Electrochem. Soc., Vol. 143, No. 9, pp.2957-2964, Sep. 1996.

- T. Ishii, H. Nozawa, T. Tamamura, *Appl. Phys. Lett.*, Vol. 70, No. 9, pp. 1110-1112, Mar. 1997.

- D. Plumwongrot, Y. Nishimoto, S. M. Ullah, Y. Tamura, M. Kurokawa, T. Maruyama, N. Nishiyama and S. Arai, *Jpn. J. Appl. Phys.*, vol. 46, no. 45, pp. L1090-L1092, Nov. 2007.

- T. Ishii, Y. Murata, K. Shigehara, *Jpn. J. Appl. Phys.*, Vol. 40, No. 5A, pp. L478-L480, May. 2001.

- T. Ishii, T. Tamamura, K. Shigehara, *Jpn. J. Appl. Phys.*, Vol. 39, No. 15, pp. L1068-L1070, Part 2, Oct. 2001.

- T. Yamaguchi, K. Yamazaki, M. Nagase, H. Namatsu, *Jpn. J. Appl. Phys.*, Vol. 42, No. 6B, pp. 3755-3762, June. 2003.

- 10) K. Yamazaki, T. Yamaguchi, H. Namatsu, Jpn. J. Appl. Phys., Vol. 42, No.6B, pp. 3833-3837, June. 2003.

- F. P. Pyne, J. P. R. Lancey, *Optical and Quantum Electronics*, Vol. 26, No. 10, pp. 977-986, Oct. 1994.

- 12) F. Ladouceur, J. D. Love, T. J. Senden, *IEE. Proc.-Optoelectron.*, Vol. 141, No. 4, pp. 242-248, Aug. 1994.

- 13) F. Grillot, L. Vivien, S. Lavel, D. Pascal, E. Cassan, *IEEE Photon. Technol. Lett.*, Vol. 16, No. 7, pp. 1661-1663, Jul. 2004.