# T2R2 東京工業大学リサーチリポジトリ

## Tokyo Tech Research Repository

## 論文 / 著書情報 Article / Book Information

| 題目(和文)            | <br>  誘電体/半導体と半導体へテロ接合界面における界面トラップおよび界<br>  面近傍のバルクトラップに関する研究                                                                                                                                     |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | A study on interface traps and near interfacial bulk traps at the interfaces of dielectric/semiconductor and semiconductor heterojunction                                                         |

| 著者(和文)            | 竇 春萌                                                                                                                                                                                              |

| Author(English)   | Chunmeng Dou                                                                                                                                                                                      |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第9533号,<br>授与年月日:2014年3月26日,<br>学位の種別:課程博士,<br>審査員:岩井 洋,名取 研二,片岡 好則,筒井 一生,若林 整,杉井<br>信之,西山 彰,角嶋 邦之,Yi Shi,Liu Ming                                          |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第9533号,<br>Conferred date:2014/3/26,<br>Degree Type:Course doctor,<br>Examiner:,,,,,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                              |

| Type(English)     | Doctoral Thesis                                                                                                                                                                                   |

### **Doctoral Thesis**

A study on interface traps and near interfacial bulk traps at the interfaces of dielectric/semiconductor and semiconductor heterojunction

誘電体/半導体と半導体へテロ接合界面における界面トラップおよび 界面近傍のバルクトラップに関する研究

by

### Chunmeng Dou

Supervisor: Prof. Hiroshi Iwai,

Co-supervisor: Associate Prof. Kuniyuki Kakushima

A dissertation submitted to

Department of Electronics and Applied Physics,

Interdisciplinary Graduate School of Science and Engineering,

Tokyo Institute of Technology

for the degree of doctor of engineering

Spring, 2014

## Acknowledgements

First and foremost, I would like to express deepest gratitude to my advisor Prof. Hiroshi Iwai from Tokyo Institute of Technology (TIT) for all of his dedicated guidance and attentive support on my studies and life. He also provides me many invaluable chances for participating research program in world-leading universities/institutes outside TIT, which greatly broaden my horizon and deepen my interest on my research field.

I am also deeply indebted to Associate Prof. Kuniyuki Kakushima of TIT, who intelligently and patiently guides me to overcome many crucial challenges in my laboratory studies and daily life through my Ph.D. journey.

Likewise, I am very grateful to Prof. Takeo Hattori, Prof. Kenji Natori, Prof. Kazuo Tsutsui, Prof. Hiroshi Wakabayashi, Prof. Nobuyuki Sugii, Prof. Akira Nishiyama, Prof. Yoshinori Kataoka, and Prof. Parhat Ahmet from TIT for their tireless mentoring and valuable advices.

Besides, I sincerely acknowledge Prof. Keisaku Yamada, Prof. Kenji Ohmori, Prof. Masaaki Niwa, and Dr. Wei Feng from Tsukuba University for their strong guidance on fabrication and characterization multi-gate MOSFETs devices after I joined the Tsukuba Nanotechnology Human Resource Development Program (honors graduate program), Tsukuba University.

Additionally, I would like to express my appreciation to Prof. Guido Groeseneken, Dr. Aaron Thean, Dr. Dennis Lin from IMEC and Prof. Yuan Taur from University of California, San Diego, for their cordial guidance on characterizing the oxide traps in III-V MOS capacitors during my intern at IMEC. I also indebted to many members of the LDD team of IMEC for many fruitful discussions and kind assistance.

I also significantly benefited from the kindest help from Ms. Akiko Matsumoto and Ms.

Masako Nishizawa from Iwai/Kakushima laboratories, Prof. Yogaku Iwamoto, and Ms. Yumiko Yuzawa from the Innovative Platform for Education and Research (IPER) of TIT, Prof. Kikuo Yamabe, Prof. Kiyoshi Asakawa, Prof. Yasuhiro Horiike, Ms. Namiko Suzuki, Ms. Midori Hirano, and Mr. Masaya Oouchi from the honors graduate program of Tsukuba University. Due to their kind arrangements, I could conduct my studies smoothly at TIT and Tsukuba University, and also participate in an intern at IMEC. I would also like to thank Dr. Daniel Berrar from IPER of TIT for proofreading my journal publications.

I would also like to express my deep gratitude to all of other research staff and student members in Iwai/Kakushima Lab for their help from many aspects, and I will always recall my time at Japan with fondness.

I would also like to gratefully appreciate Prof. Ming Liu (The Institute of Microelectronics of Chinese Academy of Sciences), Prof. Yi Shi (Nanjing University), Prof. Zhenchao Dong (University of Science and Technology of China), Prof. Hei Wong (City University of Hong Kong), for evaluating the qualification of this thesis and their valuable advices.

Lastly, many thanks to my parents and all of my family members for their constant support and firm encouragement.

### Abstract

In order to avoid CMOS down-scaling limit due to the short-channel effect, multi-gate structure, such as fin-FETs or Tri-gate has been introduced. In addition, MOSFETs with new channel materials such as InGaAs (III-V) and Ge are studied for low power application under low voltage. Also, HEMT (High Electron Mobility Transistor) devices using AlGaN/GaN hetero-junction for the channel are being developed for power and high-frequency applications.

For the development of these emerging device technologies, it is important to accurately evaluate the distribution of interface and near-interface traps at the gate dielectrics/semiconductor interfaces and the semiconductor hetero-junction interfaces and thus, to understand the behavior of those traps. In this thesis, the results of the systematic studies for the distribution of interface and near-nterface traps at SiO<sub>2</sub>/Si interfaces with fin structure, high-k/InGaAs interfaces, and AlGaN/GaN hetero-interfaces are described. We have proposed methodologies for trap characterization and revealed in-depth understanding of the distributions, origins, species, and trapping mechanisms. These methodologies and discoveries can be also easily extended for studying other dielectric/semiconductor interfaces and semiconductor hetero-interfaces, and thus provide a guideline for trap characterization for future development of advanced FETs.

In particular, following characterizing methodologies were proposed: (1) extraction of trap densities in the different regions of fin surface by the measurement of trap densities with different fin width, (2) extraction of near-interface traps (or border traps) for high-k/III-V MOS structures, from the C-V characteristics measured at different temperatures, and (3) extraction of the distribution and species of the interface traps by comparative study on conductance spectra of AlGaN/GaN hetero-junctions with different electrodes.

The major results are listed as follows; At the SiO<sub>2</sub>/Si interface with fin structure, a high concentration of interface traps tend to locate at the corners. In high-k/III-V MOS systems, there are a large amount of electrically active oxide border traps, whose concentration is likely to increase with increasing energy level and distance from the interface into the oxide. These traps seem to be caused by accumulated defectives during high-k material growth. Besides, the trapping process of oxide border traps is found to be caused by thermal activation. At last, for AlGaN/GaN hetero-interfaces, it is confirmed that there are no distributed bulk traps in the near interfacial region of the hetero-interface. Besides, the different properties of deep trap levels and shallow trap levels at the hetero-interface are also presented.

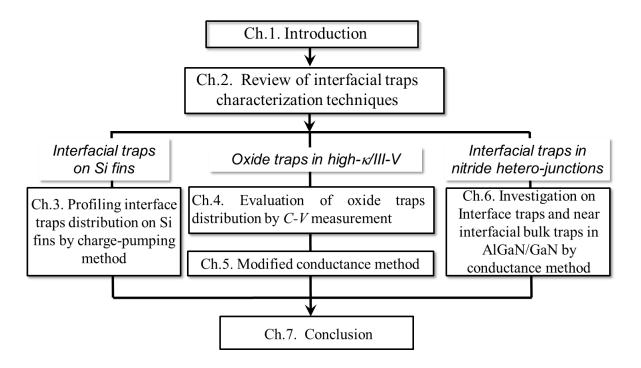

## Table of Contents

| Acknowledgements                                                                          | i    |

|-------------------------------------------------------------------------------------------|------|

| Abstract                                                                                  | iii  |

| Table of Contents                                                                         | iv   |

| Symbols and Abbreviation                                                                  | vii  |

| List of figures                                                                           | xii  |

| List of Tables                                                                            | xxii |

| Chapter 1: Introduction                                                                   | 1    |

| 1.1 Moore's law and Dennard Scaling                                                       | 2    |

| 1.1.1 Moore's law – history and current status                                            | 2    |

| 1.1.2 Dennard scaling law and its challenges                                              | 3    |

| 1.2 Overcoming the challenges faced by CMOS scaling                                       | 13   |

| 1.2.1 "More Moore" and "More than Moore"                                                  | 13   |

| 1.2.2 Multi-gate FETs for gate-to-channel electrostatic control                           | 15   |

| 1.2.3 High-k/Metal gate for EOT scaling                                                   | 18   |

| 1.2.4 III-V/Ge based FETs for mobility boosting                                           | 19   |

| 1.2.5 AlGaN/GaN based HEMT for high-frequency, high-power application                     | 22   |

| 1.3 Interface traps and near interfacial bulk traps: origin, properties and influences    | 26   |

| 1.3.1 Interface traps at dielectric/semiconductor interface                               | 27   |

| 1.3.2 Near interfacial oxide traps: emerging issues in MOS device with high mobility su   |      |

| 1.3.3 Interface and near interface traps in semiconductor hetero-junction                 | 35   |

| 1.4 Purpose and Organization of this study                                                | 37   |

| References                                                                                | 41   |

| Chapter 2: Review of the techniques for characterizing interface and near interface traps | 47   |

| 2.1 Admittance analysis for interfacial traps chracterization                             | 48   |

| 2.1.1 Low-frequency capacitance method                                                    |      |

| 2.1.2 High-frequency capacitance method                                                   |      |

| 2.1.3 Conductance method                                                                  |      |

| 2.2 Charge-pumping (CP) method for interfacial traps characterization                        | 8 |

|----------------------------------------------------------------------------------------------|---|

| 2.3 Comparison between different interfacial traps characterization techniques               | 1 |

| References 6                                                                                 | 3 |

| Chapter 3: Study of Interface traps at the surfaces of Si fins by charge-pumping method 6    | 5 |

| 3.1 Introduction                                                                             | 6 |

| 3.2 Experiments6                                                                             | 7 |

| 3.3 Results and Discussion                                                                   | 1 |

| 3.3.1 Extraction of the optimal forming gas annealing temperature                            | 1 |

| 3.3.2 Spatial distribution of the interface traps on the 3D surfaces of the Si fins          | 3 |

| 3.4 Conclusion                                                                               | 7 |

| References                                                                                   | 8 |

| Chapter 4: Study of oxide border traps in high-k/InGaAs MOS capacitor by C-V measurement 8   | 1 |

| 4.1 Introduction                                                                             | 2 |

| 4.2 Sample preparation8                                                                      | 4 |

| 4.3 Model description                                                                        | 6 |

| 4.4 Results and discussion9                                                                  | 2 |

| 4.4.1 Temperature and frequency dependence of C-V in accumulation region9                    | 2 |

| 4.4.2 Methodology for extracting the border traps distribution in energy and space9          | 6 |

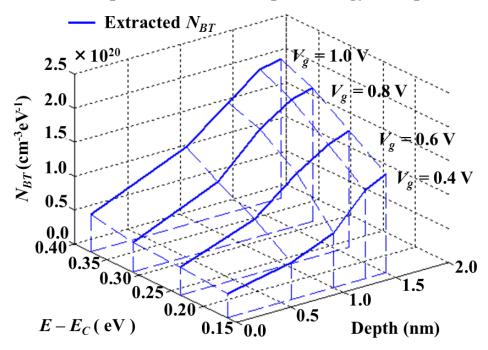

| 4.4.3 Distribution profile of border traps in energy and space                               | 3 |

| 4.5 Conclusion                                                                               | 5 |

| References                                                                                   | 6 |

| Chapter 5: Study of oxide border traps and interface traps in high-k/InGaAs MOS capacitor by |   |

| conductance method                                                                           | 0 |

| 5.1 Introduction                                                                             | 1 |

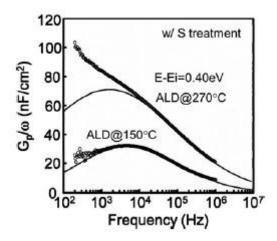

| 5.2 Sample preparation                                                                       | 3 |

| 5.3 Temperature dependent responses of interface and oxide traps                             | 4 |

| 5.4 Modified conductance method with consideration of oxide traps                            | 8 |

| 5.4.1 High temperature capacitance and conductance behaviors                                 | 8 |

| 5.4.2 Extraction of $D_{it}$ and $N_{bt}$ from $G_p/w$ versus $w$ plot                       | 0 |

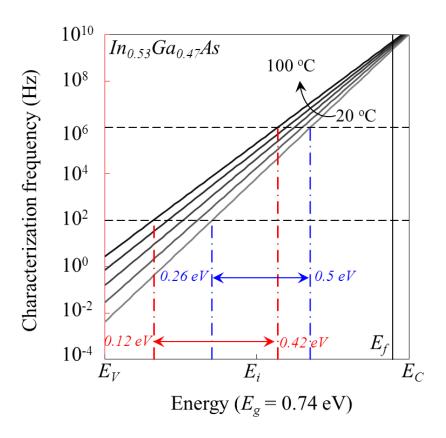

| 5.4.3 Determination of the energy level                                                      | 2 |

| 5.5 Conclusion                                                                                                                                           | 124   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| References                                                                                                                                               | 125   |

| Chapter 6: Study of interface traps and near interfacial bulk traps in AlGaN/GaN heterojunction conductance method                                       |       |

| 6.1 Introduction                                                                                                                                         | 128   |

| 6.2 Device structure                                                                                                                                     | 130   |

| 6.3 Results and Discussion                                                                                                                               | 131   |

| 6.3.1. Conductance analysis in depletion and inversion region                                                                                            | 132   |

| 6.3.2. Model of traps distribution in AlGaN/GaN heterojunction                                                                                           | 134   |

| 6.4. Conclusion                                                                                                                                          | 136   |

| References                                                                                                                                               | 137   |

| Chapter 7: Conclusion                                                                                                                                    | 139   |

| 7.1: Summary of this thesis                                                                                                                              | 139   |

| 7.2. Future work                                                                                                                                         | 142   |

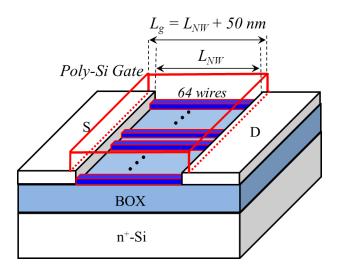

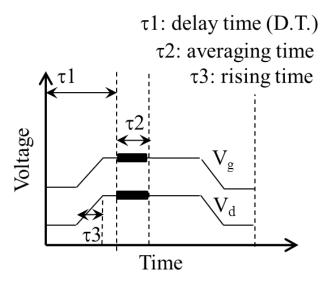

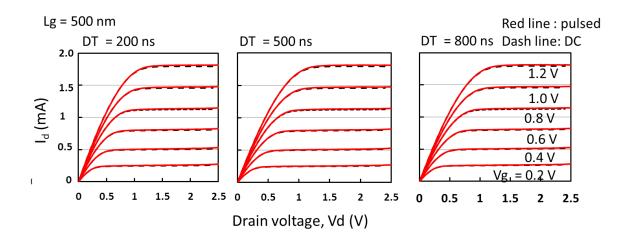

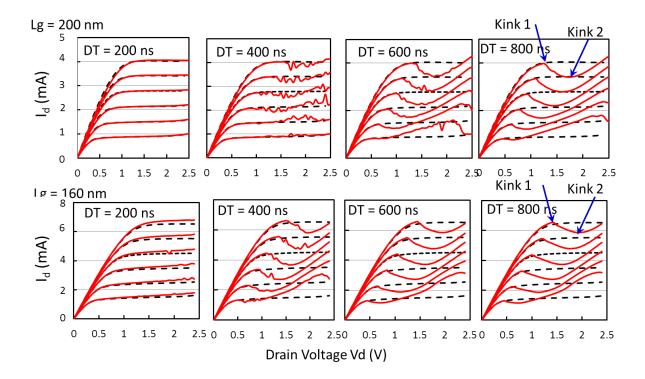

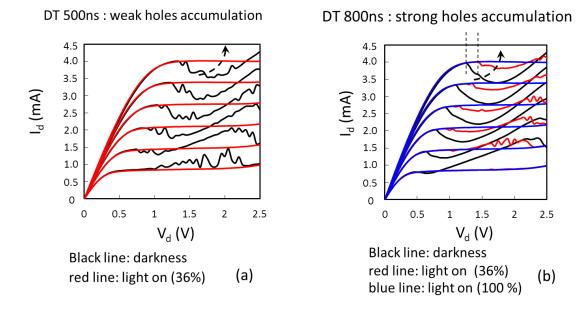

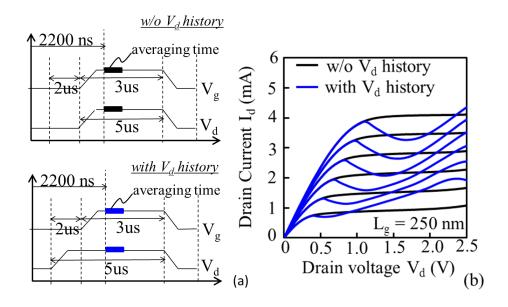

| Appendix A: Anomalies in <i>I-V</i> characteristics of multiple Si nanowire FET under pulse measurement                                                  | . 143 |

| A1 Introduction:                                                                                                                                         | 143   |

| A2 Experiment:                                                                                                                                           | 143   |

| A3 Results and discussion:                                                                                                                               | 145   |

| A4 Conclusion:                                                                                                                                           | 148   |

| Reference                                                                                                                                                | 149   |

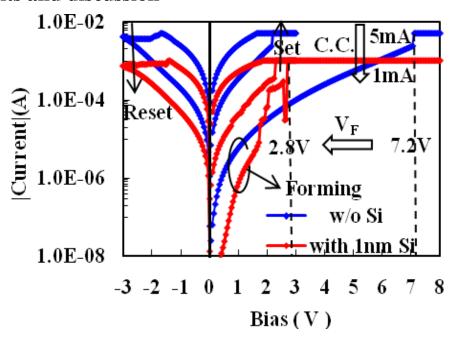

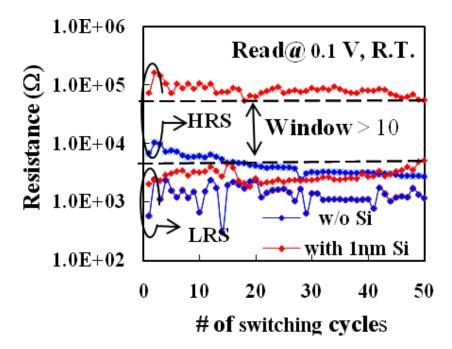

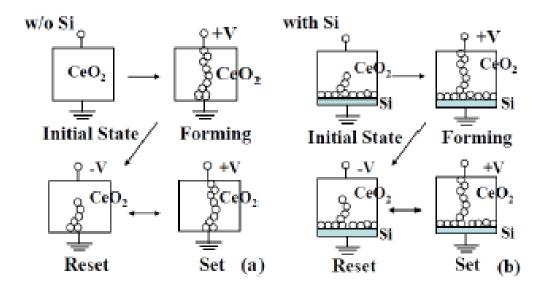

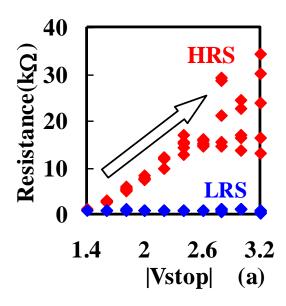

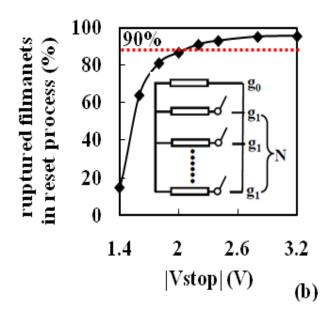

| Appendix B: Modulation of the resistive switching behaviors of the CeO <sub>2</sub> based metal-insulator metal (MIM) structure by interface engineering |       |

| B1 Introduction                                                                                                                                          | 151   |

| B2 Experiments                                                                                                                                           | 152   |

| B3 Results and discussion                                                                                                                                | 153   |

| B4 Conclusion                                                                                                                                            | 159   |

| References                                                                                                                                               | 160   |

| Publications list                                                                                                                                        | 162   |

## Symbols and Abbreviation

## A

ALD, atomic layer deposition

AC, alternating current

### B

BT, border traps or near interfacial bulk traps

## $\mathbf{C}$

CMOS, complementary metal-oxide-semiconductor

CP method, charge-pumping method

C, capacitance

$C_b$ , barrier layer capacitance

$C_m$ , measured capacitance

$C_s$ , substrate capacitance

$C_{ox}$ , oxide capacitance

$C_{it}$ , interface traps induced capacitance

$C_{tot}$ , total capacitance

$C_g$ , gate capacitance

## D or $\Delta$

DIBL, drain induced barrier lowering

D.O.S., density of states

$D_{it}$ , density of interface states

$D_{it,top}$ , density of interface states at the top wall of the fin structure

$D_{it,side,}$  density of interface states at the sidewall of the fin structure

$D_{it,corner}$ , density of interface states at the corner of the fin structure

$\Delta C_{bt}$ , incremental oxide border traps capacitance

$\Delta G_{bt}$ , incremental oxide border traps conductance

## $\mathbf{E}$

$E_C$ , conduction band edge

$E_V$ , valence band edge

$E_f$ , Fermi energy level

$E_T$ , Trap energy level

## F

FET, field-effect transistor

*f*, frequency

## G

G, conductance

$G_m$ , measured conductance

$G_p$ , parallel conductance

## H or $\hbar$

High-k, high dielectric constant

$H_{fin}$ , height of the fin structure

H.F., high frequency

$\hbar$  , reduced plank constant

### I

$I_{ON}$ , on-state current

$I_{OFF}$ , off-state current

$I_{leak}$ , leakage current

$I_{CP}$ , charge-pumping current

### K

k. Boltzmann constant

$\kappa$ , tunneling decay factor

## L

L.T., low temperature

L.F., low frequency

## $\mathbf{M}$

MOS, metal-oxide-semiconductor

MOSFET, metal-oxide-semiconductor field-effect transistor

## N

$N_C$ , density of state in the conduction band

$N_V$ , density of state in the valence band

$N_d$ , donor impurity density

$N_a$ , acceptor impurity density

$n_s$ , carrier density at the semiconductor surface

$N_{bt}$ , volume density of oxide border traps

## P

$P_{dynamic}$ , dynamic power consumption

$P_{static}$ , static power consumption

$P_{SP}$ , spontaneous polarization

$P_{PE}$ , piezo-electric polarization

## Q

#### q, element charge

## S or $\sigma$

S.S., subthreshold slope

SCE, short channel effect

SOI, silicon-on-insulator

$\sigma_{n,p}$ , capture cross-section of electrons/holes

$\sigma_s$ , surface potential parameters

## T or $\tau$

T, temperature

$t_{ox}$ , oxide thickness

$\tau_{it}$  or  $\tau_0$ , the time constant of the interface trap

$\tau_{bt}$ , the time constant of the border trap

## $\mathbf{V}$

V, voltage

$V_{dd}$ , supply voltage

$V_g$ , gate voltage

$V_{th}$ , threshold voltage

$v_{th}$ , thermal velocity

## W or w

$W_{fin}$ , width of the fin structure

W, angular frequency

## X

$X_P$ , probing depth

$X_{P, max/min}$ , maximum or minimum probing depth

## List of figures

#### Chapter 1:

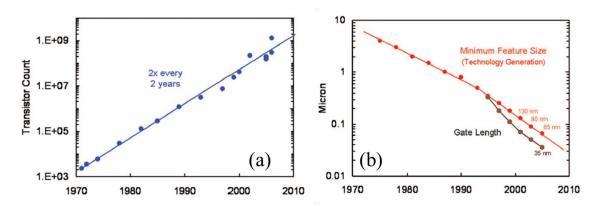

- **Fig. 1.1** The evolution of total transistor count on a chip (a) and the feature size of logic technology (b) of Intel microprocessors [1.4]

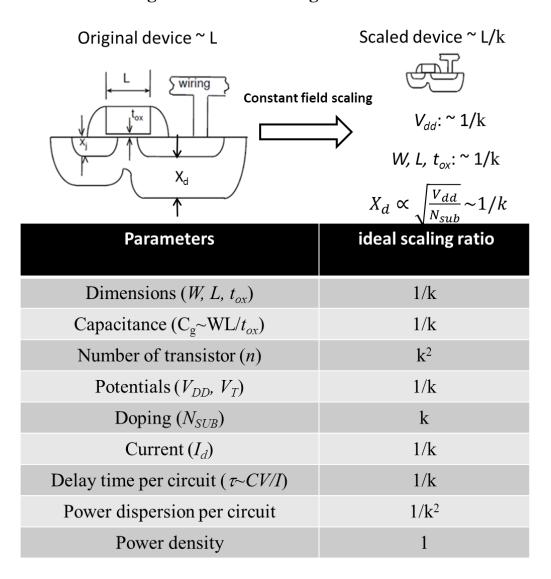

- Fig.1.2 Illustration of the constant-field scaling theory of MOSFET proposed by Dennard et al. in 1974 [1.5]

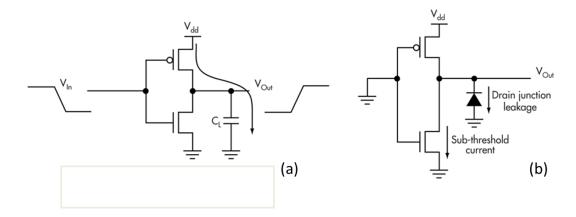

- Fig. 1.3 Illustration of the main origin of the dynamic power (a) and the static power (b) of a CMOS invertor.

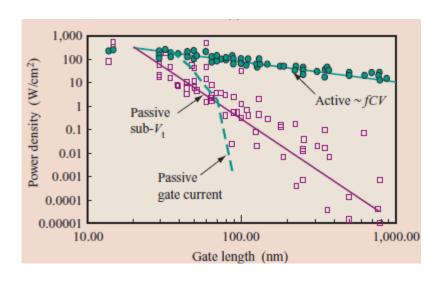

- Fig. 1.4 Evolution of the power density of CMOS circuits as a function of gate length [1.7]

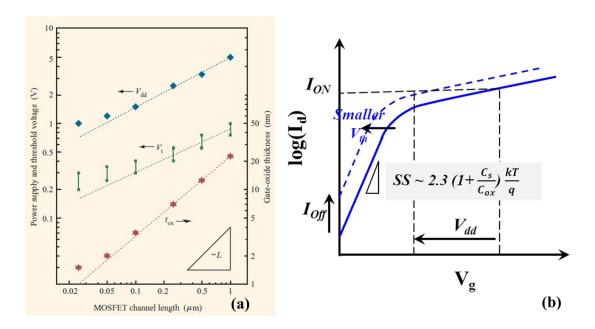

- Fig. 1.5 (a) Power-supply voltage  $(V_{dd})$ , threshold voltage  $(V_{th})$  and gate-oixde thickness  $(t_{ox})$  as a function of channel length for CMOS logic technologies [1.9], and (b) schematic drain current-gate voltage  $(I_d-V_g)$  relationships with different  $V_{dd}$  and  $V_{th}$  with illustration of the increased off-state current  $(I_{off})$  after  $V_{dd}$  or  $V_{th}$  scaling.

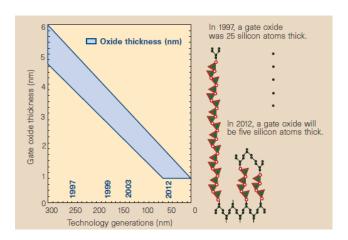

- **Fig. 1.6** (a) The road map for scaling of the gate oxide predicted by the semiconductor Industry Association (SIA), USA, in 1997 [1.10], and (b) Schematic of the evolution of the SiO<sub>2</sub> gate oxide [1.11].

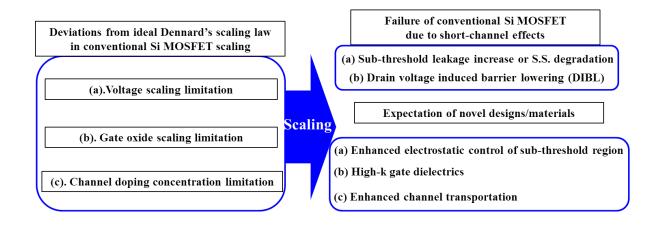

- Fig. 1.7 Illustration of the deviations from ideal Dennard's scaling law in scaling the conventional Si MOSFETs and their influences: conventional Si MOSFET will finally fail as scaling continues due to the short channel effects and novel design/materials are expected.

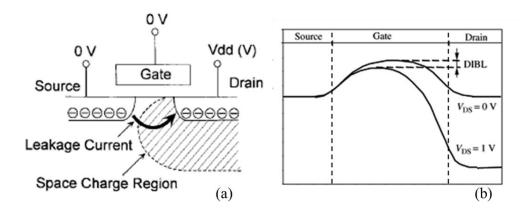

- Fig.1.8 Short channel effects in n-MOSFETs: (a) Schematics of the leakage current in sub-threshold region, [1.1] and (b) the band diagram of source/channel/drain with illustration of the drain induced barrier lowering (DIBL) effect.

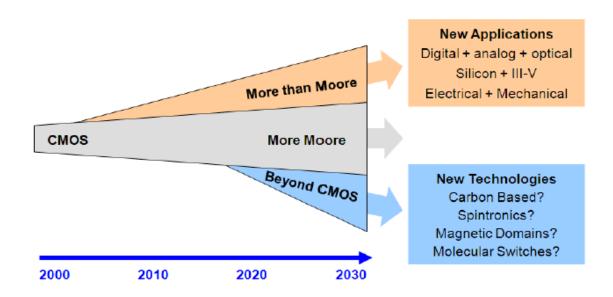

- **Fig. 1.9** Future technology directions, including "More Moore", "More than Moore", and "Beyond CMOS", to further improve the performance of LSIs. [1.12]

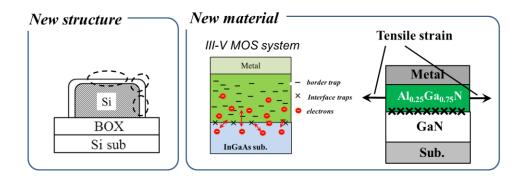

- Fig. 1.10 Representative new structure/material technology for novel field-effect

- transistors to continue CMOS scaling and diversify functionality.

- **Fig. 1.11** Structure and technology innovation for MOSFET [1.2].

- **Fig. 1.12** Enhanced electrostatic gate control of the channel can be achieved by adopting 3-D channel with multi-gate structure.[1.14]

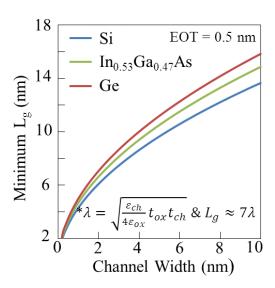

- **Fig. 1.13** Evaluated minimum gate length as a function of channel width for a gate-all-around MOSFET with Si, In<sub>0.53</sub>Ga<sub>0.47</sub>As, Ge channel.

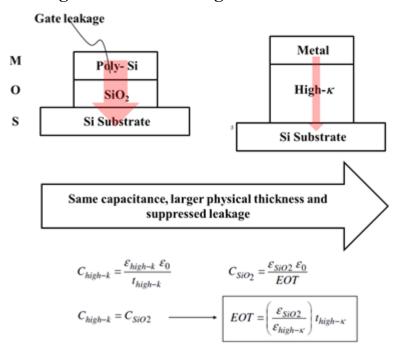

- Fig. 1.14 Illustration of (1) replacement of SiO<sub>2</sub>/poly-Si gate stack with high-k/metal electrode to achieve same capacitance with suppressed gate leakage, and (2) the concept of the equivalent oxide thickness (EOT) of the high-k dielectrics. Here,  $C_{high-k}$  and  $C_{SiO2}$  are the capacitance values of the high-k and SiO<sub>2</sub> MOS capacitors, respectively.  $t_{high-k}$  is the physical thickness of the high-k.  $\varepsilon_{high-k}$  and  $\varepsilon_{SiO2}$  are the relative permittivity, and  $\varepsilon_{O}$  is the vacuum permittivity.

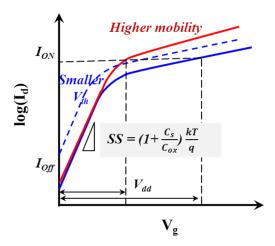

- Fig. 1.15 Schematic illustration of the necessity of adopting the high mobility channel for lowering the supply voltage without degrading the requirement for on- and off-current ( $I_{ON}$  and  $I_{OFF}$ ). The blue line shows typical  $I_d$ - $V_g$  of an MOSFET, the dash line shows the one of the device with decreased  $V_{th}$  and the red line shows the one of the device with high mobility in the channel.

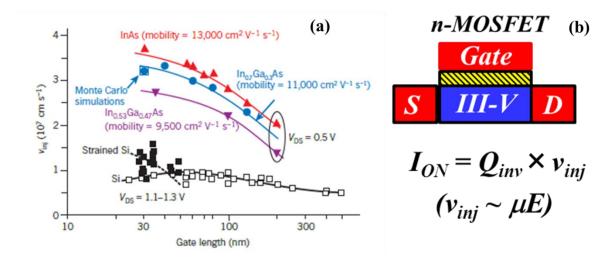

- **Fig. 1.16** (a) Comparison of the electron injection velocity  $(v_{inj})$  at different gate lengths in Si channel and III-V channel. After J.A.del Alamo, et al. [1.20], and (b) schematic image of the III-V based MOSFET with illustration the relationship between on  $I_{on}$  and  $v_{inj}$ .

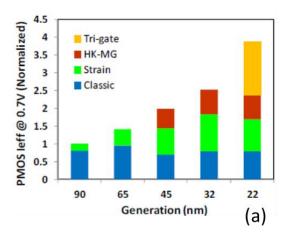

- **Fig. 1.17** (a)The improved performance of the p-MOSFET as the generation of the technology node evolves is achieved by implementation of new materials and architecture in past technology node.[1.22] and (b) the component of the ultimate CMOS device.[1.22]

- **Fig. 1.18** (a) The structure of the heterojunction structure used to constitute the field-effect transistor, and (b) The schematic band diagram of the GaAs/n-Al<sub>x</sub>Ga<sub>1-x</sub>As heterojunction with the illustration of the formation of the tow-dimensional electron gas, adopted from [1.24]

- **Fig. 1.19** Schematic drawing of the crystal structure of Ga-face GaN. [1.27]

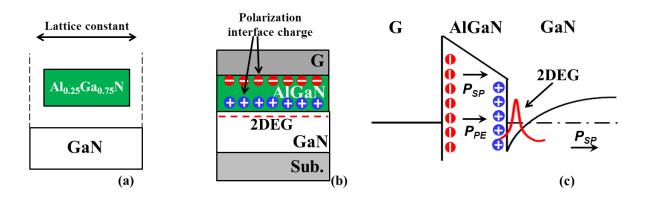

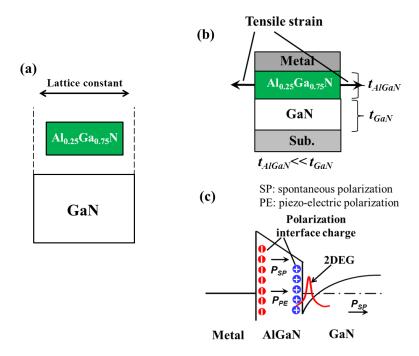

- (a) Schematic illustration of the lattice mismatch between AlGaN and GaN, (b) Schematic drawing of the polarization interface charge and the 2DEG in AlGaN/GaN heterojunction, and (c) band diagram of the AlGaN/GaN heterostructure with the illustration of polarization interface charge induced by spontaneous and piezoelectric polarization and the 2DEG formed in the quantum well at the interface between AlGaN and GaN.

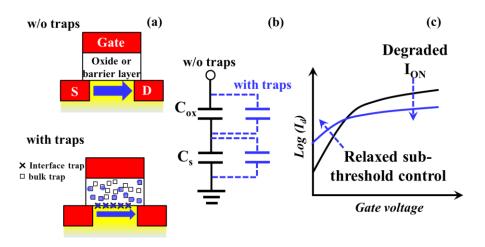

- **Fig. 1.21** (a) Illustration of the spatial distribution of interface traps and near interfacial bulk traps in MOSFETs, (b) Extremely simplified equivalent circuit to clarify the influence of interface traps and near interfacial bulk traps, and (c) Schematic comparison between the  $I_d$ - $V_g$  characteristics of the MOSFETs with and without traps in the gate stacks.

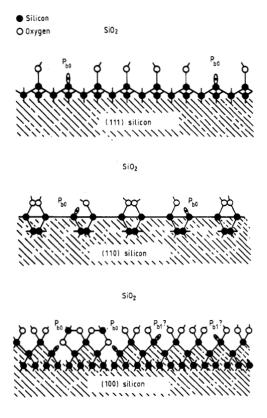

- Fig. 1.22 Structure of  $P_b$  centers on Si wafers of three major orientations. [1.30, 1.31]

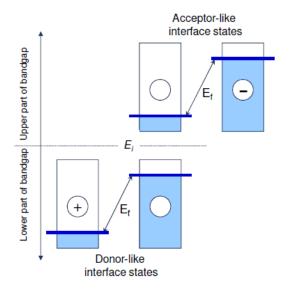

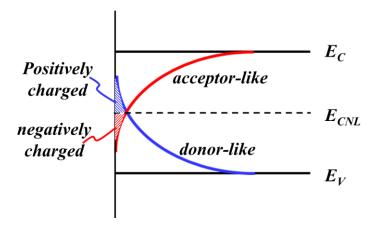

- **Fig. 1.23** The charge states of the donor-like interface states and the acceptor-like interface states blow and above the Fermi-level.

- **Fig. 1.24** Illustration of the charge neutrality level (CNL). The amount of the donor-like traps above the CNL is equal to the amount of the acceptor-like traps below the CNL.

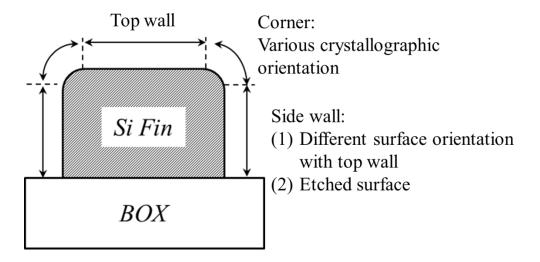

- Fig. 1.25 Schematic cross-sectional view of a Tri-gate Si MOSFET with rectangular-like cross-section shape formed. The possible origins of additional  $D_{it}$  compared the 3D surface to conventional planar ones are also listed.

- Fig. 1.26 The energy alignment of the CNL with the band edges of the representative semiconductors at MOS interfaces.[1.36]

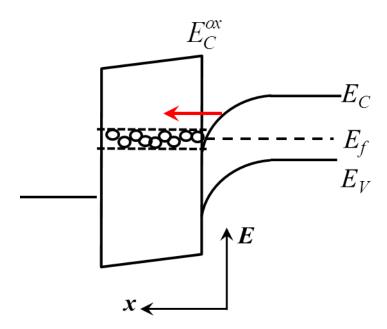

- Fig. 1.27 The charging of oxide traps in the on state of a n-MOSFET

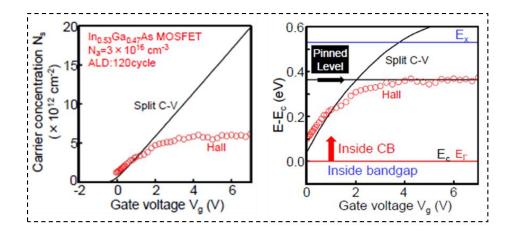

- **Fig. 1.28** Comparison on the results of (a) the carrier concentration and (b) the Fermilevel position at the ON state of InGaAs n-MOSFET evaluated by the split *C-V* measurement and Hall measurement [1. 38].

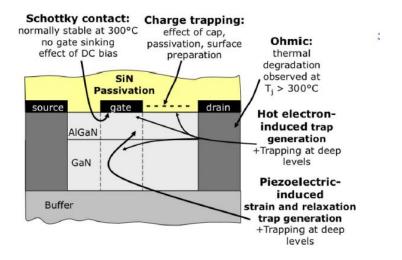

- **Fig. 1.29** Schematic cross-section on an AlGaN/GaN HEMT, identifying critical areas which can be subjected to degradation. [1.42]

**Fig. 1.30** Summary of the interface issues of novel dielectric/semiconductor and semiconductor systems investigated in this studies.

#### Chapter 2:

- Fig. 2.1 (a) The equivalent circuit for MOS capacitors with interface traps under ac small signal measurement, (b) the equivalent circuit at sufficiently high frequency that the influence of interface traps can be completely screened, and (c) the equivalent circuit at sufficiently low frequency that all of interface traps can follow the ac signal.

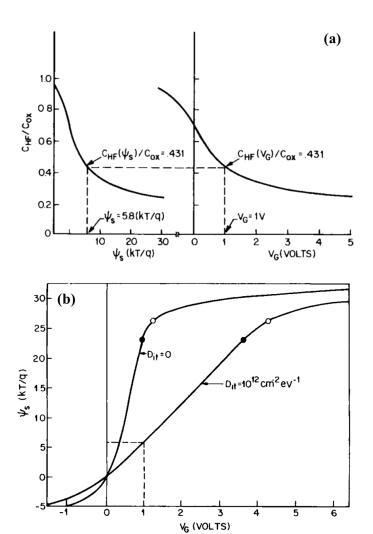

- Fig. 2.2 (a) Extraction of  $V_g$ - $\Psi_s$  relationship from high-frequency capacitance  $C_{HF}$ . The LHS diagram shows the theoretical  $C_{HF}$  versus  $\Psi_s$  without the influence of interface traps. The RHS shows the hypothetical  $C_{HF}$  versus  $V_g$ . (b) Comparison between the theoretical  $V_g$ - $\Psi_s$  with  $D_{it} = 0$  and  $D_{it} = 10^{12}$  cm<sup>2</sup> eV<sup>-1</sup> for the example shown in Fig. 2.2(a).

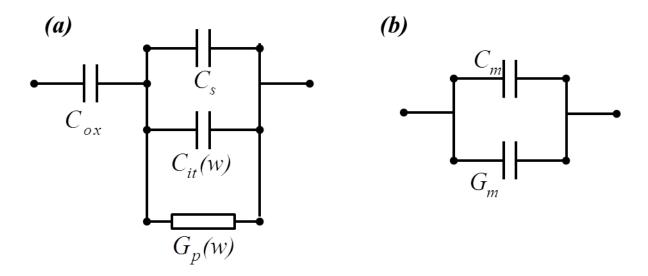

- Fig. 2.3 (a) The equivalent circuit for MOS capacitor in depletion with interface traps. Here,  $C_{ox}$  is the oxide capacitance,  $C_s$  is the semiconductor capacitance,  $C_{it}$  is parallel interface traps capacitance,  $G_p$  is the parallel interface traps conductance, and (b) The equivalent circuit for an impedance analyzer with parallel connect capacitance-conductance model.  $C_m$  and  $G_m$  are measured capacitance and conductance.

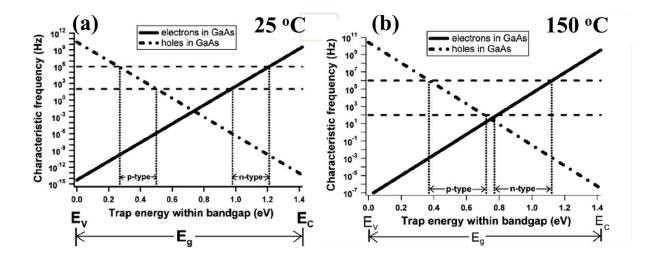

- Fig. 2.4 The characteristic frequency for electron trapping (solid line) and hole trapping (dash-dot line) as a function of energy along the band gap of GaAs at 25 °C (a) and 150 °C (b). The dash lines label commonly used frequency window of 100 Hz to 1MHz. The dot lines depict the detectable energy range for the frequency window. After G. Brammertz et al. [2.7]

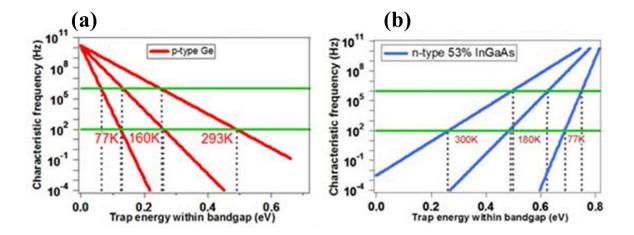

- **Fig. 2.5** (a) The characteristic frequency of hole trapping in Ge at 293K, 160K, and 77 K, and (b) the characteristic frequency of electron trapping in InGaAs at 300 K, 180 K and 77 K. The green lines label the normal measurement frequency window from 100 Hz to 1 MHz. The dot lines label the detectable energy range at different temperatures.

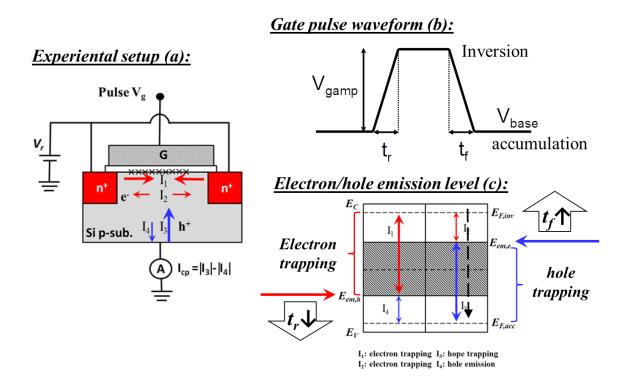

**Fig. 2.6** Schematic illustration of charge-pumping method for n-MOSFET: (a) experimental setup, (b) gate pulse waveform, and (c) description of the electron/hole emission level as a function of rising/falling time of the gate pulse.

#### Chapter 3:

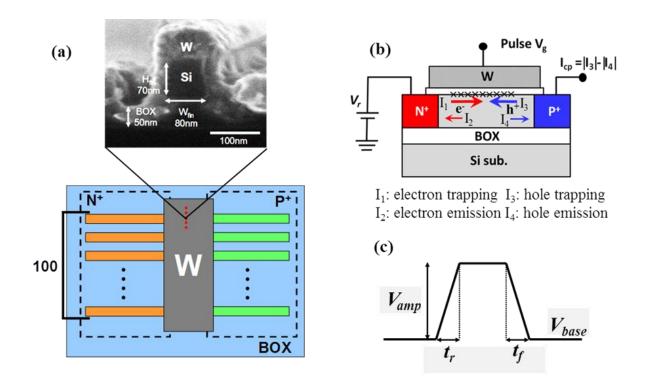

- (a) Schematics of the top view of the fabricated gated p-i-n diode device. The inset shows the SEM image of the cross-sectional view of a single fin, (b) experimental setup for the charge pumping measurement; the arrows represent four different current flows in one period of the gate pulse, and (c) the waveform of applied gate pulse.

- Fig. 3.2 Typical charge pumping characteristics of a planar SOI device: (a) charge pumping current  $(I_{cp})$  versus base level voltage of the gate pulse  $(V_{base})$ , and (b) the maximum charge pumping current  $(I_{cp,max})$  as a function of fall time  $(t_f)$ , while the rising time  $(t_r)$  is held constant at 100 ns.

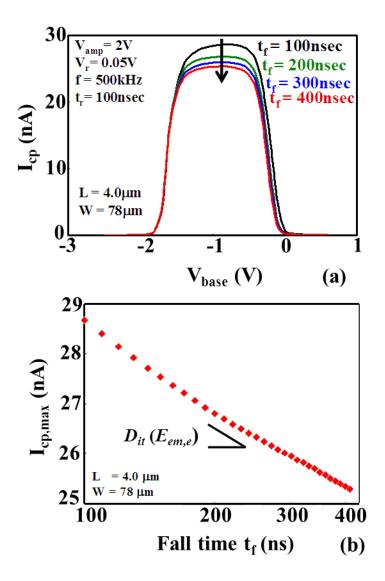

- Fig. 3.3 Energy distribution of the  $D_{it}$  of Si fin devices with width of 100 nm and height of 70 nm under F.G. annealing for 30 min at various temperatures: (a) and (b) show the  $D_{it}$  profile at lower and upper halves of the band gap of the devices with annealing temperature ranging from 300°C to 420°C, (c) and (d) show that of devices with annealing temperature ranging from 420°C to 540°C. The as-fabricated case is also shown in (a) and (b).

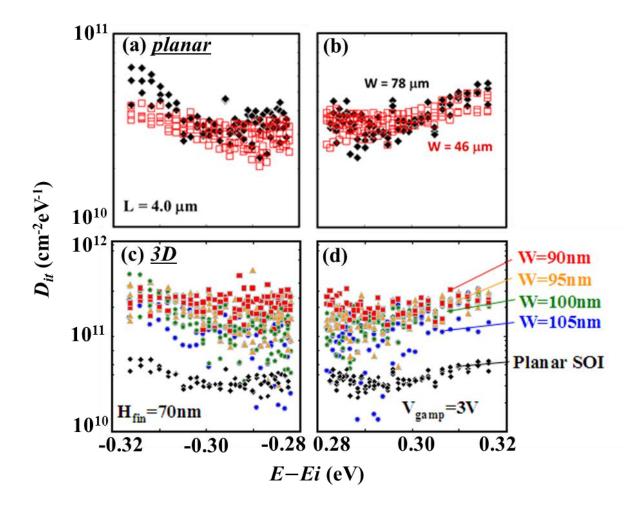

- **Fig. 3.4** (a) and (b) show the energy distribution of  $D_{it}$  of (100)-oriented planar SOI devices with different widths, (c) and (d) shows that of 3D Si fin device with width ranging from 90 to 105 nm. The case of planar is also depicted in (c) and (d) for comparison. All of the devices are annealed at 420°C under F.G. ambient for 30 min.

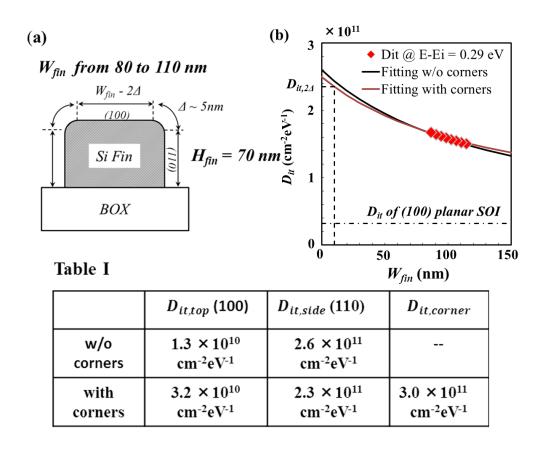

- **Fig. 3.5** (a) Schematics of the three different components, i.e., the top wall, the side walls, and the corners constituting the surface of the Si fin with rectangular-like cross-sectional shape, and (b) extraction of the  $D_{it}$  at different surface components by fitting with and without considering the corner component

using Eq. (3.3.1). The  $D_{it}$  extracted from the planar SOI device is labeled by the dash-dot line, the position of  $D_{it}(W_{fin} = 2\Delta)$  is depicted by the dash line

#### **Chapter 4:**

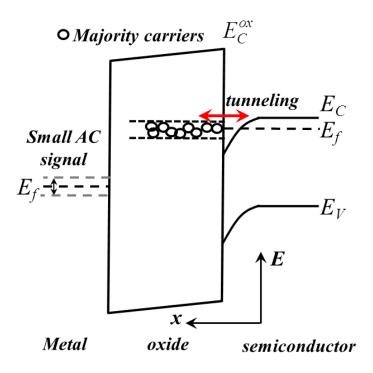

- Fig. 4.1 Band diagram of an n-type InGaAs MOS capacitor biased in strong accumulation. When a small AC signal is applied to the metal electrode, as represented by the vertical arrow, the fermi-level in the semiconductor moves up and down and the mobile carriers can be exchanged between the border traps and the conduction band states though tunneling process.

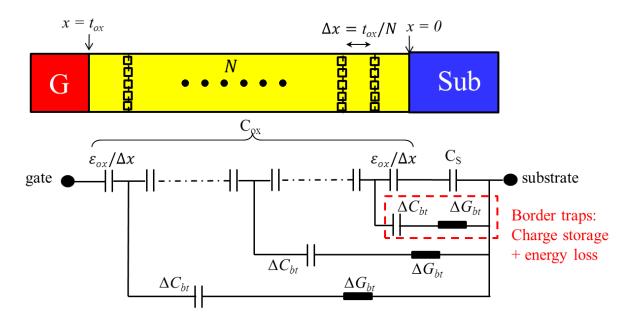

- **Fig. 4.2** The equivalent circuit for calculating the admittance characteristics in accumulation region for an MOS capacitor with border traps distributed through the thickness of the oxide [4.7, 4.8].

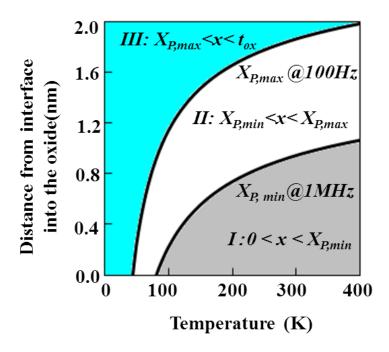

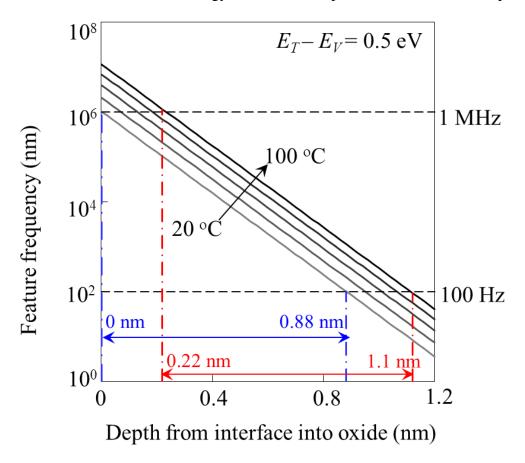

- Fig. 4.3 Estimated probing depth of the 100 Hz and 1 MHz ac signal as a fuction of temperature by using Eq. (4.3.3) and Eq. (4.3.5). The parameters adopted here are appliacabe for an n-In<sub>0.53</sub>Ga<sub>0.47</sub>As MOS capacitor baised in accumulation. ( $N_c = 2.2 \times 10^{17}$  cm<sup>-3</sup>,  $v_{th} = 5.6 \times 10^7$  cm/s,  $\sigma_n = 6 \times 10^{-15}$  cm<sup>2</sup> for In<sub>0.53</sub>Ga<sub>0.47</sub>As at 300 K [4.19], and  $E_b = 65$  meV).

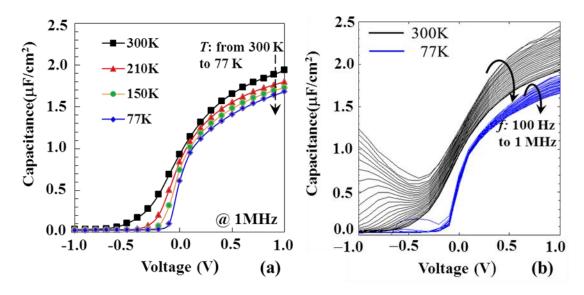

- Fig. 4.4 The C-V characteristics of the fabricated n-type  $In_{0.53}Ga_{0.47}As$  MOS capacitor. (a) high-frequency (1 MHz) C-V at 300 K, 210 K, 150 K and 77 K, and (b) multi-frequency C-V at 300 K and 77 K with 26 characterizing frequencies that logarithmically varies from 100 Hz to 1 MHz. All of the C-V measurements in this study are carried out by sweeping  $V_g$  from -1 V to 1 V.

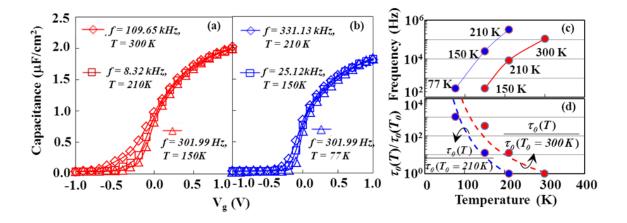

- **Fig. 4.5** The *C-V* curves with proper frequencies that have almost same capacitance in accumulation region measured at (a) 300 K, 210 K, and 150 K (red symbols), and (b) 210 K, 150 K, and 77 K (blue symbols). (c) The frequencies of the *C-V* curves used in (a) and (b) are plotted as a function of temperature by red and blue symbols, respectively. (d) The changing ratios of  $\tau_0$  as a function of temperature evaluated from the experiment (symbols) and the fitting curves (dash line) calculated by Eq. (6) using  $E_b = 65$  meV as the temperature changes from 300 K, 210 K to 150 K (red) and from 210 K, 150

K, 77 K (blue).

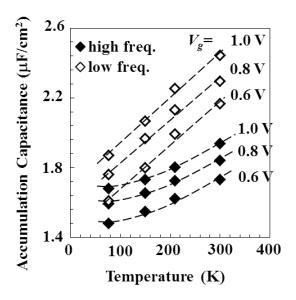

- Fig. 4.6 The accumulation capacitance measured at  $V_g = 1.0$  V, 0.8 V, and 0.6 V by the high frequency signal of 1 MHz, (the solid symbols) and the low frequency signal of 100 Hz, (the open symbols) as a function of temperature, respectively

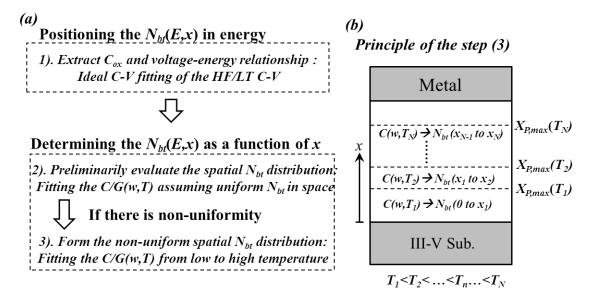

- **Fig. 4.7** (a) Proposed three-step methodology for extracting the border traps distribution in energy and space, and (b) The principle of the step 3. The  $N_{bt}$  from interface into the oxide can be gradually detected by analyzing the C-V characteristics measured from low to high temperatures with expanding the maximum probing depth,  $X_{P,max}$ .

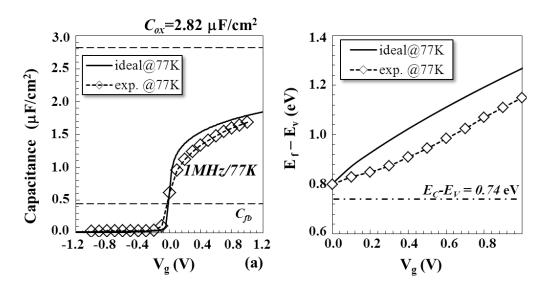

- **Fig. 4.8** (a) Comparison between the ideal C-V and the experimental 1MHz/77K C-V, and (b) the ideal voltage-energy relationship (solid line) and the extracted voltage-energy relationship (symbol) by using the Terman technique. The dash-dot line shows the position of the conduction band edge of  $In_{0.53}Ga_{0.47}As$ .

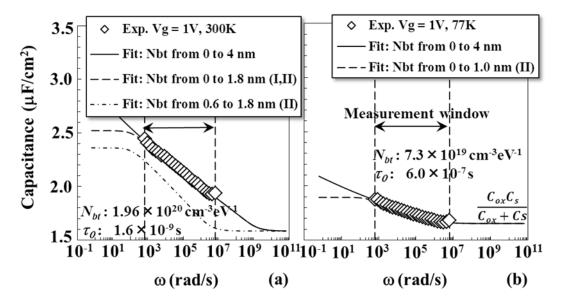

- Fig. 4.9 Fitting of the C(w) at  $V_g=1$  V at (a) 300 K and (b) 77 K, by the distributed border trap model with assuming uniform  $N_{bt}$  distributed in different regions. The fitting parameters are  $C_s(E_f, T)=3.61~\mu\text{F/cm}^2$ ,  $\kappa(E)=5.09~\text{nm}^{-1}$ ,  $N_{bt}=1.96\times10^{20}~\text{cm}^{-3}$   $\tau_0=1.6\times10^{-9}~\text{s}$  for 300 K, and,  $C_s(E_f, T)=3.98~\mu\text{F/cm}^2$ ,  $\kappa(E)=4.95~\text{nm}^{-1}$ ,  $N_{bt}=7.3\times10^{19}~\text{cm}^{-3}$ ,  $\tau_0=6.0\times10^{-7}~\text{s}$  for 77 K.  $E-E_V=1.12~\text{eV}$  and  $C_{ox}=2.82~\mu\text{F/cm}^2$  are used for both cases.

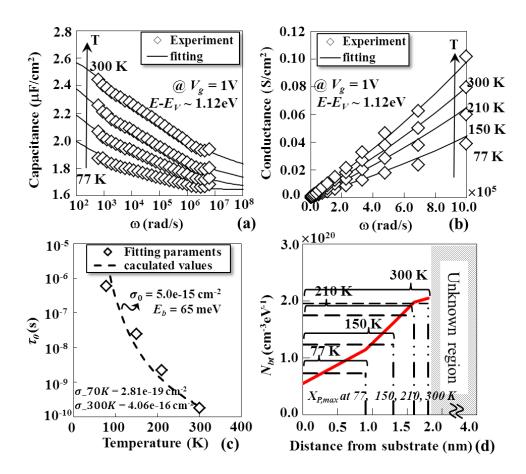

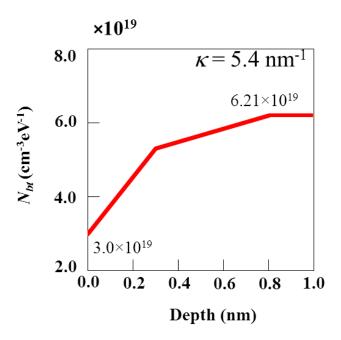

- Fig. 4.10 Comparison on frequency dispersion of capacitance (a) and conductance (b) at  $V_g = 1$ V, measured at 77 K, 150 K, 210 K and 300K, between experimental data (symbols) and fitted curves calculated by the distributed model (lines). The inputted  $\tau_0$  (symbols) for the distributed model at different temperatures and the calculated curve (dash line) by using Eq. (5) with  $N_c = 2.2 \times 10^{17}$  cm<sup>-3</sup>,  $v_{th} = 5.6 \times 10^7$  cm/s,  $\sigma_0 = 5 \times 10^{-15}$  cm<sup>2</sup> and  $E_b = 65$  meV are shown in (c). The inputted  $N_{bt}$  profile (red line) for the distributed model is shown in (d).

Besides, the vertical dash-dot lines in (d) show the evaluated maximum probing depth,  $X_{P,max}$  at different temperatures using Eq. (3) with  $\kappa = \kappa(E) = 5.09 \text{ nm}^{-1}$ , f = 100 Hz and the  $\tau_0$  shown in (c), and the horizontal dash lines in (d) shown the  $N_{bt}$  extracted at different temperatures by assuming uniform  $N_{bt}$  spatial distribution. Additionally, except the influence of border traps, that of series resistance is also considered in the distributed model by using the parameters of  $R_s = 6.6 \times 10^{-3} \,\Omega \cdot \text{cm}^2$  and  $G_{Ln} = 1.2 \times 10^{-4} \,\text{S/cm}^2$ .

Fig. 4.10 Comparison on frequency dispersion of capacitance (a) and conductance (b) at  $V_g = 1$ V, measured at 77 K, 150 K, 210 K and 300K, between experimental data (symbols) and fitted curves calculated by the distributed model (lines). The inputted  $\tau_0$  (symbols) for the distributed model at different temperatures and the calculated curve (dash line) by using Eq. (5) with  $N_c = 2.2 \times 10^{17}$  cm<sup>-3</sup>,  $v_{th} = 5.6 \times 10^7$  cm/s,  $\sigma_0 = 5 \times 10^{-15}$  cm<sup>2</sup> and  $E_b = 65$  meV are shown in (c). The inputted  $N_{bt}$  profile (red line) for the distributed model is shown in (d). Besides, the vertical dash-dot lines in (d) show the evaluated maximum probing depth,  $X_{P,max}$  at different temperatures using Eq. (3) with  $\kappa = \kappa(E) = 5.09$  nm<sup>-1</sup>, f = 100 Hz and the  $\tau_0$  shown in (c), and the horizontal dash lines in (d) shown the  $N_{bt}$  extracted at different temperatures by assuming uniform  $N_{bt}$  spatial distribution. Additionally, except the influence of border traps, that of series resistance is also considered in the distributed model by using the parameters of  $R_s = 6.6 \times 10^{-3}$   $\Omega \cdot \text{cm}^2$  and  $G_{Ln} = 1.2 \times 10^{-4}$  S/cm<sup>2</sup>.

#### **Chapter 5:**

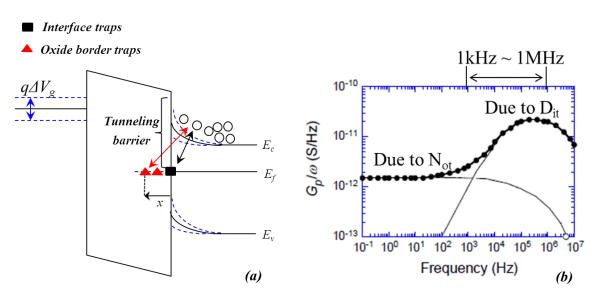

- **Fig. 5.1** (a) Band diagram of the MOS capacitor biased at the depletion condition with illustration of the trapping/de-trapping processes by interface and oxide traps under a small ac signal, and (b) typical parallel conductance versus frequency plot of a Al/SiO2/Si MOS capacitor [5.3].

- **Fig. 5.2** The experimental (symbols) and fitted (lines) conductance curves of Al<sub>2</sub>O<sub>3</sub>/InP based MOS capacitors with same surface treatments and different

gate dielectrics deposition parameters [5.4].

- Fig. 5.3 Characteristic frequency of electron trapping by interface states as a function of the energy along the band-gap with temperature as a parameter in the InGaAs MOS capacitor. The commonly used measurement frequency window ranges from 100 Hz to 1 MHz is labeled by dash lines, and the corresponding energy ranges of the interface traps at 20 °C and 100 °C are also depicted by the blue and red dash-dot lines, respectively.

- Fig. 5.4 Feature frequency as a function of the depth from interface into oxide of oxide border traps located at energy level of  $E_T$   $E_V$  = 0.5 eV. The normal used measurement frequency window range from 100 Hz to 1 MHz is labeled by the dash line.

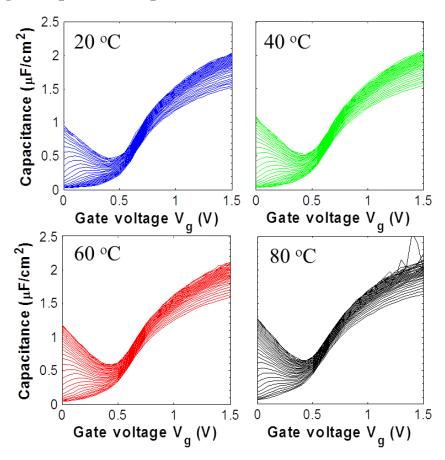

- **Fig. 5.5** Typical multi-frequency C-V characteristics of Pt/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As from 100 Hz to 1 MHz at 20, 40, 60, and 80  $^{\circ}$ C.

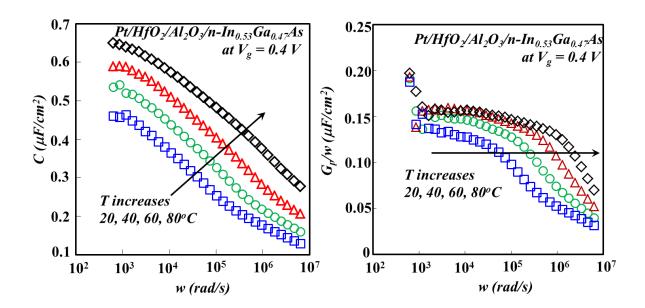

- Fig. 5.6 (a) The Capacitance versus frequency and (b) the parallel conductance versus frequency plot of the under test sample at  $V_g = 0.4$  V with measuring temperature of 20, 40, 60, 80 °C.

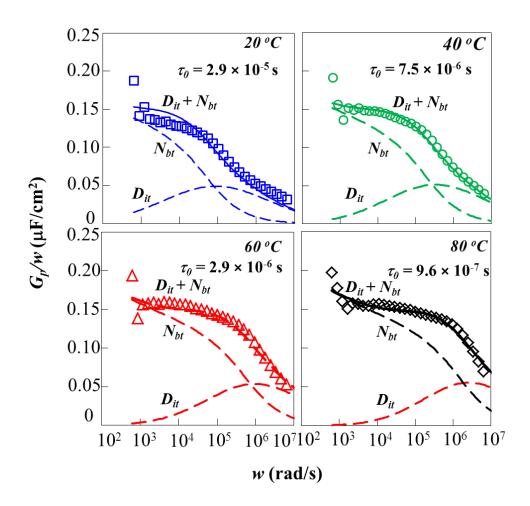

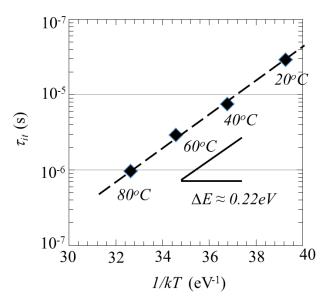

- Comparison between the experimental conductance curves (symbols) and the fitted curves (solid lines) with considering both of the responses of the interface traps and oxide border traps at 20, 40, 60, and 80 °C, respectively. The contribution of interface traps and oxide border traps on the fitted conductance curves is also plotted by dash lines.

- **Fig. 5.8** The spatial distribution profile of  $N_{bt}$  used for fitting the conductance curves shown in Fig. 5.7.

- **Fig. 5.9** The  $\log(t_{it})$  versus (1/kT) plot for extraction of the fermi-level energy. The  $t_{it}$  used here is extracted from the conductance curves as shown in Fig. 5.7.

#### **Chapter 6:**

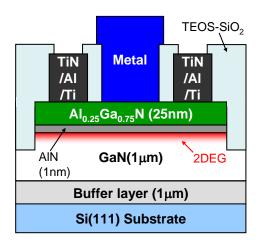

- Fig. 6.1 Schematic illustration of (a) the lattice mismatch between AlGaN and GaN crystal structures, (b) the tensile strain endured by the thin AlGaN layer in the AlGaN/GaN heterojunction, and (c) the band diagram of the AlGaN/GaN heterojunction and the formation of polarization charges and two-dimensional electron gas (2DEG).

- **Fig. 6.2** Schematic structure of fabricated AlGaN/GaN HEMTs [6.10, 6.11].

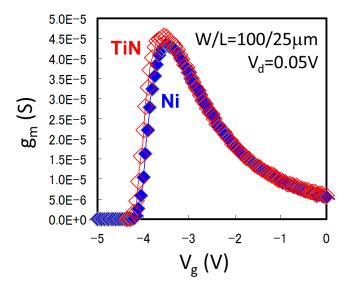

- **Fig. 6.3**. Comparison on transconductance characteristics between AlGaN/GaN based HEMTs with TiN and Ni gate electrodes.

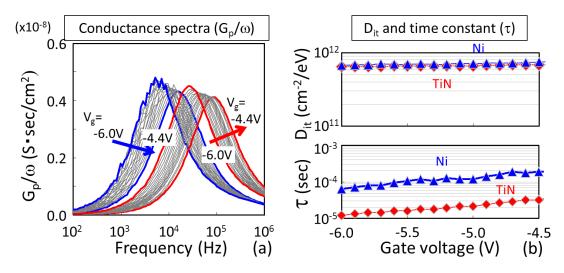

- Fig. 6.4 Comparison on the (a) conductance spectra of the AlGaN/GaN HEMTs with the Ni (blue) and TiN (red) electrodes biased in depletion region, and (b) extracted  $D_{it}$  and (c) time constant  $\tau$  by using standard conduction method

- Fig. 6.5

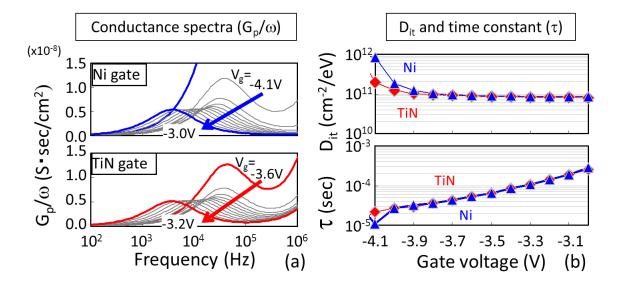

Comparison on the (a) conductance spectroscopy, (b) extracted  $D_{it}$  and (c) time constant  $\tau$  using standard conductance method of the AlGaN/GaN heterostructures with the Ni (blue) and TiN(red) electrodes biased at inversion region.

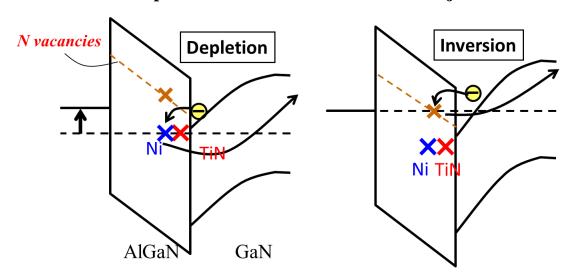

- **Fig. 6.6** Schematic band diagram of the AlGaN/GaN heterojunction in depletion and inversion with illustration of the distribution of the electrically active traps in the devices with TiN and Ni electrodes.

## List of Tables

- **Table 1.1** Comparison on critical properties for high-frequency and high-power applications between several semiconductor materials.

- Table 1.2 Comparison on the effective mass, the electron mobility and the density of states (DOS) in the conduction band in Si and representative III-V compound semiconductors. The underlying equations show how the mobility and the DOS influence the on-current of MOSFET devices.

- **Table 2.1** Comparison on the advantages and disadvantages of interfacial traps characterization techniques based on admittance analysis and CP methods.

- **Table 3.1** Summary of the extracted local  $D_{it}$  in both cases of with and without considering the corner regions.

- **Table 7.1** Summary of the major contributions of this thesis

## **Chapter 1: Introduction**

In order to avoid CMOS down-scaling limit due to the short-channel effect, multi-gate structure, such as fin-FETs or Tri-gate has been introduced. In addition, MOSFETs with new channel materials such as InGaAs (III-V) and Ge are studied for low power application under low voltage. Also, HEMT (High Electron Mobility Transistor) devices using AlGaN/GaN hetero-junction for the channel are being developed for power and high-frequency applications. However, the distribution of interface and near-interface traps at the gate dielectrics/semiconductor interfaces and the semiconductor hetero-junction interfaces in these emerging devices are still lack of investigation.

In this thesis, in order to provide a guideline for trap characterization for future development of advanced FET, we have proposed methodologies for trap characterization and revealed in-depth understanding of the distributions, origins, species, and trapping mechanisms gate dielectrics/semiconductor interfaces and the semiconductor heterojunction interfaces.

## 1.1 Moore's law and Dennard Scaling

#### 1.1.1 Moore's law – history and current status

**Fig. 1.1** The evolution of total transistor count on a chip (a) and the feature size of logic technology (b) of Intel microprocessors [1.4]

The relentless development of Si-based large-scale-integrated circuits (LSIs), in the past four decades has revolutionized the information technology, and contributed to far-reaching impacts on the modern society [1.1, 1.2]. This tremendous progress is achieved on the scaling of LSIs' technology driven by Moore's law, which predicted that the transistor density would double every 24 months [1.3]. For instance, Figure 1.1(a) shows the evolution of total transistor count on a chip of Intel microprocessors released from 1970 to 2010 [1.5]. The transistor count on a chip has approximately increased by a factor of two every two years in the past four decades, which also allows dramatic improvement on operating frequency of the microprocessors. This is mainly achieved by scaling the transistors which keeping the transistor lateral-to-vertical aspect ratio according to the scaling rule proposed by Robert Dennard et al. [1.5] as described in the following section. Figure 1.1(b) shows the aggressive scaling of the feature size for logic application in Intel [1.5]. The scaling trend of transistors still persists till today and the schedule in which the transistor density increases by 2X every 24 months is still generally recognized by the roadmap made by the industry. Nowadays, the 22 nm generation technology has already been ramped into mass production [1.6].

#### 1.1.2 Dennard scaling law and its challenges

**Fig.1.2** Illustration of the constant-field scaling theory of MOSFET proposed by Dennard et al. in 1974 [1.5]

The ideal scaling of metal-oixde-semiconductor field-effect transistors (MOSFETs), which results in smaller device size and improved device performance, can be achieved by the constant-field scaling theory proposed by Dennard et al. [1.5], as shown in **Fig.1.2**.

According to this method, in order to keep constant electric field in the channel, all of the dimensional parameters, including gate length (L), channel width (W), thickness of the gate oxide  $(t_{ox})$ , and the junction depth  $(X_j)$ , are scaled by a factor of k. The supply voltage  $(V_{dd})$  and threshold voltage  $(V_{th})$  are also scaled by a factor of k. Besides, to simultaneously scale the depletion depth  $(X_d)$  by same ratio, the doping concentration  $(N_{sub})$  in the channel is increased by a factor of k. Besides, the drain current  $I_d$ , which can be from Eq. 1.1.1 as below [1.6], is also scaled by a fact of k.

$$I_d = \mu C_{ox} \frac{W}{L} (V_{gs} - V_{th} - \frac{V_{ds}}{2}) V_{ds} \dots Eq. (1.1.1)$$

Here,  $\mu$  is the mobility,  $C_{ox}$  (~1/ $t_{ox}$ ) is the oxide capacitance,  $V_{gs}$  and  $V_{ds}$  are the gate-to-source and the drain-to-source voltage, respectively.

As a result, the delay time  $\tau(\sim CV/I)$  is scaled to  $I/\alpha$ , which indicates that the whole circuit can be operated at faster speed or higher frequency. More importantly, if the ideal constant-field scaling can be achieved, the power for switching the transistor can be scaled to  $1/k^2$ . Because the transistor density is increased to  $k^2$  due to the laterally scaling of the transistor dimensions, the power density can be kept constant after scaling. Therefore, it can be seen that high operational speed can be achieved without increasing the power density in the ideal case.

However, it should be noticed that the Dennard scaling rules are based on following assumptions. First, it ignored the impact of transistor sub-threshold leakage on overall power consumption. Secondly, it assumed that the oxide thickness can be continually scaled. Lastly, it assumed that the channel doping concentration can be continually increased.

In the early days of MOSFET scaling around 1970's, the dimensions and the operational voltages of MOSFETs were relatively large and the ideal Dennard scaling rules could be well achieved. However, after about 40 years' aggressive scaling, dimensions of advanced MOSFETs have shrunk to the deep sub-micrometer region and the aforementioned

assumptions are not valid any more. The limitations of the traditional scaling rules are discussed in details as below.

#### (a) Power-constrained supply voltage scaling

**Fig. 1.3** Illustration of the main origin of the dynamic power (a) and the static power (b) of a CMOS invertor.

The CMOS invertor is one of the fundamental components for constructing LSIs, in which both of n-type and p-type MOSFETs are complementarily used. The power consumption of a CMOS invertor can be divided into two types, dynamic and static, as illustrated in **Fig. 1.3**. As shown by **Fig. 1.3** (a), the dynamic power mainly origins from the energy that is used to charge and discharge the load capacitance. It can be derived that the energy per transition for charging or discharging can be given by:

Energy / transistion =

$$C_L \times V_{dd}^2$$

, Eq. (1.1.2)

Therefore, the dynamic power can be given by:

$$P_{dynamic} = Energy / transistion \times frequency = C_L \times V_{dd}^2 \times f$$

, Eq. (1.1,3)

On the other hand, the static power is mainly associated with the leakage current, such as sub-threshold leakage and drain junction leakage, as shown in Fig. 1.3 (b). It can be given

by:

$$P_{static} = V_{dd} \times I_{leak}$$

, Eq. (1.1.4)

Thereby, the total power consumption can be given by:

$$P = P_{dynamic} + P_{static} = C_L \times V_{dd}^2 \times f + V_{dd} \times I_{leak}$$

Eq. (1.1.5)

**Fig. 1.4** Evolution of the power density of CMOS circuits as a function of gate length [1.7]

Ideally, the static power of the CMOS invertor should be very low, which also widely recognized as one of the most important advantage of the CMOS technology, because n-MOSFET and p-MOSFET always do not switch on or off at the same time in this type of circuit. Thus the static power should be ignorable compared to the dynamic power. This is generally true for the technology generation with relatively long gate length (~ 1μm). However, as shown by **Figure 1.4**, as the gate length scaled to the < 100 nm region, it can be seen that the static power significantly increases with decreasing gate length. It also noteworthy that the static power even may even surpasses the dynamic power when the gate length scaled to around 10 nm. Considering the extremely high transistor density, the increased static power of the LSIs constructed by highly scaled transistors may result in huge power consumption. In addition, the huge power consumption also considerably rise

the temperature of the chip, which may leads to several failure mechanisms and degrade the reliability of the circuit [1.8]. In short, to continually the CMOS scaling trend, suppressing the power consumption, especially the static power consumption, is of significant importance.

**Fig. 1.5** (a) Power-supply voltage  $(V_{dd})$ , threshold voltage  $(V_{th})$  and gate-oixde thickness  $(t_{ox})$  as a function of channel length for CMOS logic technologies [1.9], and (b) schematic drain current-gate voltage  $(I_d-V_g)$  relationships with different  $V_{dd}$  and  $V_{th}$  with illustration of the increased off-state current  $(I_{off})$  after  $V_{dd}$  or  $V_{th}$  scaling.

**Figure 1.5** (a) shows the history and trends of the power-supply voltage, threshold voltage as a function of channel length for CMOS logic technologies, adopted from Ref. [1.9]. It can be seen that when the channel length was scaled from ~1  $\mu$ m to ~ 0.1  $\mu$ m, the  $V_{dd}$  was scaled with a smaller rate compared to that of the scaling of the channel length. Besides,  $V_{th}$  was scaled even slower that of the scaling of  $V_{dd}$ . Furthermore, as the channel length was scaled to sub-100 nm region, the scaling of  $V_{dd}$  and  $V_{th}$  almost got saturated. The underlying mechanism that hinders the scaling of  $V_{dd}$  and  $V_{th}$  is shown in **Fig. 1.5** (b). In order to scale  $V_{dd}$  without sacrificing on-state current,  $I_{ON}$ ,  $V_{th}$  also has to be scaled at the same time.

However, it can be seen that the off-state current,  $I_{OFF}$ , increases logarithmically with decreasing  $V_{th}$ . At the early stage of CMOS scaling, the sub-threshold leakage was relatively low and its contribution to the chip total power consumption was ignorable. Considering relatively high sub-threshold leakage current and transistor density nowadays, it is very difficult to further continually scale the  $V_{th}$  and  $V_{dd}$ . To overcome this impediment, novel devices with new operational principle allowing ultra-steep sub-threshold slope, or novel channel design having enhanced carrier's transportation, are under development.

#### (b) The limitation of scaling the thickness of gate dielectrics

**Fig. 1.6** (a) The road map for scaling of the gate oxide predicted by the semiconductor Industry Association (SIA), USA, in 1997 [1.10], and (b) Schematic of the evolution of the SiO<sub>2</sub> gate oxide [1.11].

The SiO<sub>2</sub> gate insulator is considered as one of key points that contribute to the unprecedented success of the Si MOSFETs as the workhorse for modern microelectronic industry. It owns high resistance and high breakdown voltage. Besides, it can be easily grown on Si substrate by thermal oxidation process with abrupt interface and few amounts of active interface traps. However, **Fig. 1.6** (a) the roadmap predicted by SIA in 1997 (note that the actual scaling trend is more aggressive than this), the technology nodes below 50

nm require that the thickness of SiO<sub>2</sub> should be scaled to 1.3 nm. As shown by the schematic image of the atomic structure of the SiO<sub>2</sub> layer in **Fig. 1.6** (b), a 1.3-nm-thick SiO<sub>2</sub> layer contains only five layers of atomic. While the top and bottom layers are used to connect the Poly-Si gate and the Si channel, only three atomic layers serve as the insulating layer, which is considering the minimum requirement for effective suppression of the tunneling current between gate and substrate. It means that the thickness scaling of the SiO<sub>2</sub> gate oxide had already been reached now. To tackle this challenge, the SiO<sub>2</sub>/poly-Si gate stack has to be replaced by the high-k/metal-gate configuration, as introduced in the later sections.

#### (c) The limitation of increasing the channel doping concentration

In Dennard's law, another very important enabling factor for continuing the constant-field scaling is that continual increasing the channel doping concentration. However, the channel doping concentration cannot be too high mainly because of two reasons: (1) the carrier mobility can be severely degraded due to increased impurity scattering, and (2) the drain junction leakage may considerably increases due to direct band-to-band tunneling.

**Fig. 1.7** Illustration of the deviations from ideal Dennard's scaling law in scaling the conventional Si MOSFETs and their influences: conventional Si MOSFET will finally fail as scaling continues due to the short channel effects and novel design/materials are expected.

Here, we summarized the aforementioned limitations that deviate the scaling of conventional Si MOSFET from the ideal scaling rules: (a) the limitation of voltage scaling due to the power concern, (b) the limitation of scaling the thickness of SiO<sub>2</sub> gate oxides, and (c) the limitation of increasing the channel doping concentration, as shown in the left-hand side in **Fig. 1.7**. In the extremely scaled devices, these limitations lead to (a) the horizontal electric field from source to drain is increased, (b) the electrostatic control of channel by gate is weakened, and (c) the space charge region cannot be sufficiently scaled as the same ratio of the scaling of the dimensions of the devices. These effects due to the deviations from the ideal scaling rules induce so-called "short-channel effects", including the increase of the sub-threshold leakage, or the S.S. degradation, and the drain induced barrier lowering (DIBL), as shown by the upper part of the right-hand side in **Fig. 1.7**.

**Fig.1.8** Short channel effects in n-MOSFETs: (a) Schematics of the leakage current in subthreshold region, [1.1] and (b) the band diagram of source/channel/drain with illustration of the drain induced barrier lowering (DIBL) effect.

**Figure 1.8** shows two key device degradation mechanisms as channel length decreases known as short channel effects: (a) increasing in sub-threshold leakage, or degradation of S.S., and (b) DIBL effects, as described in details as follows. In generally, the short channel effects are caused by two facts that violated the constant-field rule: (1) the horizontal electric field from source to drain substantially increased and thus drain electric-field may penetrate to the source side, and (2) the vertical electric field is weakened as thus the gate-to-channel control degrades. Simply put, the drain take over the control of the channel from the gate as channel length decreases.

The underlying mechanism of increased sub-threshold leakage in short-channel devices is schematically shown in **Fig. 1.8** (a). It is mainly caused by the fact that the space charge region cannot be scaled as the same ratio as that of scaling of the device dimensions. As a result, if the large space charge region in the drain junction caused by the reverse drain bias sufficiently approaches the source, the carriers in source can directly inject from source to drain and thus a leakage path beneath the surface channel is created. This effect contributes to additional sub-threshold leakage current and can significantly degrade the S.S. characteristic.

The other short channel effect known as DIBL is mainly caused by penetration of the drain electric-field to the source sides, as shown by **Fig. 1.8** (b). Ideally, in long channel devices, the barrier between the source and the channel should be completely controlled by the gate electrode. However, in extremely scaling devices, the barrier can be lowered by drain electric-field. This effect leads to (1) increasing sub-threshold leakage, and (2) drain voltage dependent  $V_{th}$  that can further increase the sub-threshold leakage.

The short channel effects caused by the deviation from the ideal scaling rule finally cause the failure of convention Si MOSFET to continue the aggressive CMOS scaling trends. As a result, novel designs/materials have to be implanted to overcome these challenges, as summarized in the lower part of the right-hand side in **Fig. 1.7**. To continually enhance the

gate-to-channel control, multi-gate structure or high-k gate dielectrics can be adopted. To further reduce the supply voltage, one of possible solutions is adopting high-mobility channel to boost the drivability. In addition, another emerging trend to improve the performance of IC is innovatively integrated the semiconductor devices for digital applications, which need to be scaled for increasing performance, and those for non-digital applications, which do not need to be scaled at the same ratio with those for digital application. From this perspective, high performance flied-effect transistors for non-digital application are also of particular importance. In the following sections, the strategy and the emerging device technologies for overcoming the current challenges faced on continuing Moore's law are discussed in details.

#### 1.2 Overcoming the challenges faced by CMOS scaling

#### 1.2.1 "More Moore" and "More than Moore"

**Fig. 1.9** Future technology directions, including "More Moore", "More than Moore", and "Beyond CMOS", to further improve the performance of LSIs. [1.12]

As discussed in the previous sections, CMOS scaling is facing critical challenges in deep sub-micrometer regoin. To further improve the IC's performance, there are three main directions, including "More Moore", "More than Moore", and "Beyond CMOS", as illurstrated by Fig. 1.9. In further, CMOS scaling is still the mainstrain drived by Moore's law, namely "More Moore". To continue the progess in this direction, novel structures/materials. such as muti-gate configuration, high-k/metal gate, and high-mobility channel, have to be intregrated into convention bulk planr MOSFET. The second trend is so called "More than moore". It is characterized by functional diversication of semiconductor-based devices, and invovative integration of the non-digital functionalities that do not necessarily scales at the same rate as the one required by the digital circuits. To develop this technology trend, novel semiconductor devices for analog/RF, high power electronics, sensors and etc., such as III-nitride based HEMT, are expected. The last trend is the

"Beyond CMOS", which emphasize on developing electronic systems based on revolutionary concept that is completely different with that of conventional CMOS technolgy. Examples incudes carbon-based electronics, spintronics, molecular switching devices and etc.

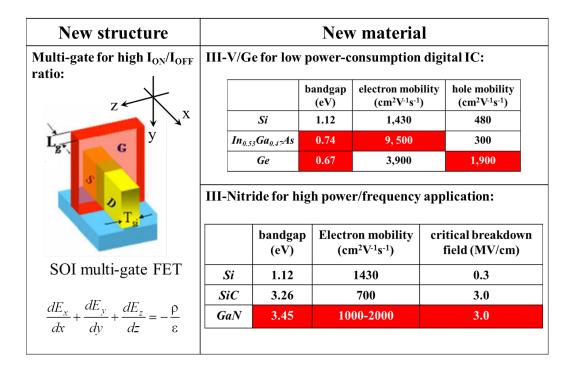

**Fig. 1.10** Representative new structure/material technology for novel field-effect transistors to continue CMOS scaling and diversify functionality.

Our study mainly focuses on the new structure/material technology for novel FETs to continue CMOS scaling and diversify functionality for "More Moore" and "More than Moore". Specifically, as shown by **Fig. 1.10**, from structure prospective, multi-gate structure can be adopted to enhance the electrostatic control of the channel. From material perspective, compared to conventional Si channel, semiconductors with relatively small bandgap and high mobility, such as III-V and Ge, can be integrated for low power-consumption digital IC. On the other hand, semiconductors with relatively large bandgap and high mobility, such as III-nitride, are attractive for high-power and high-frequency application. The principles and features of these technologies are detailed as follows.

#### 1.2.2 Multi-gate FETs for gate-to-channel electrostatic control

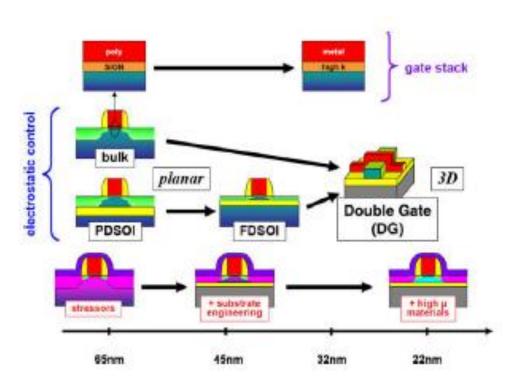

Fig. 1.11 Structure and technology innovation for MOSFET, adopted from H. Iwai [1.2].

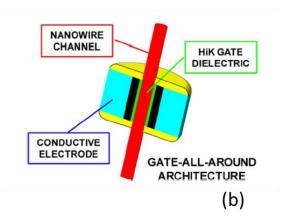

**Figure 1.11** [1.2] shows the structure innovation for MOSFET to address SCEs by increasing electrostatic control. The three-dimension (3D) channel with gate-all-around (GAA) structure is considered to be the ideal structure for ultimate scaling because it's excellent gate-to-channel electrostatic control [1.14, 1.15]

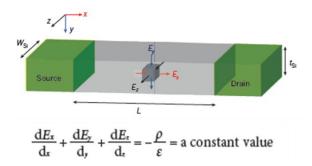

**Fig. 1.12** Enhanced electrostatic gate control of the channel can be achieved by adopting 3-D channel with multi-gate structure. After I. Ferain, et al [1.14]

**Figure 1.12** illustrates the principle for enhanced electrostatic control by using the 3D channel. Considering the Possion equation in the channel of the MOSFET in conventional planar devices, the electric field in the channel comes from (1) the horizontal electric field from the drain to source (x-direction) and (2) the vertical electric field from the gate to the channel (y-direction). Therefore, the Possion equation in the channel can be given by:

$$\frac{dE_x}{dx} + \frac{dE_y}{dy} = -\frac{\rho}{\varepsilon}$$

(1.2.1)

On the other hand, in a MOSFET with 3D channel as shown in **Fig. 1.11**, the vertical electric field form the gate to the channel is not only one dimensional but surrounding the channel. For a 3D channel with rectangular-like cross-sectional shape, the Possion equation in the channel can be given by:

$$\frac{dE_x}{dx} + \frac{dE_y}{dy} + \frac{dE_z}{dz} = -\frac{\rho}{\varepsilon}$$

(1.2.2)

By comparing Eq. (1.2.1) and Eq. (1.2.2), we see that the electrostatic control in the 3D channel is more effective than that in conventional planar devices.

Furthermore, based on the Possion equation shown in Eq. (1.2.2) with a few assumptions, a parameter called the natural length ( $\lambda$ ), which reflects the penetration of the drain electric field from the drain side to the source side, can be calculated, and the minimum gate length ( $L_g$ ) is about seven times of  $\lambda$  [1.14]. Particularly,  $\lambda$  can be given by [1.9]:

$$\lambda = \sqrt{\frac{\varepsilon_{ch}}{N\varepsilon_{ox}}} t_{ox} t_{ch} \ (1.2.3)$$

Here,  $\varepsilon_{ch}$  and  $\varepsilon_{ox}$  are the relative dielectric constants of the channel material and the oxide materials.  $t_{ox}$  and  $t_{ch}$  represent the thickness of the gate oxide and the channel. N is the number of the "effective gate number"(Planar: N=1, Double-Gate: N=2, Tri-Gate: N=3, GAA: N=4). From the Eq. (1.2.3), the penetration of the electric field form the drain to the

source can be effectively suppressed by (1) using the 3D structure channel, (2) shrinking the thickness of the channel and (3) the gate stack with ultra-thin high-k dielectric. The later issue will be further discussed in the coming section.

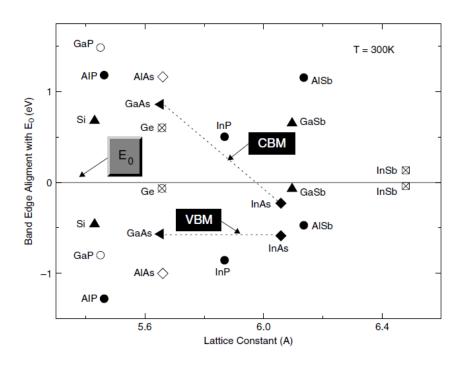

**Fig. 1.13** Evaluated minimum gate length as a function of channel width for a gate-all-around MOSFET with Si,  $In_{0.53}Ga_{0.47}As$ , Ge channel.

In 3D MOSFET with fully-depleted channels, shrinking the dimensions of the cross-section is also a big channel. It not only relies on the development of advanced process, but also may arouse new transportation mechanism. Here, we also estimated the minimum gate length as a function of the channel width according to Eq. (1.2.3) of a GAA MOSFET with the equivalent oxide thickness (EOT) of 0.5 nm, as shown in **Fig.1.13**. It can be seen that scaling the gate length requires aggressive scaling of the channel width. Specifically, gate length below 10 nm requires Si channel width below 6 nm. Furthermore, introduction of new channel materials, such as In<sub>0.53</sub>Ga<sub>0.47</sub>As and Ge, requires even smaller dimension because of thier relatively low dielectrics constants.

In addition, it is also noteworthy that in 3D channel structure, the scaling of channel width is of significant importance to realize 1D ballistic transportation [1.16]. In case of ballistic transportation, the carriers are expected to be directly injected from the source to the drain

without experiencing any scattering. Therefore, achieving 1D ballistic transportation in extremely scaled 3D MOSFET devices is highly expected for superior drivability.

#### 1.2.3 High-k/Metal gate for EOT scaling

**Fig. 1.14** Illustration of (1) replacement of SiO<sub>2</sub>/poly-Si gate stack with high-k/metal electrode to achieve same capacitance with suppressed gate leakage, and (2) the concept of the equivalent oxide thickness (EOT) of the high-k dielectrics. Here, C<sub>high-k</sub> and C<sub>SiO2</sub> are the capacitance values of the high-k and SiO<sub>2</sub> MOS capacitors, respectively. t<sub>high-k</sub> is the physical thickness of the high-k. ε<sub>high-k</sub> and ε<sub>SiO2</sub> are the relative permittivity, and ε<sub>0</sub> is the vacuum permittivity.

Replacement of the SiO<sub>2</sub>/poly-Si gate stack by that consisting high-k/metal electrode can address this problem by achieving same capacitance with suppressed gate leakage. As shown in **Fig. 1.14**, since the larger dielectrics constant of high-k materials compared to that of SiO<sub>2</sub>, same capacitance can be achieved by high-k dielectrics with thicker physical oxide thickness. Therefore, the gate leakage in the high-k based MOS device can be effectively suppressed. In addition, the equivalent oxide thickness (EOT) of high-k can be

defined by calculating the thickness of SiO<sub>2</sub> that gives same capacitance.

Furthermore, the deployment of metal electrodes is also an indispensable element to realize the high-k technology. Poly-Si/high-k gate stack have following problems. (1) weak depletion of the poly-Si electrode degrades the EOT [1.6], (2) the fermi-level is pining at the poly-Si/high-k interface due to the large amount of traps at the surface [1.17] and thus we cannot adjust the threshold voltage by change the doping in the poly-Si electrode, and (3) poly-Si/high-k gate stack shows strong remote phonon scattering phenomenon and considerably degrades the channel mobility [1.18]. These issues can be solved by using high-k/metal gate structure [1.19].

#### 1.2.4 III-V/Ge based FETs for mobility boosting

**Fig. 1.15** Schematic illustration of the necessity of adopting the high mobility channel for lowering the supply voltage without degrading the requirement for on- and off-current ( $I_{ON}$  and  $I_{OFF}$ ). The blue line shows typical  $I_d$ - $V_g$  of an MOSFET, the dash line shows the one of the device with decreased  $V_{th}$  and the red line shows the one of the device with high mobility in the channel.

As previously discussed, the supply voltage cannot be scaled due to the power consumption considerations. One solution of this problem, as illustrated in **Fig. 1.15**, is adopting the channel with enhancement transportation, such as strained Si, Ge, and III-V compound semiconductor. It can results in larger on-current and thus allow reducing  $V_{dd}$  without sacrificing the requirements on  $I_{on}$  and  $I_{off}$ .

**Fig. 1.16** (a) Comparison of the electron injection velocity  $(v_{inj})$  at different gate lengths in Si channel and III-V channel. After J.A.del Alamo, et al. [1.20], and (b) schematic image of the III-V based MOSFET with illustration the relationship between on  $I_{on}$  and  $v_{inj}$ .

In particular, III-V compound semiconductors, such as  $In_{0.53}Ga_{0.47}As$  and InAs, are extensively studied as alternative channel materials of n-type metal-oxide-semiconductor field effect transistors (n-MOSFETs) for future high-speed, low-power logic applications due to their intrinsic high electron mobility [1.20, 1.21]. As shown in **Fig. 1.16(a)** [1.20], compared to conventional Si or Strained Si channels with large  $V_{dd}$  (1.1-1.3 V), the III-V channels with small  $V_{dd}$  (0.5 V) show much larger injection velocity, especially at short gate length case ( $L_g \sim 30$  nm), and thus potentially show better drivability (**Fig. 1.16(b)**).

**Fig. 1.17** (a) The improved performance of the p-MOSFET as the generation of the technology node evolves is achieved by implementation of new materials and architecture in past technology node.[1.22] and (b) the component of the ultimate CMOS device.[1.22]

In summary, to extend the Moore's law and take the advantage of improving the performance while lowering the cost by scaling, new structures and materials have to be developed. **Fig. 17** (a) shows the utilizing of new structures and materials has become the key to boost the performance in recent technology nodes, e.g., the high-k/metal gate replaced SiO<sub>2</sub> based gate insulator in 45 nm generation to overcome the scaling limit of the gate oxide, the tri-gate structure was introduced in 22 nm, in which the fully-depleted Si Fin channel was surround by the top/side gate electrodes and the electrostatic control was substantially increased. **Fig. 17** (b) schematically shows the component for the ultimate scaling [1.22]. The three key ingredients are: (1) the nanowire channel with GAA architecture, (2) enhanced transportation in the channel, and (3) the high- $\kappa$  gate dielectrics. In the following section, we will discuss the role of interface and near-interface bulk traps in the realization of this "the ultimate component".

## 1.2.5 AlGaN/GaN based HEMT for high-frequency, high-power application

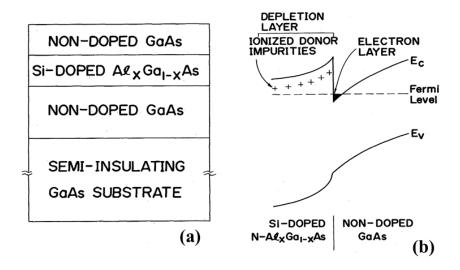

High-Electron mobility Transistor (HEMT), using GaAs and AlGaAs based heterojunctions, was invented by Prof. Mimura around 1980 [1.23-1.25], which has already become one of the mainstream technology for high-frequency electronics. The first experimental demonstration of HEMT [1.24] is based on the heterojunction structure based on alternative thin layers of n-type AlGaAs and undoped GaAs, as shown in **Fig. 1.18** (a). At the interface of n-type AlGaAs and GaAs, due to the higher electron affinity of GaAs, the electrons in the n-type AlGaAs layer can move into the GaAs potential wells. As a result, the near interfacial layer of the AlGaAs layer is depleted and quasi tow-dimensional (2D) electron gas is formed at the interface of GaAs, as schematically shown by the band diagram in **Fig. 1.18** (b). This 2D electron gas (2DEG) has very high mobility for two reasons: (1) III-V compound semiconductor has the internal property of high electron mobility, and (2) compared to conventional MOSFET, because the mobile electrons is physically separated from the space charge in the depletion region in HEMT, the 2DEG in HEMT is less suffered from the coulomb scattering than that in MOSFET devices.

**Fig. 1.18** (a) The structure of the heterojunction structure used to constitute the field-effect transistor, and (b) The schematic band diagram of the GaAs/n-Al<sub>x</sub>Ga<sub>1-x</sub>As heterojunction

with the illustration of the formation of the tow-dimensional electron gas, adopted from [1.24]

|                             |                      | Si   | SiC  | AlGaAs/ | InAlAs/ | AlGaN/        |

|-----------------------------|----------------------|------|------|---------|---------|---------------|

| Characteristic              | Unit                 |      |      | InGaAs  | InGaAs  | GaN           |

| Bandgap                     | eV                   | 1.1  | 3.26 | 1.42    | 1.35    | 3.45          |

| Mobility                    | cm <sup>2</sup> /V•s | 1500 | 700  | 8500    | 5400    | 1000-<br>2000 |

| Saturated velocity          | 10 <sup>7</sup> cm/s | 1.0  | 2.0  | 1.3     | 1.0     | 1.3           |

| Critical<br>Breakdown field | MV/cm                | 0.3  | 3.0  | 0.4     | 0.5     | 3.0           |

| Thermal conductivity        | W/cm•K               | 1.5  | 4.5  | 0.5     | 0.7     | >1.5          |

| $\epsilon_{ m r}$           |                      | 11.8 | 10.0 | 12.8    | 12.5    | 9.0           |

**Table 1.1** Comparison on critical properties for high-frequency and high-power applications between several semiconductor materials.

Although AlGaN/GaN heterojunction based HEMT is still in its fancy before piratical application, it has already aroused extensive attention due to its outstanding properties for high power and high frequency application [1.26]. As shown by **Table 1.1**, the AlGaN/GaN heterojunction structure shows unique combination of large band-gap, high break-down field, high mobility and saturation velocity, and good thermal conductivity. All of these properties of AlGaN/GaN heterojunction make it as an extremely promising candidate for high power and high frequency electronics.

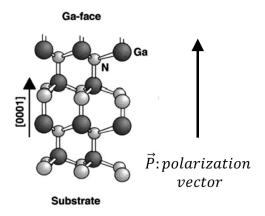

Fig. 1.19. Schematic drawing of the crystal structure of Ga-face GaN. [1.27]

Unlike AlGaAs/GaAs HEMT that requiring intentional doping to from charge, 2DEG in AlGaN/GaN HEMT are induced by the polar nature of AlGaN and GaN, including both of spontaneous and piezoelectric polarization ( $P_{SP}$  and  $P_{PE}$ ), and thus no intentionally doping is needed. Normally, the high-quality GaN epitaxy layers have the crystal structure with Ga-polarity, or Ga-face, as shown in **Fig. 1.19** [1.27, 1.28]. Due to strong noncentrosymmetric crystal structure of the GaN, GaN based compounds show strong spontaneous polarization. Besides, the external strain can also modify the crystal structure of GaN and thus change its polarization. Therefore, GaN based compounds also shows strong piezoelectric polarization.

In  $Al_xGa_{1-x}N/GaN$  heterojunction structure, due to the lattice mismatch between the  $Al_xGa_{1-x}N$  and GaN (**Fig.1.20(a**)), tensile strain is applied to the AlGaN layer after the formation of the heterojunction. As a results, due to the internal spontaneous polarization and the external piezoelectric polarization caused by the strain stored in the the heterjunction, a large amount of the polarization charge appears at the interfaces (**Fig.1.20(b**)). This interfacial polarization charges result in the formation of a high concentration of 2DEG in the interface of the heterojunction (**Fig.1.20(c**)). Therefore, the 2DEG can be formed in the AlGaN/GaN heterojunction without intentional doping. Besides, comparing the schematic band diagram of n-type AlGaAs/GaAs (**Fig.1.18(b**)) and AlGaN/GaN (**Fig.1.20(c**)), it can be seen that due to the 2DEG is caused by depletion of the

donors in the n-type AlGaAs in the previous one and that in the later one is caused by the polarization induced charge-sheet, stronger conduction band discontinuity, or "sharper" quantum well, can be found at the interface of AlGaN/GaN heterojunction. This means the distribution of electron gas in the AlGaN/GaN is closer to the ideally two-dimensional distribution, which suggests that higher mobility could be achieved.

**Fig. 1.20**. (a) Schematic illustration of the lattice mismatch between AlGaN and GaN, (b) Schematic drawing of the polarization interface charge and the 2DEG in AlGaN/GaN heterojunction, and (c) band diagram of the AlGaN/GaN heterostructure with the illustration of polarization interface charge induced by spontaneous and piezoelectric polarization and the 2DEG formed in the quantum well at the interface between AlGaN and GaN.

# 1.3 Interface traps and near interfacial bulk traps: origin, properties and influences.

**Fig. 1.21** (a) Illustration of the spatial distribution of interface traps and near interfacial bulk traps in MOSFETs, (b) Extremely simplified equivalent circuit to clarify the influence of interface traps and near interfacial bulk traps, and (c) Schematic comparison between the  $I_d$ - $V_g$  characteristics of the MOSFETs with and without traps in the gate stacks.