# T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

# 論文 / 著書情報 Article / Book Information

| 題目(和文)            | 革新的なFPGAアクセラレータのための効率的な開発基盤                                                                                                                                                                    |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | Efficient Development Infrastructure for Innovative FPGA Accelerators                                                                                                                          |

| 著者(和文)            | 小林諒平                                                                                                                                                                                           |

| Author(English)   | Ryohei Kobayashi                                                                                                                                                                               |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第10238号,<br>授与年月日:2016年3月26日,<br>学位の種別:課程博士,<br>審査員:吉瀬 謙二,横田 治夫,宮崎 純,金子 晴彦,渡部 卓雄                                                                         |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第10238号,<br>Conferred date:2016/3/26,<br>Degree Type:Course doctor,<br>Examiner:,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                           |

| Type(English)     | Doctoral Thesis                                                                                                                                                                                |

Tokyo Institute of Technology Department of Computer Science

# Efficient Development Infrastructure for Innovative FPGA Accelerators

## (革新的な FPGA アクセラレータのための 効率的な開発基盤)

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Engineering

Ryohei Kobayashi

March 2016

Graduate School of Information Science and Engineering Department of Computer Science Tokyo Institute of Technology

# Abstract

Computer systems have been continuously improved throughout the years, and they tend to employ fabrics such as FPGAs and GPUs to accelerate some computing tasks that normally run on general-purpose CPUs. FPGA-based accelerators can achieve higher performance and better power efficiency than implementations on CPUs and GPUs because designers can implement circuits that realize applicationspecific pipelined hardware and data supply systems. This thesis presents a novel infrastructure supporting efficient development of FPGA-based accelerators. This shows how to build high-performance accelerators targeting several fundamental applications, and enables high-speed RTL simulation to verify that a designed accelerator works as intended.

The first contribution of this work is to propose a high performance FPGA-based accelerator for 2D stencil computation. In the last several decades, stencil computation has been accelerated by using multicore microprocessors and GPUs. However, sustained performance is limited due to memory bandwidth restriction, and also because the computation kernel has small arithmetic intensity. To address this problem, I propose a high performance architecture for 2D stencil computation employing multiple small FPGAs. In this architecture, the data set is divided into multiple blocks and each block is assigned to each FPGA, which means that the data set is stored in FPGA internal memory instead of in an external DRAM. This also means that the according to this architecture, the number of connected FPGAs scales with the size of the data set. The proposed stencil computation hardware was implemented with HDL, and I confirmed that the developed hardware accurately worked. The evaluation result shows that the proposed accelerator achieves even better power efficiency than a typical GPU.

The second contribution of this work is to propose an FPGA-based sorting accelerator, which combines the sorting network and the merge sorter tree. The proposed sorting hardware is customizable by means of tuning design parameters. I also provide an analytical model that accurately estimates the sorting performance depending on the hardware configuration. In other words, designers can estimate sorting accelerator performance in advance and can implement the best one that fulfills cost and performance constraints. I also propose a data compression mechanism for the sorting accelerator to mitigate memory bandwidth limitation. Similar to the stencil-computation accelerator, I developed the proposed sorting accelerator with HDL, and confirmed that the developed hardware actually achieved the estimated performance and higher performance than a typical desktop computer. In order to allow every designer to easily and freely use this accelerator, the RTL source code is released as an open-source hardware.

Finally I summarized important points for the efficient development infrastructure of FPGA-based accelerators according to the two previous contributions. For development of FPGA accelerators, designers implement logic circuits with HDL and verify the circuit behavior. However, designing large-scale circuits leads to long RTL simulation times, which means that traditional RTL simulators cannot finish the circuit behavior verification within a realistic time frame. To address this problem, I propose a high-speed RTL simulator employing two prior studies. I evaluated it in terms of the RTL simulation speed by using the designs of the two proposed accelerators, and confirmed that it could do the RTL simulation much faster than a commercial one. Also, I discussed that the findings obtained from the development of the two FPGA-based accelerators are useful in other hardware platforms and computation kernels.

# Contents

| 1   | In    | troduction                                                               | 1  |

|-----|-------|--------------------------------------------------------------------------|----|

| 1.1 | Motiv | vation                                                                   | 1  |

| 1.2 | Contr | ribution                                                                 | 3  |

| 1.3 | Outli | ne of This Thesis                                                        | 4  |

| 2   | FI    | PGA-based Accelerators                                                   | 6  |

| 2.1 | FPGA  | A: Field Programmable Gate Array                                         | 6  |

|     | 2.1.1 | FPGA Architecture                                                        | 7  |

|     | 2.1.2 | FPGA Design Flow                                                         | 9  |

| 2.2 | Point | s of Interest for developing FPGA-based Accelerators                     | 10 |

| 2.3 | Deve  | lopment Frameworks for FPGA-based Accelerators                           | 12 |

|     | 2.3.1 | High-Level Synthesis                                                     | 12 |

|     | 2.3.2 | System Development Using Domain Specific Language                        | 13 |

|     | 2.3.3 | Discussion                                                               | 14 |

| 2.4 | Throu | ughput Computing Kernels                                                 | 15 |

| 2.5 | Sumr  | mary                                                                     | 17 |

| 3   | А     | Scalable Stencil-computation Accelerator by Employing Multiple Small FP- |    |

|     | G     | As                                                                       | 19 |

| 3.1 | Motiv | vation                                                                   | 19 |

| 3.2 | Stenc | cil Computation                                                          | 20 |

| 3.3 | Key l | Issues of FPGA Array System                                              | 21 |

|     | 3.3.1 | ScalableCore System                                                      | 21 |

|     | 3.3.2 | Preliminary Evaluation regarding Clock Variation Problem                 | 22 |

| 3.4 | Scala | ble Stencil-computation Methodology Employing Multiple Small FPGAs       | 24 |

|     | 3.4.1 | Data Set Decomposition                                                   | 25 |

|     | 3.4.2 | Computation Order Optimization                                           | 25 |

| 3.5 | Desig | gn of Scalable Stencil-computation Architecture                          | 27 |

|     | 3.5.1 | System Architecture                                                      | 27 |

| 3.6 | Imple | ementation of Scalable Stencil-computation Accelerator                   | 31 |

|     | 3.6.1 | Development Flow of Scalable Stencil-computation Accelerator             | 31 |

|     | 3.6.2 | Identification of Location Information                                   | 32 |

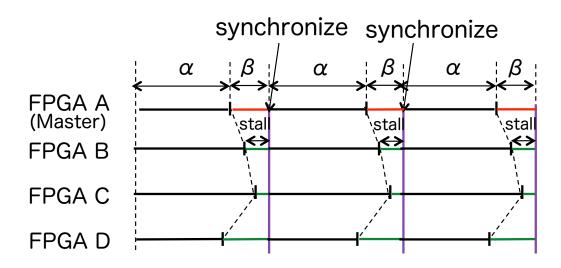

|     | 3.6.3 | Synchronization Mechanism to Address Clock Variation Problem                | 33 |

|-----|-------|-----------------------------------------------------------------------------|----|

| 3.7 | Eval  | uation                                                                      | 35 |

|     | 3.7.1 | Setup                                                                       | 35 |

|     | 3.7.2 | Hardware Resource Usage                                                     | 35 |

|     | 3.7.3 | Stencil Computation Performance                                             | 36 |

| 3.8 | Rela  | ted Work                                                                    | 40 |

| 3.9 | Sum   | mary                                                                        | 41 |

| 4   | Α     | High Performance FPGA-based Sorting Accelerator with a Data Compres-        |    |

|     | si    | on Mechanism                                                                | 43 |

| 4.1 | Moti  | vation                                                                      | 43 |

| 4.2 | Sorti | ng Architectures                                                            | 44 |

|     | 4.2.1 | Sorting Network                                                             | 44 |

|     | 4.2.2 | Merge Sorter Tree                                                           | 45 |

| 4.3 | Prop  | osed Sorting Accelerator                                                    | 48 |

|     | 4.3.1 | Data Path                                                                   | 48 |

|     | 4.3.2 | Control Logic                                                               | 50 |

|     | 4.3.3 | Performance Model                                                           | 52 |

|     | 4.3.4 | Improvement by Duplication of the Merge Sorter Tree                         | 53 |

| 4.4 | Data  | Compression for the Sorting Accelerator                                     | 54 |

|     | 4.4.1 | Algorithm                                                                   | 54 |

|     | 4.4.2 | Adoption of the Data Compression against the Proposed Sorting Accelerator . | 55 |

|     | 4.4.3 | Data Path                                                                   | 56 |

|     | 4.4.4 | Control Logic                                                               | 59 |

| 4.5 | Eval  | uation                                                                      | 60 |

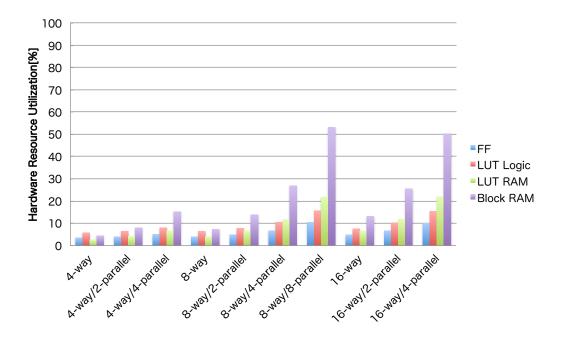

|     | 4.5.1 | Implementation                                                              | 60 |

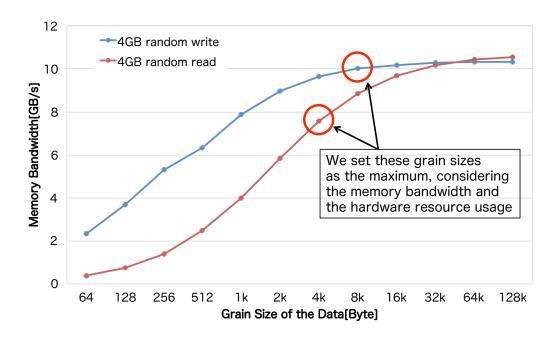

|     | 4.5.2 | Memory Bandwidth                                                            | 61 |

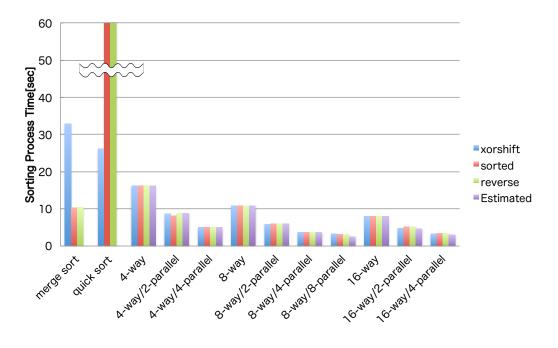

|     | 4.5.3 | Sorting Performance without Data Compression                                | 62 |

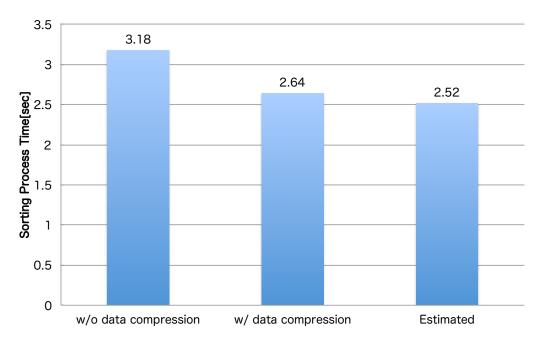

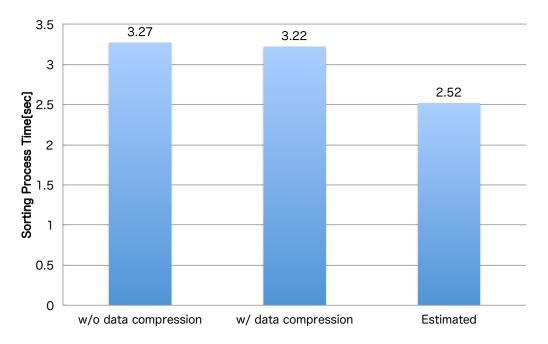

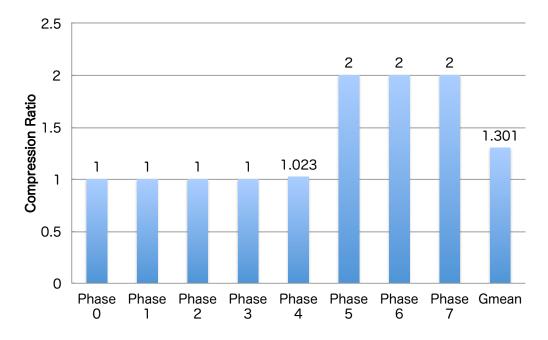

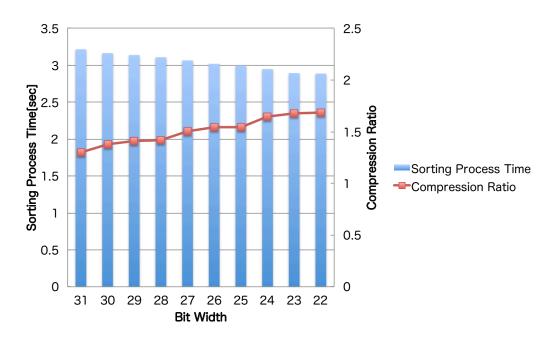

|     | 4.5.4 | Sorting Performance with Data Compression                                   | 65 |

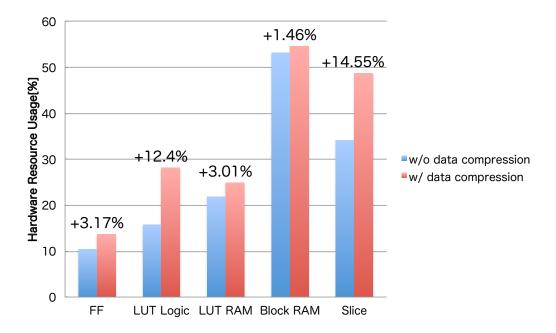

|     | 4.5.5 | Discussion                                                                  | 68 |

| 4.6 | Rela  | ted Work                                                                    | 71 |

| 4.7 | Sum   | mary                                                                        | 72 |

| 5   | E     | ssential Components for Efficient Development Infrastructure                | 73 |

| 5.1 |       | vation                                                                      | 73 |

| 5.2 | High  | n-speed RTL Simulation Overview                                             | 74 |

|     | 5.2.1 | Pyverilog                                                                   | 76 |

|     | 5.2.2 | ArchHDL                                                                     | 77 |

| 5.3 | Arch  | HDL Code Generator                                                          | 80 |

| 5.4 | Eval  | uation                                                                      | 81 |

|         | 5.4.1 Sorting Accelerator               | 1 |

|---------|-----------------------------------------|---|

|         | 5.4.2 Stencil-computation Accelerator   | 4 |

| 5.5     | Related Work                            | 6 |

| 5.6     | Discussion                              | 6 |

|         | 5.6.1 SimVerilog Usability              | 6 |

|         | 5.6.2 Finding Applicability             | 7 |

| 5.7     | Summary                                 | 8 |

| 6       | Conclusion 9                            | 0 |

| 6.1     | Concluding Remarks                      | 0 |

| 6.2     | Open Research Topics                    | 1 |

| Ackno   | wledgement 9.                           | 3 |

| Bibliog | graphy 9:                               | 5 |

| Public  | ation 10-                               | 4 |

| 6.3     | Journal Paper                           | 4 |

| 6.4     | International Conference Paper          | 4 |

| 6.5     | Domestic Conference Paper (with Review) | 4 |

| 6.6     | Technical Report                        | 5 |

| 6.7     | Other Presentation and Poster           | 5 |

|         |                                         |   |

V

# **List of Figures**

| 2.1  | SRAM-based FPGA architecture                                                         | 8  |

|------|--------------------------------------------------------------------------------------|----|

| 2.2  | 4-input LUT realizing X=(A&B) (C&D)                                                  | 8  |

| 2.3  | FPGA design flow overview                                                            | 10 |

| 2.4  | This figure depicts how to implement a logic circuit on an FPGA using an EDA         |    |

|      | tool, which is composed of (a) Synthesis, (b) Technology Mapping, and (c) Place      |    |

|      | and Route.                                                                           | 11 |

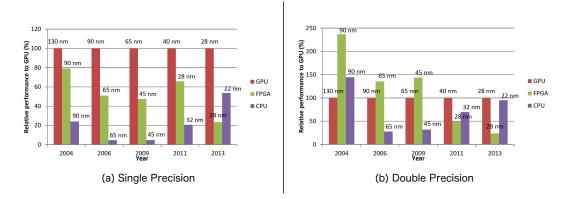

| 2.5  | Peak performance of FPGA and CPU relative to GPU for (a) single precision and (b)    |    |

|      | double precision cited from [15]                                                     | 11 |

| 2.6  | Stencil computation and sorting are fundamental operations for many applications     | 16 |

| 3.1  | The pseudo code of kernel part for stencil computation                               | 20 |

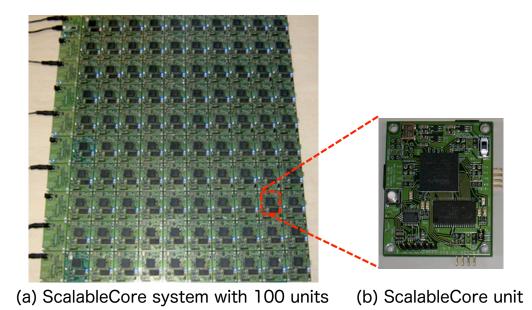

| 3.2  | Photo of ScalableCore system with 100 units (a) and Scalable Core unit (b)           | 21 |

| 3.3  | Clock variations by measuring 20 seconds                                             | 23 |

| 3.4  | Data set decomposition for stencil computation with many FPGAs                       | 24 |

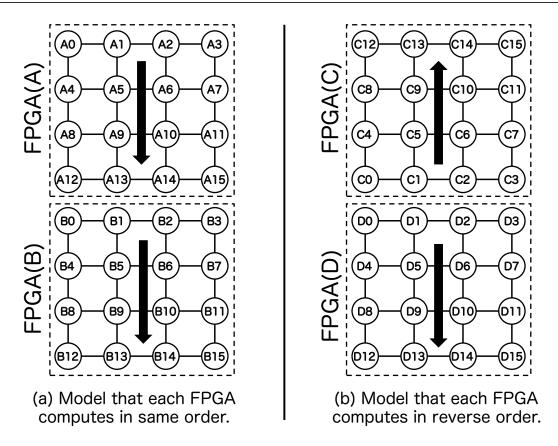

| 3.5  | Calculation order of conventional method (a) and proposed method (b) for the two     |    |

|      | FPGA stencil computation                                                             | 26 |

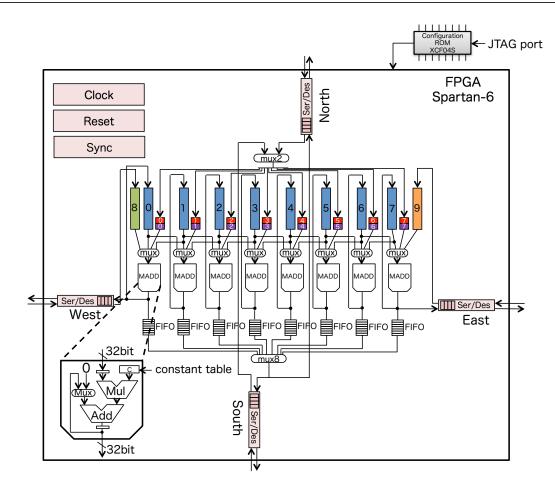

| 3.6  | System architecture of a single FPGA node for the scalable stencil-computation ac-   |    |

|      | celerator                                                                            | 28 |

| 3.7  | Relationship of Block RAM and values in a single FPGA node                           | 29 |

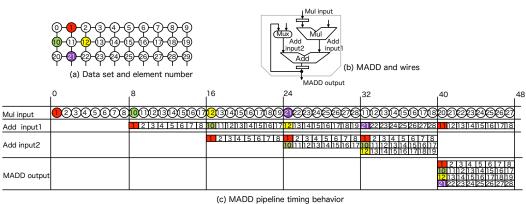

| 3.8  | Pipelining of multiply and add unit for floating-point numbers                       | 29 |

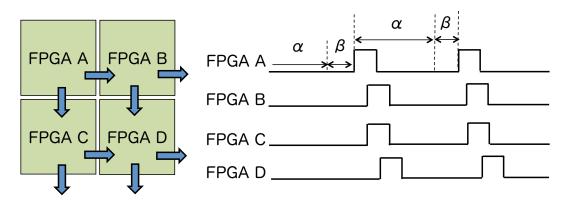

| 3.9  | The configuration of the implemented scalable stencil-computation accelerator        | 32 |

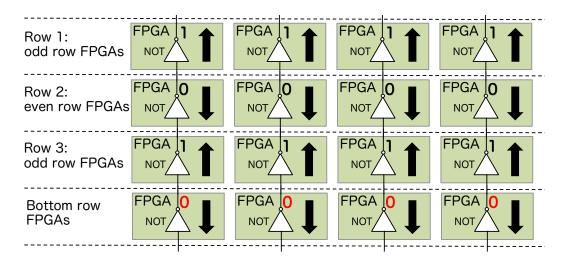

| 3.10 | The mechanism to identify odd/even row FPGAs                                         | 33 |

| 3.11 | Synchronization mechanism to deal with the variation of clock oscillators            | 34 |

| 3.12 | Implementation of synchronization mechanism to deal with the variation of clock      |    |

|      | oscillators                                                                          | 34 |

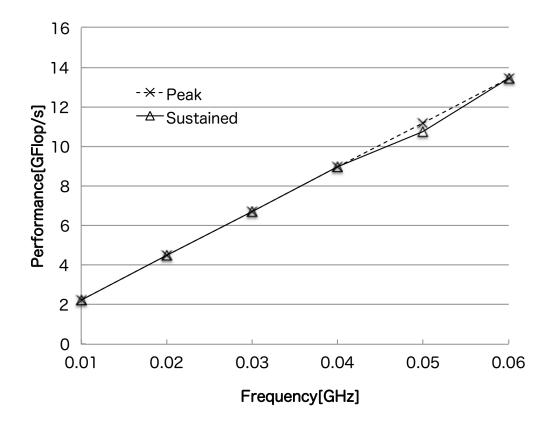

| 3.13 | Sustained performance and peak performance of stencil calculation in the FPGA array  |    |

|      | of 16 nodes                                                                          | 36 |

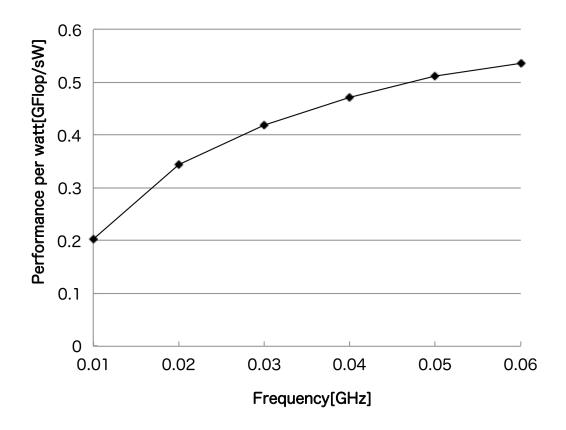

| 3.14 | Computation performance per watt in FPGA array of 16 nodes                           | 37 |

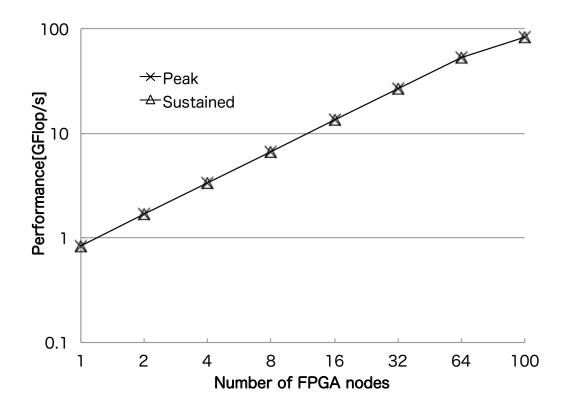

| 3.15 | Sustained performance and peak performance of stencil calculation running $60 MHz$ . | 38 |

| 3.16 | Computation performance per watt in FPGA array running 60MHz                         | 39 |

| 4.1  | Bubble sort network with 4-inputs and 4-outputs                                                | 45 |

|------|------------------------------------------------------------------------------------------------|----|

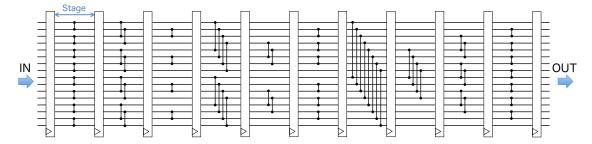

| 4.2  | Pipelined synchronous Batcher's odd-even merge sort network with 16-inputs and                 |    |

|      | 16-outputs                                                                                     | 45 |

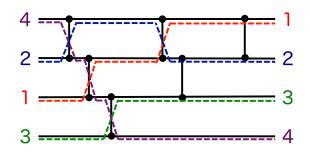

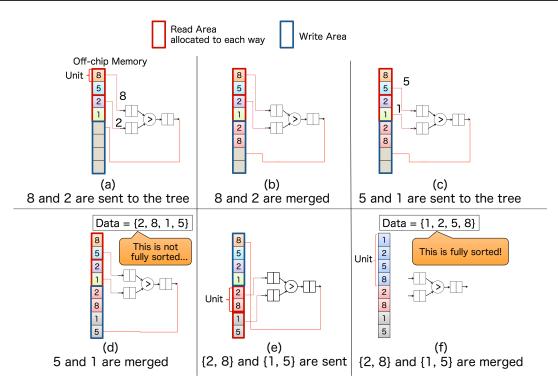

| 4.3  | Sorting process in merge sorter tree                                                           | 46 |

| 4.4  | The merge sorter tree and off-chip memory. The tree sorts the initial data sequence            |    |

|      | {8, 5, 2, 1} by using the memory                                                               | 47 |

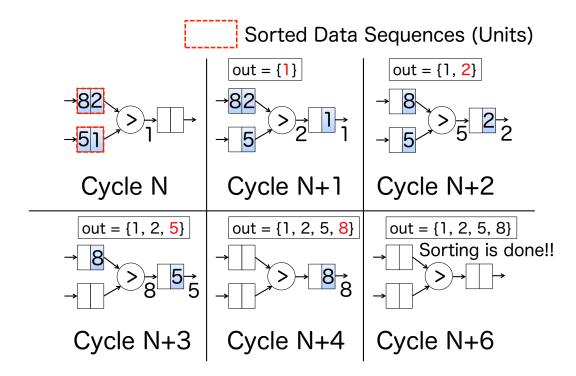

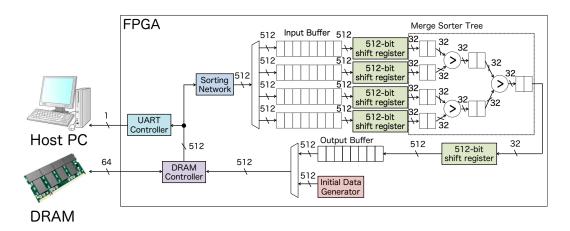

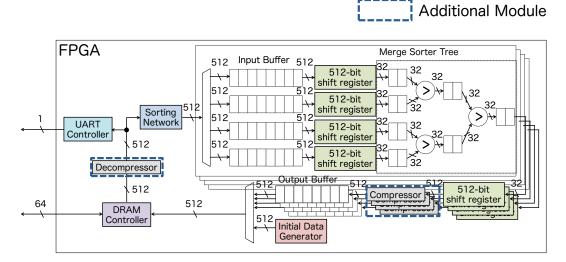

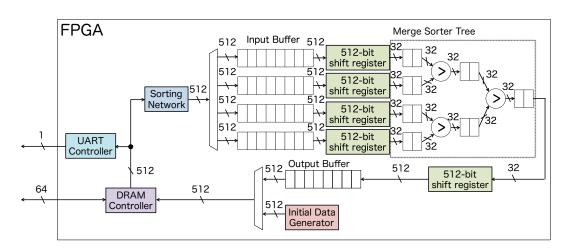

| 4.5  | Data path of the baseline sorting accelerator of FACE                                          | 48 |

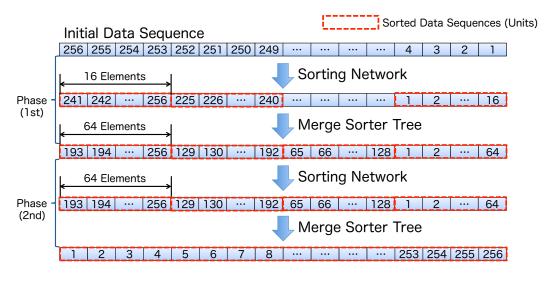

| 4.6  | Example: sorting 256 elements from 256 to 1                                                    | 48 |

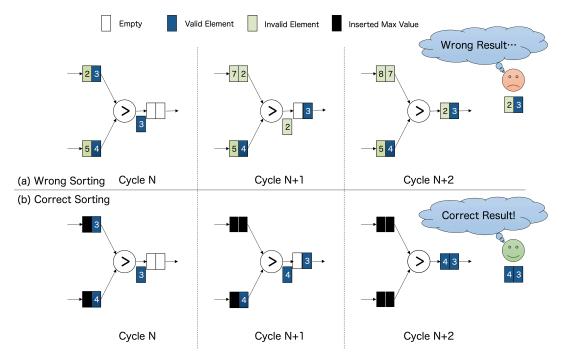

| 4.7  | Wrong sorting and correct sorting                                                              | 50 |

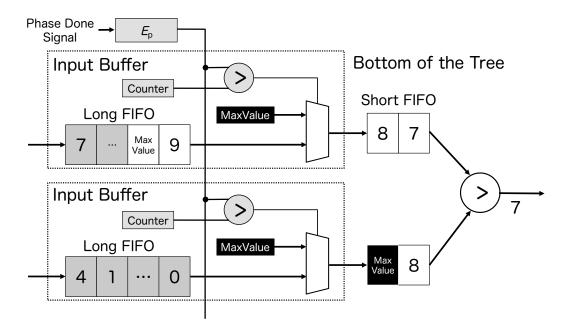

| 4.8  | Two input buffers and one sorter cell                                                          | 51 |

| 4.9  | How to generate reset signal from output buffer                                                | 51 |

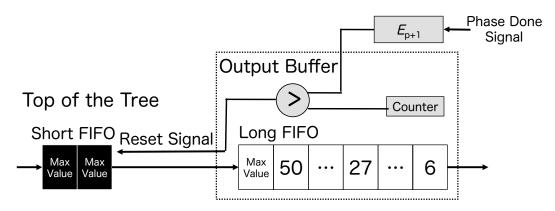

| 4.10 | Data path of the proposed sorting accelerator with the duplicated merge sorter trees .         | 53 |

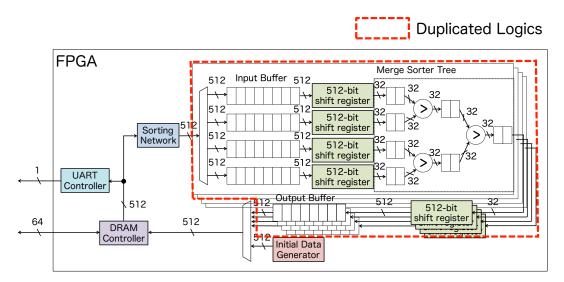

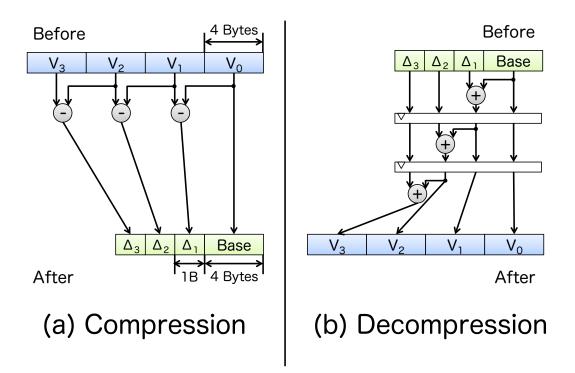

| 4.11 | Example of the compressor and decompressor method that is described in [91]. In                |    |

|      | this example, 4Bytes values are compressed into a 4Bytes base and an array of 1Byte $\Delta$ . | 55 |

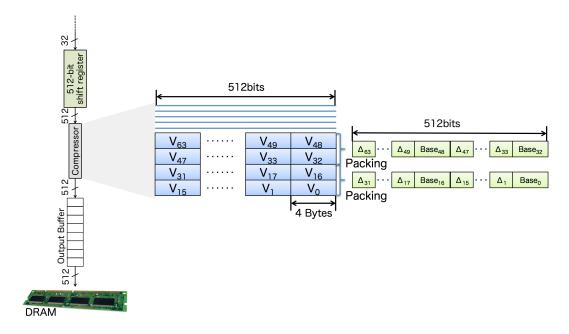

| 4.12 | Adoption of the data compression                                                               | 56 |

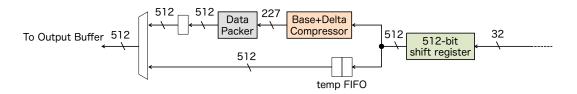

| 4.13 | Data path of the proposed sorting accelerator with the compressor and decompressor.            | 57 |

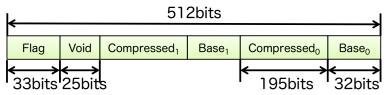

| 4.14 | The encoding format for the 2x compression                                                     | 57 |

| 4.15 | Modified compression and decompression designs based on the prior work. In this                |    |

|      | diagram, 4Bytes values are compressed into a 4Bytes base and an array of 1Byte $\Delta$ .      | 58 |

| 4.16 | Data path of the compressor                                                                    | 58 |

| 4.17 | Data path of the decompressor                                                                  | 58 |

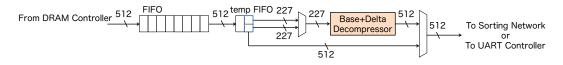

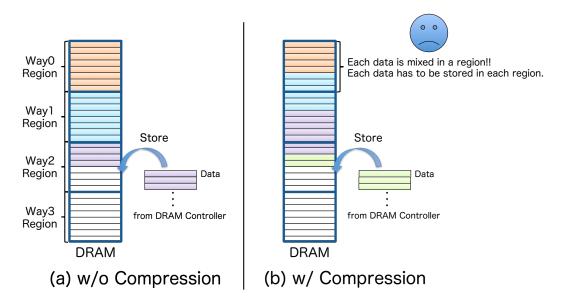

| 4.18 | The data emitted from the merge sorter tree is sequentially written into the head of the       |    |

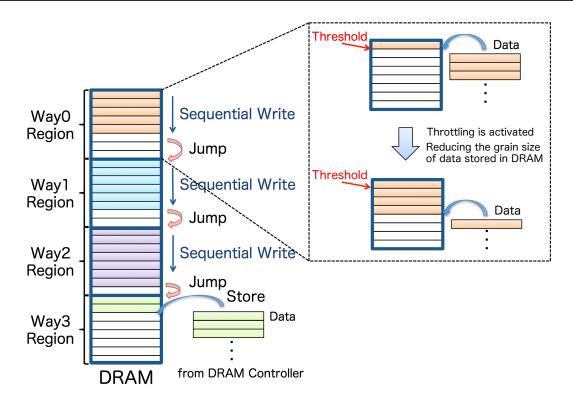

|      | Write Area, without (a) and with (b) the data compression.                                     | 60 |

| 4.19 | Writing the data emitted from the merge sorter tree by Throttling                              | 61 |

| 4.20 | The memory bandwidth when randomly reading and writing 4GB data, depending on                  |    |

|      | grain size of the read and written data                                                        | 62 |

| 4.21 | Sorting performance comparison between the software and the proposed sorting ac-               |    |

|      | celerator                                                                                      | 63 |

| 4.22 | Hardware resource usage of the proposed sorting accelerator                                    | 64 |

| 4.23 | The sorting performance of 8-way/8-parallel with and without the data compression              |    |

|      | mechanism when the initial data-sequence types is a reverse-order sorted data sequence         | 65 |

| 4.24 | The sorting performance of 8-way/8-parallel with and without the data compression              |    |

|      | mechanism when the initial data-sequence types is a random data sequence using                 |    |

|      | Xorshift                                                                                       | 66 |

| 4.25 | The data compression ratio in each Phase of 8-way/8-parallel                                   | 67 |

| 4.26 | The sorting process time and average compression ratio using a random data sequence            |    |

|      | with small deltas                                                                              | 68 |

| 4.27 | The hardware resource usage of 8-way/8-parallel with and without the data compres-   | 60 |

|------|--------------------------------------------------------------------------------------|----|

|      | sion mechanism                                                                       | 69 |

| 4.28 | Relationship between the performance and the hardware resource usage                 | 70 |

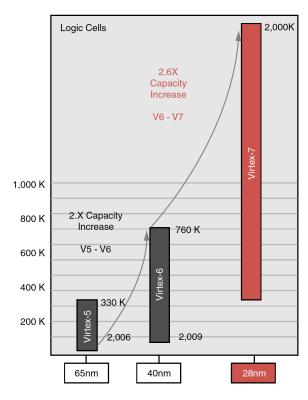

| 5.1  | The capacity increase in Xilinx FPGAs cited from [110]                               | 74 |

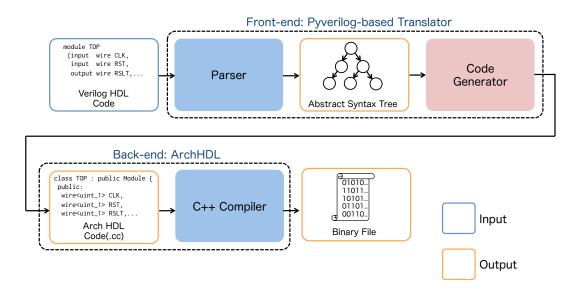

| 5.2  | SimVerilog overview. I implement Code Generator to produce ArchHDL code from         |    |

|      | the generated abstract syntax tree by analyzing Verilog HDL source code with Parser. | 75 |

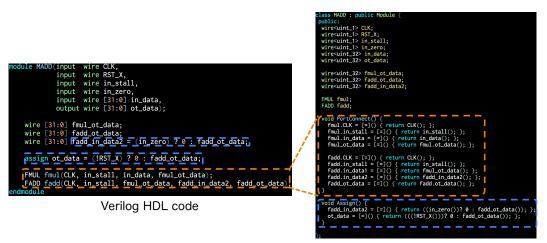

| 5.3  | The correspondence relationship between Verilog HDL and ArchHDL                      | 75 |

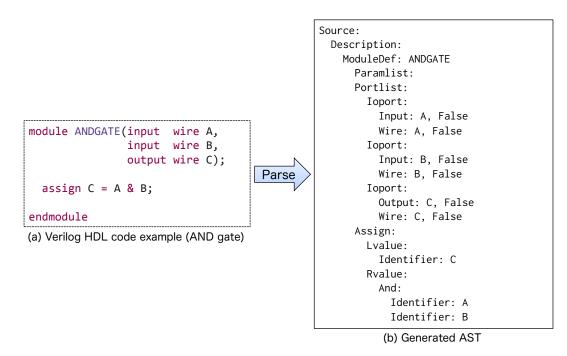

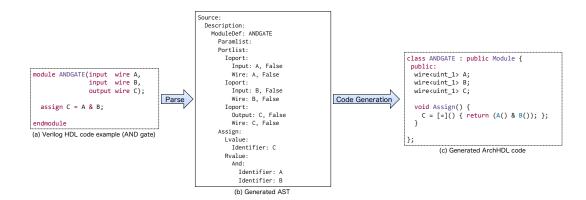

| 5.4  | Pyverilog analyzes (a) the Verilog HDL source code of AND gate and generates (b)     |    |

|      | the Abstract Syntax Tree (AST).                                                      | 76 |

| 5.5  | Xorshift pseudo random value generator and test bench in ArchHDL                     | 78 |

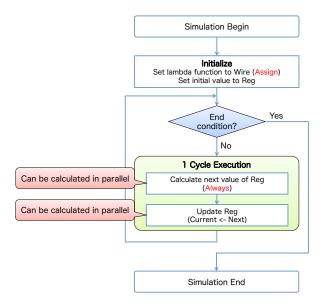

| 5.6  | Simulation flow chart of ArchHDL                                                     | 79 |

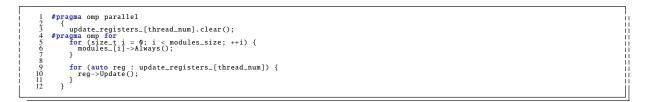

| 5.7  | Simulation kernel of ArchHDL using OpenMP                                            | 79 |

| 5.8  | The overview of ArchHDL code generation from Verilog HDL source code                 | 80 |

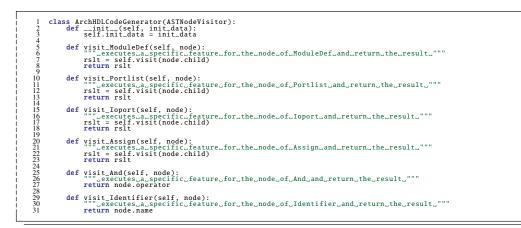

| 5.9  | The visitor pattern for the generated AST from Verilog HDL source code in Python .   | 80 |

| 5.10 | The implementation of ArchHDL code generator inheriting ASTNodeVisitor illus-        |    |

|      | trated in Figure 5.9                                                                 | 80 |

| 5.11 | The proposed sorting accelerator with 4-way merge sorter tree                        | 82 |

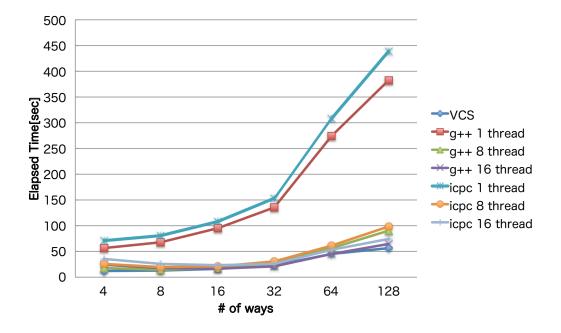

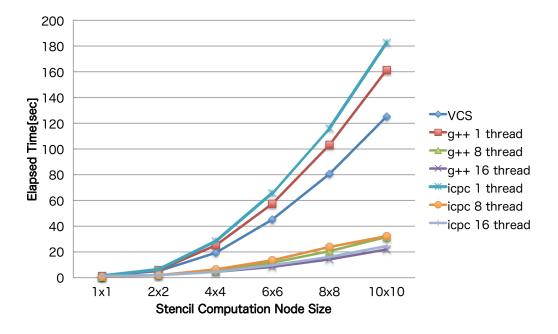

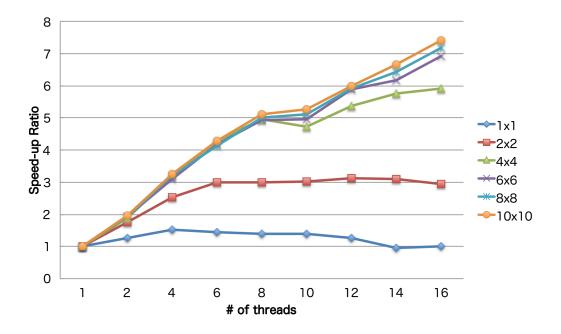

| 5.12 | Simulation time of VCS and SimVerilog using OpenMP, depending on each hardware       |    |

|      | running 256K elements sorting                                                        | 82 |

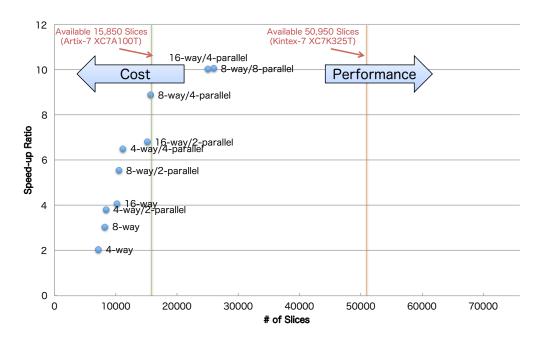

| 5.13 | Speed-up ratio compared with g++ single thread in each hardware running 256K         |    |

|      | elements sorting                                                                     | 83 |

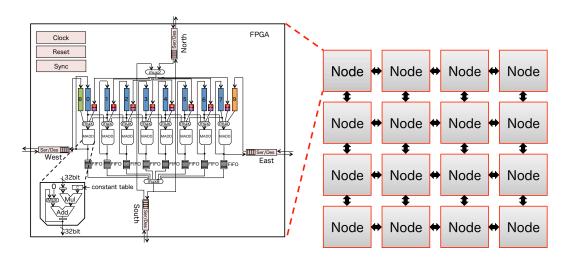

| 5.14 | The proposed stencil-computation accelerator composed of $4 \times 4$ nodes          | 84 |

| 5.15 | Simulation time of VCS and SimVerilog using OpenMP, depending on each hardware       |    |

|      | configuration for stencil computation                                                | 84 |

| 5.16 | Speed-up ratio compared with g++ single thread in each hardware configuration for    |    |

|      | stencil computation                                                                  | 85 |

| 5.17 | Hardware platform example: an FPGA and two DRAMs                                     | 87 |

# **List of Tables**

| 2.1 | Programming technology characteristics                          | 7  |

|-----|-----------------------------------------------------------------|----|

| 2.2 | Throughput computing kernel characteristics cited from [68]     | 15 |

| 3.1 | Worst value and standard deviation of measured clock variations | 22 |

| 3.2 | Hardware resources usage in a single FPGA                       | 35 |

| 5.1 | Evaluation setup                                                | 81 |

# Chapter 1 Introduction

### **1.1 Motivation**

Computer systems are essential components to sustain the information age, and are nowadays used for lots of fields from scientific technologies to those we use in daily life, like weather forecast, drug development, financial engineering, artificial intelligence, automotive, smart phones, gaming machines, etc. Human beings have received these benefits that are thanks to performance improvements of computer systems. To make the future of the world more bright and prosperous, it is the key to research how to build innovative computer systems and how to apply them to practical matters.

To achieve high performance computer systems, one of the key components is a microprocessor, which is also called Central Processing Unit (CPU). In the past, a microprocessor consists of a singlecore, and the performance improvements of microprocessors had relied on high clock rates and hardware features exploiting inherent instruction-level parallelism (ILP). However the performance improvements reached the limit in the late of 2000s. This is mainly because the power consumption and calorific value are not trivial. Besides it has been challenging to improve ILP by complex hardware components and this approach can cause more power consumption. Therefore, instead of a single-core processor, multi-core and many-core processors have become mainstream, accelerating applications by parallel processing like exploiting thread-level parallelism. The number of cores has been increased year after year due to improvements of semiconductor integration technologies depending on Moore's Law [1], and many-core processors with up to 256 cores begin to appear [2, 3, 4].

Not only CPUs but also other components like memory systems have also been advanced. In particular, graphics performance has been significantly improved thanks to technology evolution of Graphics Processing Unit (GPU). Although GPUs are originally specialized in image processing, in recent years they have been used for the high performance computing, known as General-Purpose computing on GPU (GPGPU). This is because GPU has even more parallel processing elements than CPU, and the high-performance computing kernels frequently have inherent data-level parallelism that GPUs can efficiently exploit. Their large parallel computing capability enables powerful scientific simulations like linear algebra [5]. In modern supercomputers, GPUs have been seriously employed such as in TSUBAME2.5 [6], HA-PACS [7], etc.

CPU and GPU computation capabilities have been improved year by year, but their performance cannot be 100% delivered depending on application characteristics. For instance, authors in [8] can only exploit 21.8% of peak performance of two Intel Xeon E5220 CPUs for stencil computation used in fluid dynamics. Phillips et al. [9] propose a stencil computation approach using NVIDIA TESLA C1060 GPU, and the sustained performance of a single GPU is 65.6% of the peak performance, and worse, a GPU cluster composed of 16 GPUs can work at only 42.2% of the cluster peak performance. These low performance efficiencies are due to multicores and GPUs architectural aspects including memory bandwidth limitations. Besides CPUs and GPUs are prone to face power efficiency problems [10, 11] in not only stencil computation, and it is necessary to tackle these problems in order to realize computer systems of the future.

To address them, Field-Programmable Gate Array (FPGA) based accelerators have been attractive in recent years. FPGA is a programmable LSI on which designers can implement any desired digital circuit, and FPGA-based accelerators can achieve higher performance and better power efficiency than implementations on CPUs and GPUs because designers can implement circuits that realize applicationspecific pipelined hardware and data supply systems. For instance, in [12], an FPGA-based system to accelerate data center tasks is proposed. This system improves PageRank throughput of "Bing" as much as 195%. [13] presents a dedicated hardware to accelerate stencil computation that is used in several fields, such as fluid calculation, weather calculation, molecular simulation, etc. The proposed hardware is implemented by using multiple FPGA boards. The accelerator obtains higher computational performance at up to 13.7x compared with Intel Core i7-3930K with six cores operating at 3.2GHz, and the power efficiency is about 7x better than [10]. In June 2015 Intel Corporation announced the acquisition of Altera Corporation that is one of the biggest FPGA vendors in the world. Intel aims to accelerate database operations using FPGA integrated into Xeon processors [14], and will ship its first Xeon server chip with a programmable FPGA from Altera in the first quarter 2016. A lot of companies and research institutes have given considerable attention to FPGAs, and from now on the hybrid computing model based on CPUs, GPUs and FPGAs seriously begins [15].

To exploit the remarkable potentials of FPGA-based accelerators, it is truly necessary to consider how to build them. In other words, designers have to pay attention to an appropriate FPGA device, hardware design, and implementation depending on application characteristics. Another obstacle is to need long simulation times for circuit behavior verification. For development of FPGA accelerators, designers usually implement logic circuits with Hardware Description Language (HDL) and verify that the circuit behavior is as intended. However, designing large-scale circuits leads to long Register Transfer Level (RTL) simulation times, which means that traditional RTL simulators cannot finish the circuit behavior verification within a realistic time frame. Besides, FPGAs have become larger and larger due to transistor scaling and stacking, and it enables implementation of larger hardware on FPGAs. However the simulation time is also larger, and that is why high-speed simulation environments are required.

This thesis presents a novel infrastructure supporting efficient development of FPGA-based accelerators. The proposed infrastructure shows how to build high-performance FPGA-based accelerators targeting fundamental applications and enables high-speed RTL simulation to verify whether or not a designed accelerator works as intended. The evaluation results show that designed FPGA-based accelerators outperform corresponding implementation on CPUs and GPUs in terms of both performance and power efficiency.

### **1.2** Contribution

The contributions of this thesis are as follows:

- I propose a high performance FPGA-based accelerator for 2D stencil computation employing multiple small FPGAs.

- In this architecture, the data set is divided into multiple blocks and each block is assigned to each FPGA, which means that the data set is stored in FPGA internal memory instead of in an external DRAM. This also means that the according to this architecture, the number of connected FPGAs scales with the size of the data set. To realize the proposed accelerator, I developed a computation order optimization mechanism considering location information of each FPGA, a deeply pipelined stream computation unit, and a synchronization mechanism to absorb clock variations between FPGAs. The proposed stencil computation hardware was implemented with Hardware Description Language (HDL), and I confirmed that the developed hardware accurately worked. The evaluation result shows that the proposed accelerator accelerator achieves even better power efficiency than a typical GPU.

- I propose an FPGA-based sorting accelerator that combines the sorting network and the merge sorter tree.

- The proposed sorting hardware is customizable by means of tuning design parameters. I also provide an analytical model that accurately estimates the sorting performance depending on the hardware configuration. In other words, designers can estimate sorting accelerator performance in advance and can implement the best one that fulfills cost and performance constraints. Similar to stencil-computation accelerator, I developed the proposed sorting accelerator with HDL, and confirmed that the developed hardware actually achieved the estimated performance and higher performance than a typical desktop computer. Be-

sides, I propose a data compression mechanism for the sorting accelerator to mitigate memory bandwidth limitation, and the evaluation results show that the sorting accelerator with the mechanism achieves better performance than without it. In order to allow every designer to easily and freely use this accelerator, the RTL source code is released as an open-source hardware.

- I propose a novel infrastructure to show how to build high-performance FPGA-based accelerators targeting fundamental applications and to enable high-speed RTL simulation to verify that developed hardware works as intended.

- Based on the two previous contributions, I summarized important points for the efficient development infrastructure of FPGA-based accelerators. To shorten long RTL simulation times required to verify a designed circuit behavior, I propose a high-speed RTL simulator. I evaluated it in terms of the RTL simulation speed by using the designs of the two proposed accelerators, and confirmed that it could do the RTL simulation much faster than a commercial one. Also, I discussed that the findings obtained from the development of the two FPGA-based accelerators are beneficial in other hardware platforms and computation kernels.

## **1.3** Outline of This Thesis

This thesis consists of six chapters and is organized as follows.

In Chapter 2, I describe the fundamental knowledge of the FPGA-based accelerator and the background of my work. At first I briefly introduce the FPGA history, architecture and how to develop desired hardware on FPGAs and then discuss the point of interest for developing FPGA accelerators and the pros and cons of previously proposed development frameworks. Besides, I look into important computation kernels and explain that stencil computation and sorting are appropriate ones to be accelerated.

In Chapter 3, I describe the first main contribution of this work, which is to propose a high performance FPGA-based accelerator for 2D stencil computation employing multiple small FPGAs. In this architecture, the number of connected FPGAs scales with the size of the data set. I detail the design and implementation, and the evaluation results show that the proposed accelerator achieves even better power efficiency than a typical GPU.

In Chapter 4, I propose an FPGA-based sorting accelerator that combines the sorting network and the merge sorter tree, which is the second main contribution of this work. The proposed sorting hardware is customizable by means of tuning design parameters and I also provide an analytical model that accurately estimates the sorting performance depending on the hardware configuration. I detail the design

and implementation, and the evaluation result shows that the developed hardware actually achieves the estimated performance and higher performance than a typical desktop computer. Additionally, I propose a data compression mechanism for the sorting accelerator to mitigate memory bandwidth limitation.

In Chapter 5, I describe a novel infrastructure to show how to build high-performance FPGA-based accelerators targeting fundamental applications and to enable high-speed RTL simulation to verify that developed hardware works as intended. Based on the two previous contributions, I list important points for efficient development infrastructure for FPGA-based accelerators. To realize the high-speed RTL simulation, I employ two previously proposed tools; these are Pyverilog and ArchHDL. I briefly introduce the two tools and describe how to use them in the Proposed RTL simulator. The evaluation results show that it is possible to simulate faster the proposed stencil-computation and sorting accelerators behavior compared with a commercial simulator. Also, I discuss that the findings obtained from the development of the two FPGA-based accelerators are useful in other hardware platforms and computation kernels.

Finally in Chapter 6, I conclude this thesis with the discussion of open-research areas.

# Chapter 2 FPGA-based Accelerators

This chapter provides the fundamental knowledge for the FPGA-based accelerator. First I briefly introduce the FPGA history, architecture and how to develop desired hardware on FPGAs and then discuss points of interest for developing FPGA-based accelerators. I also present development frameworks for FPGA-based accelerators previously proposed around the world, along with their pros and cons. Finally, I look into important computation kernels and explain why stencil computation and sorting are appropriate ones to be accelerated, and summarize the motivation of this work.

## 2.1 FPGA: Field Programmable Gate Array

The FPGA is a semiconductor device on which designers can program/reprogram any digital circuit. In 1985, Xilinx invented the first commercially viable FPGA (the XC2064), and engineers paid attention to it. This is because it is attractive to freely reprogram digital circuits since it was commonly accepted that hardware changes are difficult at that time. However these initial FPGAs were small and costly, and were used for only research prototyping and educational system rather than for commercial products. After several decades, FPGA capabilities have been significantly improved thanks to improvements of semiconductor integration technologies and research outcomes of FPGA architecture, and many companies and research institutes have begun to examine the FPGA availability. Given the FPGA characteristic features, FPGAs are mainly used in the three following cases

- as a platform for design and verification of Application Specific Integrated Circuits (ASICs) like CPUs,

- 2. as a hardware component dealing with systems having frequent design changes like image processing systems, network servers, etc.,

- 3. as a hardware accelerator in order to reduce power consumption while increasing performance.

As mentioned before, I focus on and describe the third case in this thesis.

| Programming Technology | Volatile | Reprogrammable | Operating Speed |

|------------------------|----------|----------------|-----------------|

| SRAM-based FPGA        | Yes      | Yes            | Fast            |

| Antifuse-based FPGA    | No       | No             | Fast            |

| Flash-based FPGA       | No       | Yes            | Slow            |

Table 2.1

Programming technology characteristics

#### 2.1.1 FPGA Architecture

FPGAs are composed of programmable logic blocks and interconnection, which means that designers can electrically rewrite logic block contents and their interconnection configuration. Table 2.1 shows programming technologies for FPGAs [16].

SRAM programming technology is based on static memory cells storing a stream of configuration bits for logic block contents and their interconnection. The advantage of this technology is to strongly receive benefits of the semiconductor processes refinement, since this technology can be implemented under the standard CMOS process. Designers can reprogram desired digital circuits a number of times, but once the device is powered down, the configuration data is lost because SRAM is volatile memory. Therefore, this technology needs to reload the configuration data from external flash or EEPROM devices.

Antifuse programming technology is based on structures that exhibit very high-resistance under normal circumstances. By applying a voltage, these high resistances can be 'blown' to create a low resistance link, and this technology can form digital circuits based on the blown connection. Unlike SRAM programming technology, the configuration data is never lost and the implemented circuit is small and works at high speeds and low energy because this technology does not employ SRAM. However, the largest disadvantage is that antifuse-based FPGAs are one-time programmable devices.

Flash programming technology is based not on static memory cells but flash memory cells storing a stream of configuration bits for logic block contents and their interconnection. Unlike SRAM and antifuse programming technologies, this technology does not lose the configuration data and can reprogram digital circuits any times. However, the manufacturing process is complicated and the operating speed is slow since the read speed from the memory is slower than SRAM.

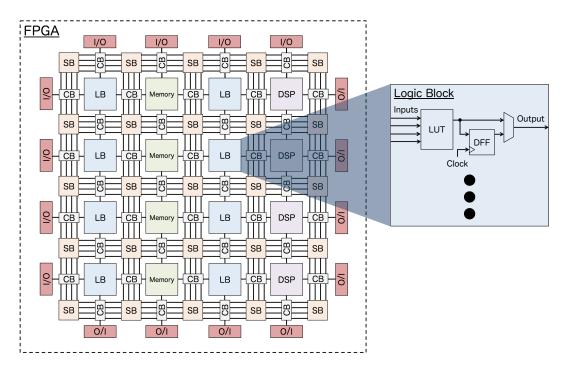

Given these advantages and disadvantages, SRAM-based FPGAs have nowadays become mainstream. Figure 2.1 shows the SRAM-based FPGA architecture. Most of the today's FPGAs consist of arrays of programmable Logic Blocks (LBs) and hard blocks with fixed functionality, like memory and Digital Signal Processor (DSP), which can work faster and can offer more compact implementations of hardware functions than using LBs. The arrays are surrounded by I/O blocks, which connect the FPGA chip to the outside world. These programmable logic blocks, hard blocks, and I/O blocks are all in-

Figure 2.1 SRAM-based FPGA architecture

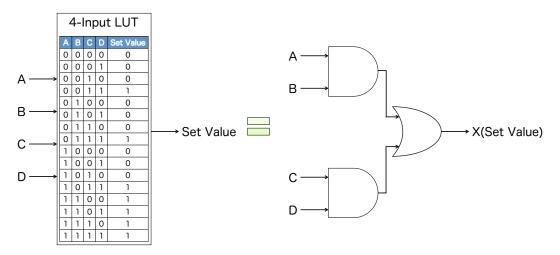

Figure 2.2 4-input LUT realizing X=(A&B)|(C&D)

terconnected using programmable routing fabrics that are Switch Boxes (SBs) and Connection Blocks (CBs). These routing fabrics are composed of 1-bit SRAM cells, and by storing the proper bits in these fabrics, SBs and CBs determine which wire should be connected to another wire and LB/hard block. This two-dimensional mesh interconnected routing architecture is called island-style [17, 18]. Another routing architecture, which is hierarchical [19], was proposed but designers employ island-style for most of the today's FPGAs development because hierarchical usually incurs a significant delay penalty [16].

The programmable logic block is basically composed of Look-Up Tables (LUTs) and D-type Flip Flops (DFF) [18]. LUTs are also composed of 1-bit SRAM cells, and by storing the proper bits in the SRAM cells, various combinational logic functions could be implemented. Figure 2.2 shows one of the examples. The LUT in this figure consists of 16 1-bit SRAM cells and returns a 1-bit value set in an SRAM cell according to the four inputs, which is called 4-input LUT. It realizes a boolean function, which is equal to X=(A&B)|(C&D) where X represents a 1-bit value set in an SRAM cell. To implement sequential circuits like Finite State Machines (FSMs), a DFF is connected to the output of LUTs. The multiplexer is also based on 1-bit SRAM cells, and determines which signal should be emitted depending on the set values.

SRAM-based FPGAs can realize a desired logic circuit by storing proper bits in 1-bit SRAM cells in LBs, SBs, and CBs. To implement a high performance FPGA-based accelerator, it is important to efficiently utilize and connect hard blocks like memory and DSP in addition to LBs.

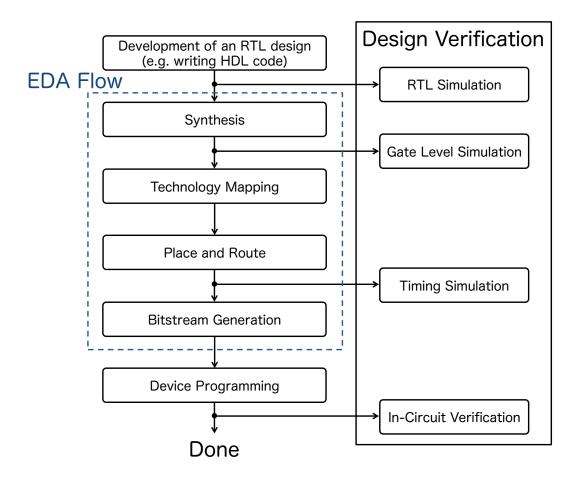

#### 2.1.2 FPGA Design Flow

Figure 2.3 shows a typical FPGA design flow. At first, designers develop a Register Transfer Level (RTL) design after the hardware specifications are determined. To develop the RTL design, Hardware Description Languages (HDLs) like VHDL and Verilog HDL are mostly used. After that, the RTL design can be verified by using commercial [20, 21, 22, 23, 24] or open-source [25, 26, 27, 28] RTL simulators. This is a truly important step to confirm that the design behavior works as intended.

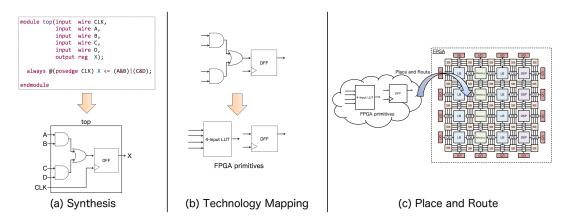

The next step is to create the FPGA circuit image (bitstream) file the RTL design. This step requires a unique Electronic Design Automation (EDA) tool depending on the targeted FPGA device. For instance using Xilinx, Altera, or Lattice FPGAs require ISE/Vivado Design Suite [29, 30], Quartus Prime (Quartus II) [31], or Lattice Diamond [32] respectively. Although this step needs these FPGA vendor's own development tools, it consists of four processes that are Synthesis, Technology Mapping, Place and Route, and Bitstream Generation shown in the dotted line region in Figure 2.3.

In Synthesis, the developed RTL design is translated into the gate-level netlist shown in Figure 2.4 (a), and designers can simulate the logic circuit behavior in more detail (Gate Level Simulation). The next process, Technology Mapping, fits the synthesized design into targeted FPGA primitives. In Figure 2.4 (b), the design is mapped into the two primitives that is a single LUT and flip flop. This is because the combinational logic composed of two AND gates and an OR gate can be translated into an LUT as described in Figure 2.2. After this process, these mapped FPGA primitives are placed and routed to satisfy the required timing performance, which is illustrated in Figure 2.4 (c). Using the timing information generated by Place and Route, designers can more accurately verify the design behavior in Timing Simulation, compared with RTL and Gate Level Simulation. Finally, the placed and routed design information is used to generate the bitstream for the targeted FPGA configuration.

Figure 2.3 FPGA design flow overview

After the EDA flow, designers can program the developed design by downloading the generated bitstream to the targeted FPGA. To confirm that the implemented design on the FPGA correctly works as intended (In-Circuit Verification), designers can use logic analyzers provided by FPGA vendors.

### 2.2 Points of Interest for developing FPGA-based Accelerators

In this section, I explain the points of interest for developing FPGA-based accelerators. Figure 2.5 shows peak floating-point performance of the three devices for single precision and double precision. This figure is cited from [15]. According to Figure 2.5 (a), GPUs are always GPUs have always the best performance for single precision. The most interesting points of Figure 2.5 (a) is that in 2011 both FPGAs and CPUs have increased their relative performance, but in 2013 relative performance of FPGAs is degraded while CPUs keep improving. This is because many-core CPUs like Intel Xeon Phi began to appear. In Figure 2.5 (b), GPUs have dominated the peak performances, except for the first years and the CPUs started to dominate FPGAs from 2011 for double precision. In 2013 the peak

Figure 2.4 This figure depicts how to implement a logic circuit on an FPGA using an EDA tool, which is composed of (a) Synthesis, (b) Technology Mapping, and (c) Place and Route.

Figure 2.5 Peak performance of FPGA and CPU relative to GPU for (a) single precision and (b) double precision cited from [15]

performances of both GPUs and many-core CPUs came close with about 5%.

Peak performance just gives a theoretical comparison. The sustained performance, which is performance achieved when running a particular application, can vary with each particular application and the power efficiency is similar to it. This is because these computing devices have different architectural aspects including the memory architecture with its external memory bandwidth and the communication network, which are more appropriate for specific applications.

For instance, [33] compares sustained performance between NVIDIA Tesla C2090 GPU, Xilinx ZYNQ XC7Z020 FPGA, and Intel Xeon processor in different encryption algorithms. The authors report that the GPU outperforms the CPU by 13x and the FPGA provides a throughput speed-up of 6~9 over the GPU for 8KB and 16KB plaintext blocks. This is because the FPGA has enough capacities to do streaming computation. For larger plaintext sizes, the GPU and FPGA provide similar throughput. [34] compares the implementation of a quasi-Monte Carlo simulation between Xilinx Virtex-4 FPGA,

NVIDIA 8800GTX GPU and a 2.8 MHz Intel Xeon CPU. According to the results, the FPGA outperforms the CPU-based implementation by 2 orders of magnitude. Also, the FPGA achieves around 3x speed-up compared to equivalent the GPU-based implementation. The Power consumption of the FPGA is 336x more energy efficient than the CPU, and 16x more energy efficient than the GPU.

However, depending on application algorithms, hardware designs, and implementation, FPGAs are not always effective. Authors in [5] compare implementations of Black-Scholes between Intel i7-960 CPU, NVIDIA GTX480 GPU and Xilinx Virtex-6 FPGA and conclude that the GPU is about 1.4x faster than the FPGA and 22x faster than the CPU. In power efficiency, the GPU is about 1.3x more power efficient than the FPGA and almost 40x compared to the CPU. The authors also compare implementation dense matrix multiplication between the computing devices and conclude that the GPU with a sustained performance of 541 GFlop/s is about 3x faster than the FPGA and 6x faster than the CPU. Considering power efficiency, both FPGA and GPU are 3x better than that of the CPU. Therefore, it is necessary to consider an appropriate FPGA device, hardware design, and implementation depending on application characteristics, such as a sequential algorithm, an iterative algorithm, data-parallel algorithm or memory intensive algorithm, etc.

### 2.3 Development Frameworks for FPGA-based Accelerators

As mentioned before, in order to develop the RTL design, HDLs like VHDL and Verilog HDL are mostly used. However unfortunately, these HDLs hardly have the high-level and abstraction facilities commonly found in modern mainstream languages. Because of this, the FPGA development can be tedious, inefficient and error-prone for non-expert designers, what is worse, it might also affect expert FPGA designers from the productivity point of view [35, 36]. To address this problem, many development approaches have been proposed by many companies and research institutes in the world.

#### 2.3.1 High-Level Synthesis

High-Level Synthesis (HLS) languages and tools are emerging as the most promising technique to provide higher the programmability for FPGA-based hardware development and to make FPGAs more accessible to software developers. HLS techniques translate software languages like C language into RTL designs [37, 38, 39, 40, 41, 42, 43, 44, 45, 46, 47, 48, 49].

These days, there are a lot of available commercial HLS languages and tools. Xilinx Vivado HLS [37] can accelerate IP cores creation by enabling C, C++ and SystemC specifications to be directly targeted into Xilinx FPGAs without the need to manually create RTL. This tool has been a commercial product so far, but becomes free of charge and gets included in all Vivado software editions from Vivado Design Suite 2015.4 [50]. Altera OpenCL [38] enables the easy implementation of applications onto FPGAs by abstracting away the complexities of FPGA design, allowing software programmers to write

hardware-accelerated kernel functions in OpenCL C. Not only FPGA vendors but also other companies provide HLS languages and tools. CyberWorkBench [39] is C-based integrated environment for System LSI design developed by NEC Corporation. Impulse C [40] is also a C-based HLS tool developed by Impulse Accelerated Technologies, which is specialized in dataflow-oriented streaming applications. Calypto Catapult C [41] can accept C++ and SystemC and can generate RTL code targeted to FPGAs and ASICs. Lime [42] is a Java-based language that is designed to be executable across a broad range of architectures from FPGAs to conventional CPUs. This language is developed by IBM Research and is used in the Liquid Metal project as a single unified programming language.

Several open-source HLS frameworks also proposed. LegUp [43, 44] is an open source HLS tool being developed at the University of Toronto. This tool accepts a standard C program as input and automatically compiles the program to a hybrid architecture containing an FPGA-based MIPS soft processor and custom hardware accelerators that communicate through a standard bus interface. The Riverside Optimizing Compiler for Configurable Computing (ROCCC) [45] a C to VHDL compiler, which is specifically designed to automatically generate FPGA-based accelerators. Unlike LegUp, this tool aims to compile only critical regions of an application. Synthesijer [46] is a HLS tool that generates VHDL and Verilog HDL code from Java code. This tool does not need any hardware-aware description manner, but some syntax like dynamic memory and recursive functions are unsupported. CoRAM, CoRAM++, PyCoRAM [47, 48, 49] are slightly different from other HLS tools. These tools virtualize the communication and control infrastructure that interfaces the in-fabric hardware acceleration kernels with external memory (DRAM) to improve portability of hardware accelerators. Designers implement the hardware kernels in any hardware design methodology and describe control threads for memory access pattern in software. The designed control threads are translated into control circuits of memory operations. In [47, 48], the control threads are written in C-based language and in [49], Python is used to do this.

#### 2.3.2 System Development Using Domain Specific Language

In addition to HLS techniques, lots of Domain Specific Languages (DSLs) are proposed and published year after year. The most difference from HLS techniques is that designers develop hardware, more or less considering the hardware details like clock timing and interconnection than HLS techniques.

Hardware design DSLs using software language like C++, Java, Python, Haskell, etc. have been proposed before. ArchHDL [51] is a C++11-based library for RTL modeling and simulation. MyHDL [52] is an Python-based DSL that can translate a source code in MyHDL into Verilog or VHDL code. JHDL [53] is a Java-based DSL for reconfigurable systems that allows designers to express circuit organizations that dynamically change over time. Chisel [54] is a Scala-based DSL and hardware designs in Chisel can be translated into C++ simulators or Verilog RTL descriptions. [55] proposes

Veriloggen, which is a library for constructing a Verilog HDL source code in Python. Unlike MyHDL, this tool provides a lightweight abstraction of Verilog HDL AST, and designers can build up a hardware design written in Verilog HDL by using the AST abstraction and the entire functionality of Python. Lava [56] is a Haskell based DSL and has several distributions such as Chalmers Lava, Xilinx Lava, Kansas Lava, and York Lava. Similar to MyHDL and Veriloggen, PyMTL [57] is also a Python-based DSL but can do multi-level hardware modeling composed of functional level, cycle level, and register transfer level. Except for ArchHDL, these DSLs are already open-source.

Some application-specific DSLs have been proposed. Authors in [58] propose a hardware generation framework and system for linear transforms. This approach uses SPIRAL proposed in [59] to automatically produce software implementations of signal transforms, including automatic parallelization and vectorization. HDL Coder [60] generates portable and synthesizable HDL code from MATLAB functions and Simulink blocks. The generated HDL code can be used for FPGA programming or ASIC prototyping and design. Optimus [61] is an optimizing synthesis compiler for streaming applications, which compiles programs written in StreamIt [62] to either software or hardware implementations.

Some companies and research institutes have proposed hardware design DSLs supporting specific programming models. Bluespec SystemVerilog (BSV) [63] is an extended SystemVerilog developed by Massachusetts Institute of Technology, which enhances fine-grained parallel programming approach while abstracting hardware details. MaxCompiler [64] is developed by Maxeler Technologies in order to build high-performance dataflow hardware accelerator. This tool supports stream-oriented programming model using Java. FloPoCo [65] is developed by Institut National de Recherche en Informatique et en Automatique (INRIA), which automatically generates pipelined floating-point units. Using FloPoCo as a back-end, [66, 67] proposes a framework to generate high-throughput pipelined stream processors using their DSL. [66, 67] mentions that unlike MAXCompiler, this tool is designed to easily generate IP cores of stream processors that can be embedded into a common SoC platform on an FPGA.

#### 2.3.3 Discussion

A lot of development frameworks for FPGA-based accelerator have been proposed, but the ease of programmability, performance, resource usage and efficiency can vary from one technology to another, and there is usually a tradeoff between these characteristics [35]. Also, it is not easy to choose the best development framework for implemented applications and this is mostly dependent on programmer experience. These frameworks can verify the designed hardware behavior at higher abstraction layer but it is necessary to verify the behavior at low abstraction layer like RTL or gate-level in order to accurately detect the hardware errata. Therefore development frameworks based on HLS tools and DSLs have been attractive, nevertheless it is common that HDL-based circuit design and the circuit

| Kernel          | Application           | SIMD                        | Thread Level Parallelism | Characteristic                                                                |

|-----------------|-----------------------|-----------------------------|--------------------------|-------------------------------------------------------------------------------|

| SGEMM           | Linear algebra        | Regular                     | Across 2D tiles          | Compute bound after tiling                                                    |

| Monte Carlo     | Computational finance | Regular                     | Across paths             | Compute bound                                                                 |

| Convolution     | Image analysis        | Regular                     | Across pixels            | Compute bound; BW bound for small filters                                     |

| FFT             | Signal processing     | Regular                     | Across smaller FFTs      | Compute bound or BW bound for small filters                                   |

| SAXPY           | Dot product           | Regular                     | Across vector            | BW bound for large vectors                                                    |

| LBM             | Time migration        | Regular                     | Across cells             | BW bound                                                                      |

| Constant solver | Rigid body physics    | Gather/Scatter              | Across constraints       | Synchronization bound                                                         |

| SpMV            | Sparse solver         | Gather                      | Across non-zero          | BW bound for typical large matrices                                           |

| GJK             | Collision detection   | Gather/Scatter              | Across objects           | Compute bound                                                                 |

| Sort            | Database              | Gather/Scatter              | Across elements          | Compute bound                                                                 |

| Ray casting     | Volume rendering      | Gather                      | Across rays              | 4-8MB first level working set;<br>over 500MB last level working<br>set        |

| Search          | Database              | Gather                      | Across queries           | Compute bound for small tree,<br>BW bound at bottom of tree<br>for large tree |

| Histogram       | Image analysis        | Requires conflict detection | Across pixels            | Reduction/synchronization bound                                               |

Table 2.2 Throughput computing kernel characteristics cited from [68]

behavior verification are repeated as required for development of FPGA-based accelerators. However, designing large-scale circuits leads to long RTL simulation times, which means that traditional RTL simulators cannot finish the circuit behavior verification within a realistic time frame. In the future, FPGAs will be larger thanks to transistor scaling and stacking, leading to more RTL simulation times. Therefore high-speed simulation environments are required.

### 2.4 Throughput Computing Kernels

In this section, I look into important computation kernels and explain why stencil computation and sorting are appropriate ones to be accelerated.

Recent information technology advances in the past decade have led to an explosion in the amounts of data being generated such as digital documents, stock market data, personal records, electronic commerce sales data, news, etc. As digital data continues to grow rapidly, it is important to process the ever-growing data in a reasonable duration of time.

Authors in [68] mention that processing huge amount of data to distill and deliver appropriate content to users in a timely manner has made throughput computing an important aspect for emerging applications, and they rigorously analyzed CPU and GPU performance differences between a set of important throughput computing kernels. They also analyzed the computational and memory characteristics of four recently proposed benchmark suites and formulated the set of throughput computing kernels that capture these characteristics. Table 2.2 summarizes the throughput computing kernel characteristics. The authors classify these kernels according to (1) their computational and memory requirements, (2) regularity of memory accesses that determines the ease of exploiting data-level parallelism, which

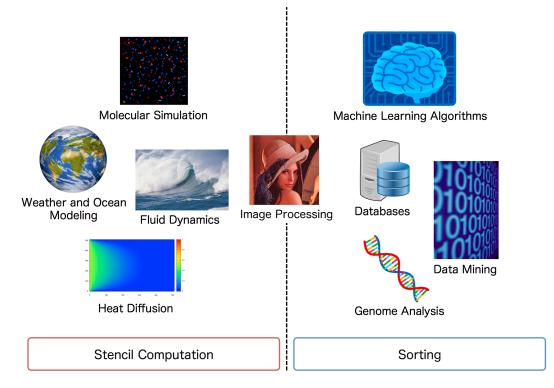

Figure 2.6 Stencil computation and sorting are fundamental operations for many applications.

means the use of Single Instruction Multiple Data (SIMD), and (3) the granularity of tasks, which determines the impact of synchronization. They mention that these characteristics provide insights into the architectural features that are required to achieve good performance.

In this thesis, I select Lattice Boltzmann method (LBM) and Sort as a kernel to be accelerated by FPGAs and discuss that the findings obtained from the two designed FPGA-based accelerators can be applied to the other kernels. As shown in Table 2.2, almost all of the kernels are either compute-bound or bandwidth bound. To demonstrate that FPGA-based acceleration approaches are valuable, it is necessary to clarify that the approaches can achieve better performance than CPUs and GPUs in both compute and bandwidth-bound kernels. Besides, the two kernels are applied to lots of applications shown in Figure 2.6. That is why it is valuable to try to accelerate them, and as a representative of bandwidth and compute-bound kernels, LBM and Sort are selected respectively.

LBM is a class of computational fluid dynamics based on stencil computation whose algorithm updates values associated with points on a multidimensional grid using weighted contributions from a subset of its neighbors in both time and space. Stencil computation plays a crucial role in a variety of different fields of application, ranging from partial differential equation solving, to computer simulation of particles' interaction, to image processing and computer vision [69]. Basically, stencil computation is bandwidth bound due to the algorithm characteristic, which requires to load several data from an

external memory to update a value in each time step.

As already known, sorting is used in a lot of fields, especially databases. [68] picks up radix sort and describes the trendy implementation for CPUs and GPUs. At the time, the best implementation on CPUs is to use SIMD instructions and implement a scatter-oriented rearrangement within cache. On GPUs, radix sort is implemented using the SIMD-friendly 1-bit split algorithm described in [70]. However, the split-based implementation executes even more instructions than a scalar sort, and therefore the overall efficiency of SIMD use relative to optimized scalar code is not high. The authors in [68] mention that totally radix sort has O(n) bandwidth and compute requirements, where n is the number of elements to be sorted, but is usually compute bound because of the inefficiency of SIMD use.

### 2.5 Summary

In this chapter, I described the fundamental knowledge of the FPGA-based accelerator and the background of my work.

FPGA-based accelerators have been attractive as an alternative computing device in recent years. Although the peak performance is low compared with the other two devices, FPGA-based accelerators can achieve higher performance and better power efficiency than implementations on CPUs and GPUs because designers can implement circuits that realize application-specific pipelined hardware and data supply systems. However in order to receive the remarkable potentials, designers have to decide on an appropriate FPGA device, hardware design, and implementation depending on application characteristics, such as a sequential algorithm, an iterative algorithm, data-parallel algorithm or memory intensive algorithm, etc.

Moreover, many companies and research institutes in the world have proposed development frameworks for FPGA-based accelerator. However there is a tradeoff between the ease of programmability, performance, resource usage and efficiency. Besides their characteristics can vary among the frameworks and it is not easy to choose the best development framework for implemented applications. Therefore it is still common that designers implement logic circuits with HDL and verify the circuit behavior in order to develop FPGA-based accelerators. However, designing large-scale circuits leads to long RTL simulation times, which means that traditional RTL simulators cannot finish the circuit behavior verification within a realistic time frame. In the future, FPGAs will be larger thanks to transistor scaling and stacking, leading to more RTL simulation times. Therefore high-speed simulation environments are required. To address this problem, I propose a novel infrastructure enabling high-speed RTL simulation to verify whether or not the developed hardware works as intended.

Finally I discuss a set of important throughput computing kernels and explain that stencil computation and sorting are appropriate ones to be accelerated by FPGAs. In this thesis, I propose two high performance FPGA-based accelerators targeting them. In order to show that the acceleration methods are promising, I evaluate the designed accelerators performance in the compute and bandwidth-bound kernel and discuss the applicability of the findings obtained from the development of the proposed accelerators against the other kernels.

# **Chapter 3**

# A Scalable Stencil-computation Accelerator by Employing Multiple Small FPGAs

### 3.1 Motivation

Stencil computation is one of the typical scientific computing kernels. It is applied to diverse areas such as earthquake simulation, digital signal processing and fluid calculation. In the last several decades, stencil computation has been accelerated by using multicore microprocessors and GPUs. However, sustained performance is limited due to memory bandwidth restriction, and also because the computation kernel has small arithmetic intensity. To address this problem, I propose a high performance architecture for 2D stencil computation employing multiple small FPGAs. In this architecture, the data set is divided into multiple blocks and each block is assigned to each FPGA, which means that the data set is stored in FPGA internal memory instead of in an external DRAM. This also means that the according to this architecture, the number of connected FPGAs scales with the size of the data set. I detail the design and implementation of the proposed FPGA-based accelerator, and evaluate it in terms of the sustained performance, scalability, and power efficiency.

The main contributions of this chapter are:

- to propose a high performance computation architecture for 2D stencil computation using multiple small FPGAs,

- to develop an FPGA-based scalable stencil-computation accelerator to realize my proposed architecture,

- to show the architecture usability on the 100-FPGA array system in terms of the sustained performance, scalability, and power efficiency.

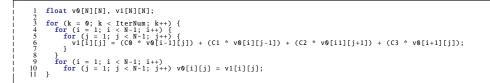

Figure 3.1 The pseudo code of kernel part for stencil computation

## 3.2 Stencil Computation

In the area of scientific computation a class of iterative kernels is frequently used, which uses some values of a time step and calculate a result associated with those values of the next time step. In the class, *stencil computation* [10] updates values according to some **fixed pattern**. Stencil computation is one of the approaches to calculate an approximate solution of partial differential equations, and is used in lots of areas like earthquake simulation, digital signal processing and fluid calculation.

In this thesis I focus on the 2D Jacobi iteration kernel [71] and the formula is given by

$$v_{i,j}^{k+1} = c_0 v_{i-1,j}^k + c_1 v_{i,j-1}^k + c_2 v_{i,j+1}^k + c_3 v_{i+1,j}^k$$

(3.1)

where  $v_{x,y}^k$  and  $v_{x,y}^{k+1}$  are values of x, y at time step k and k + 1 respectively, and  $c_0$ ,  $c_1$ ,  $c_2$ , and  $c_3$  stand for weighting factor. In this thesis, the data type of the weighting factor and values are single precision floating-point. As shown in the formula, a value  $v_{x,y}^{k+1}$  is calculated from the summation of the left, up, right and down values multiplied by each weighting factor. If all weighting factors are 0.25, updating values of the next time step stands for the arithmetic mean of the four values of the current time step.

Figure 3.1 shows the pseudo code of kernel part for stencil computation. k and (i, j) are a time step and value coordinate. The two vectors v0 and v1, which are declared at line 1, are used to store the two-dimensional  $N \times N$  data set. A value at (i, j) is represented as v0[i][j] or v1[i][j]. At line 6 in Figure 3.1, v1[i][j] is calculated from the summation of v0[i-1][j], v0[i][j-1], v0[i][j+1], and v0[i+1][j] multiplied by each weighting factor. At line 9 and 10 in Figure 3.1, all values of v1 are copied into v0. In this thesis, the process at a time step k (line  $4 \sim 10$ ) is called **Iteration**. *IterNum* at line 3 in Figure 3.1 is constant that stands for the number of executed Iterations.

As shown in Figure 3.1, the kernel part for stencil computation is simple, yet needs large computation time since the computation kernel has small arithmetic intensity [72] and the number of Iterations is large. Arithmetic intensity is defined as the number of floating-point operations (Flops) per data size (bytes) read from an external DRAM for cache misses. As described above, stencil computation requires multiple data accesses per unit operation. In a practical application, because the number of memory accesses is even larger than this example, microprocessors and GPUs cannot achieve high

Figure 3.2 Photo of ScalableCore system with 100 units (a) and Scalable Core unit (b)

sustained performance due to memory bandwidth restriction. According to [72], straightforward implementation of stencil computation can achieve only 10% of the peak performance of AMD Opteron microprocessors because of its small arithmetic intensity of 0.5 Flop/Byte. Therefore, several research institutes have proposed FPGA-based accelerators for stencil computation [73, 74].

In this chapter, I propose a scalable stencil-computation accelerator by employing multiple small FPGAs [75]. To realize this proposal, I use ScalableCore system [76] that we have developed. I detail the design and implementation that efficiently executes 2D stencil computation, and evaluate the proposed accelerator in terms of the sustained performance and power efficiency.

### 3.3 Key Issues of FPGA Array System

In this section, I describe ScalableCore system that is a hardware platform for design and implementation of the proposed stencil-computation accelerator, and discuss a clock variation problem that is due to a different clock oscillator on each FPGA node.

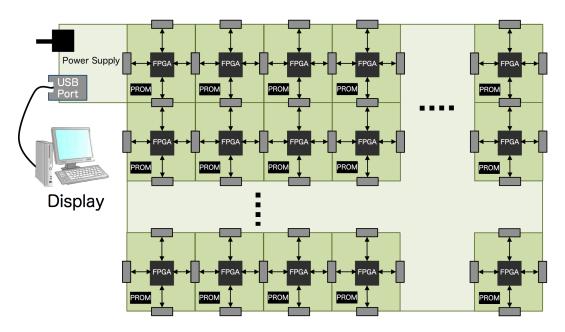

#### 3.3.1 ScalableCore System

Figure 3.2 (a) shows ScalableCore system using 100 FPGAs. ScalableCore system is an FPGA array system employing multiple small FPGAs. Figure 3.2 (b) shows an FPGA node called ScalableCore unit. The board size is 4.67cm  $\times 6.0$ cm. The FPGA node works as a stand-alone FPGA board and has

| Time [sec] | Worst Value [ppm] | Standard Deviation |

|------------|-------------------|--------------------|

| 20         | 20.47 (x=5, y=3)  | 4.73               |

| 40         | 20.47 (x=5, y=3)  | 4.68               |

| 80         | 20.47 (x=5, y=3)  | 4.73               |

| 160        | 20.59 (x=5, y=3)  | 4.77               |

| 320        | 20.66 (x=5, y=3)  | 4.79               |

Table 3.1

Worst value and standard deviation of measured clock variations.

an FPGA (Xilinx Spartan-6 XC6SLX16), 512KB SRAM<sup>\*1</sup>, 40MHz clock oscillator, and configuration ROM. Connection between the FPGA nodes is realized via the external I/O pins on the left, right, top and bottom side.

The leftmost nodes in Figure 3.2 (a) have a DC5V power supply and USB-UART IC chip. Application programs are loaded from a Linux host PC and are transferred to ScalableCore system via USB-UART IC chip on the upper left board. After that, ScalableCore system executes the programs and displays the execution result on the host PC.

ScalableCore system is originally developed for high speed many-core processor simulation. The power consumption of an FPGA is about 1 Watt [76]. Based on the power consumption, I estimate the power efficiency of the proposed stencil-computation accelerator and the estimated power efficiency is 1.7x better than a previous study [77] that uses several large FPGAs to accelerate stencil computation. Because of the examination result, I decide to use ScalableCore system as a hardware platform for the proposed stencil-computation accelerator.

#### 3.3.2 Preliminary Evaluation regarding Clock Variation Problem

As shown in Figure 3.1, stencil computation uses the four adjacent values to calculate the center value of the next time step. Therefore data transfer between FPGA nodes is necessary if the divided tasks are assigned to each FPGA. Besides, the data transfer has to be executed at an appropriate timing because updating values at an Iteration needs the neighborhood values calculated at the previous Iteration.

On the other hand, each FPGA constituting ScalableCore system has an individual clock oscillator that is 40MHz CSX-750PB. The frequency stability of the clock oscillator is  $\pm$ 50ppm. The frequency stability  $\pm$ 50 means that it is guaranteed that the number of deviated cycles per 1 million cycles is  $\pm$ 50 based on the perfect clock. However even if  $\pm$ 50ppm, it may generate a gap of 120,000 cycles per minute because 40MHz CSX-750PB may generate a gap of 2,000 cycles per second. This gap is not trivial and it is necessary to design a robust system that can absorb the clock variation.

In this section, I quantitatively evaluate clock variation of each FPGA node. The original Scal-

<sup>\*1</sup> The proposed stencil-computation accelerator does not use it.

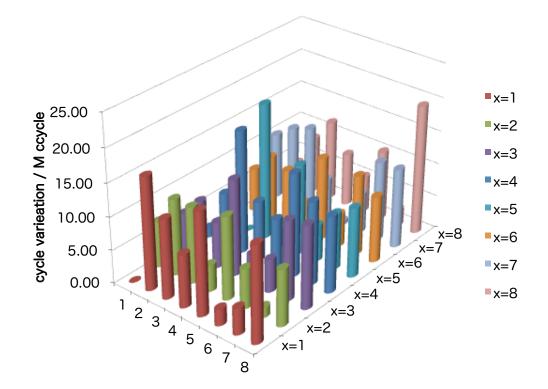

Figure 3.3 Clock variations by measuring 20 seconds

ableCore system emulates many-core processor behavior and the emulated many-core processor works while synchronized under Virtual Cycle proposed in [76]. Using this mechanism, I implement a C application to measure the frequency stability. In this preliminary evaluation, the C program runs on  $8 \times 8$  ScalableCore system and I evaluate the clock variation of each FPGA node depending on the measurement time.

Figure 3.3 shows clock variation of each FPGA node by measuring 20 seconds. The points on x-axis and y-axis stand for each FPGA coordinate. The z-axis represents the absolute value of the number of deviated cycles per 1 million cycles. This result shows that the all deviated cycles are within 50 cycles according to the clock oscillator specification. The worst deviated cycle is 20.47, which is generated from the FPGA node located at (x=5, y=3).

Table 3.1 shows the worst value and standard deviation of measured clock variations. Time, Worst Value, and Standard Deviation in this table stand for the measurement time, the worst deviated cycle with the FPGA node coordinate, and standard deviation of all clock variations in  $8 \times 8$  ScalableCore system. The worst deviated cycle and standard deviation hardly change depending on the measurement time. It means that the clock variation is larger at a constant rate depending on the operating time.

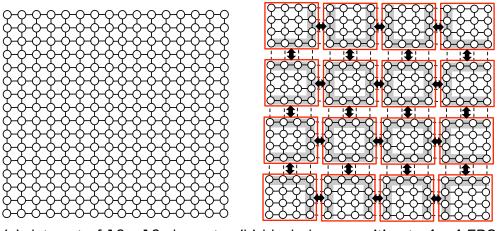

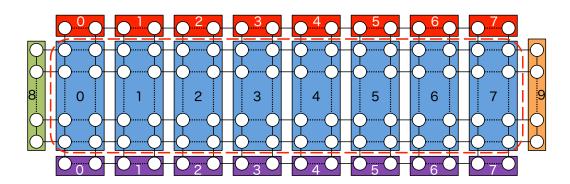

(a) data set of 16 x 16 elements (b) block decomposition to 4 x 4 FPGAs

Figure 3.4 Data set decomposition for stencil computation with many FPGAs

As shown in these results, this clock variation is not trivial problem and it is impossible to design the proposed hardware ignoring this important matter. Therefore, it is necessary to design a robust system that can absorb the clock variation.