### T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

### 論文 / 著書情報 Article / Book Information

| 題目(和文)            |                                                                                                                                                                             |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | Charge Trapping Characteristics of MAHOS Capacitor Structures with High-k Dielectric Materials as Charge Trapping Layers                                                    |

| 著者(和文)            | RifaiAbdulloh                                                                                                                                                               |

| Author(English)   | Abdulloh Rifai                                                                                                                                                              |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第10027号,<br>授与年月日:2015年12月31日,<br>学位の種別:課程博士,<br>審査員:中村 吉男,史 蹟,小林 能直,村石 信二,三宮 工                                                       |

| Citation(English) | Degree:,<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第10027号,<br>Conferred date:2015/12/31,<br>Degree Type:Course doctor,<br>Examiner:,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                        |

| Type(English)     | Doctoral Thesis                                                                                                                                                             |

The Dissertation Committee for Tokyo Institute of Technology certifies that this is the approved version of the following dissertation:

# Charge Trapping Characteristics of MAHOS Capacitor Structures with High-κ Dielectric Materials as Charge Trapping Layers

|             | Committee:        |

|-------------|-------------------|

| Supervisor: |                   |

| •           | (Yoshio Nakamura) |

## Charge Trapping Characteristics of MAHOS Capacitor Structures with High-κ Dielectric Materials as Charge Trapping Layers

by

Abdulloh Rifai (11D51284)

Dissertation

Presented to Department of Metallurgy and Ceramics Science

Faculty of Graduate School of Science and Engineering

of Tokyo Institute of Technology

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Engineering**

Tokyo Institute of Technology

December 2014

#### **Contents**

| Copy  | yright Pa                  | ge i                                                                    |  |

|-------|----------------------------|-------------------------------------------------------------------------|--|

| Sign  | ature Pag                  | ge ii                                                                   |  |

| Title | Page                       | iii                                                                     |  |

|       |                            | iv                                                                      |  |

| Abst  | ract                       | v                                                                       |  |

| Cont  | ents                       | vi                                                                      |  |

| List  | of Table                   | S                                                                       |  |

| List  | of Figure                  | es                                                                      |  |

|       |                            |                                                                         |  |

|       | _                          | ntroduction                                                             |  |

| 1.1   | The Ba                     | asics of Non-Volatile Memory $1-1$                                      |  |

| 1.2   | The Ro                     | ole of High- $\kappa$ Dielectric Materials in Non-Volatile Memory $1-6$ |  |

|       | 1.2.1                      | High- $\kappa$ Dielectric Materials as Blocking Layer                   |  |

|       | 1.2.2                      | High- $\kappa$ Dielectric Materials as Tunneling Layer $1-8$            |  |

|       | 1.2.3                      | High-κ Dielectric Materials as Charge Trapping Layer 1 – 9              |  |

| 1.3   | Background of the Research |                                                                         |  |

|       | 1.3.1                      | Motivation of the Research $1-10$                                       |  |

|       | 1.3.2                      | Current Status of Research utilizing High-к Dielectric                  |  |

|       |                            | Materials as Charge Traping Layers 1 – 14                               |  |

|       | 1.3.3                      | Issues and Challenges of Research utilizing High-κ                      |  |

|       |                            | Dielectric Materials as Charge Traping Layers 1 – 18                    |  |

| 1.4   | What t                     | to Propose and the Purpose of the Research                              |  |

| 1.5   | Thesis                     | Organization                                                            |  |

| Refe  | rences                     |                                                                         |  |

| Cha   | pter 2: I                  | Device Fabrication and Structural Properties Characterizations          |  |

| 2.1   |                            | n Consideration of MAHOS Capacitor Structures                           |  |

| 2.2   | Ū                          | ation of MAHOS Capacitor Structures 2 – 2                               |  |

|       |                            | RCA Cleaning Process                                                    |  |

|       |                            | Rapid Thermal Processing (RTP)                                          |  |

|       |                            | Atomic Layer Deposition (ALD)                                           |  |

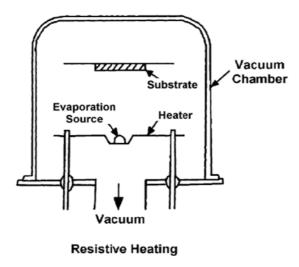

|       | 2.2.4   | Thermal Evaporation                                                                                                          | 2 – 11 |

|-------|---------|------------------------------------------------------------------------------------------------------------------------------|--------|

| 2.3   | Struct  | cural Properties and Chemical States of the MAHOS Capacitor                                                                  |        |

|       | Struct  | ures                                                                                                                         | 2 – 13 |

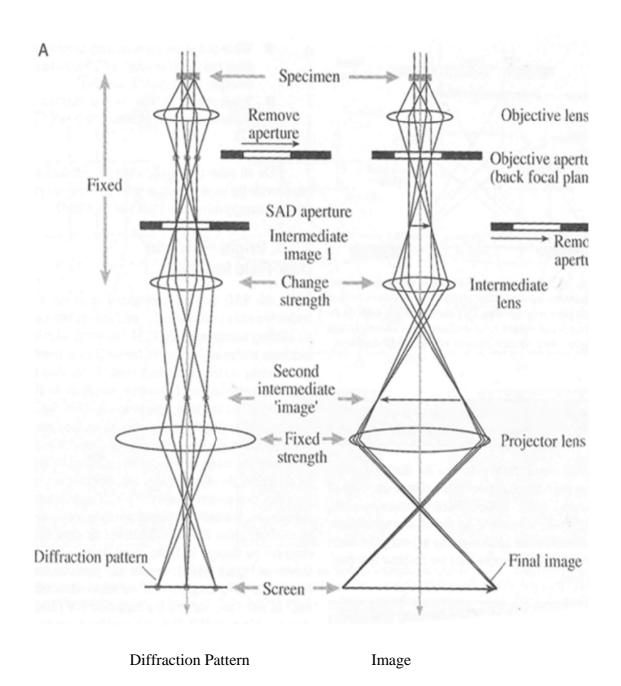

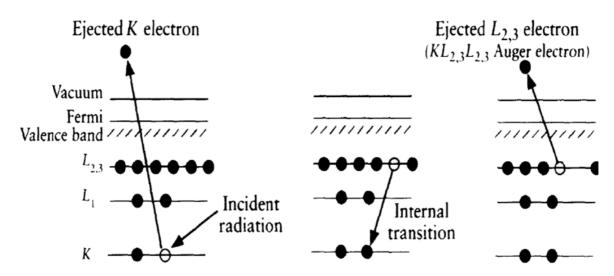

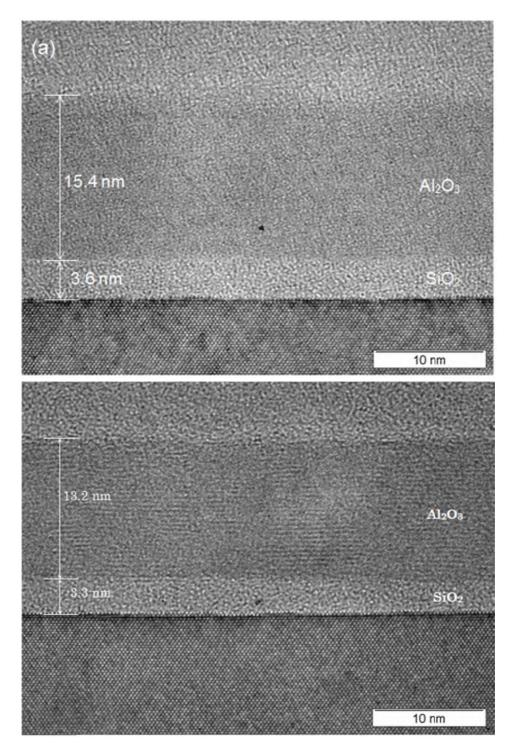

|       | 2.3.1   | Structural Properties Characterized by HRTEM                                                                                 | 2 – 13 |

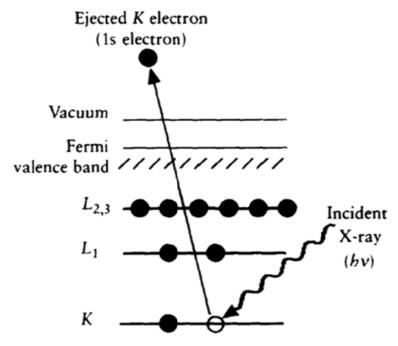

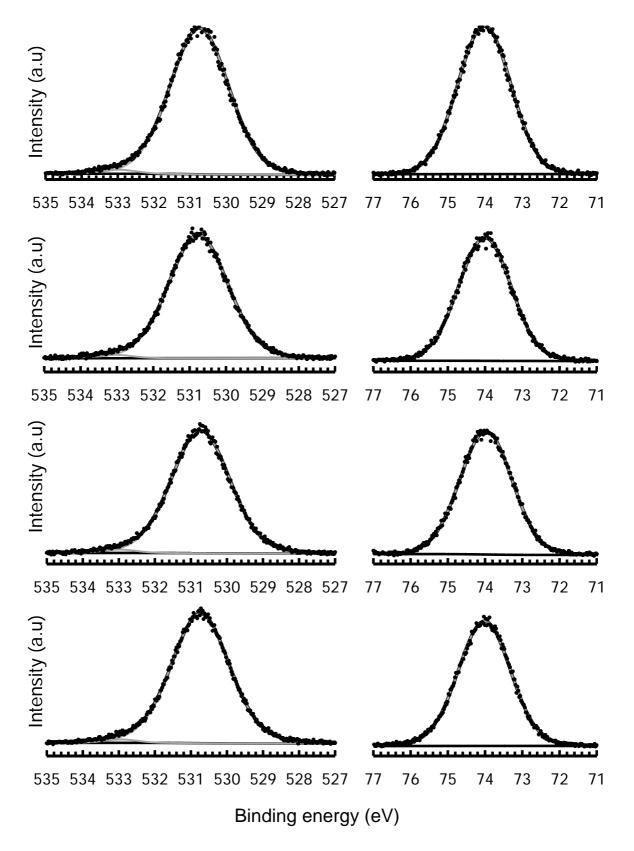

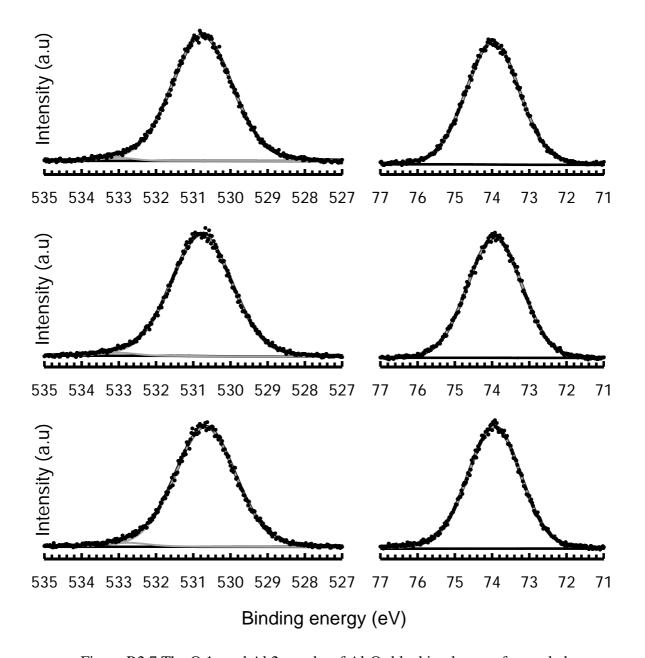

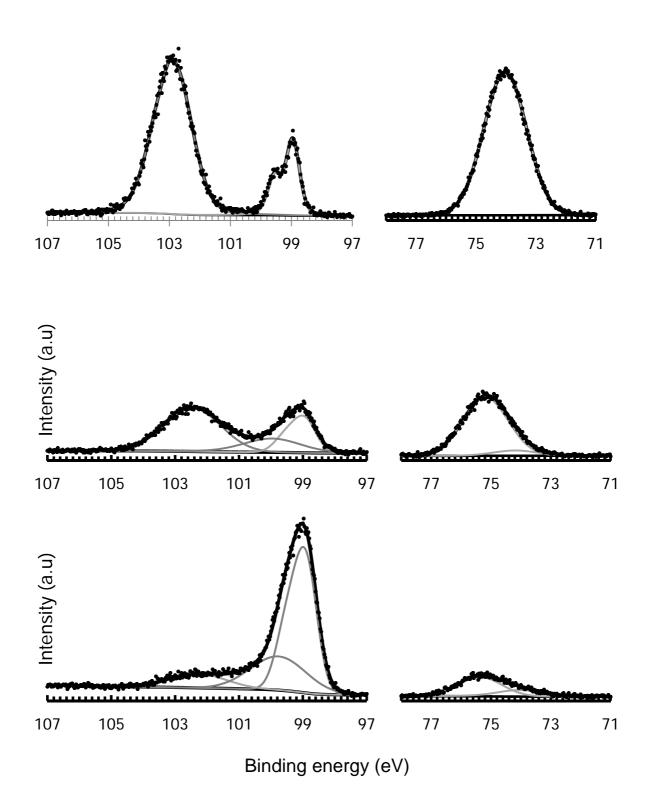

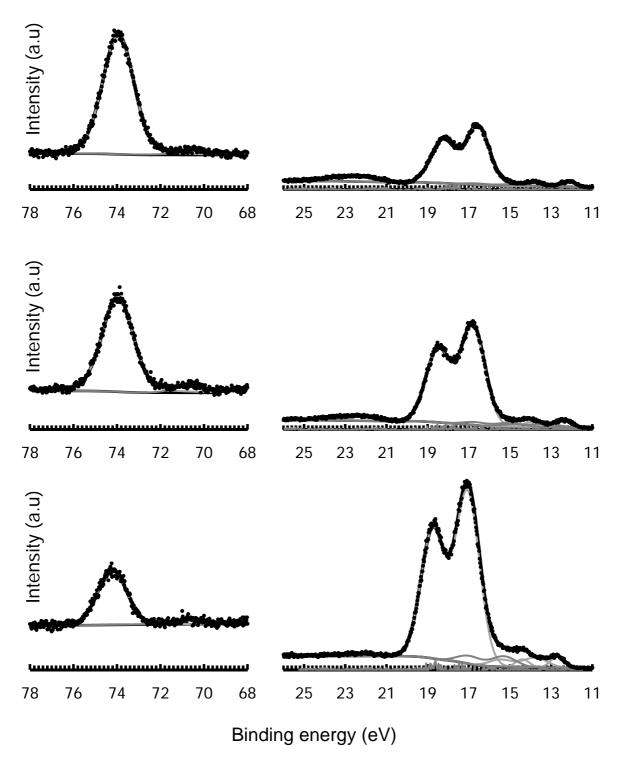

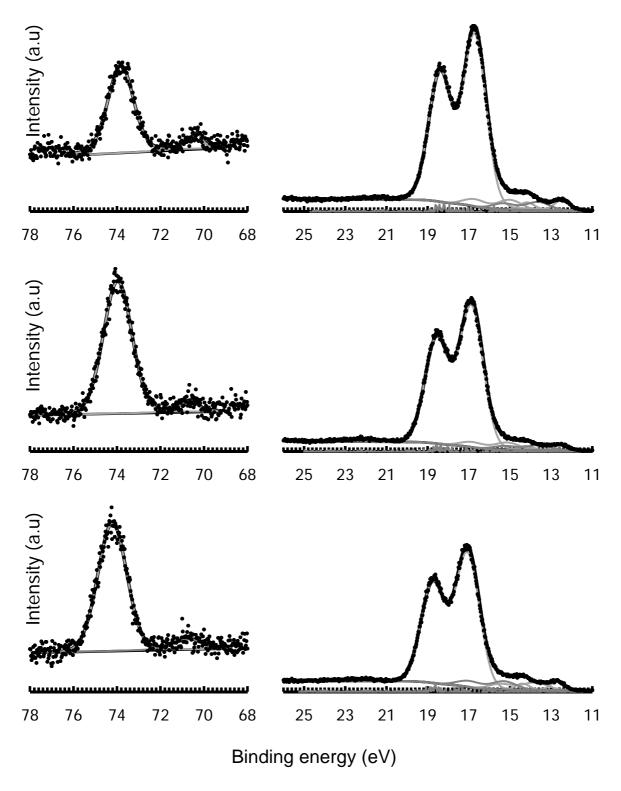

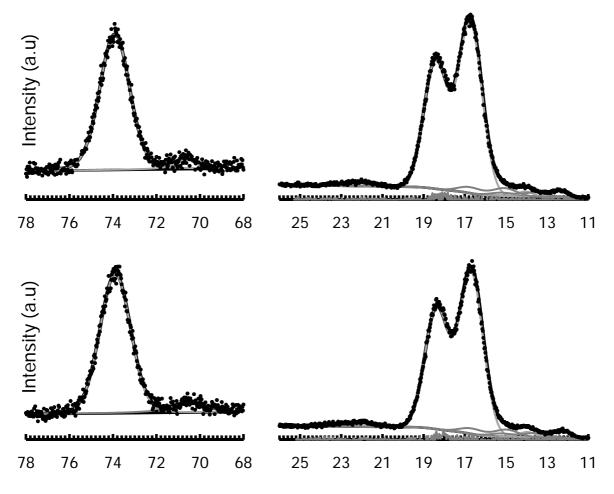

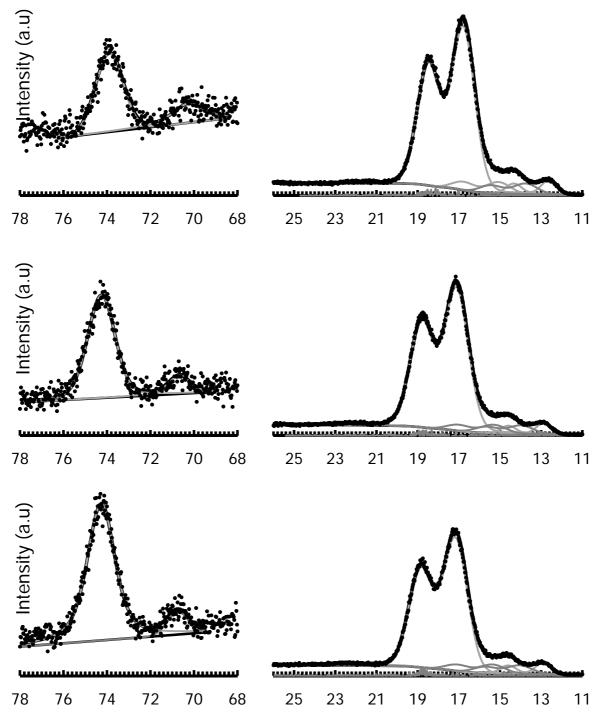

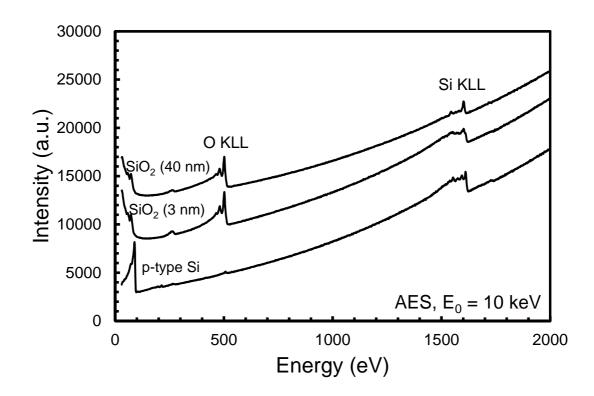

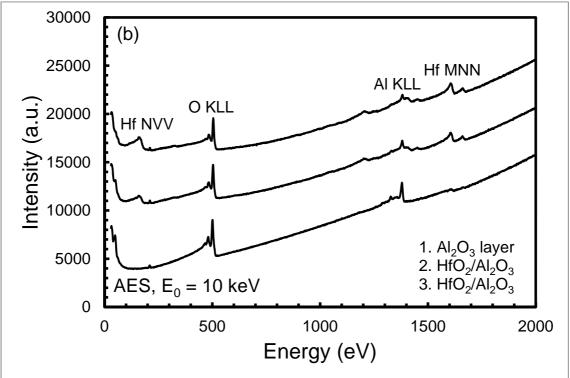

|       | 2.3.2   | Chemical State Identification by XPS and AES                                                                                 | 2 – 13 |

| 2.4   | Struct  | tural Properties and Chemical States of the MAHOS Capacitor                                                                  |        |

|       | Struct  | ures                                                                                                                         | 2 – 18 |

|       | 2.4.1   | SiO <sub>2</sub> Grown on p-type Si Substrate                                                                                | 2 – 18 |

|       | 2.4.2   | Al <sub>2</sub> O <sub>3</sub> as Charge Trapping Layer in Al/Al <sub>2</sub> O <sub>3</sub> /SiO <sub>2</sub> /Si Structure |        |

|       |         | and as Blocking Layer in MAHOS Structures                                                                                    | 2 – 19 |

|       | 2.4.3   | $Al_2O_3/SiO_2/Si\ Interface\ in\ Al/Al_2O_3/SiO_2/Si\ Structure$                                                            | 2 - 21 |

|       | 2.4.4   | HfAlO Layer and [Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> ] Nanolaminate Structures                                  | 2 - 22 |

|       | 2.4.5   | High-κ/SiO <sub>2</sub> /Si Structure and Its Interface                                                                      | 2 - 27 |

| 2.5   | Sumn    | nary                                                                                                                         | 2 - 27 |

| Refer | ences . |                                                                                                                              | 2 – 29 |

| Figur | es of R | esults                                                                                                                       | 2 – 31 |

|       |         |                                                                                                                              |        |

| Chap  | ter 3:  | Energy Band Alignment of the MAHOS Memory Capacitors                                                                         |        |

| 3.1   | Backg   | ground                                                                                                                       | 3 – 1  |

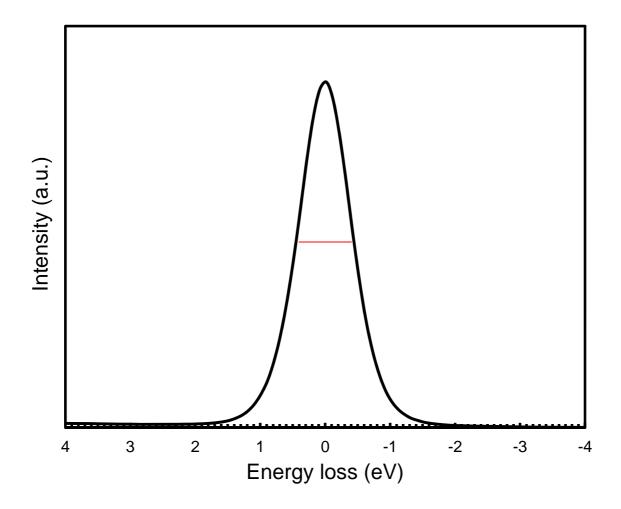

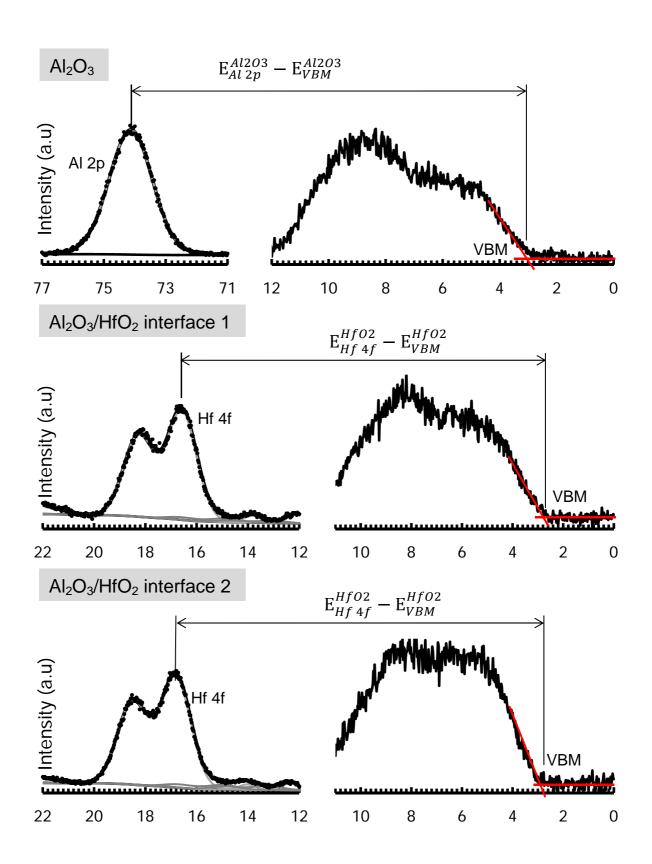

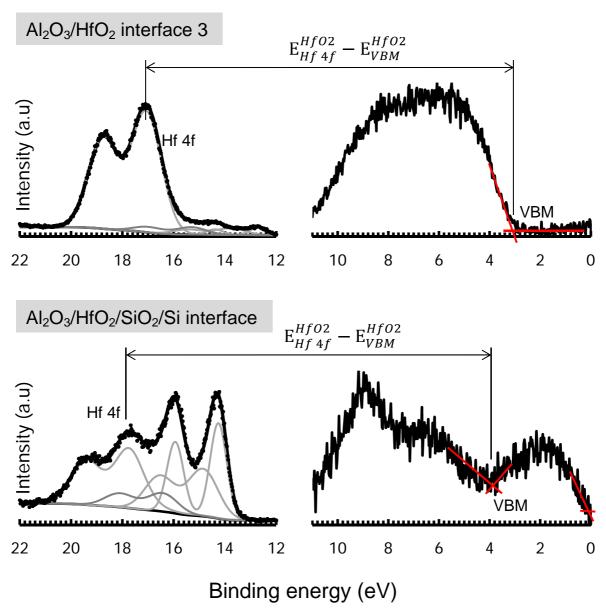

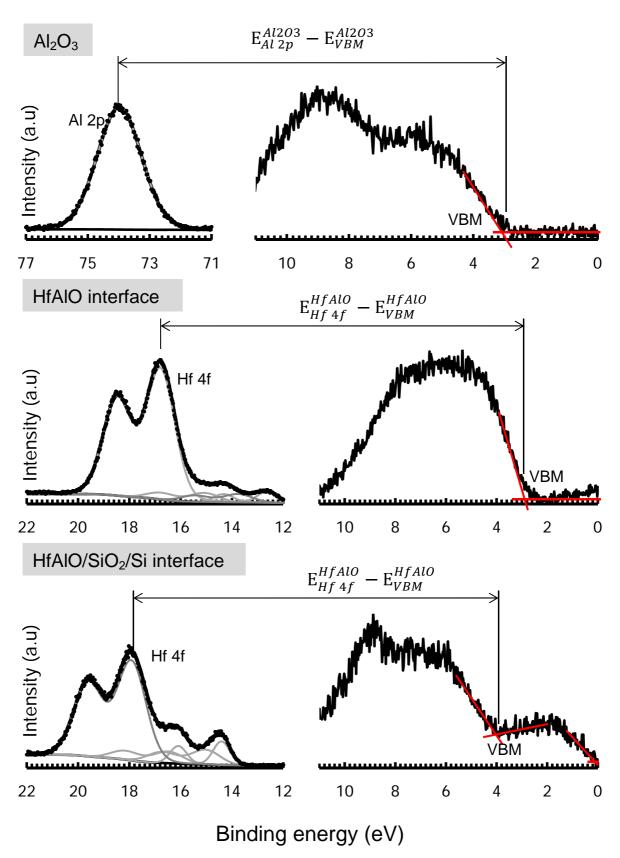

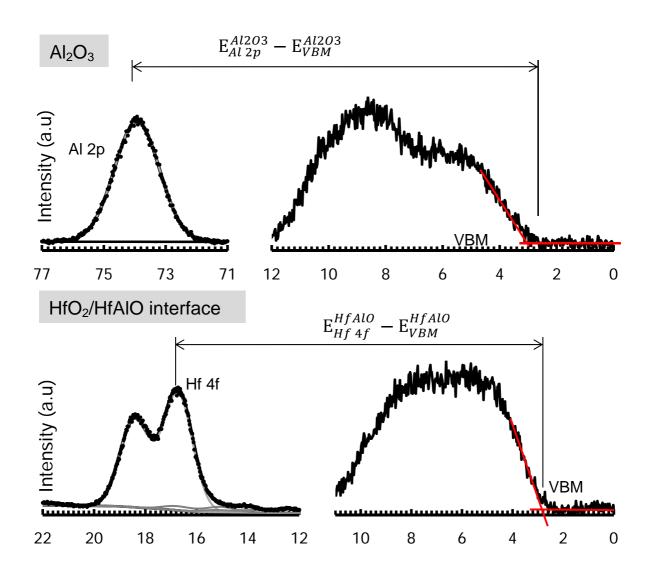

| 3.2   | Energ   | y Band Parameter Measurement by AES-REELS and XPS                                                                            | 3 - 2  |

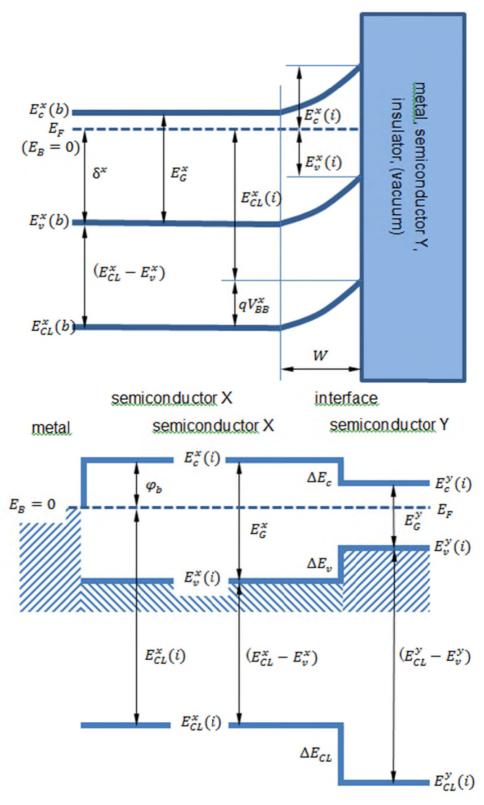

|       | 3.2.1   | Energy Band Diagram at the Interface between Two Materials                                                                   | 3 - 2  |

|       | 3.2.2   | Energy Band Parameter Determination                                                                                          | 3 - 4  |

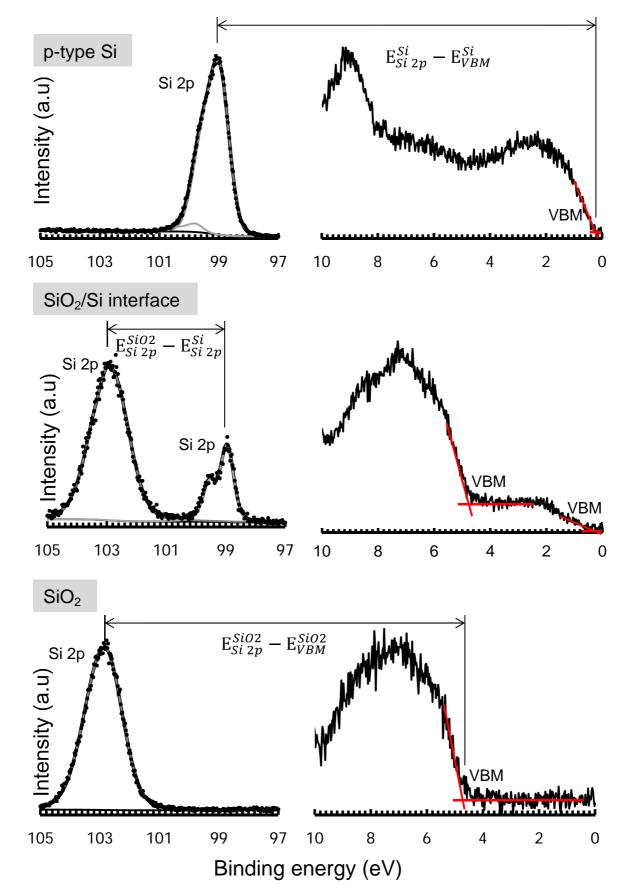

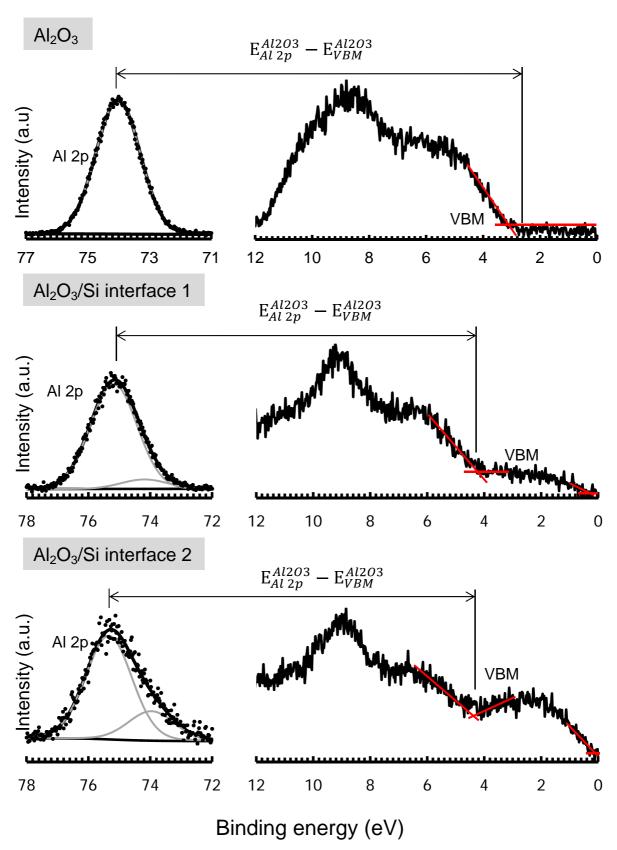

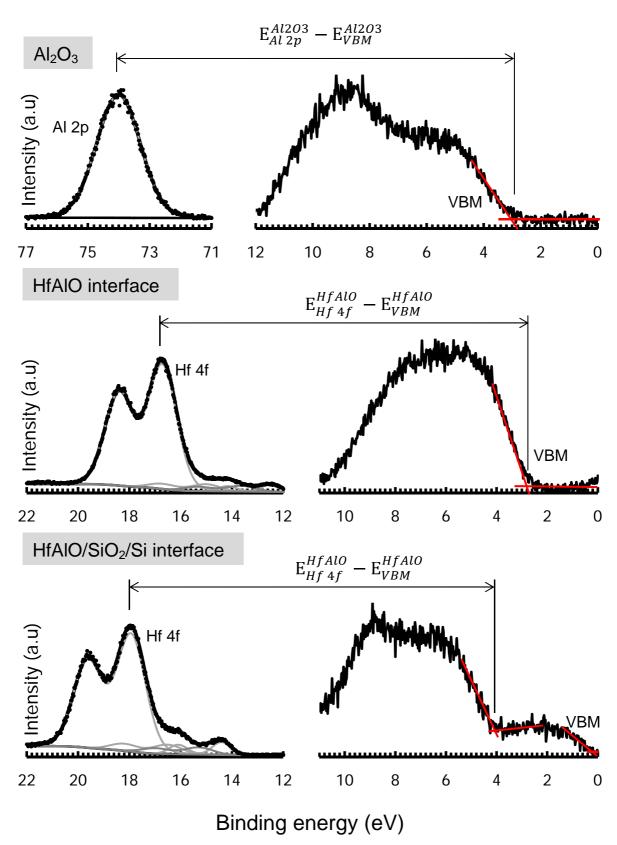

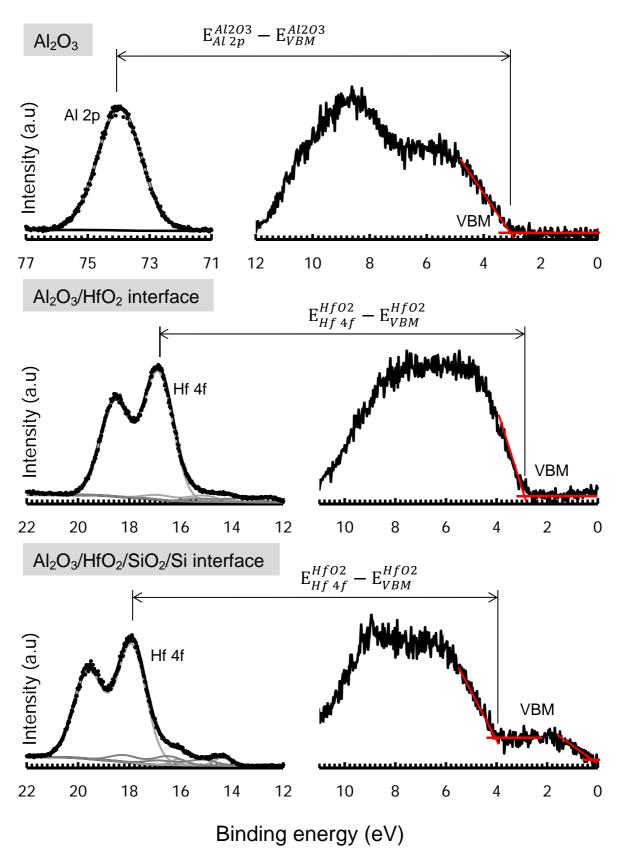

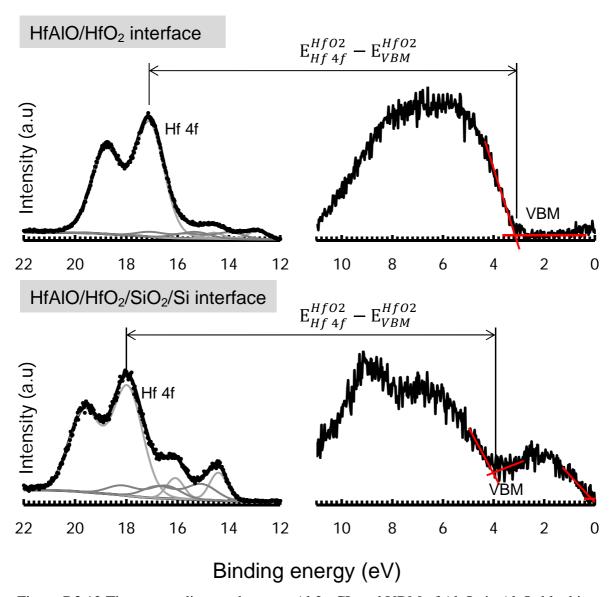

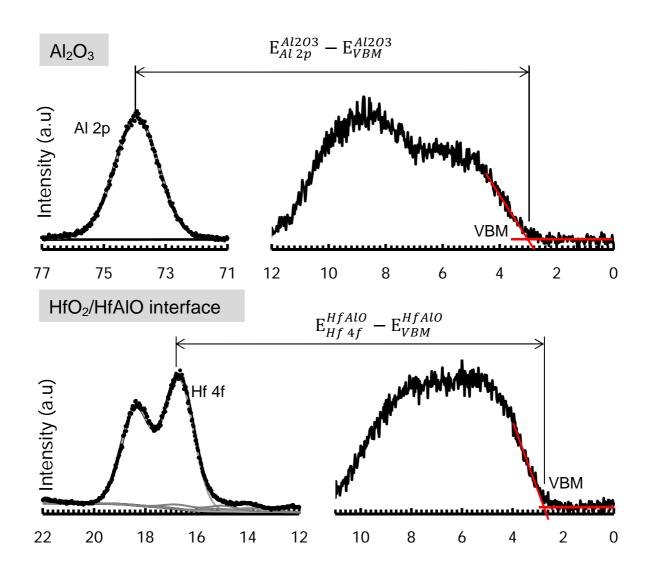

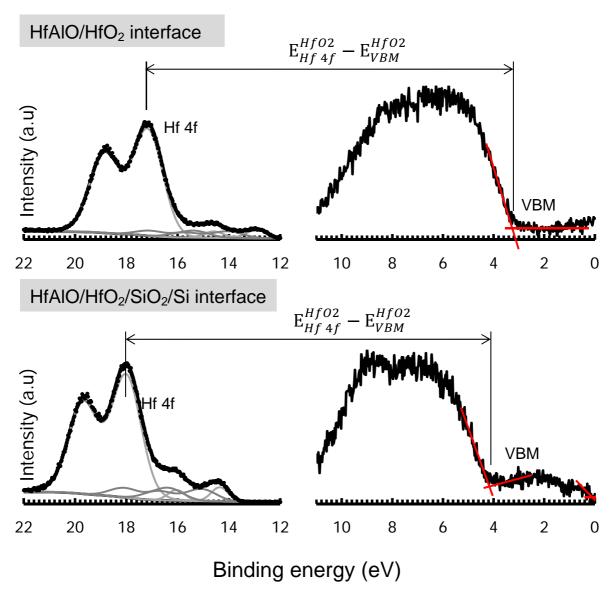

|       | 3.2.3   | Valence Band Offset Measurement                                                                                              | 3 - 5  |

| 3.3   | Band    | Gap of Materials in the MAHOS Capacitor Structures                                                                           | 3 - 7  |

|       | 3.3.1   | Band Gap of SiO <sub>2</sub> in SiO <sub>2</sub> /p-type Si Structures                                                       | 3 - 7  |

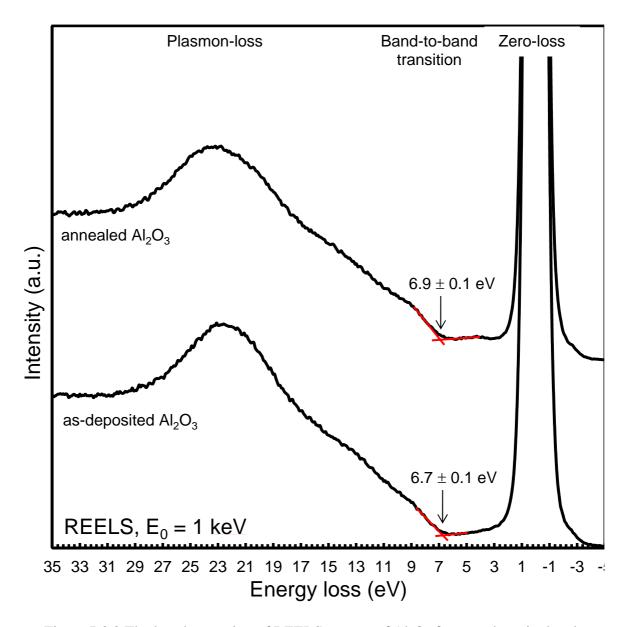

|       | 3.3.2   | Band Gap of Al <sub>2</sub> O <sub>3</sub> in MAHOS Structures                                                               | 3 - 8  |

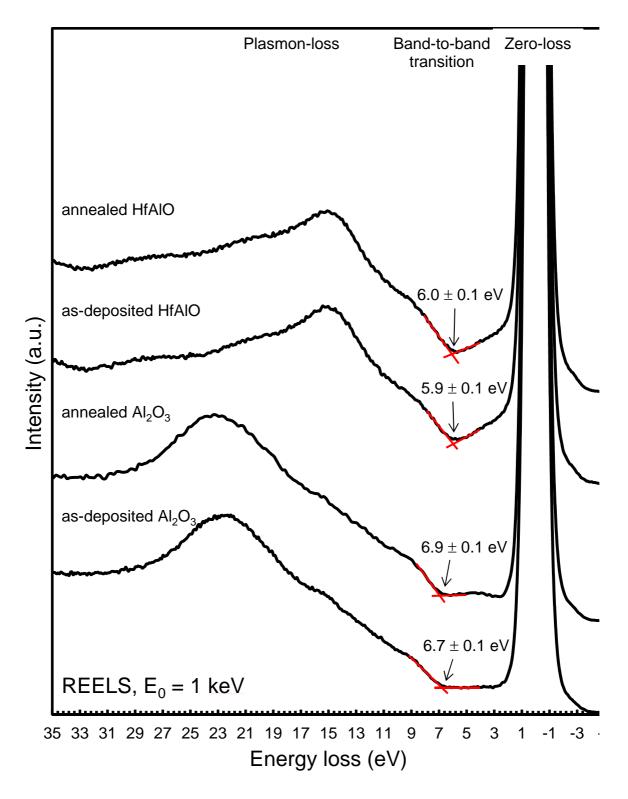

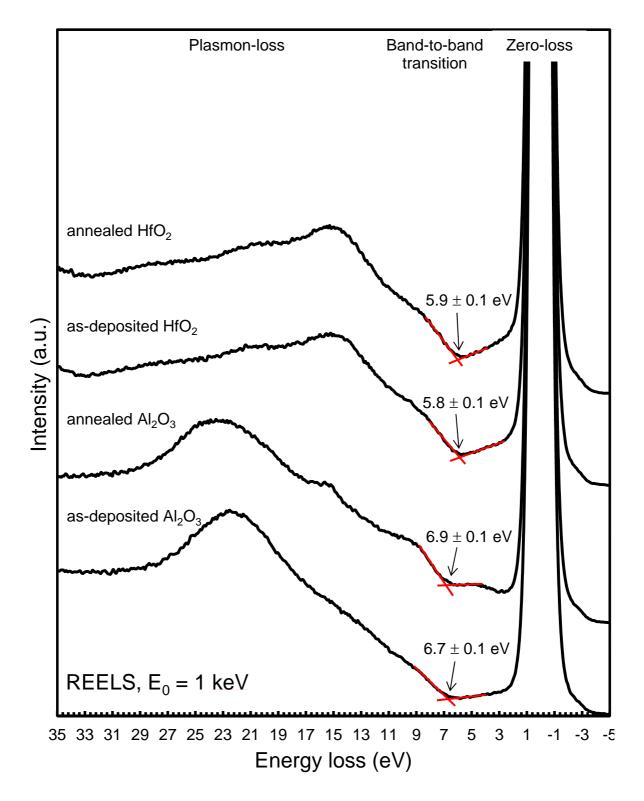

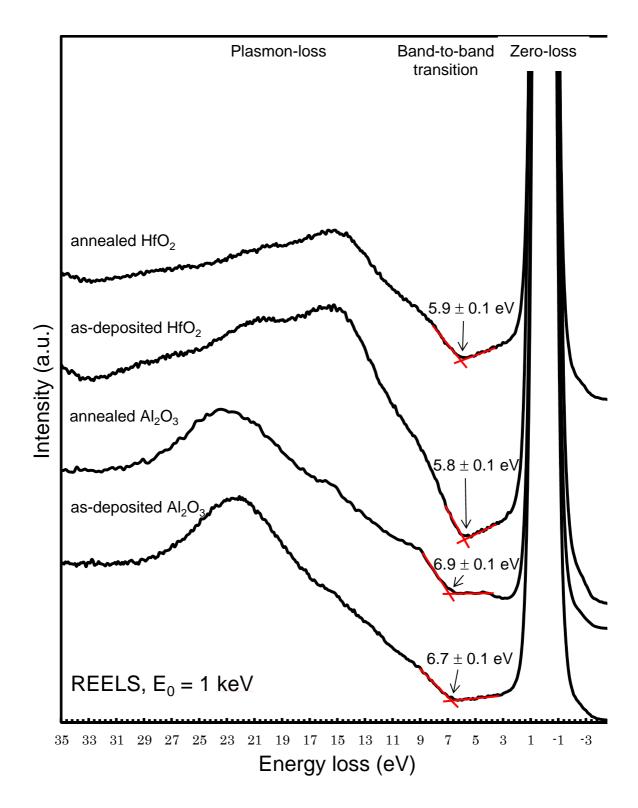

|       | 3.3.3   | Band Gap of HfAlO and HfO2 in MAHOS Structures                                                                               | 3 – 9  |

| 3.4   | Band    | Alignment in MAHOS Capacitor Structures                                                                                      | 3 – 9  |

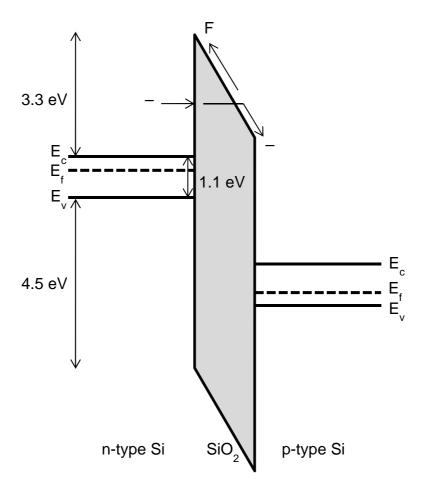

|       | 3.4.1   | Band Alignment of SiO <sub>2</sub> in SiO <sub>2</sub> /p-type Si Structures                                                 | 3 – 9  |

|       | 3.4.2   | Band Alignment of MAHOS Structures in Flatband Condition                                                                     | 3 - 11 |

|       | 3.4.3   | Band Alignment of High-κ Oxide in Contact with High-κ Oxide                                                                  |        |

|       |         | in Thermodynamic Equilibrium                                                                                                 | 3 – 19 |

|       | 3.4.4   | Band Alignment of High-к Oxide in Contact with SiO <sub>2</sub> /p-type Si                   |            |

|-------|---------|----------------------------------------------------------------------------------------------|------------|

|       |         | Structures in Thermodynamic Equilibrium                                                      | 3 – 20     |

| 3.5   | Sumn    | nary                                                                                         | 3 – 22     |

| Refer | ences   | ·                                                                                            | 3 – 24     |

| Figur | es of R | esults                                                                                       | 3 – 28     |

|       |         |                                                                                              |            |

| Chap  | ter 4:  | Charge Trapping in Capacitor Structures with As-deposited High                               | - <b>K</b> |

|       | Diele   | ctric Materials as Charge Trapping Layers                                                    |            |

| 4.1   | Introd  | duction                                                                                      | 4 – 1      |

|       | 4.1.1   | Background on Using Al <sub>2</sub> O <sub>3</sub> /HfO <sub>2</sub> Nanolaminates as Charge |            |

|       |         | Trapping Layer                                                                               | 4 – 1      |

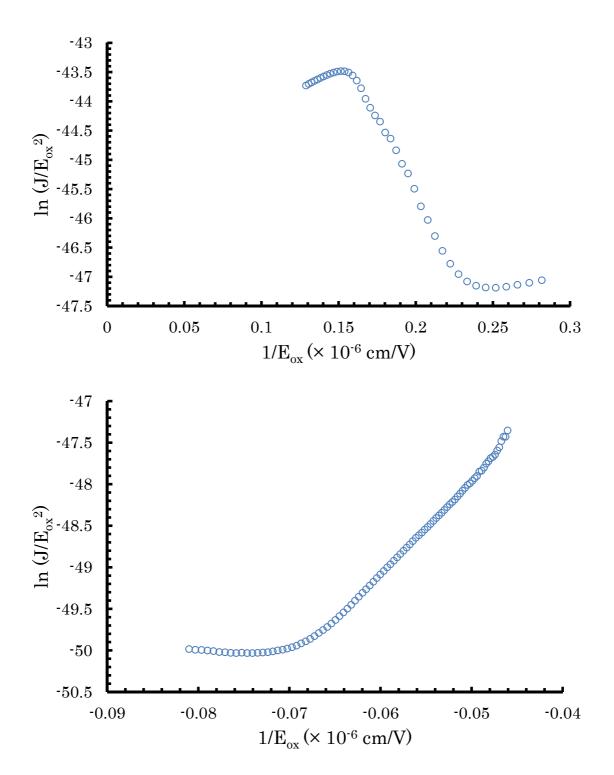

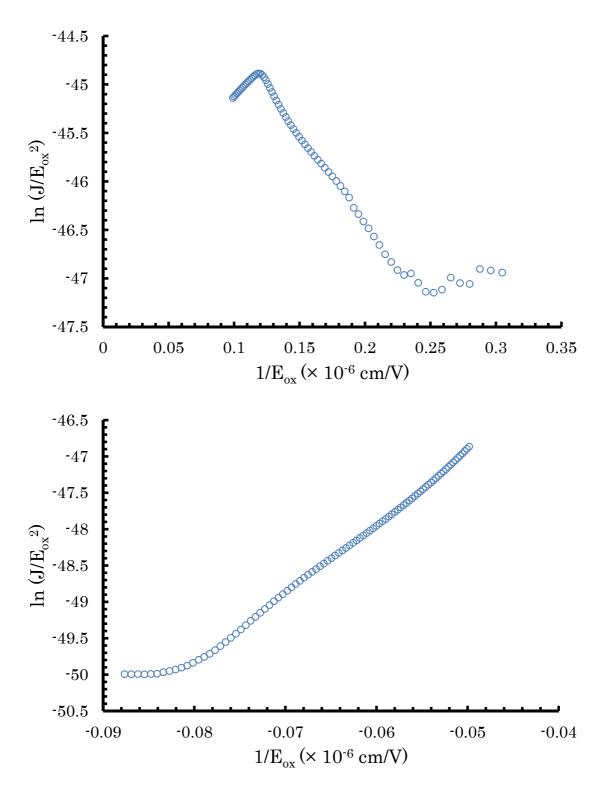

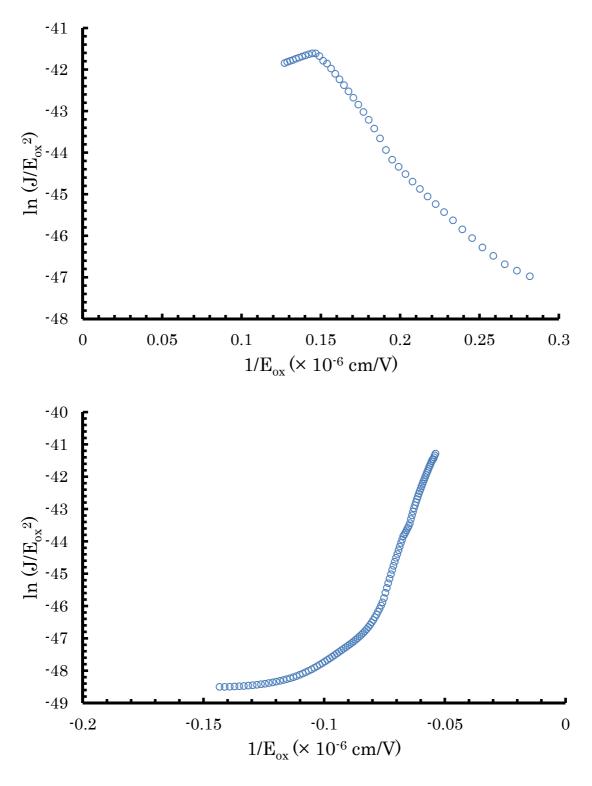

|       | 4.1.2   | Charge Injection Mechanism by Fowler – Nordheim Tunneling                                    | 4 - 2      |

| 4.2   | Meas    | urement Methods                                                                              | 4 – 5      |

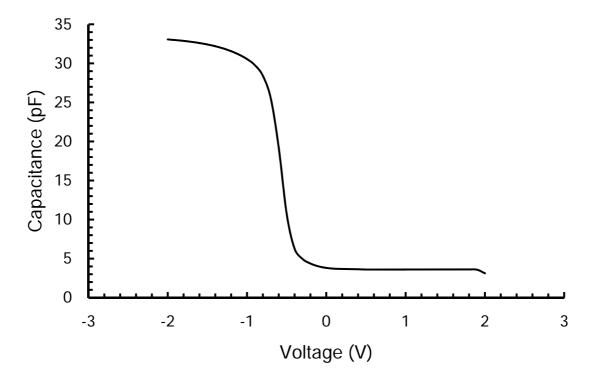

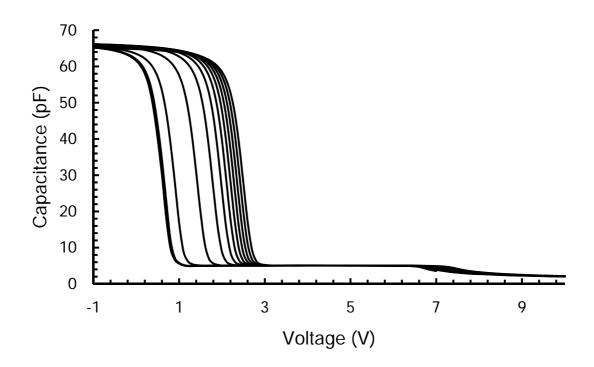

|       | 4.2.1   | High Frequency (1 MHz) Capacitance – Voltage (C – V)                                         |            |

|       |         | Characteristics Measurement                                                                  | 4 – 5      |

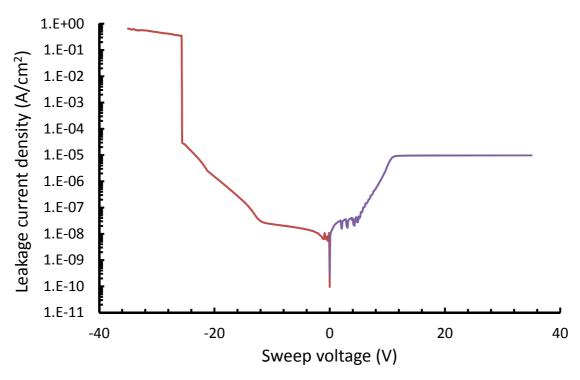

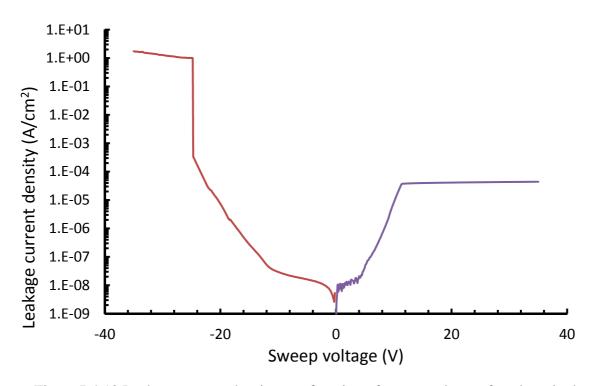

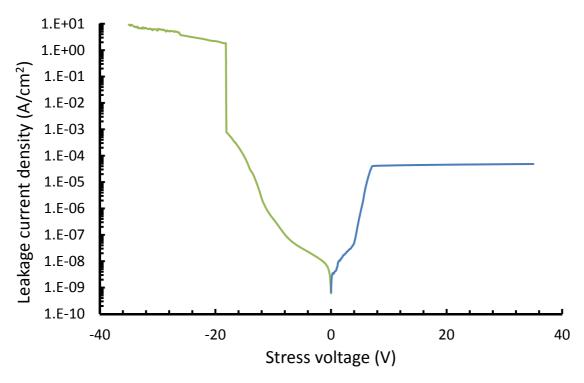

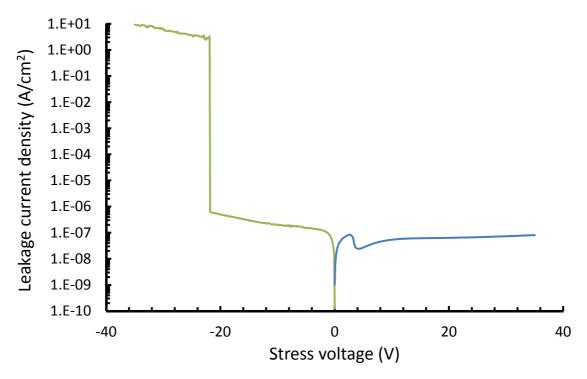

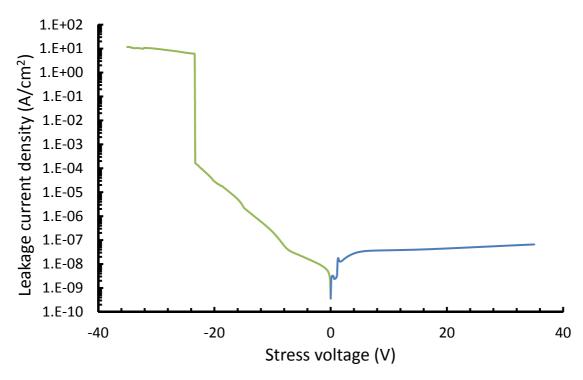

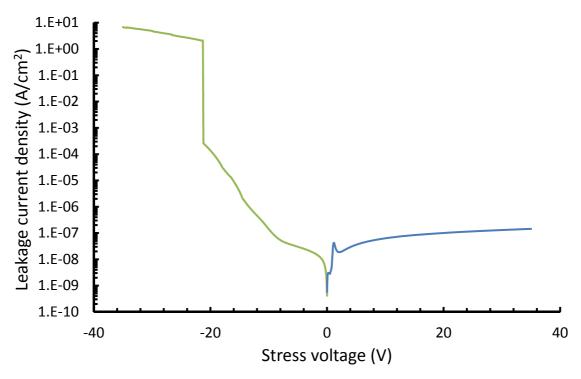

|       | 4.2.2   | Leakage Current Density Measurement                                                          | 4 – 6      |

| 4.3   | Deter   | mination of Dopant Concentration, Electron Concentration,                                    |            |

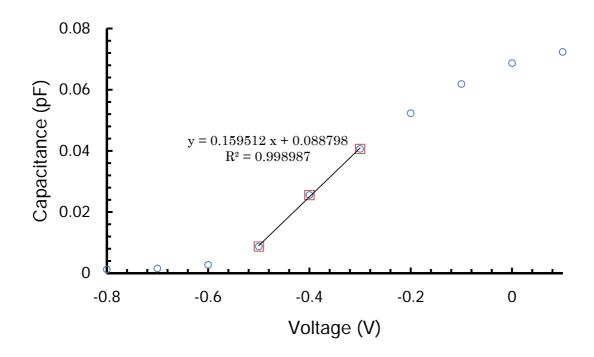

|       | and F   | ermi Level of p-type Silicon Substrate                                                       | 4 – 6      |

|       | 4.3.1   | Dopant Concentration                                                                         | 4 – 6      |

|       | 4.3.2   | Carrier Concentrations and the Fermi Level at Equilibrium                                    | 4 – 9      |

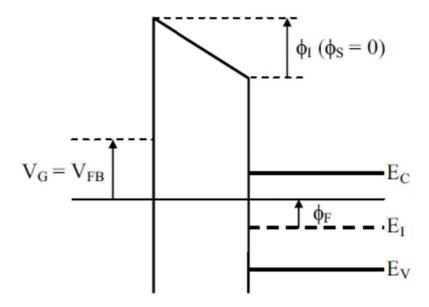

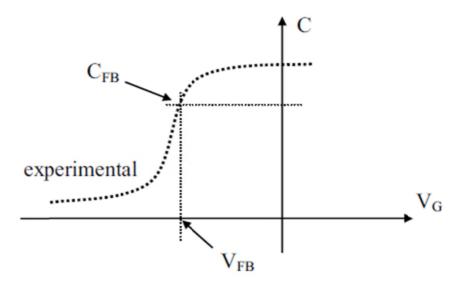

| 4.4   | Neutr   | al Flatband Voltage Determination                                                            | 4 – 9      |

|       | 4.4.1   | Flatband Voltage Calculation                                                                 | 4 – 9      |

|       | 4.4.2   | Neutral Flatband Voltage in As-deposited MAHOS Capacitor                                     |            |

|       |         | Structures                                                                                   | 4 – 12     |

| 4.5   | Charg   | ge Trapping in As-deposited MAHOS Capacitor Structures                                       | 4 – 13     |

| 4.6   | Leaka   | age Current Measurement in As-deposited MAHOS Capacitor                                      |            |

|       | Struc   | tures                                                                                        | 4 – 16     |

| 4.7   | Suma    | ary                                                                                          | 4 – 17     |

| Refer |         | · · · · · · · · · · · · · · · · · · ·                                                        |            |

| Figur | es of R | esults                                                                                       | 4 – 20     |

| Chap  | oter 5: Charge Trapping in Capacitor Structures with Annealed High-κ |        |

|-------|----------------------------------------------------------------------|--------|

|       | Dielectric Materials as Charge Trapping Layers                       |        |

| 5.1   | Introduction                                                         | 5 – 1  |

| 5.2   | Measurement Methods                                                  | 5 - 2  |

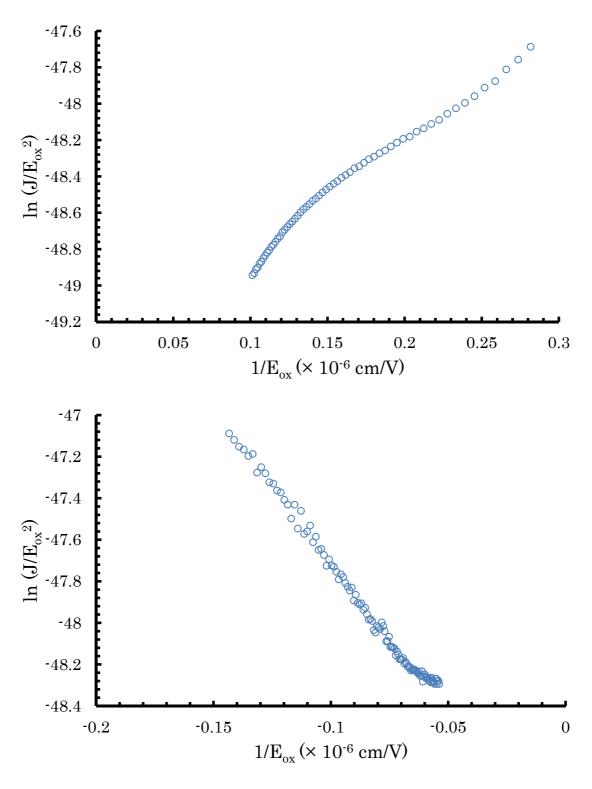

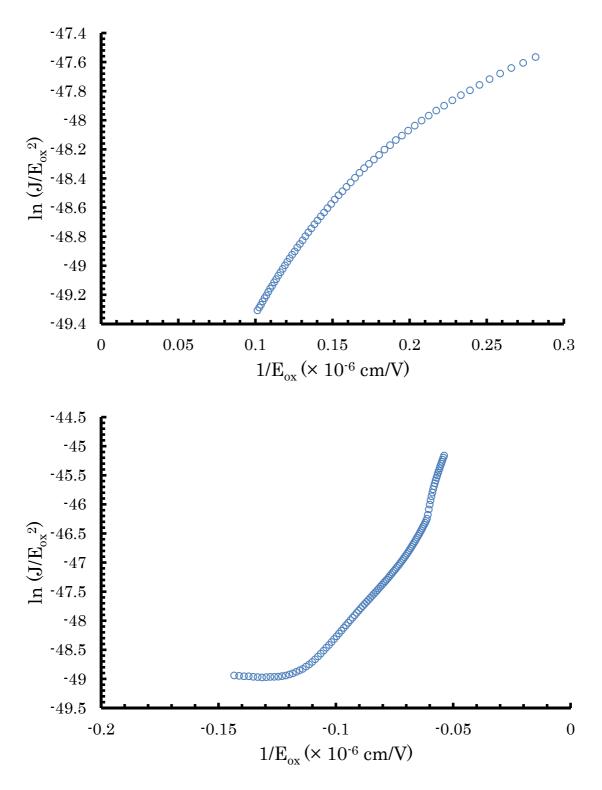

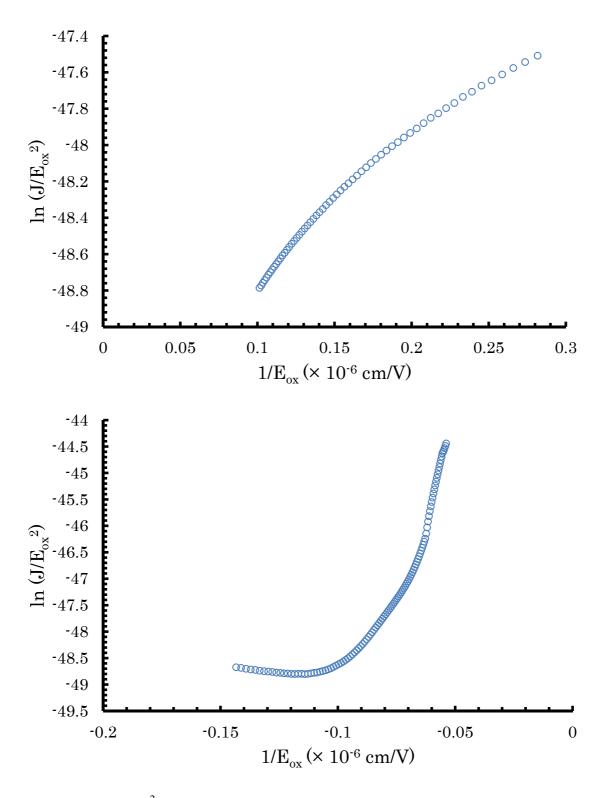

| 5.3   | Neutral Flatband Voltage in Annealed MAHOS Capacitor Structures      | 5 – 3  |

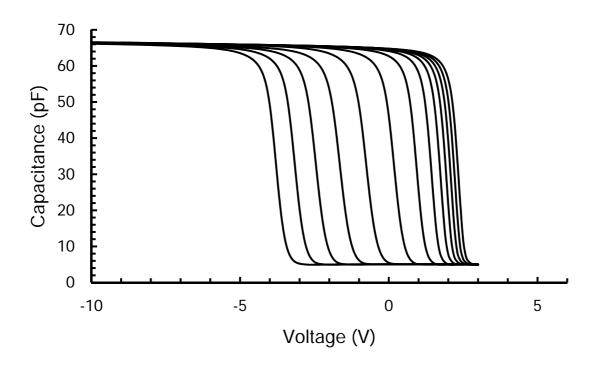

| 5.4   | Charge Trapping in Annealed MAHOS Capacitor Structures               | 5 - 4  |

| 5.5   | Leakage Current Density in Annealed MAHOS Capacitor Structures       | 5 – 6  |

| 5.6   | Summary                                                              | 5 – 7  |

| Refer | rences                                                               | 5 – 8  |

| Figur | es of Results                                                        | 5 – 10 |

|       |                                                                      |        |

| Chap  | ter 6: Conclusions and Recommendations for Future Works              |        |

| 5.1   | Conclusions                                                          | 6 – 1  |

| 5.2   | Recommendations for Future Works                                     | 6 - 4  |

#### Chapter 1

#### Introduction

In this chapter, the basics of non-volatile memory will be described and the role of high-κ dielectric materials as tunneling layer, blocking layer, and charge trapping layer in memory structures will be reviewed. Current status on utilizing high-κ dielectric materials as charge trapping layers will be discussed. Motivation of this research will be stated. Issue and challenges in this field of research will be identified. Strategy to solve the issue is proposed and the chapter is ended by stating our research purposes which would be the centerpiece of our work.

#### 1.1 The Basics of Non-Volatile Memory

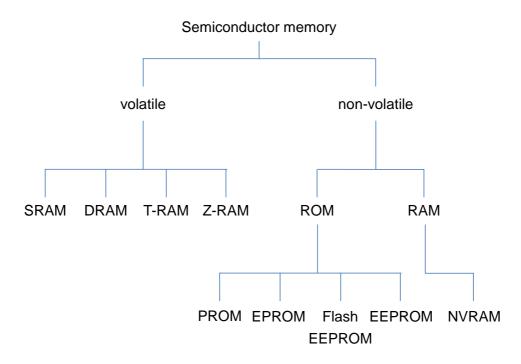

Based on data loss due to disconnected power supply, memory device can be classified into two groups, including volatile memory and non-volatile memory, as shown in Figure 1.1. Volatile memory, such as SRAM and DRAM, is memory that requires power to maintain the stored information. A volatile memory typically has a worst case retention time of less than a second. Non-volatile memory is memory that has the ability to maintain data when the circuit power supply is turned off. Non-volatile memories have two major application, including code applications and data applications<sup>[1]</sup>. For code applications, non-volatile memories store the program and operating system and process it by microprocessor or microcontroller. Non-volatile memory integration in logic systems allows software updates, stores identification codes, or reconfigures the system on the field. In this sense, non-volatile memory devices are widely used in several fields, such as in the computer environment, on the computer network equipments, and in the automotive electronics. In the computer environment, non-volatile memory stores and updates the operation system in PC BIOS and harddisk drives, in almost all peripherals such as printers and DVD-readers, and in

most add-on boards such as video and sound cards. On computer network equipments, non-volatile memory upgrades the software in modems, interface cards and network routers. In the automotive electronics field, non-volatile memories are used in vital function such as engine control units (ECUs) and global positioning systems (GPS). For data applications, non-volatile memories are used as data storage where data files for document, audio and video files are recorded and read sequentially. This is to create storing elements like memory boards or solid-state hard disks, made by Flash memory arrays, which are configured to create large size memories.

Flash EEPROM, which is a type of non-volatile memory, can be electrically programmed and erased. There are some variants of Flash, but in current production, Flash memory is dominated by two types, including NAND Flash, which is oriented toward datablock storage applications, and NOR Flash, which is suited for code and word addressable data storage. Flash memory devices are mainly charge-based where charge can be injected into or removed from a critical region of a device and the presence or absence of the charge can be sensed. Charge-based memory was invented by Sze and Kahng at Bell Labs in 1967<sup>[1]</sup>. The program/erase state is defined via adding charges to and removing charges from the charge-storage layer respectively. Charge-based memory is compatible with the complementary metal-oxide-semiconductor (CMOS) technology, and easy to be integrated with current fabrication process.

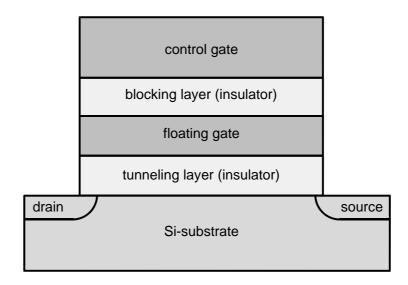

Figure 1.2 shows the cross-section of a floating-gate memory transistor which is the first generation of charge-based memory structure. The floating-gate memory consists of a polysilicon layer formed within the gate insulators, tunneling layer and blocking layer, between the normal gate electrode (the control gate) and the channel. The amount of charge is injected on the floating gate during programming. Since the floating gate is completely surrounded by insulators, it retains charge for a long period of time independent of whether

Figure 1.1 Classification of semiconductor memory.

Figure 1.2 The structure of charge-based memory transistor.

the circuit power supply voltage is present.

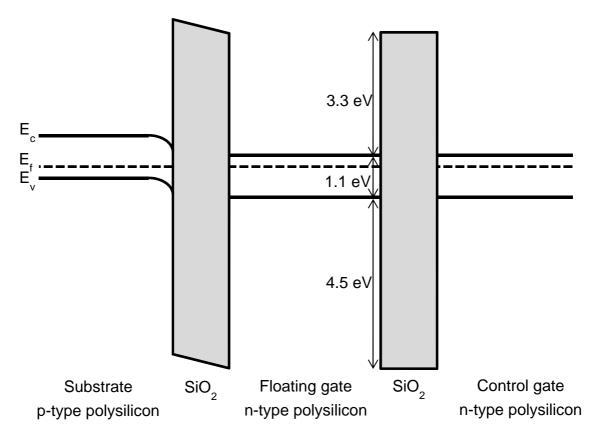

To understand the nature of the charge-based memory device, we need to consider the energy levels involved. Figure 1.3 shows the band structure for a simple charge-based memory device. The n-type poly-Si floating gate is embedded within insulators and isolated from the exit or entry of charge by the high – energy barrier. These barriers, which are much greater than the thermal energy, provide nonvolatile retention of the charge. The amount of charge stored on the floating gate can be changed by changing the potential of the floating gate relative to the potential on the opposite side of either SiO<sub>2</sub> layer until some conduction mechanism is invoked that can overcome or tunnel through the barrier. Two common conduction mechanisms are channel hot – electron (CHE) injection and Fowler – Nordheim (FN) tunneling.

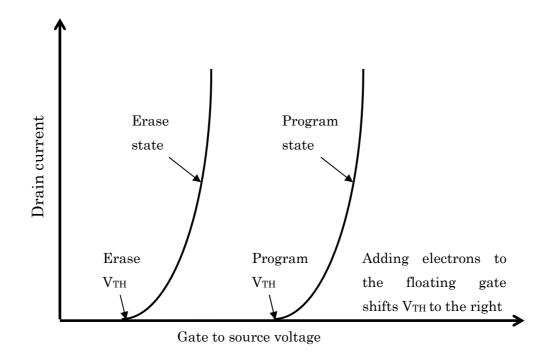

The process of writing or storing data into a charge-based memory involves two operations, including initializing the state of the cells which means that all of the cells are cleared to a "one" state and programming the cells to "zero" or left at "one" in accord with the input data signals. Figure 1.4 shows the relative relationship of the erase and program states in terms of the resulting current – voltage characteristics. Erasing moves the threshold voltage in a negative direction while writing moves the threshold voltage in a positive direction.

There are two parameters that describe reliability of a nonvolatile memory cell, including retention and endurance<sup>[1]</sup>. Retention defines the elapsed time between data storage and the first erroneous readout of the data. There are three factors that can impact the retention properties, which are defects associated with materials, details of device geometry, and aspects of circuit design. Each of these three factors can result in the addition or removal of charge to/from the floating gate. The processes involved in writing or reading non-volatile memory cells results in stresses that eventually degrade the properties of the memory or

Figure 1.3 Energy band diagram for a typical charge-based memory structure.

Figure 1.4 The current – voltage characteristics of erase state and program state.

disturb the contents of the memory. The ability of a device to withstand stresses is called endurance which is quantified as a minimum number of erase – write cycles or write – read cycles that the non-volatile memory chips can be expected to survive.

#### 1.2 The Role of High-κ Dielectric Materials in Non-Volatile Memory

The use of high-κ dielectric materials in electronic devices, such as metal-oxide-semiconductor field effect transistors (MOSFETs) is prompted by the need of new gate insulators to replace SiO<sub>2</sub> in future generation of MOSFETs in order to meet the attempt to reduce the device dimensions by following Moore's law. Due to higher dielectric constant, with the same equivalent oxide thickness (EOT) with SiO<sub>2</sub>, high-κ dielectric materials can be thicker without reducing the device performance.

In recent development of floating gate structure for non-volatile memory application, high- $\kappa$  dielectric has been investigated as tunneling layer replacing SiO<sub>2</sub>, blocking layer, and charge trapping layer.

#### 1.2.1 High-к Dielectric Materials as Blocking Layer

The first generation flash memory uses SiO<sub>2</sub> as blocking layer. As the flash memory's dimension is continually scaled down, the use of SiO<sub>2</sub> become unacceptable due to the large tunneling current through SiO<sub>2</sub>. Since the erase speed for this type of SONOS devices is determined by the competition of the direct band-to-band tunneling current through a tunnel oxide and the unwanted Fowler-Nordheim tunneling current through a blocking oxide, the tunnel oxide thickness is fundamentally required to be less than 2 nm for a stable erase operation. Therefore, numerous attempts have been tried to replace thermal oxides by new dielectrics or related new structures.

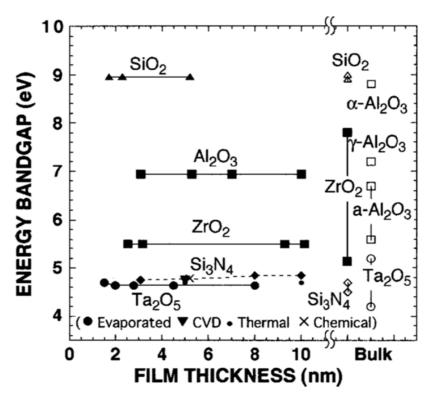

As the blocking oxide layer, high- $\kappa$  dielectrics proportionally reduced the electric field across the blocking oxide with its dielectric constant. Therefore, electron injection from

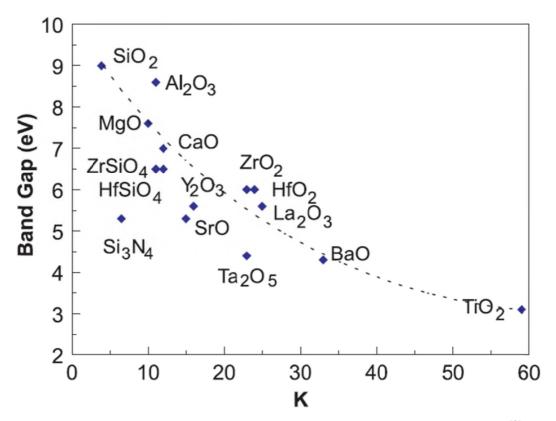

the gate during erase can be effectively suppressed, which will generally in turn enhance the erase speed. In addition, using a physical thicker blocking layer film minimizes the electron leaking out to the gate during retention. Materials with high- $\kappa$  dielectric constants can be seen in Figure 1.5<sup>[3]</sup>. There are some good candidate dielectrics to replace SiO<sub>2</sub>, including Al<sub>2</sub>O<sub>3</sub> and rare earth oxides, such as Gd-based dielectric (Gd<sub>2</sub>O<sub>3</sub> and Al-doped Gd<sub>2</sub>O<sub>3</sub>), La-based dielectric (La<sub>2</sub>O<sub>3</sub> and LaAlO<sub>x</sub>), and Y-based dielectric (Y<sub>2</sub>O<sub>3</sub> and Y<sub>x</sub>Al<sub>y</sub>O)<sup>[4-7]</sup>.

Al<sub>2</sub>O<sub>3</sub> has some favourable properties, including a wide band gap, high dielectric constant ( $\kappa \sim 9$ ) which is higher than SiO<sub>2</sub> ( $\kappa \sim 3.9$ ), good thermodynamic stability on Si up to high temperatures, and amorphous under the condition of interest. Fast program/erase operation by Fowler - Nordheim (FN) tunneling has been achieved by utilizing Al<sub>2</sub>O<sub>3</sub> as blocking layer in SANOS structure which consist of Si/Al<sub>2</sub>O<sub>3</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>/Si<sup>[4]</sup>. In addition, this structure achieves longer data retention and realizes lower voltage programming. Faster operation speed has also been obtained by using Al<sub>2</sub>O<sub>3</sub> as blocking layer. However, due to its dielectric constant, Al<sub>2</sub>O<sub>3</sub> is not suitable as long-term solution. Gd-based dielectric shows a superior charge retention property and an improved operation speed<sup>[5]</sup>. La-based dielectric is considered as blocking layer due to its relatively large conduction band offset and high dielectric constant<sup>[6]</sup>. Its properties provide faster program speed, wider threshold voltage window, more robustness to voltage stress, and has a better retention properties under temperature below 120°C. Y<sub>2</sub>O<sub>3</sub> is also potential as blocking layer due to its strongest affinity for oxygen, no humidity absorption, and no magnetic characteristic. However Y<sub>2</sub>O<sub>3</sub> has poor thermal property and relaatively small band gap, ~6 eV. The optimized YxAlyO film shows lower interface-state density, lower bulk charge-trapping density, higher dielectric constant, and smaller gate leakage, due to the suppressed interlayer and good thermal property ascribed to appropriate Y and Al contents in the thin film<sup>[7]</sup>.

#### 1.2.2 High-κ Dielectric Materials as Tunneling Layer

SiO<sub>2</sub> is used as tunneling layer in the first generation of flash memory and SONOS. SiO<sub>2</sub> is chosen because it can be thermally grown on Si substrate, has the largest band gap among dielectric materials, and make a good contact with Si with best interface quality as well as least oxide traps, thus lowest leakage current. Considering reliability degradation issue, thermal SiO<sub>2</sub> is still the best option as tunneling layer. For the next generation flash memory, it is required that memory devices have thinner tunneling oxide to achieve higher program/erase speeds and lower operating voltages. However, SiO<sub>2</sub> as tunneling layer suffers from retention problem due to direct tunneling leakage through the thin tunnel oxide.

To solve the retention issue, a band-gap engineered ONO tunneling dielectric was proposed to replace the traditional SiO<sub>2</sub> in SONOS structure since the ultra-thin nitride which is less than 2 nm has negligible charge trapping<sup>[8]</sup>. This concept is demonstrated by a multilayer structure of SONONOS with the ultra-thin O1/N1/O2 structure as a tunneling dielectric, N2 as the charge storage layer, and O3 as the blocking oxide. The ultra-thin ONO structure suppresses direct tunneling at low electric field during retention, while it allows efficient hole tunneling erase at high electric field due to the band offset. The ONO tunneling dielectric serves as an efficient hole tunneling barrier for SONOS, and it is much more reliable and practical. Therefore, this SONOS offers fast hole tunneling erase, while it is immune to the retention problem of the conventional SONOS.

Another option to solve the retention issue due to tunneling layer scaling is to utilize a novel multilayer tunnel barrier which consists of a two-layer dielectrics stack with a low-κ/high-κ combination or three-layer dielectric stack with low-κ/high-κ/low-κ combination in symmetric form that allows for either lower voltage or higher speed programming due to the increased current-voltage (I-V) slope<sup>[9]</sup>. The stack can be regarded as a VARIable Oxide Thickness (VARIOT) dielectric. The thicker physical thickness of the

stack offers better retention as compared to the EOT layer at low biases.

#### 1.2.3 High-κ Dielectric Materials as Charge Trapping Layer

In 1990s, the performance and reliability of non-volatile memory (NVM) was enhanced by appplying silicon-oxide-nitride-oxide-silicon (SONOS) technology in which thin  $Si_3N_4$  film was used as charge trapping layer replacing the conducting polysilicon floating-gate electrode<sup>[10]</sup>.  $Si_3N_4$  film in SONOS device improved endurance since a single defect will not cause the discharge of the memory. In SONOS memory, the charges are stored in isolated sites within the  $Si_3N_4$  dielectric. To suppress short-channel effects, it is required to scale down the charge-trapping layer to <6 nm. However, this becomes issue since the charge trapping deteriorates when the  $Si_3N_4$  is made thinner. Very little charge trapped in a 2 nm  $Si_3N_4$  layer in SONOS. In addition, the high temperature retention also gets worse when the  $Si_3N_4$  is thin because of the higher trap energy in the oxide/ $Si_3N_4$ /oxide, arising from quantum confinement.

The dielectric constant of  $Si_3N_4$ ,  $\kappa \sim 7$ , is not so high that it also faces issues related to the the continual down-scaling of cell size and reduction of operating voltage. Various high- $\kappa$  dielectrics with higher  $\kappa$  value have been widely investigated as charge trapping layer to solve these issues. With higher dielectric constant, high- $\kappa$  dielectrics allow a higher electric field over the tunnel dielectric and results in enhanced program/erase speed. For charge trapping layer, crystalline high-k dielectrics is preferable than amorphous one, for example, tetragonal and cubic  $ZrO_2$ , have theoretical k-values of 46.6 and 36.8, respectively, which are much higher than their amorphous-phase counterpart, so they will be beneficial to enhance memory performance<sup>[11]</sup>.

In addition, high- $\kappa$  dielectrics should have a larger conduction-band offset with respect to the tunnel dielectric to get better charge retention. Another drawback of  $Si_3N_4$  as charge trapping layer in SONOS structure is it has small conduction band discontinuity at the

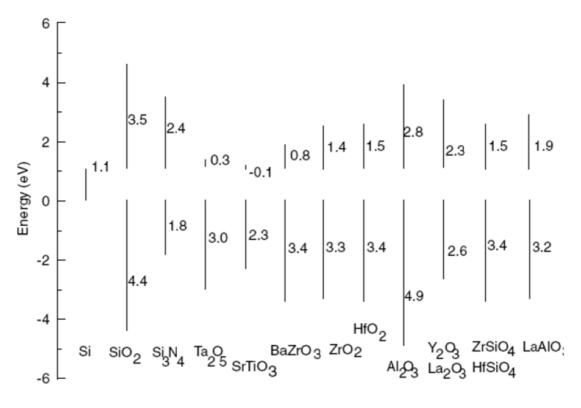

Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> interface, which causes the charge leak out from the shallow trap levels of Si<sub>3</sub>N<sub>4</sub>. To overcome this problem, high-*k* dielectric materials, such as ZrO<sub>2</sub>, HfO<sub>2</sub>, and Ta<sub>2</sub>O<sub>5</sub> are promising candidates to replace a Si<sub>3</sub>N<sub>4</sub> film as the charge trapping layer of SONOS memory devices since they have a larger conduction-band offset as shown in Figure 1.6<sup>[12]</sup>. By using such high-*k* dielectric films, charge trapping characteristics can be improved since they have sufficient densities of trap states and deep trap energy levels which give rise to better data retention.

#### 1.3 Background of the Research

#### **1.3.1** Motivation of the Research

The development of the next generation charge-based non-volatile memory requires the memory device to be scaled down without deteriorating the charge trapping characteritics of the device and to be able to achieve fast programming/erasing speed with low programming voltage and good retention for over 10 years. The scaling projection for charge-based non-volatile memory devices can be found in the International Technology Roadmap for Semiconductor (ITRS) documents. The ITRS scaling projection has been used by researchers as a guideline for further improvement in the field of non-volatile memory. Table 1.1 and Table 1.2 show the ITRS scaling projection for charge trapping NAND flash and NOR flash, respectively. The memory devices will progressively scaled down beyond 25 nm technology.

Thermally grown SiO<sub>2</sub> is still the best choise as tunneling layer since amorphous SiO<sub>2</sub> is an excellent insulator with very few electronic defects and it forms an excellent interface with Si. As tunneling layer, its thickness cannot be reduced to less than 3 nm because because the charge will tunnel across it by direct tunneling mechanism. Instead of SiO<sub>2</sub>, the ONO structure which consists of SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> stack is used as tunneling layer since it

Figure 1.5 Static dielectric constant vs. band gap for candidate gate oxides<sup>[3]</sup>.

Figure 1.6 Band alignments of high-  $\!\kappa$  dielectrics  $^{[12]}\!.$

Table 1.1 International Technology Roadmap for Semiconductors (ITRS) scaling projections for charge trapping NAND flash<sup>[13]</sup>.

| Year of Production                                               | 2012                    | 2013                    | 2014                    | 2015                    | 2016                           | 2024                           |

|------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------------------|--------------------------------|

| Charge trapping NAND Flash (MANOS or Barrier Engineering)        |                         |                         |                         |                         |                                |                                |

| NAND Flash poly 1/2 Pitch (nm)                                   | 25                      | 22                      | 20                      | 19                      | 18                             | 8                              |

| Cell size – area factor a in multiples of F <sup>2</sup> SLC/MLC | 4.0/1.3                 | 4.0/1.3                 | 4.0/1.0                 | 4.0/1.0                 | 4.0/1.0                        | 4.0/1.0                        |

| Tunnel dielectric material                                       | SiO <sub>2</sub> or ONO        | SiO <sub>2</sub> or ONO        |

| Tunnel dielectric thickness EOT (nm)                             | 3 – 4                   | 3 – 4                   | 3 – 4                   | 3 – 4                   | 3 – 4                          | 3 – 4                          |

| Blocking dielectric material                                     | $Al_2O_3$               | $Al_2O_3$               | $Al_2O_3$               | $Al_2O_3$               | Al <sub>2</sub> O <sub>3</sub> | Al <sub>2</sub> O <sub>3</sub> |

| Blocking dielectric thickness EOT (nm)                           | 6 – 8                   | 6 – 8                   | 6                       | 6                       | 6                              | 5                              |

| Charge trapping layer material                                   | SiN                     | SiN                     | SiN                     | SiN                     | SiN/high-κ                     | SiN/high-κ                     |

| Charge trapping layer thickness (nm)                             | 5 – 7                   | 5                       | 4 – 6                   | 4 – 6                   | 4 – 6                          | 3 – 4                          |

| Gate material                                                    | Metal                   | Metal                   | Metal                   | Metal                   | Metal                          | Metal                          |

| Highest W/E voltage (V)                                          | 15 – 17                 | 15 – 17                 | 15 – 17                 | 15 – 17                 | 15 – 17                        | 15 – 17                        |

| Endurance (erase/write cycles)                                   | $10 \times 10^5$        | $10 \times 10^4$        | $10 \times 10^4$        | $10 \times 10^4$        | $10 \times 10^4$               | $10 \times 10^4$               |

| Non-volatile data retention (years)                              | 10 – 20                 | 10 – 20                 | 10 – 20                 | 10 – 20                 | 5 – 10                         | 5 – 10                         |

| Maximum number of bits per cell (MLC)                            | 3                       | 3                       | 4                       | 4                       | 4                              | 4                              |

Table 1.2 International Technology Roadmap for Semiconductors (ITRS) scaling projections for charge trapping NOR flash<sup>[13]</sup>.

| Year of Production                                                         | 2012             | 2013             | 2014             | 2015             | 2016             | 2024    |

|----------------------------------------------------------------------------|------------------|------------------|------------------|------------------|------------------|---------|

| Charge trapping NOR Flash (SONOS/NROM)                                     |                  |                  |                  |                  |                  |         |

| SONOS/NROM technology node, F (nm)                                         | 35               | 32               | 28               | 25               | 22               | 10      |

| SONOS/NROM cell size – area factor a in multiples of F <sup>2</sup>        | 7 – 8            | 7 – 8            | 7 – 8            | 8 – 9            | 8 – 9            | 9 – 10  |

| Cell size (per bit) – area factor a in multiples of F <sup>2</sup> SLC/MLC | 3.7/1.9          | 3.7/1.9          | 3.7/1.9          | 4.3/2.2          | 4.3/2.2          | 4.8/2.4 |

| Gate length L <sub>g</sub> , physical (nm)                                 | 100              | 100              | 90               | 90               | 80               | 60      |

| Tunnel oxide thickness (nm)                                                | 4.5              | 4                | 4                | 4                | 4                | 3.5     |

| Charge trapping layer thickness (nm)                                       | 4 – 6            | 4 – 6            | 4 – 6            | 4 – 5            | 4 – 5            | 4       |

| Blocking (top) dielectric material EOT (nm)                                | 6 – 8            | 6 – 8            | 6 – 8            | 5 – 7            | 5 – 7            | 5 – 7   |

| Highest W/E voltage (V)                                                    | 6 – 8            | 6 – 8            | 5 – 7            | 5 – 7            | 5 – 7            | 4 – 6   |

| I <sub>read</sub> (μA)                                                     | 17 – 22          | 15 – 20          | 14 – 19          | 13 – 18          | 12 – 17          | 6 – 10  |

| Endurance (erase/write cycles)                                             | $10 \times 10^5$ | $10 \times 10^5$ | $10 \times 10^5$ | $10 \times 10^6$ | $10 \times 10^6$ |         |

| Non-volatile data retention (years)                                        | 10 – 20          | 10 – 20          | 10 – 20          | 10 – 20          | 10 – 20          | 10 – 20 |

| Maximum number of bits per cell (physical 2-bit/cell + MLC)                | 2-4              | 2 – 4            | 2 – 4            | 4                | 4                | 4       |

suppresses direct tunneling at low electric field during retention and allows efficient hole tunneling erase at high electric field. Al<sub>2</sub>O<sub>3</sub> is used as blocking layer due to good thermodynamic stability on Si up to high temperatures, higher dielectric constant of 9, and a wide band gap. The thickness of Al<sub>2</sub>O<sub>3</sub> is projected to be reduced to 5 nm in 2024. As charge trapping layer, Si<sub>3</sub>N<sub>4</sub> is used since the charges are stored in isolated sites within the Si<sub>3</sub>N<sub>4</sub> dielectric and it provides good endurance. The thickness of charge trapping layer is projected to be scaled down to about 4-6 nm in the next few years and 3-4 nm in 2024 and it has been reported that Si<sub>3</sub>N<sub>4</sub> as charge trapping layer faces issues related to the the continual down-scaling of cell size. Therefore, high- $\kappa$  dielectric material is considered to replace Si<sub>3</sub>N<sub>4</sub>.

## 1.3.2 Current Status of Research utilizing High-k Dielectric Materials as Charge Traping Layers

Many non-volatile memory structures have been prepared with high-κ dielectric materials as charge trapping layer in various kinds of structures, such as SOHOS device, MHOS device, MONOS device, MOHOS device etc. Different kinds of methods have been used to deposit materials, including chemical vapour deposition, reactive magnetron sputtering, atomic layer deposition, etc. Charge trapping characteristics, including program/erase characteristic, endurance characteristics, and retention characteristics have been reported.

The polysilicon–oxide–high- $\kappa$ –oxide–silicon (SOHOS) structure with high- $\kappa$  dielectrics as charge trapping layer have been investigated. Compared to the conventional SONOS devices, the SOHOS structure, with HfO<sub>2</sub> as the charge-storage layer, demonstrates a superior charge-storage capability at low voltages, faster programming, and less over-erase problems compared to the conventional SONOS devices. However, it suffers from a poorer charge-retention capability than the SONOS one. On the other hand, The SOHOS structure with  $Al_2O_3$  as the charge-storage layer results in an improved charge-retention performance,

but at the expense of a slower programming speed. By adding a small amount of Al to HfO<sub>2</sub> to form HfAlO, the SOHOS structure with HfAlO as the charge trapping layer combines the advantages of both HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>, such as fast programming speed and good charge-retention capability<sup>[14]</sup>. In this structure, electron trapped in the bulk of the HfAlO layer, rather than negative charge trapping at the tunnel oxide/high-*k* interface, since the charge-storage capability depends on the HfAlO thickness.

The charge trapping and tunneling characteristics of the metal-hafnium-oxide-semiconductor (MHOS) structure capacitors with HfO<sub>2</sub> layer as charge trapping layer have been investigated and compared with those of metal-nitride-oxide-semiconductor (MNOS) structure capacitors<sup>[15]</sup>. It is reported that at the same trap layer thickness, the MHOS capacitors showed a larger memory window than the MNOS capacitors. The ultrathin HfO<sub>2</sub> trap layer with a thickness of 2 nm stored almost the same charges with Si<sub>3</sub>N<sub>4</sub> layer with a thickness of 7 nm. These results show that the HfO<sub>2</sub> layer has better charge trapping efficiency than the Si<sub>3</sub>N<sub>4</sub> layer. The MNOS capacitors faces scaling-down issue due to the increase of tunneling current. On the other hand, in MHOS capacitor the gate leakage current due to tunneling was reduced significantly by stacking the HfO<sub>2</sub> trap layer on thin SiO<sub>2</sub> tunnel layer.

In 2008, MONOS memory devices which has the structure of TaN/HfLaON/  $Hf_{1-x-y}N_xO_y/SiO_2/Si$  was fabricated and the nitrogen composition dependence of the characteristics was studied by Yang *et al.*<sup>[16]</sup>. Lower program/erase voltages and better high temperature retention can be achieved with using a higher k  $Hf_{1-x-y}N_xO_y$  dielectric as charge trapping layer. To investigate how nitride composition alters the characteristics, its composition in the  $Hf_{1-x-y}N_xO_y$  was varied. By increasing the N composition in the  $Hf_{1-x-y}N_xO_y$  trapping layer, both the memory window and high-temperature retention can be enhanced. Another MONOS memory device fabricated to improve both the retention time

and the programming speed was a memory structure based on the band engineering considerations of  $HfO_2$  for the tunneling and blocking layer and  $Ta_2O_5$  for the charge storage layer<sup>[17]</sup>. It was observed that the device with  $HfO_2$  which has low charge barrier height and  $Ta_2O_5$  which has deep-trap energy level and proper band offset alignments was able to achieve faster programming and better retention performance simultaneously. The retention decay rate of this device is improved by a factor more than three as compared to the conventional SONOS type devices.

In 2008, a novel charge-trap-engineered flash NVM device was proposed with the structure of p-Si/SiO<sub>2</sub>/LaAlO<sub>3</sub>/HfON/Si<sub>3</sub>N<sub>4</sub>/LaAlO<sub>3</sub>/SiO<sub>2</sub>/metal, combining a 5 nm Si<sub>3</sub>N<sub>4</sub> with a 0.9 nm equivalent oxide thickness (EOT) layer of HfON, within double-barrier and double-tunnel layers. This device shows good retention and a large memory window. At 150 °C and  $\pm 16$  V program/erase, the device showed a program/erase speed of 100  $\mu$ s, an initial  $\Delta V_{th}$  window of 5.6 V and extrapolated 10 year retention of 3.8 V. These results are much better than those of a control charge trap flash device with a single Si<sub>3</sub>N<sub>4</sub> trapping layer, which had a smaller initial  $\Delta V_{th}$  and poorer 10-year retention.

In 2010, a cubic  $ZrO_2$  film was investigated as the charge-trapping layer for nonvolatile memory formed by annealing of amorphous ZrON <sup>[11]</sup>. The memory with a nitrogen-stabilized cubic  $ZrO_2$  film shows promising performance in terms of 3.81 V hysteresis memory window by  $\pm$  7 V program/erase voltage and 1.98 V flat-band voltage shift by programming at  $\pm$  7 V for 10 ms. Improved performance is mainly due to the greatly enhanced k-value of 32.8 and the increased trapping sites provided by grain boundaries.

Rare-earth oxides such as  $Tb_2O_3$  and  $Y_2O_3$  have attracted much interest in research for complementary metal oxide semiconductor (CMOS) applications of high-k materials and are attractive candidates for the trapping layer memory because of good thermodynamic stability, their large energy band gaps, a large conduction band offset with regard to silicon, and high

dielectric constants. A metal-oxide-high-κ-oxide-silicon (MOHOS) memory structure with high-κ  $Tb_2O_3$  charge-trapping layer has been investigated <sup>[18]</sup>. The device annealed at 800 °C exhibited large threshold voltage shift, with memory window of 1.41 V operated at  $V_g = 8$  V at 0.1 s, good data retention with charge loss of 10% measured time up to  $10^4$  s and at 85 °C, and good endurance characteristics with program/erase cycles up to  $10^5$  due to charge trapping at deep trap level. This crystalline  $Tb_2O_3$  has a high dielectric constant of 11.8. Another rare earth oxides,  $Y_2O_3$ , with a high dielectric constant of 18, a high conduction band offset over 2 eV, and a low lattice mismatch with silicon, was used as charge trapping layer in SONOS memory device <sup>[19]</sup>. This memory device exhibited large threshold voltage shift, good data retention with charge loss of ~4% measured time up to  $10^4$  s at room temperature, and good endurance characteristics with program/erase cycles up to  $10^5$  because of the higher probability for trapping charge carriers.

Among various high-*k* dielectrics, ternary compounds also have been investigated as charge trapping layer in memory devices, such as SrTiO<sub>3</sub> with its high dielectric constant of 140 and BaTiO<sub>3</sub> with its high dielectric constant of higher than 100. SrTiO<sub>3</sub> has zero band-offset with respect to silicon which is desirable as charge trapping layer for memories to improve the program/erase speeds and retention property. Huang, et al incorporated nitrogen in SrTiO<sub>3</sub> resulted in more charges trap in the band gap through substitution of oxygen by nitrogen<sup>[20]</sup>. This nitrided SrTiO<sub>3</sub> has higher dielectric constant. Ti silicate between the CTL and SiO<sub>2</sub> can be suppressed by nitrogen passivation. The device with nitrided SrTiO<sub>3</sub> showed a larger memory window, higher program/erase speeds and good retention properties with charge loss of 38% after 10<sup>4</sup> s. Another ternary compound used as charge trapping layer is BaTiO<sub>3</sub> which has negative band offset with respect to Si, so it has a large barrier height relative to SiO<sub>2</sub>. Huang et al reported that the isovalent substitution of Ti with Zr in BaTiO<sub>3</sub> in Zr-doped BaTiO<sub>3</sub> has been demonstrated to have higher program speed at low gate voltage, a

lower leakage current than BaTiO<sub>3</sub> while maintaining a comparable dielectric constant, better endurance, and good data retention with charge loss of 6.4% at 150°C for 10<sup>4</sup> s)<sup>[21]</sup>. Zr-doped BaTiO<sub>3</sub> exhibited higher charge-trapping efficiency and higher density of traps.

## 1.3.3 Issues and Challenges of Research utilizing High- $\kappa$ Dielectric Materials as Charge Traping Layers

High- $\kappa$  dielectrics are highly considered for CTM upon continually scaling down of the dimensions of flash memory. The using of high- $\kappa$  dielectrics makes it possible for continual down-scaling of the cell size due to the advantage of using high- $\kappa$  dielectrics which is the high- $\kappa$  dielectrics can have a thicker physical thickness than silicon dioxides for the same equivalent oxide thickness (EOT). As charge trapping layers, high- $\kappa$  dielectrics have to answer some challenges. High- $\kappa$  dielectrics should have sufficient densities of trap states and deep trap energy levels which give rise to better data retention. High- $\kappa$  dielectrics also should have a wide conduction band offset with respect to the tunneling oxide to prevent the charge leak out from the shallow trap levels in high- $\kappa$  dielectrics. In addition, high- $\kappa$  dielectrics have to possess good thermodynamic stability and good compatibility with current semiconductor technologies.

To fabricate the device structure beyond 25 nm technology for electronic purposes, the roughness among layers and the uniformity of the thickness also become major concern. The capability of fabrication technology to deposit semiconductor materials on top of one another with virtually no interface traps is necessary.

To explain the charge trapping characteristic in memory devices, it is essential to evaluate the energy band parameters of each layer in the structure, including the band gap and barrier heights, which include valence band offset (VBO) and conduction band offset (CBO). Some works on the study of charge trapping characteristics evaluated the interfacial barriers using the bulk parameters of solids which can be misleading since the bulk parameters may

not necessarily reflect the properties of thin films.

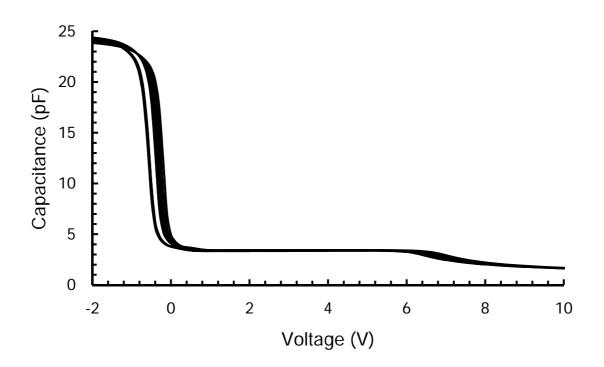

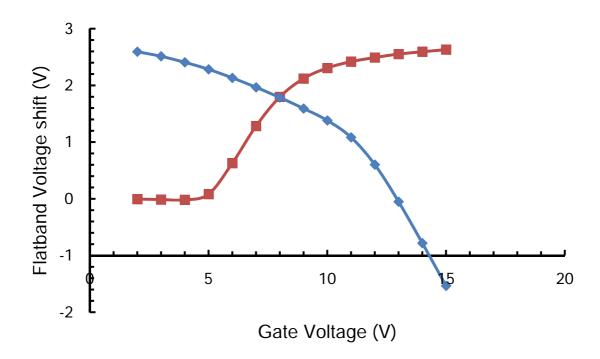

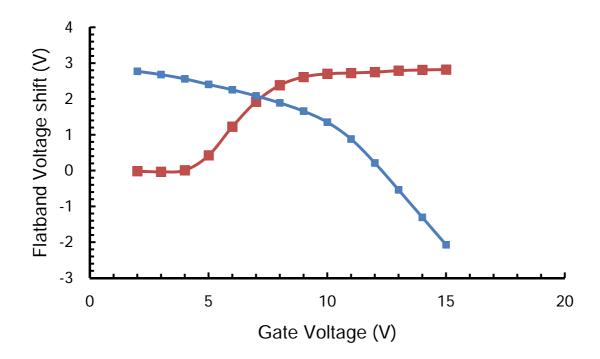

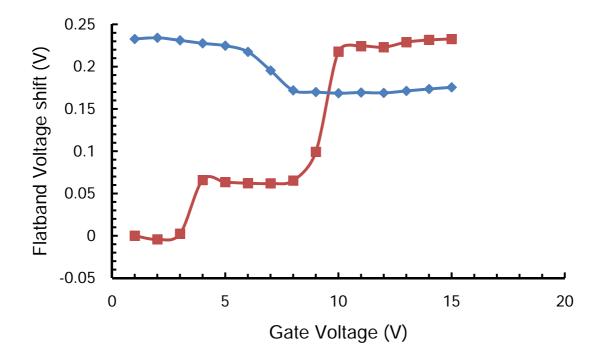

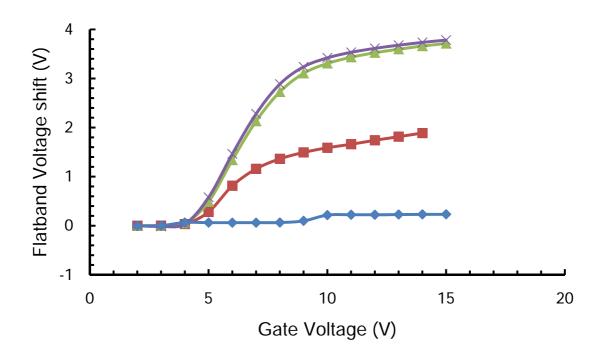

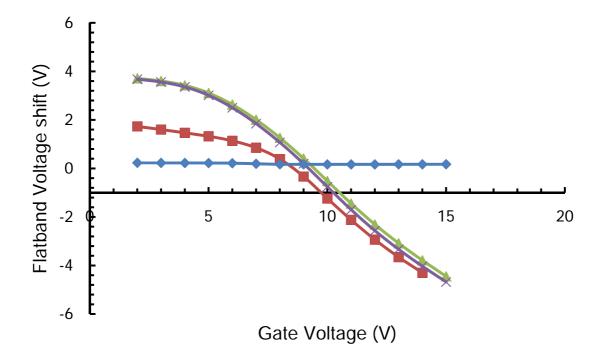

In our preliminary works, it is found that as-deposited capacitor structure with amorphous high- $\kappa$  as charge trapping layer did not trap electrons during inversion step, but it trap holes during accumulation step in capacitance – voltage (C – V) measurement. The charge trapping in high- $\kappa$  is related to the presence of the electronic defects. This issue of charge trapping should be explained after evaluating the device structures and energy band parameters.

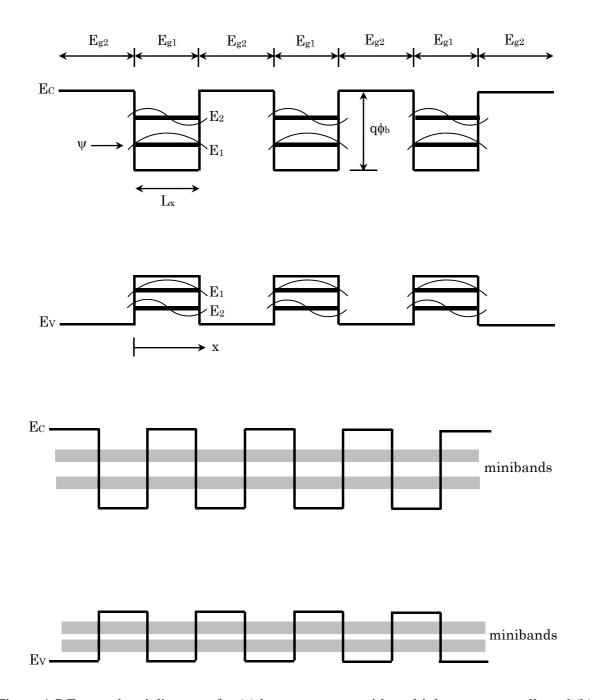

#### 1.4 What to Propose and the Purpose of the Research

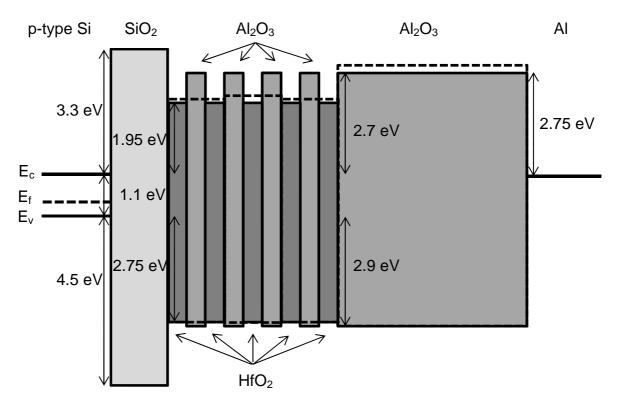

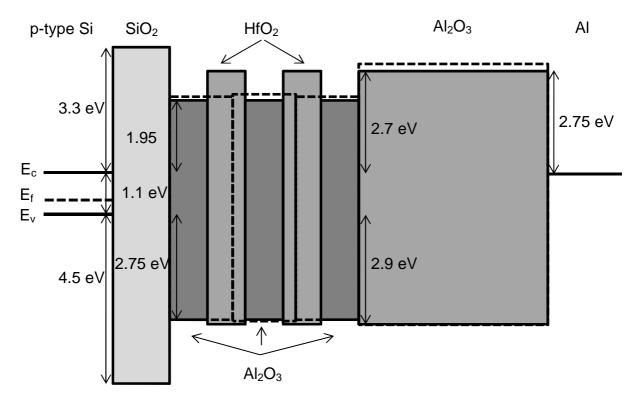

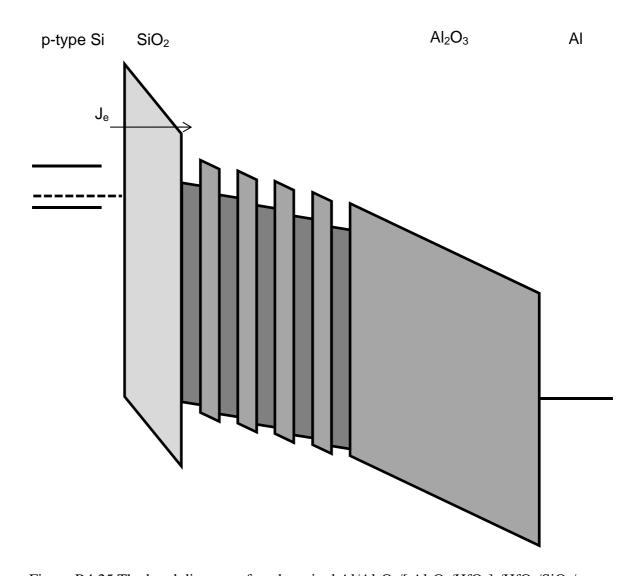

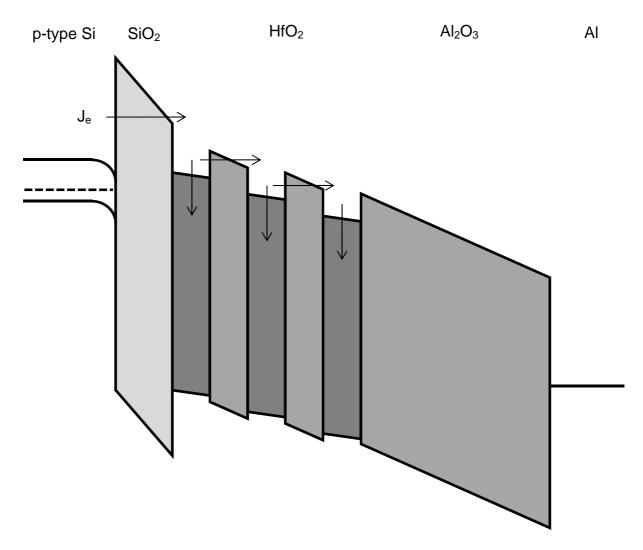

To fulfil the requirements of the next generation of non-volatile memory devices, which are low programming voltage, low leakage current, and good retention characteristics for over 10 years, high-κ Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> nanolaminates as charge trapping layer in metal gate electrode – Al<sub>2</sub>O<sub>3</sub> – high – SiO<sub>2</sub> – p-type Si substrate (MAHOS) structure is proposed. By utilizing nanolaminates as charge trapping layer, heterojunction formed between two dissimilar semiconductors is created to get unique properties provided by the difference in energy gap, which can be seen in Figure 1.7. HfO<sub>2</sub> is believed to have deep trap level and has smaller conduction and valence band offset with respect to Si substrate, so the charges can be trapped with lower programming voltage and faster erase speed can be achieved. Al<sub>2</sub>O<sub>3</sub> is used to modulate charge trapping distribution. Since it has wider bandgap and band offset with respect to Si than those of HfO<sub>2</sub>, it is hoped that the retention properties can be improved.

Before explaining the charge trapping characteristics in the device structure, the evaluation of the microstructure and chemical state is also proposed to answer the device fabrication issue. In addition, the measurement of energy band parameters will be conducted to to analyze the charge transport mechanisms across the semiconductor structure.

Figure 1.7 Energy-band diagrams for (a) heterostructure with multiple quantum wells and (b) heterostructure superlattice<sup>[22]</sup>.

By considering the background discussed in the previous section which includes the motivation, current status, and challenges, the main goal of this research is to investigate the charge trapping characteristics in the MAHOS capacitor structure with high- $\kappa$  dielectric nanolaminates and high- $\kappa$  dielectrics as charge trapping layer for non-volatile memory application beyond 25 nm technology.

To achieve the main goal, this research is divided into four works based on their specific objectives mentioned as follow:

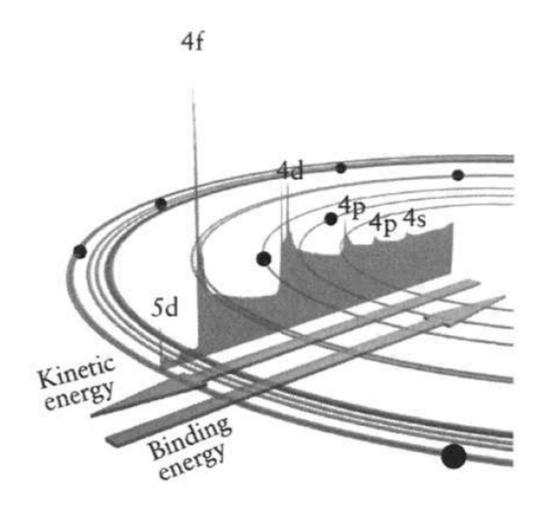

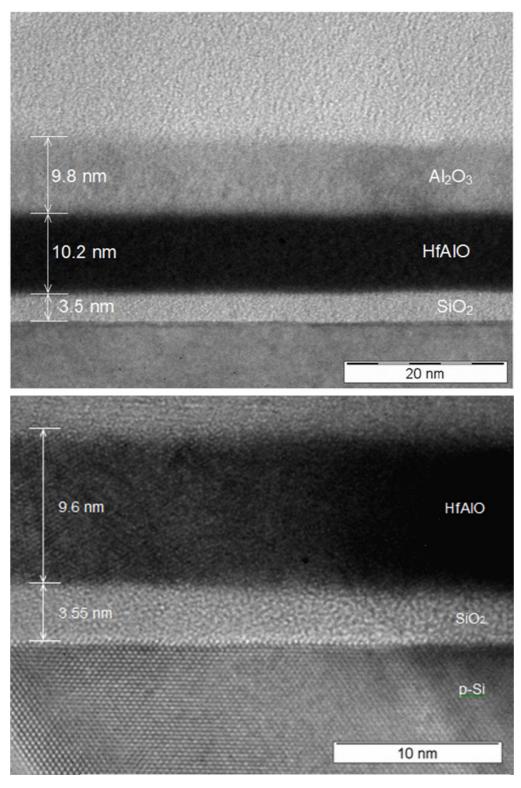

- 1. To fabricate and to evaluate the MAHOS capacitor structures by high resolution transmission electron microscopy (HR-TEM), x-ray photoelectron spectroscopy (XPS), and auger electron spectroscopy (AES). (Chapter 2)

- 2. To investigate the energy band parameters, including bandgap, valence band offset, and conduction band offset, of materials in the MAHOS capacitor structures by reflection electron energy-loss spectroscopy (REELS) and x-ray photoelectron spectroscopy (XPS). (Chapter 3)

- To investigate the memory fuction of the as-deposited MAHOS capacitor structures by inductance – capacitance – resistance (LCR) meter and semiconductor analyzer system.

(Chapter 4)

- To investigate the memory fuction of the annealed MAHOS capacitor structures by inductance – capacitance – resistance (LCR) meter and semiconductor analyzer system.

(Chapter 5)

#### 1.5 Thesis Organization

This Dissertation consists of 6 chapters, including:

Chapter 1: "Introduction". The basic of non-volatile memory is described and the role of high-κ dielectric materials for non-volatile memory application is reviewed. The background

of this research which includes the motivation, current status of the research, and some challenges is described. The research purpose which would be the centerpiece of our work is stated.

Chapter 2: "Device Fabrication and Structural Properties Characterizations". The fabrication of MAHOS capacitor structures for non-volatile memory application, which involves Radio Corporation America (RCA) cleaning, rapid thermal oxidation (RTO), atomic layer deposition (ALD), rapid thermal annealing (RTA), and thermal evaporation, is explained. The microstructures of the MAHOS capacitor structures, which also include the interface and roughness, is evaluated by high-resolution transmission electron microscope (HRTEM). The chemical states and the binding energy of materials in the structure are evaluated by x-ray photoemission spectroscopy (XPS) and auger electron spectroscopy (AES).

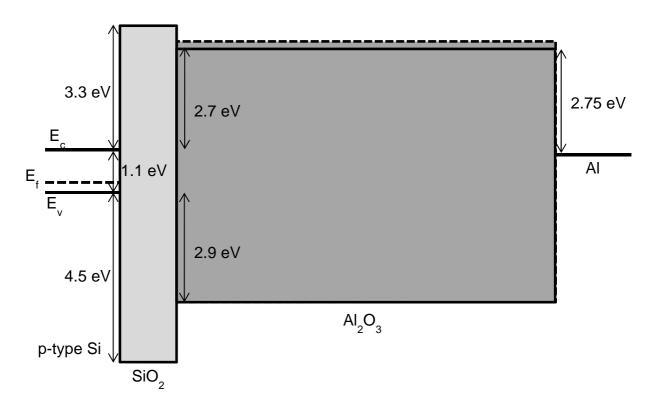

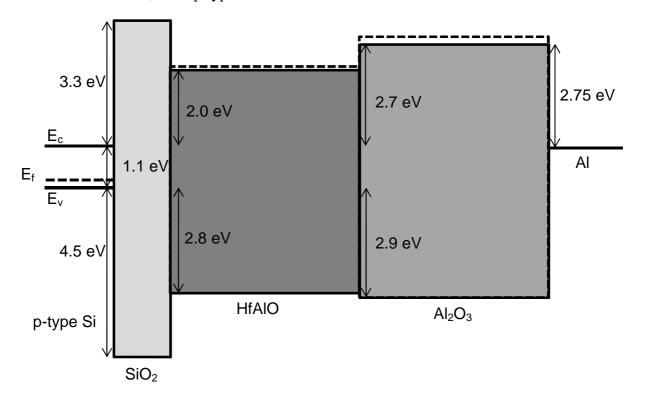

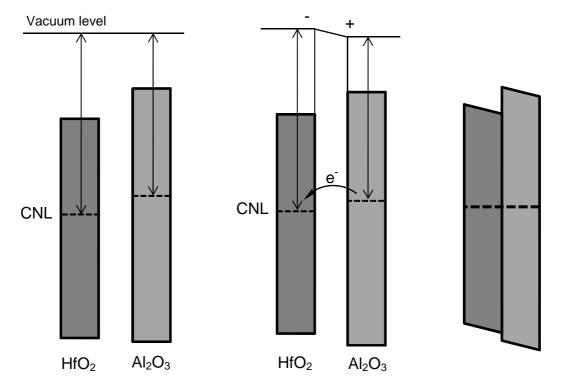

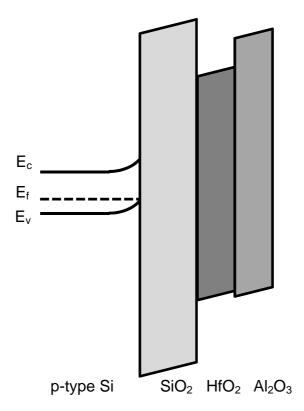

Chapter 3: "Energy Band Alignment of the MAHOS Memory Capacitors". The energy band parameters, such as band gap, valence band offset (VBO) and conduction band offset (CBO) are obtained from experimental results. The energy band gap of materials is observed by reflection energy electron loss spectroscopy (REELS) and the VBO and CBO are obtained from the x-ray photoelectron spectroscopy (XPS) spectra. The energy band alignment of each MAHOS structure is drawn. The effect of the dipole formation on the band structure at semiconductor/semiconductor interfaces is also explained.

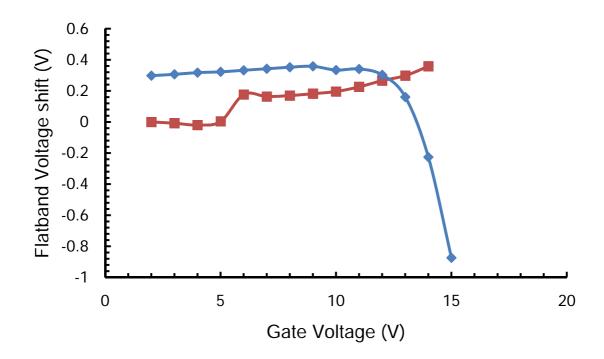

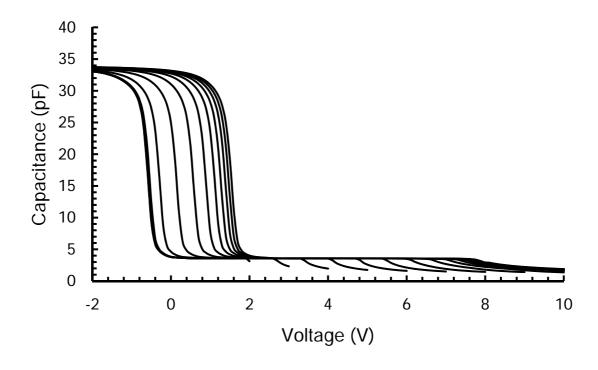

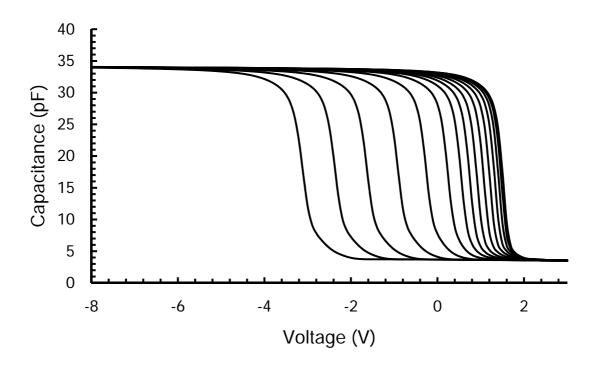

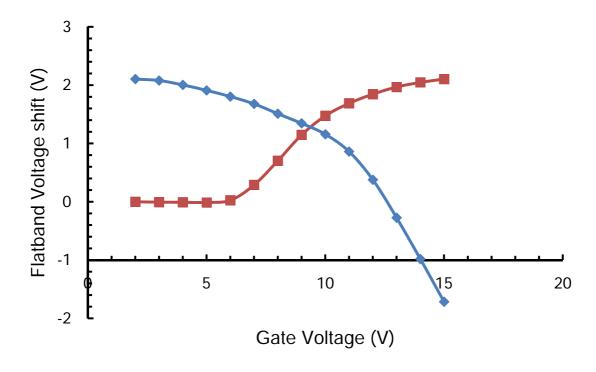

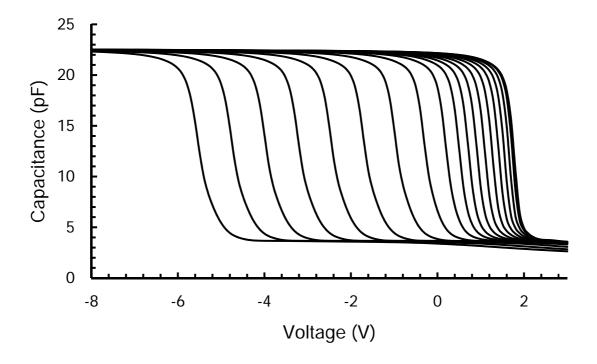

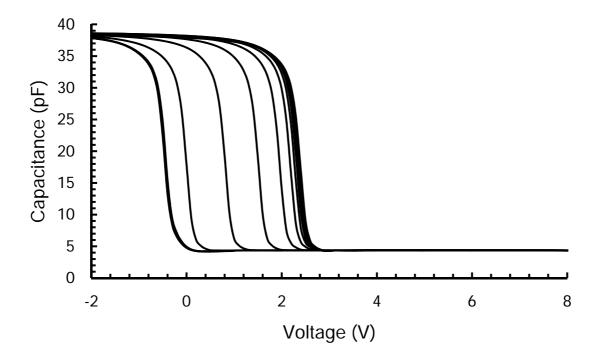

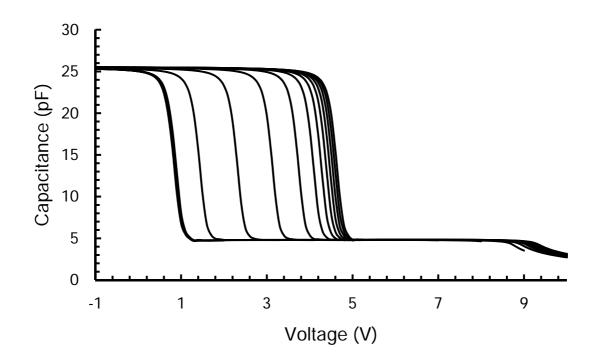

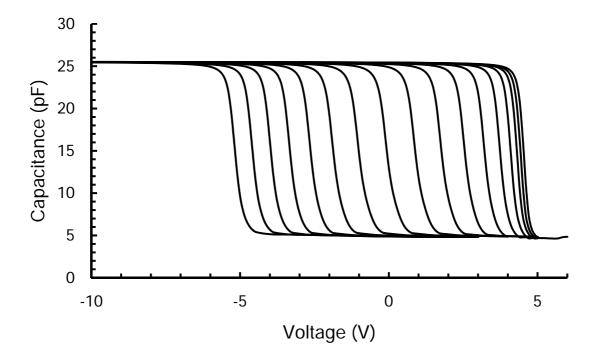

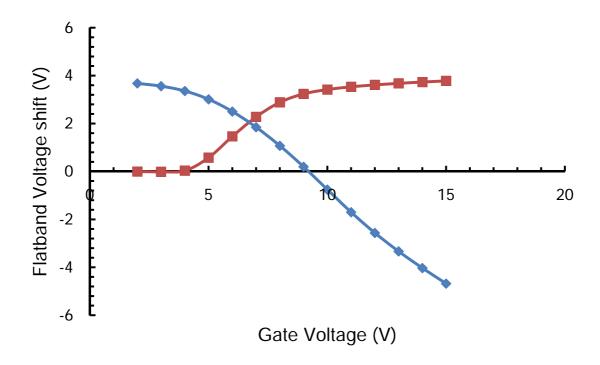

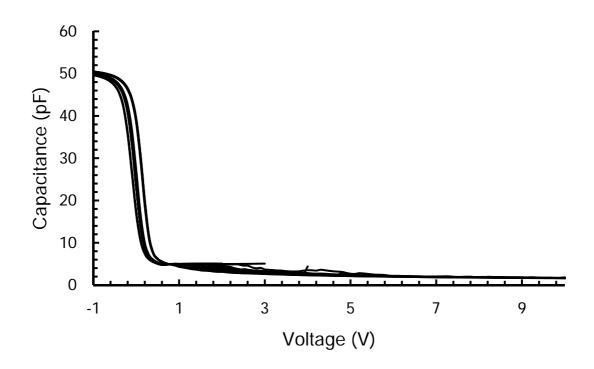

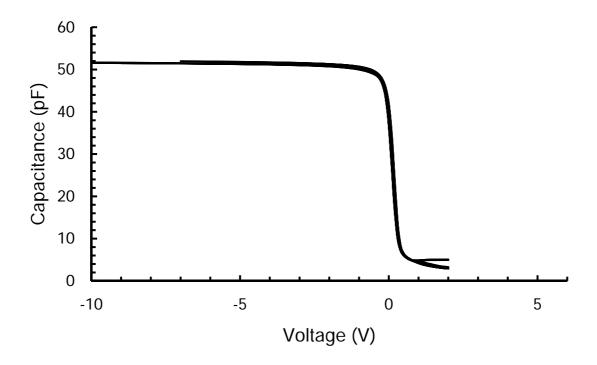

Chapter 4: "Charge Trapping in Capacitor Structures with As-deposited High-κ Dielectric Materials as Charge Trapping Layers". The charge trapping properties of as-deposited MAHOS capacitor structures are explained by evaluating, leakage current density – electric field characteristics, high frequency (1 MHz) capacitance – voltage (C – V) characteristics. The neutral flatband voltage is analyzed. The charge transport mechanism is explained by considering energy band diagram of the structures.

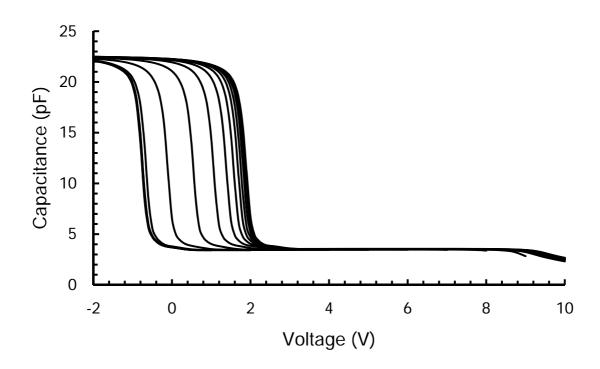

Chapter 5: "Charge Trapping in Capacitor Structures with Annealed High-□ Dielectric

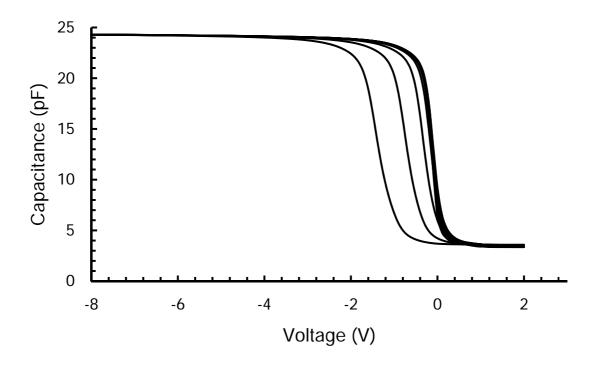

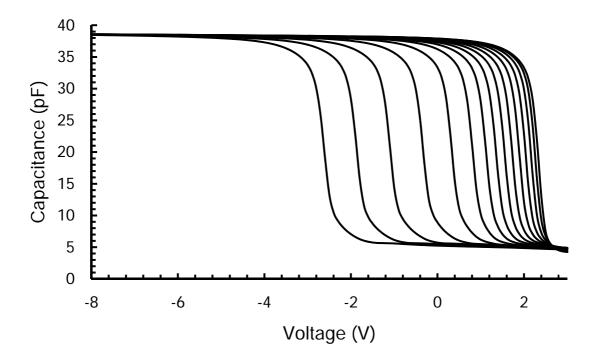

Materials as Charge Trapping Layers". The charge trapping characteristics of annealled MAHOS capacitor structures are investigated from high frequency (1 MHz) capacitance – voltage (C – V) measurement results. The charge transport mechanism is analyzed from leakage current density measurement. The energy band diagram of the capacitor structures is also considered in explaining the charge injection. The difference in charge trapping characteristics between as-deposited MAHOS structures and annealed MAHOS structures is discussed.

Chapter 6: "Conclusions dan Recommendation for Future Works". This chapter concludes the whole research works and states some recommendation for future works.

#### References

- [1] Brewer, J.; Gill, M. Nonvolatile Memory Technologies with Emphasis on Flash: A Comprehensive Guide to Understanding and Using NVSM Devices; IEEE Press: Piscataway, NJ, USA, 2008.

- [2] D.Khang and S.M.Sze. A floating gate and its application to memory devices. Bell Sys.Tech.j., vol.46, p.1288, 1967.

- [3] John Robertson. Band offsets of wide-band-gap oxides and implications for future electronic devices. J. Vac. Sci. Technol. B 18, 1785 (2000).

- [4] Lee, C.H.; Hur, S.H.; Shin, Y.C.; Choi, J.H.; Park, D.G.; Kim, K. Charge trapping device structure of SiO<sub>2</sub>/SiN/high-k dielectric Al<sub>2</sub>O<sub>3</sub> for high-density flash memory. Appl. Phys. Lett. 2005, 86.

- [5] Pu, J.; Chan, D.S.; Kim, S.-J.; Cho, B.J. Aluminum-doped gadolinium oxides as blocking layer for improved charge retention in charge-trap-type nonvolatile memory devices. IEEE Trans. Electron Devices 2009, 56, 2739–2745.

- [6] He, W.; Pu, J.; Chan, D.S.; Cho, B.J. Performance improvement in charge-trap flash memory using lanthanum-based high-k blocking oxide. IEEE Trans. Electron Devices 2009, 56, 2746–2751.

- [7] Huang, X.D.; Liu, L.; Xu, J.P.; Lai, P.T. Improved performance of yttrium-doped Al2O3 as inter-poly dielectric for flash-memory applications. IEEE Trans. Device Mater. Rel. 2011, 13, 490–494.

- [8] Lue, H.-T.; Wang, S.-Y.; Lai, E.-K.; Shih, Y.-H.; Lai, S.-C.; Yang, L.-W.; Chen, K.-C.; Ku, J.; Hsieh, K.-Y.; Liu, R.; *et al.* BE-SONOS: A bandgap engineered SONOS with excellent performance and reliability. In *Proceedings of IEEE International IEDM Technical Digest Electron Devices Meeting*, Washington, DC, USA, 5 December 2005; pp. 547–550.

- [9] Govoreanu, B.; Blomme, P.; Rosmeulen, M.; van Houdt, J.; de Meyer, K. VARIOT: A novel multilayer tunnel barrier concept for low voltage nonvolatile memory devices. *IEEE Electron Device Lett.* 2003, 24, 99–101.

- [10] White, M.H.; Adams, D.A.; Bu, J. On the go with SONOS. *IEEE Circuits Devices Mag.* 2000, 16, 22–31.

- [11] Wu, Y.H.; Chen, L.L.; Wu, J.R.; Wu, M.L.; Lin, C.C.; Chang, C.H. Nonvolatile memory with nitrogen-stabilized cubic-phase ZrO<sub>2</sub> as charge-trapping layer. *IEEE Electron Device Lett.* **2010**, *31*, 1008–1010.

- [12] J. Robertson. High dielectric constant gate oxides for metal oxide Si transistors. Rep.Progress in Physics, vol. 69, pp. 327 390, 2006.

- [13] International Technology Roadmap for Semiconductors: Process Integration, Devices and Structures. **2009**. <a href="http://www.itrs.net/Links/2009ITRS/Home2009.htm">http://www.itrs.net/Links/2009ITRS/Home2009.htm</a>.

- [14] Tan, Y.N.; Chim, W.K.; Choi, W.K.; Joo, M.S.; Byung, J.C. Hafnium aluminum oxide as charge storage and blocking-oxide layers in SONOS type nonvolatile memory for high-speed operation. *IEEE Trans. Electron Devices* **2006**, *53*, 654–662.

- [15] You, H.-W.; Cho, W.-J. Charge trapping properties of the HfO2 layer with various thicknesses for charge trap flash memory applications. Appl. Phys. Lett. 2010, 96, 093506:1–093506:3.

- [16] Yang, H.J.; Cheng, C.F.; Chen, W.B.; Lin, S.H.; Yeh, F.S.; McAlister, S.P.; Chin, A. Comparison of MONOS memory device integrity when using Hf<sub>1-x-y</sub>N<sub>x</sub>O<sub>y</sub> trapping layers with different N compositions. *IEEE Trans. Electron Devices* **2008**, *55*, 1417–1423.

- [17] Wang, X.; Liu, J.; Bai, W.; Kwong, D.-L. A novel MONOS-type nonvolatile memory using high-*k* dielectrics for improved data retention and programming speed. *IEEE Trans. Electron Devices* **2004**, *51*, 597–602.

- [18] Pan, T.-M.; Jung, J.-S.; Chen, F.-H. Metal-oxide-high-k-oxide-silicon memory structure incorporating a Tb<sub>2</sub>O<sub>3</sub> charge trapping layer. *Appl. Phys. Lett.* **2010**, *97*, 012906:1–012906:3.

- [19] Pan, T.-M.; Yeh, W.-W. High-performance high-k Y<sub>2</sub>O<sub>3</sub> SONOS-type flash memory.

\*IEEE Trans. Electron Devices 2008, 55, 2354–2360.

- [20] Huang, X.D.; Lai, P.T.; Liu, L.; Xu, J.P. Nitrided SrTiO<sub>3</sub> as charge-trapping layer for nonvolatile memory applications. *Appl. Phys. Lett.* **2011**, *98*.

- [21] Huang, X.D.; Sin, J.K.O.; Lai, P.T. Improved Charge-Trapping Characteristics of BaTiO<sub>3</sub> by Zr Doping for Nonvolatile Memory Applications. *IEEE Electron Device Lett.* **2013**, *34*, 499–501.

- [22] S. M. Sze and Kwok K. Ng. Physics of Semiconductor Devices, Third Edition. 2007.

John Wiley & Sons, Inc.

#### Chapter 2

#### **Device Fabrication and Structural Properties Characterizations**

In chapter 2, the experimental procedures on the fabrication of the MAHOS capacitor structures will be described. The process flow of the device fabrication, including Radio Corporation America (RCA) cleaning, rapid thermal oxidation (RTO), atomic layer deposition (ALD), rapid thermal annealing (RTA), and thermal evaporation, will be explained. The microstructures and the chemical states of the MAHOS capacitor structures will be evaluated. Structural properties of the devices were characterized by high-resolution transmission electron microscope (HRTEM) and chemical states of the devices are characterized by x-ray photoemission spectroscopy (XPS) and auger electron spectroscopy (AES).

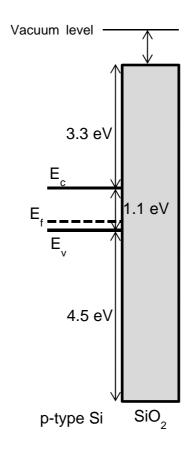

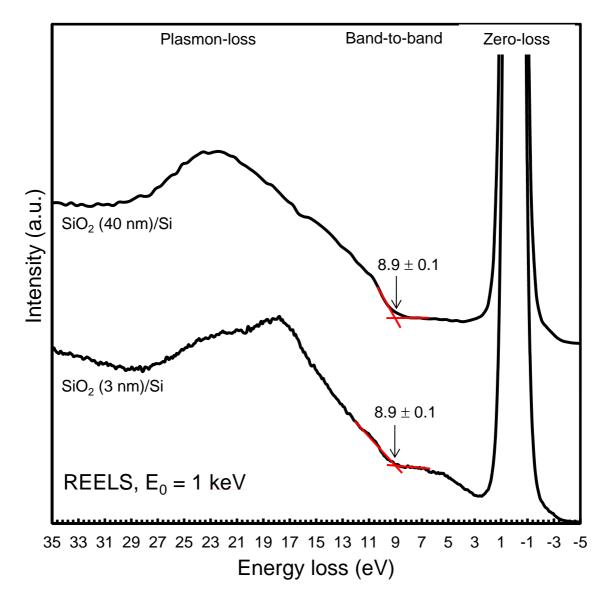

#### 2.1 Design Consideration of MAHOS Capacitor Structures

In this research, the MAHOS capacitor structure was designed as memory structure for non-volatile memory application. For this application, the MAHOS capacitor structures consists of Aluminum as gate electrode,  $Al_2O_3$  as blocking oxide, high- $\kappa$  dielectric materials as charge trapping layer,  $SiO_2$  as tunneling layer, and p-type Silicon substrate. For tunneling oxide and blocking oxide, the energy barriers for electrons ( $\Phi$ e) and holes ( $\Phi$ h) at the metal gate/oxide and Si/oxide interfaces must be sufficiently high to suppress the tunneling effect<sup>[1]</sup>. It is required that the potential barrier at each band is higher than 1 eV to inhibit conduction by the Schottky emission of electrons or holes into the oxide bands<sup>[2]</sup>. SiO<sub>2</sub> was selected as tunneling oxide since it is an excellent insulator with amorphous structure, large band gap of about 8.9 eV with high barriers for both electrons and holes, and very few electronic defects<sup>[3,4]</sup>. SiO<sub>2</sub> is thermally grown on Si substrate with excellent interface with Si. High- $\kappa$

dielectric  $Al_2O_3$  is used as blocking oxide. Using high- $\kappa$  dielectric materials as blocking oxide increases the electric field across the tunnel oxide and charge-storage layers and decreases the electric field across the blocking oxide layer at the same time which results in increase in the program and erase speeds and improve the retention characteristics<sup>[5,6,7]</sup>. For charge trapping layer, high- $\kappa$  dielectric materials were used since they have electronic defects which can trap charges due to possessing ionic bonding and high coordination number<sup>[8,9,10]</sup>. In this research, we will compare the charge trapping characteristics in  $Al_2O_3$  single layer, the mixture of high- $\kappa$  dielectric  $Al_2O_3$  and  $HfO_2$ , and the nanolaminate structure of  $HfO_2/Al_2O_3$ . The nanolaminate structure as charge trapping layer created heterojunction structure with multiple quantum well.

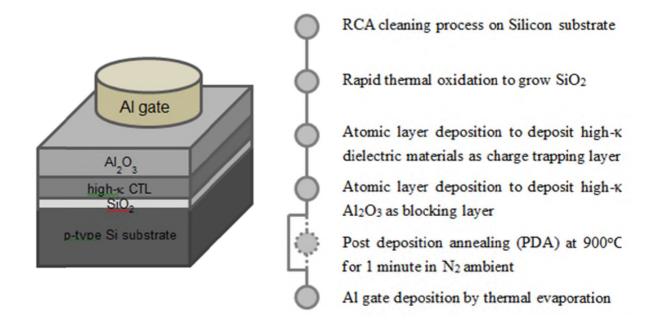

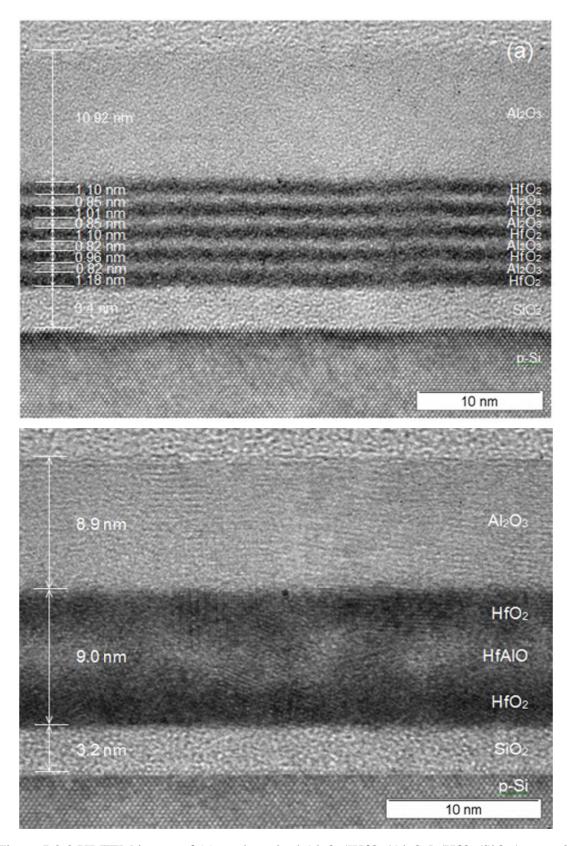

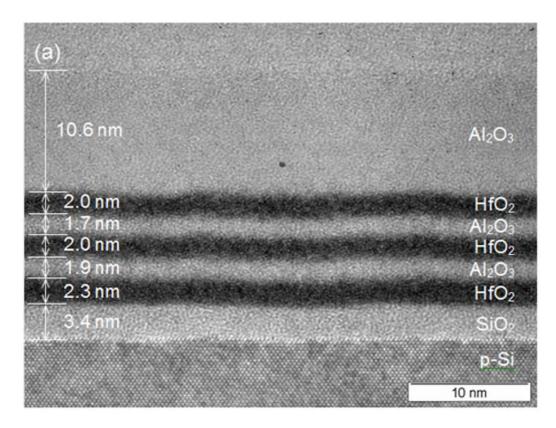

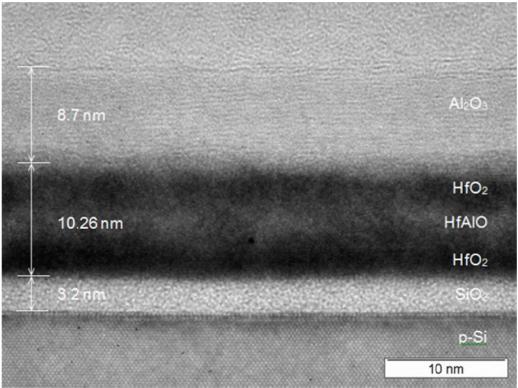

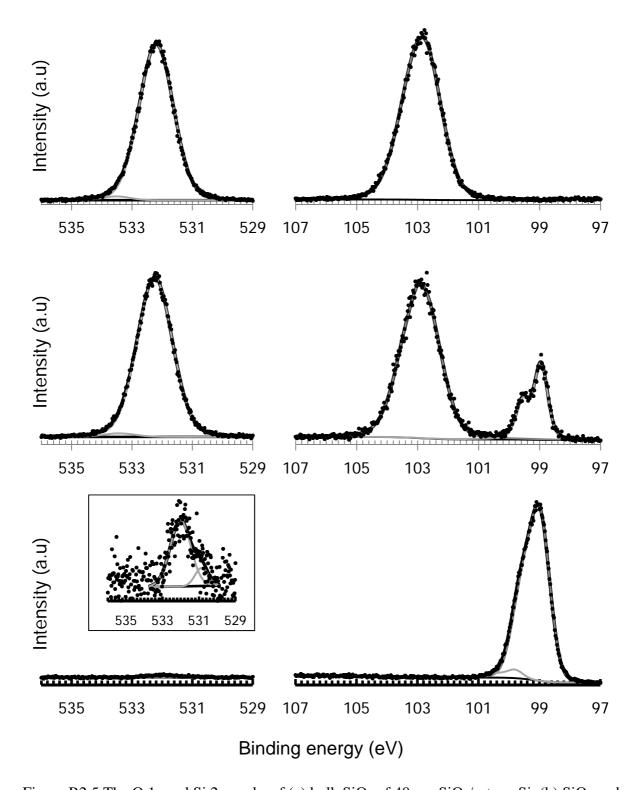

The MAHOS capacitor structures prepared in this works are shown in table 2.1. The structures were prepared by applying certain methods to make sure that the high quality MAHOS structures can be fabricated. The process flow of the MAHOS capacitor fabrication is shown in figure 2.1. In this chapter, the MAHOS structures are evaluated by HRTEM, XPS, and AES.

#### 2.2 Fabrication of MAHOS Capacitor Structures

#### **2.2.1 RCA Cleaning Process**

The Radio Corporation America (RCA) cleaning process is a standard set of silicon wafer cleaning in semiconductor manufacturing which needs to be performed before high temperature processing steps, such as thermal oxidation to grow SiO<sub>2</sub> and structure deposition<sup>[11,12]</sup>. Based on the purposes, there are three steps in RCA cleaning process, including the removal of organic contaminants (organic clean), the removal of thin SiO<sub>2</sub> layer (oxide strip), and the removal of ionic contamination (ionic clean).

Table 2.1 The MAHOS Capacitor Structures

| The MAHOS Structure                                                                                             | RTA | Sample name |

|-----------------------------------------------------------------------------------------------------------------|-----|-------------|

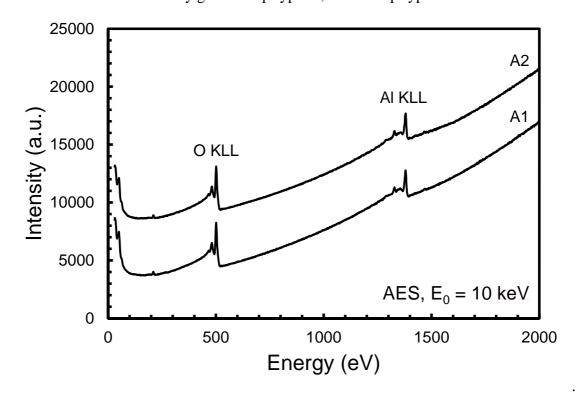

| Al gate/Al <sub>2</sub> O <sub>3</sub> (20 nm)/SiO <sub>2</sub> (3 nm)/p-type Si                                | no  | A1          |

|                                                                                                                 | yes | A2          |

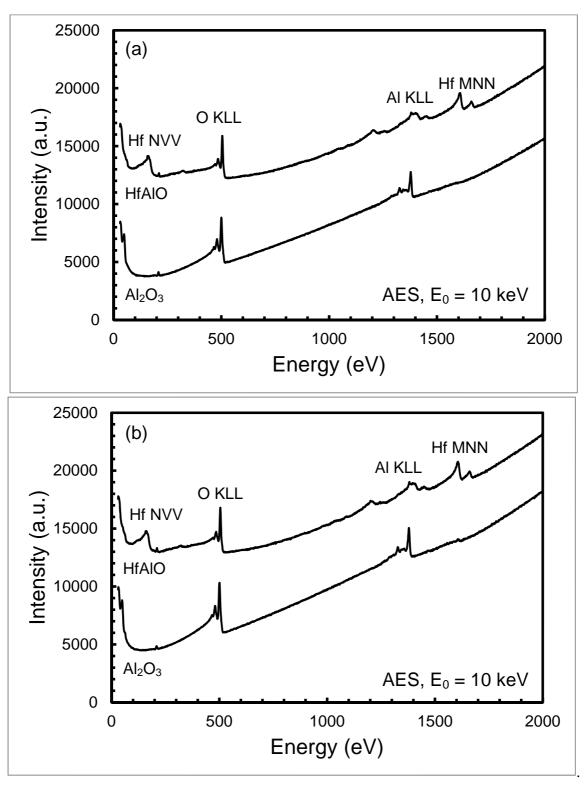

| Al gate/Al <sub>2</sub> O <sub>3</sub> (10 nm)/HfAlO (10 nm)/SiO <sub>2</sub> (3 nm)/p-type                     | no  | HA1         |

| Si                                                                                                              |     |             |

|                                                                                                                 | yes | HA2         |

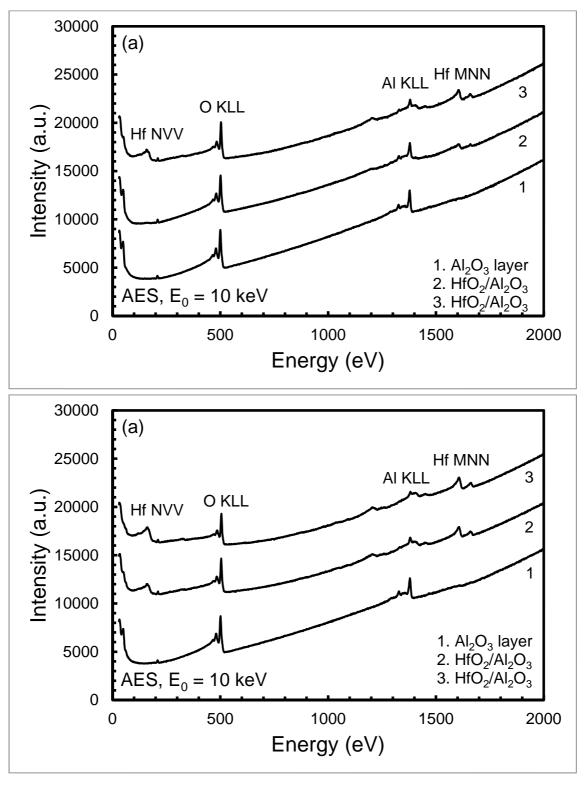

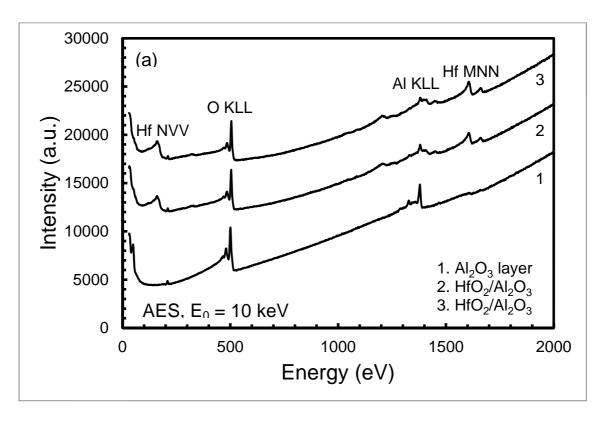

| Al gate/Al <sub>2</sub> O <sub>3</sub> (10 nm)/HfO <sub>2</sub> (2 nm)/                                         | no  | NA1         |

| $[HfO_2(2~nm)/Al_2O_3(2~nm)]_2/SiO_2(3~nm)/p\text{-type Si}$                                                    |     |             |

|                                                                                                                 | yes | NA2         |

| Al gate/Al <sub>2</sub> O <sub>3</sub> (10 nm)/HfO <sub>2</sub> (1 nm)/                                         | no  | NB1         |

| [HfO <sub>2</sub> (1 nm)/Al <sub>2</sub> O <sub>3</sub> (1 nm)] <sub>4</sub> /SiO <sub>2</sub> (3 nm)/p-type Si |     |             |

|                                                                                                                 | yes | NB2         |

Figure 2.1 Process flow of the fabrication of the MAHOS capacitor structure.

For three different purposes, three chemical mixtures, including organic clean mixture, oxide strip mixture, and ionic clean mixture, are prepared. Organic clean mixture has to be made less than 45 minutes prior to being used. The mixture consists of 5 parts of DI water, 1 part of hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>, 30%), and 1 part of ammonium hydroxide (NH<sub>4</sub>OH, 28%). The solutions are poured into the beaker and stirred with clean teflon rod. The beaker is placed into the temperature-controlled water bath and the hotplate is adjusted to maintain the solution temperature at 50°C. Oxide strip mixture consists of 30 parts of DI water and 1 part of hydrofluoric acid (HF, 49%). The solutions are poured into propylene beaker. Ionic clean mixture consists of 6 parts of DI water, 1 part of hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>, 30%), and 1 part of hydrochloric acid (HCl, 37%). The solutions are poured into the beaker and the beaker is placed into the temperature-controlled water bath.

To clean the silicon wafer, the wafer is placed in teflon basket. Then, it is submerged in the organic clean solution for 10 minutes and heated to 50°C. The basket with silicon wafer is removed from the bath and rinsed in the DI water for 1 minute. Then, the basket with wafer is submerged in the oxide strip solution for 15 seconds. After that, it is removed from the bath and rinsed in the DI water for 1 minute. Last, the basket with wafer is submerged in the ionic clean solution for 10 minutes and heated to 50°C. The basket is removed from the bath and rinsed wafer in the DI water for 1 minute. Then, the basket is removed from the DI water and the silicon wafer is blown dry with nitrogen.

In our work, p-type silicon (100) wafers with a resistivity of  $15 - 25 \Omega$ .cm were used. RCA cleaning process was done on all Si substrates prior to thin film deposition.

## 2.2.2 Rapid Thermal Processing (RTP)

In this research, rapid thermal processing (RTP) was applied to grow high quality tunneling oxide,  $SiO_2$ , by rapid thermal oxidation (RTO) in  $O_2$  and  $N_2$  ambient and to anneal

the capacitor structures by rapid thermal annealing in  $N_2$  ambient before Al gate electrode deposition was done.

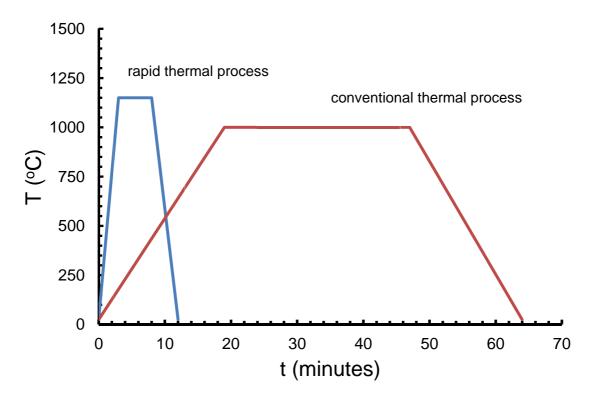

When the SiO<sub>2</sub> is grown on Si substrate by thermal oxidation process, the oxidation process influences the distribution of impurities in the bulk of silicon and at the Si/SiO<sub>2</sub> interface. Since the movement of impurities affects the device size and its electrical properties, it is important to control and minimize the effects of oxidation on the impurity profile. This can be achieved by controlling the oxidation temperature precisely and reducing the thermal budget of the heat cycle required for an oxide film growth<sup>[13,14]</sup>. In this case, the conventional furnace oxidation has a limitation because its inertia to temperature transition will result in a higher thermal budget than that required for oxidation. Decreasing the duration of these transitions can reduce the thermal budget considerably. Rapid thermal processing (RTP) offers a process with smaller thermal budget so it can reduce the effects of oxidation on the impurity profile, as shown in figure 2.2.

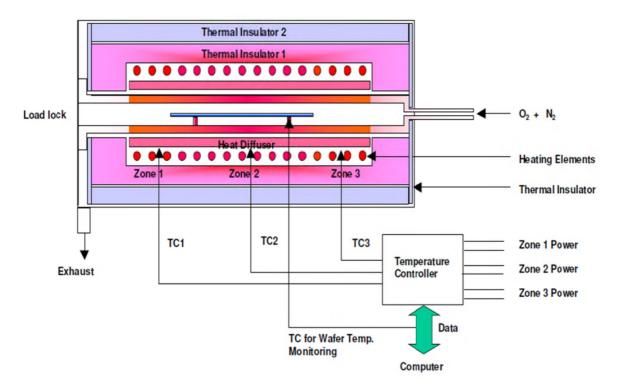

During RTP, the silicon wafer is rapidly heated from room temperature to a high processing temperature ( $T > 800^{\circ}\text{C}$ ) with temperature transition rates range from 10 to  $350^{\circ}\text{C/s}$ , compared with about  $0.1^{\circ}\text{C/s}$  for furnace processing. The wafer is held at high temperature for a short time, varies from 1s to 5 minutes and then cooled down rapidly to a low temperature. By rapid heating and rapid cooling down, RTP reduces the ramp-up and ramp-down durations. Due to its superior process and operational flexibility, RTP is commonly used in semiconductor device manufacturing fabrications and is suitable to grow thin oxide films with thickness less than 40 nm, where a precise temperature control and short oxidation times are important [15,16].

An RTP system is single-wafer furnace, only one wafer is in the chamber and processed. A schematic cross-section of RTP system which is a single wafer rapid thermal

Figure 2.2 The thermal budget reduction in rapid thermal processing.

Figure 2.3 A schematic cross-section of single wafer rapid thermal furnace (SWRTF).

furnace (SWRTF) is shown in Fig. 2.3. The heat source is typically an array of tungsten halogen lamps in an optical system.

After RCA cleaning process, high quality tunneling layer, SiO<sub>2</sub>, was grown on p-type Si substrate by RTO in O<sub>2</sub> ambient with a design thickness of 3 nm. RTA was done on the structure after charge trapping layer and blocking layer deposition in N<sub>2</sub> ambient. The RTP parameters for thermal oxidation and post deposition annealing can be seen in table 2.2.

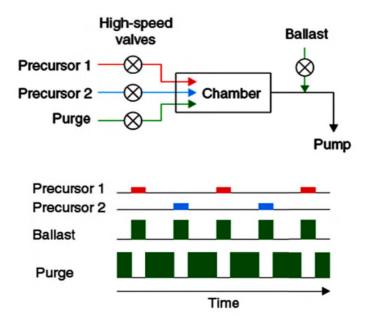

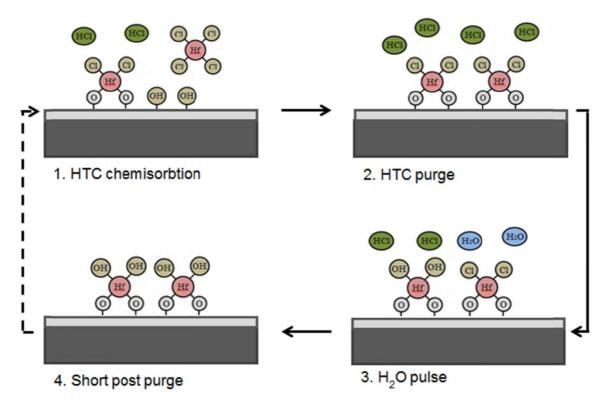

## 2.2.3 Atomic Layer Deposition (ALD)

Atomic layer deposition (ALD) is a chemical gas phase thin film deposition method in which thin film is grown through sequential saturative surface reactions that are realized by pulsing the two (or more) precursors into the reactor alternatively, one at a time, separated by purging or evacuation steps<sup>[17]</sup>. The reactions in ALD are saturative which makes the film growth self-limiting that, in turn, gives the method a number of advantages. The self-limiting growth ensures that each cycle deposits the same amount of material on all surfaces independent of the precursor dose received as long as the dose is high enough to saturate the reactions. As a consequence, the ALD method offers excellent large area uniformity and conformality. In addition, film thicknesses are accurately controlled simply by the number of deposition cycles applied. This makes it also straightforward to tailor film composition at an atomic layer level. Preparation of multicomponent and multilayer materials is further facilitated by the fact that process temperature windows are often reasonably wide so that binary processes are easy to combine.

Successful utilization of ALD is dependent on two factors, including proper precursors and fast and efficient reactors. The precursors must be volatile enough to ensure efficient transportation for saturating the surface reactions. The precursors and the surface species formed thereof do not decompose thermally on their own to maintain atomic level accuracy in film thickness control and uniformity. The precursor dosed onto the substrate

should react rapidly with the surface species left from the previous precursor pulse to achieve fast saturation in each reaction step. Another related requirement is that the reactions should be complete to provide high film purity. Precursors should not etch the material formed during the deposition process. The by-products formed in the surface exchange reactions should be unreactive so that they can be easily purged away from the reactor.

In our research, the high-κ trapping layers, including Al<sub>2</sub>O<sub>3</sub>, HfAlO, and (HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>) nanolaminates and Al<sub>2</sub>O<sub>3</sub> blocking layer were deposited on SiO<sub>2</sub>/p-type Si substrate by ALD. The designed thickness of charge trapping layer and blocking layer for each MAHOS structures can be seen in Table 2.2. High-κ Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> were deposited at a substrate temperature of 300°C by using tri-methylaluminium [Al(CH<sub>3</sub>)<sub>3</sub>] and hafnium tetrachloride (HfCl<sub>4</sub>) precursors, respectively. The precursor temperatures were 23°C for Al(CH<sub>3</sub>)<sub>3</sub> and 185°C for HfCl<sub>4</sub>. The H<sub>2</sub>O was used as an oxidant precursor.

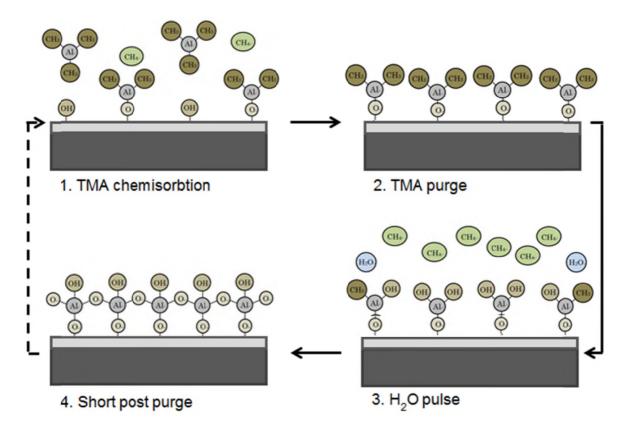

Flow-type reactor was used in this research. The first precursor gas was introduced into the process chamber and produces a monolayer of gas on the wafer surface. A second precursor of gas was then introduced into the chamber reacting with the first precursor to produce a monolayer of film on the wafer surface. There are two fundamental mechanisms during atomic layer deposition, including chemisorption saturation process and sequential surface chemical reaction process.

In air,  $H_2O$  vapor is adsorbed on most surfaces, forming a hydroxyl group. The hydroxyl group form  $Si-O-H_{(s)}$  with  $SiO_2$ . After placing the substrate in the reactor, for  $Al_2O_3$  deposition, trymethyl aluminum,  $Al(CH_3)_3$  (TMA) is pulsed into the reaction chamber. TMA reacts with the adsorbed hydroxyl groups, producing methane as the reaction product.

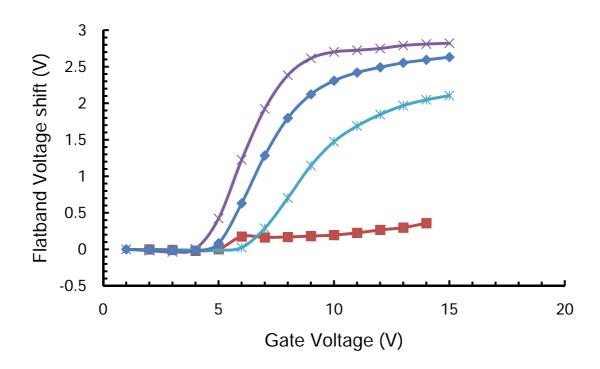

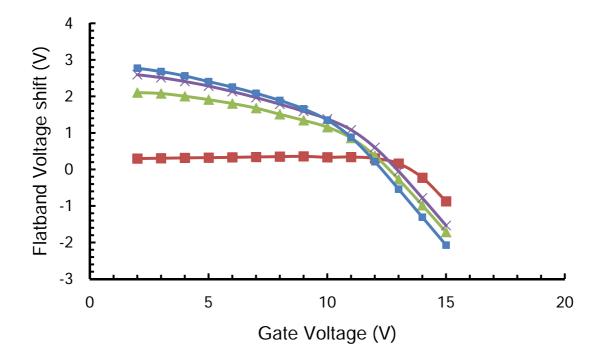

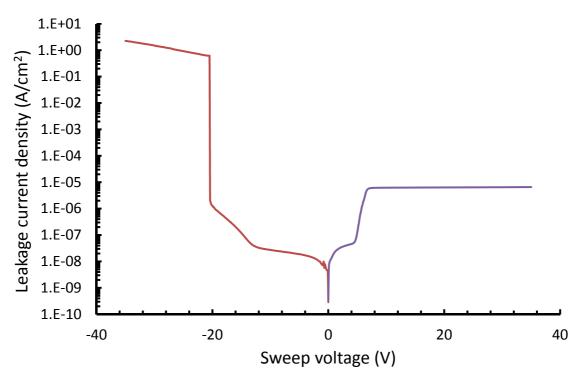

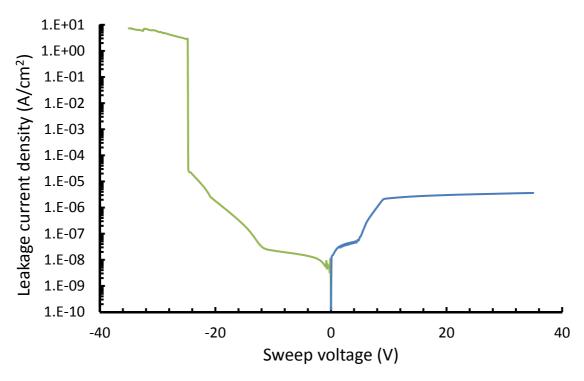

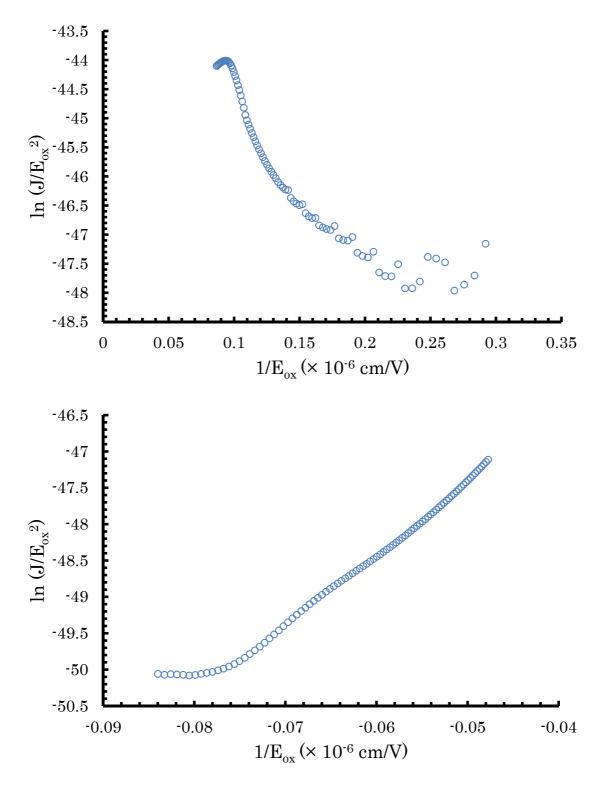

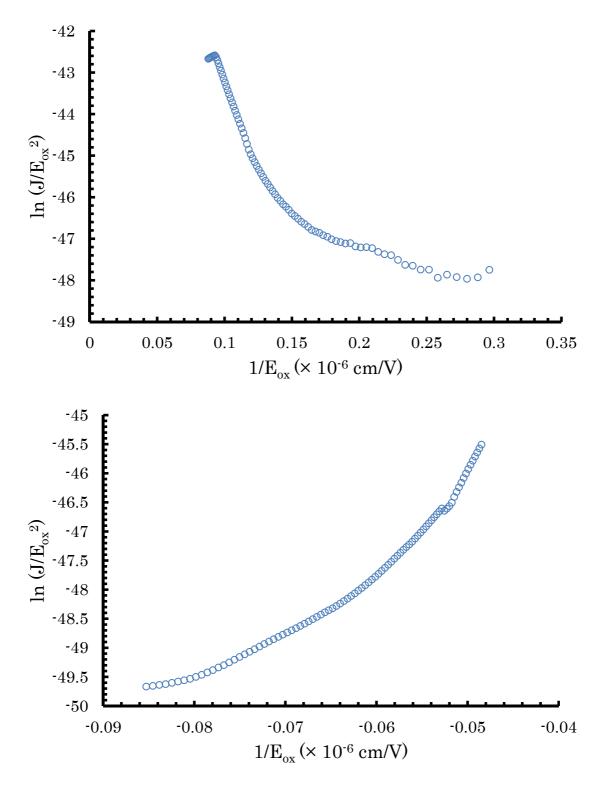

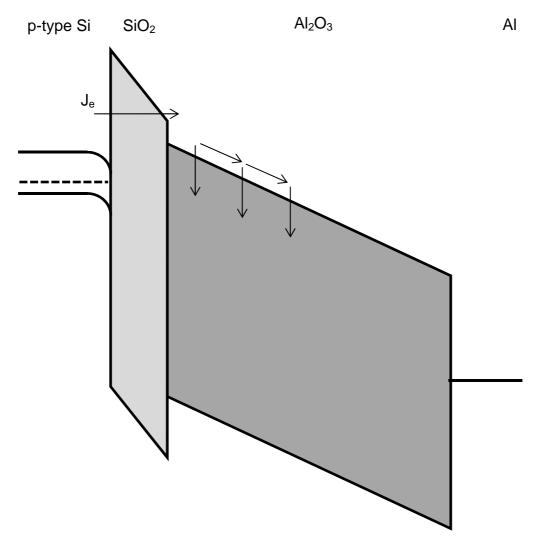

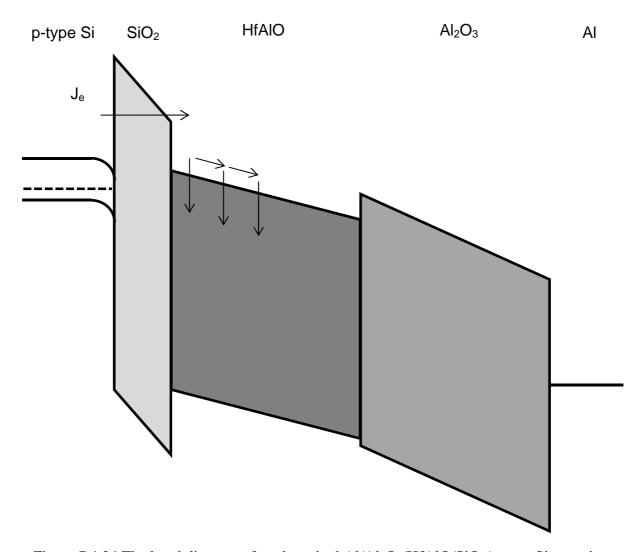

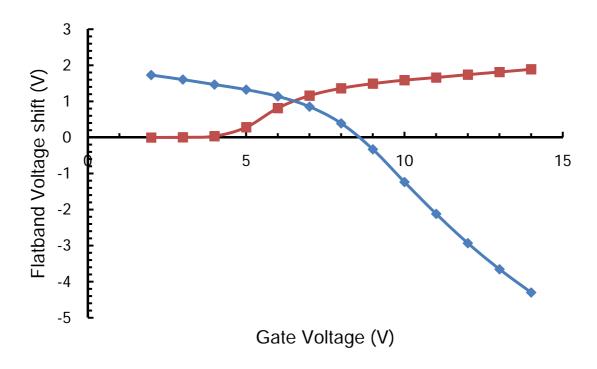

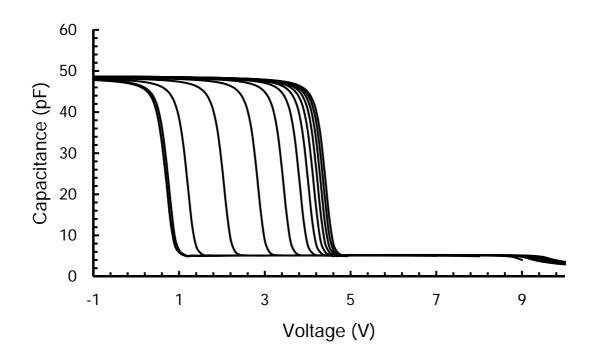

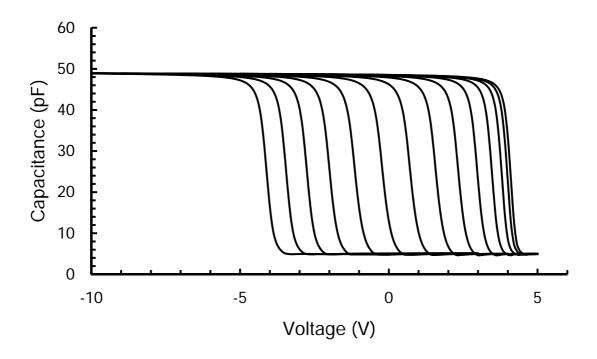

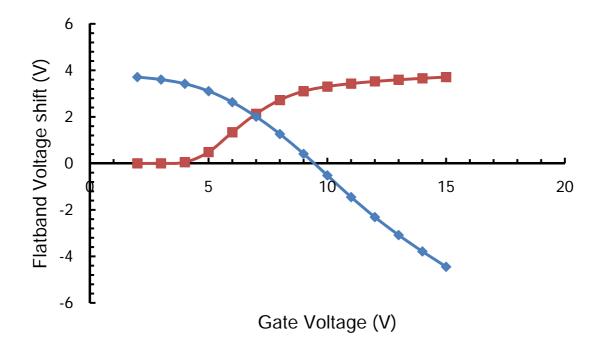

$$Al(CH_3)_{3(g)} + :Si-O-H_{(s)} \rightarrow :Si-O-Al(CH_3)_{2(s)} + CH_{4(g)}$$