# T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

# 論文 / 著書情報 Article / Book Information

| 題目(和文)            | ペトリネットと時相論理を用いたリアクティブ並行システムの開発球<br>境の研究                                                                                                                                                    |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Title(English)    | A programming environment for reactive and concurrent systems using petri nets and temporal logic                                                                                          |  |

| 著者(和文)            |                                                                                                                                                                                            |  |

| Author(English)   | Naoshi Uchihira                                                                                                                                                                            |  |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:乙第3125号,<br>授与年月日:1997年12月31日,<br>学位の種別:論文博士,<br>審査員:佐伯 元司                                                                                            |  |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:乙第3125号,<br>Conferred date:1997/12/31,<br>Degree Type:Thesis doctor,<br>Examiner: |  |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                       |  |

| Type(English)     | Doctoral Thesis                                                                                                                                                                            |  |

# A Programming Environment for Reactive and Concurrent Systems Using Petri Nets and Temporal Logic

ペトリネットと時相論理を用いた リアクティブ並行システムの開発環境の研究

#### Naoshi Uchihira

内平 直志

Graduate School of Information Science and Engineering Tokyo Institute of Technology

東京工業大学 情報理工学研究科 計算工学専攻

A thesis submitted to Tokyo Institute of Technology in partial fulfillment of the requirement for the degree of Doctor of Engineering

December, 1997

## **ABSTRACT**

There has been a rapid trend towards parallel, distributed, and interactive/reactive computing over the past decade. Generally speaking, it is not so easy for ordinary programmers to produce correct and efficient programs for these systems as compared with sequential programming. Therefore, some kind of computer-aided concurrent programming environment is necessary to achieve high productivity and high reliability. The purpose of this thesis is to present theories, methods and tools (programming environments) for reactive and concurrent systems using Petri nets and temporal logic.

Both Petri nets and temporal logic have been investigated as formal specification languages for reactive and concurrent systems. While temporal logic is appropriate for specifying the properties and constraints of programs but inappropriate for specifying the behavioral structures of programs, Petri nets can specify the behavioral structures but not the properties and constraints. In this thesis, the fusion of Petri nets and temporal logic is proposed as a specification language for reactive and concurrent systems. Then, practical and efficient verification and synthesis methods using Petri nets and temporal logic and Petri-net-based design methodology are described. Finally, a programming environment embedding these methods is introduced. This thesis attempts in illustrating a typical programming paradigm and its environment using Petri nets and temporal logic.

The main outcomes of this thesis are as follows.

#### (1) Specification by fusion of Petri nets and temporal logic

The fusion of Petri nets and temporal logic is proposed as a specification language, and its applications to verification and synthesis are considered. The remarkable point is that the proposed methods are for unbounded Petri nets, while former verification and synthesis methods were mainly for bounded (i.e., finite) ones.

#### (2) Compositional verification

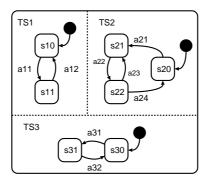

An efficient and practical verification method using transition systems (bounded Petri nets) and temporal logic is proposed. Generally, the computation costs for verification increase exponentially as the scale of the programs increases. To overcome this problem, a reduction technique of the target program has been investigated using bisimulation equivalence. However, bisimulation equivalence cannot deal with "divergence" explicitly. Therefore, a new process equivalence relation ( $\pi\tau\omega$ -bisimulation equivalence) is proposed. A Process Query Language (PQL) which is an extended temporal logic and semantics of which is based on  $\pi\tau\omega$ -bisimulation equivalence is defined. Then, a compositional verification method using PQL is proposed.

#### (3) Compositional program adjustment

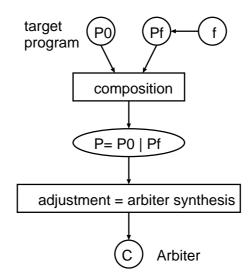

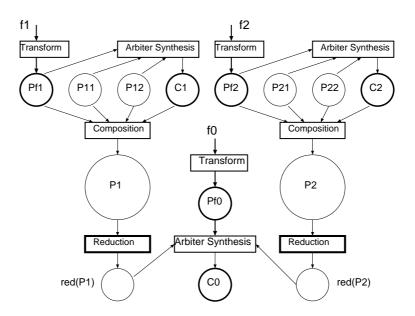

A new synthesis method using transition systems (bounded Petri nets) and temporal logic is proposed. Since conventional program generation from a temporal logic specification is impractical, this thesis proposes a new approach, "program adjustment". In program adjustment, a target program written by programmers which may be functionally correct but may be imperfect in its timing is automatically adjusted (tuned up) to satisfy given temporal logic constraints.

#### (4) Petri-net-based software design methodology

A Petri-net-based software design method is proposed. In this method, a causality matrix is introduced for an earlier design phase when the system structure is obscure and it is difficult to write Petri nets directly. A designer can construct Petri nets systematically from an ambiguous requirement using the causality matrices according to the design method.

#### (5) MENDELS ZONE

A programming environment, MENDELS ZONE, based on the above techniques has been developed. MENDEL net which is a high-level Petri net for reactive and concurrent systems is used as the programming language. The designer constructs a program (MENDEL net) and verifies it using temporal logic. If there are any bugs, the program can be adjusted. Finally, the constructed program is executed on a parallel computer.

## 概要

計算機システムの並列化、分散化、インタラクティブ/リアクティブ化に伴い、並行プログラミングの需要はますます大きくなりつつある。しかしながら、並行プログラムの開発は、逐次プログラムの開発に比べて格段に難しい。さらに、制御システムなどのリアクティブシステムの並行プログラムには高い信頼性が要求されることが多い。このようなソフトウェアの高生産性および高信頼性を確保するためには、ソフトウェア開発の計算機支援は不可欠である。本研究の目的は、ペトリネットと時相論理を用いたリアクティブ・並行システムのソフトウェア開発支援技術を確立することである。

ペトリネットと時相論理はともに並行システムの形式的な仕様記述法として研究されてきた.しかし,時相論理は制約記述には適しているが構造記述には不適であり,逆にペトリネットは構造記述には適しているが制約記述には不適であった.そこで,本研究では時相論理とペトリネットの融合によるリアクティブ・並行システムの仕様記述法を採用する.さらに,ペトリネットと時相論理を用いた実用的な検証・合成手法などの要素技術を開発し,それらを組み込んだプログラムの開発環境の試作およびソフトウェア設計方法論の提示を行なう.本研究により,ペトリネットと時相論理を用いた一つの具体的なソフトウェア開発支援体系を確立することができた.

本研究の主な具体的成果としては,以下の項目がある.

(1) ペトリネットと時相論理の融合による仕様記述法の提案,

時相論理とペトリネットの融合法を示し、ペトリネットが時相論理を満たすか否かを検証する アルゴリズムを示した.従来、有界なペトリネットに対する時相論理による検証法は知られていた が、それを有界でない一般のペトリネットの検証に拡張した.

(2) 積み重ね式検証法の研究

遷移システム (有限ペトリネット) と時相論理を用いた大規模プログラムに対する効率的な検証法を示した. 従来,時相論理のモデル検査法では検証に要するコストの爆発的増大が問題あり,これを回避するために様々な方法が提案され,その1つに検証対象の縮約手法がある. しかし,従来の方式では,「内部遷移による無限ループ」の処理に関して問題があった. 本研究では,その問題点を指摘するとともに,それを是正する新しい様相論理 PQL を提案し, PQL を用いた積み重ね検証法を示した.

(3) プログラム調整法の研究

遷移システム (有限ペトリネット) と時相論理による並行プログラムの新しい合成法を示した. 従来の時相論理からのプログラム合成法は、実用規模のプログラムに適用するには仕様記述能力および計算量の点で非現実的であった. そこで、プログラム全体の自動合成ではなく、人間が作成した不完全なプログラム (遷移システム) を時相論理式で記述された仕様を満たすように部分的に自動修正し、目的のプログラムを生成する「プログラム調整法」を提案した.

(4) ネット指向ソフトウェア設計法の提案

ペトリネットは単なる記述手段であり、あいまいな仕様からペトリネットを導出するためのガイドライン (設計法) が必要である。本研究では、あいまいな仕様をペトリネットに具体化する手段として因果関係マトリックスを導入したリアクティブ・並行システムのソフトウェア設計法を提案した。

(5) プログラミング環境 MENDELS ZONE の開発

上記の要素技術を統合したプログランミング環境を並列計算機上に試作した。ここで、プログラムは高水準ペトリネットである MENDEL ネットで記述する。設計者はネット指向設計法によりプログラム (MENDEL ネット) を作成し、プログラム検証でプログラムを検証し、もし問題点がある場合はプログラム調整によりプログラムを改善する。さらに、生成されたプログラムを実際に並列マシン上で実行できる。

# Acknowledgments

This thesis was supervised by Prof. Motoshi Saeki. I am grateful for his kind and helpful guidance and continuous encouragement which lead me to accomplishing my thesis. Also, this thesis was advised by Prof. Takuya Katayama, Prof. Naoki Yonezaki, Prof. Takehiro Tokuda, Prof. Tomohiro Yoneda, and Prof. Takashi Imaizumi. I am very thankful for their advice.

The greater part of my research has been carried out as a part of MENDELS ZONE project at Toshiba Corporation. My special thanks go to Dr. Shinichi Honiden who was a project leader. At the beginning of the project, he provided me chance to study temporal logic and Petri nets from a software engineering viewpoint. Throughout the project, he has properly supported, guided, and encouraged my research activities.

Hideji Kawata is my research partner who made considerable contribution on the implementation and improvement of our tools, MENDELS ZONE and SAVE/SFC. I wish to express my gratitude for his generous collaboration.

I also have many thanks to the all other members of the MENDELS ZONE project and SAVE/SFC project, especially to Akihiko Ohsuga, Kazunori Matsumoto, Mikako Arami, Toshiaki Kasuya, Toru Uraoka, Akiko Uraoka, and Toshibumi Seki. When PQL was applied to a practical machine control program, the discussion with Satoshi Sumida was very helpful. I would like to thank him.

When joining Toshiba in 1982, I was a novice in software engineering. A lot of senior researchers of our laboratory educate, train, and promote me through the wide range of software engineering activities. These valuable experiences lie at the foundation of this thesis. I would like to thank them, especially Kazuo Matsumura, Hideo Nakamura, Yutaka Ofude, and Shoichi Kojima.

I am also grateful to successive directors and senior managers of the Systems & Software Engineering Laboratory, Seiichi Nishijima, Sadakazu Watanabe, Mutsuhiro Arinobu, Masahiko Arai, Takeshi Kohno, Shinsuke Tamura, Junichiro Tsuda, and Kazuo Mikame. Without their continuous support and encouragement, I could not continue the research about temporal logic and Petri nets during a long term (more than 10 years).

This research has been affected by both Petri net and software engineering communities. Many people gave me fruitful suggestions and critical comments in the related conferences. I would like to tender my thanks to them, especially Prof. Mikio Aoyama and Prof. Kunihiko Hiraishi. The MENDELS ZONE project has been supported by ICOT. I am also indebted to members of ICOT.

Finally, I reserve a special gratitude to my wife, Mari, for mental and physical support. I dedicate this thesis to Mari and our baby girl, Akari.

# Contents

| 1 | Intr           | roduction                                                           | 10            |

|---|----------------|---------------------------------------------------------------------|---------------|

|   | 1              | Motivation                                                          | 10            |

|   | 2              | Background                                                          | 11            |

|   |                | 2.1 Formal Specification for Reactive and Concurrent Systems        | 11            |

|   |                |                                                                     | 14            |

|   |                |                                                                     | 14            |

|   |                | v v                                                                 | 15            |

|   |                |                                                                     | 15            |

|   | 3              | v v                                                                 | 16            |

| 2 | $\mathbf{Pre}$ | eliminaries: Models and Logics for Reactive and Concurrent Systems  | 19            |

|   | 1              |                                                                     | 19            |

|   |                |                                                                     | 19            |

|   |                |                                                                     | 19            |

|   |                | v                                                                   | 20            |

|   |                | <u> </u>                                                            | 21            |

|   |                |                                                                     | $\frac{1}{2}$ |

|   |                |                                                                     | 23            |

|   |                |                                                                     | 24            |

|   |                |                                                                     | 24            |

|   | 2              |                                                                     | 24            |

|   | _              |                                                                     | 24            |

|   |                |                                                                     | 25            |

|   |                | <u>.</u> 0                                                          | 26            |

|   |                |                                                                     | 27            |

|   |                |                                                                     | 28            |

|   |                |                                                                     | 28            |

|   |                |                                                                     | 28            |

|   | 3              |                                                                     | 29            |

|   | 5              | Other Related Approaches                                            | ۷.            |

| 3 |                |                                                                     | 30            |

|   | 1              |                                                                     | 30            |

|   |                |                                                                     | 30            |

|   |                |                                                                     | 31            |

|   |                |                                                                     | 32            |

|   |                |                                                                     | 32            |

|   |                |                                                                     | 32            |

|   |                |                                                                     | 33            |

|   | 2              | •                                                                   | 33            |

|   |                |                                                                     | 35            |

|   |                | •                                                                   | 35            |

|   |                | 1 9                                                                 | 36            |

|   | 3              | Programming Environment for RCS Using Petri Nets and Temporal Logic | 36            |

|   | 4              | Currence ner                                                        | 20            |

| 4 | Spe | cification, Verification, and Synthesis Using Petri Nets and Temporal Logic 40 |

|---|-----|--------------------------------------------------------------------------------|

|   | 1   | Petri Nets and Temporal Logic as Specification Language                        |

|   | _   | 1.1 How to Fuse Petri Nets and Temporal Logic                                  |

|   |     | 1.2 Example of Specification                                                   |

|   |     | 1.3 Theoretical Results                                                        |

|   | 2   | Concurrent Program Verification                                                |

|   | 3   | Concurrent Program Synthesis                                                   |

|   | 9   | 3.1 Composition of Petri Nets                                                  |

|   |     |                                                                                |

|   |     |                                                                                |

|   |     | 0                                                                              |

|   |     | 1 0 1                                                                          |

|   |     | 3.5 Controller Synthesis                                                       |

|   | 4   | 3.6 Agent Synthesis                                                            |

|   | 4   | Related Works                                                                  |

|   | 5   | Summary                                                                        |

| 5 | Con | npositional Verification Using Modal Logic 56                                  |

|   | 1   | Background and Motivation                                                      |

|   | _   | 1.1 Background                                                                 |

|   |     | 1.2 Motivation                                                                 |

|   |     | 1.3 Overview of Main Results                                                   |

|   |     | 1.4 Organization of the Chapter                                                |

|   | 2   | Representation of Concurrent Programs                                          |

|   | -   | 2.1 Equivalence of Transition Systems for Compositional Verification           |

|   |     | 2.2 Composition of Transition Systems                                          |

|   | 3   | Process Query Language                                                         |

|   | 9   | 3.1 SPQL (Strong Process Query Logic)                                          |

|   |     | 3.2 PQL (Process Query Language)                                               |

|   | 4   | Compositional Verification                                                     |

|   | 4   | 4.1 Verification Scope                                                         |

|   |     | 4.1 Verification Scope                                                         |

|   |     |                                                                                |

|   |     |                                                                                |

|   |     |                                                                                |

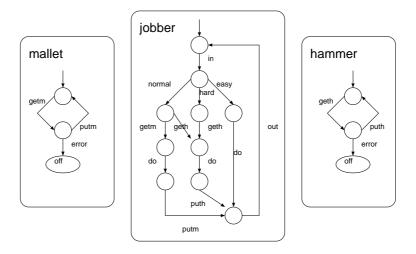

|   |     | 4.4.1 The Jobshop                                                              |

|   | _   |                                                                                |

|   | 5   | Toward Practical Verification                                                  |

|   |     | 5.1 Translation Target Program to Transition Systems                           |

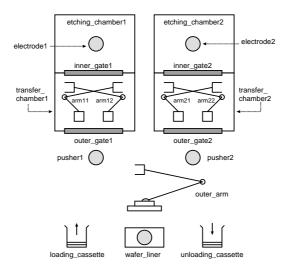

|   |     | 5.2 Chemical Plant Control Software                                            |

|   | _   | 5.3 Verification Tool                                                          |

|   | 6   | Related Works                                                                  |

|   |     | 6.1 Compositional Verification Methods                                         |

|   | _   | 6.2 Comparison with Partial Order Approach                                     |

|   | 7   | Summary                                                                        |

| 6 | Cor | npositional Program Adjustment 90                                              |

| • | 1   | Motivation and Overview                                                        |

|   | -   | 1.1 Motivation                                                                 |

|   |     | 1.2 Overview of Main Results                                                   |

|   |     | 1.3 Organization of the Chapter                                                |

|   | 2   | Finite State Processes                                                         |

|   | _   | 2.1 Equivalence of Finite State Processes                                      |

|   |     | 2.1 Equivalence of Finite State Processes                                      |

|   | 3   | 1                                                                              |

|   | J   | O v                                                                            |

|   |     | 1 0                                                                            |

|   |     | <b>U</b>                                                                       |

|   | 4   | 3.3 Compositional Adjustment                                                   |

|   | 4   | Example and Experimental Result                                                |

|   | 5<br>6<br>7 | $\operatorname{Relate}$ | Example: The Machine Control Program10Experimental Result10am Adjustment in Standard Programming Languages10ed Works10tary10 | )0<br>)4<br>)5 |

|---|-------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------|

| 7 | ME          | NDEL                    | Net: High-Level Petri Net for Reactive and Concurrent Systems 10                                                             | 7              |

|   | 1           |                         | uction                                                                                                                       |                |

|   | 2           |                         | Nets as Programming Language                                                                                                 |                |

|   |             | 2.1                     | Programming Language for Reactive and Concurrent Systems                                                                     |                |

|   |             | 2.2                     | Extension of Petri Nets as Programming Language                                                                              |                |

|   |             | 2.3                     | Petri-Net-Based Programming Languages                                                                                        |                |

|   |             | 2.4                     | High-Level Petri Net as Programming Language                                                                                 |                |

|   | 3           | MENI                    | DEL Net                                                                                                                      |                |

|   |             | 3.1                     | Place                                                                                                                        |                |

|   |             | 3.2                     | Transition                                                                                                                   |                |

|   |             | 3.3                     | I/O Interface                                                                                                                |                |

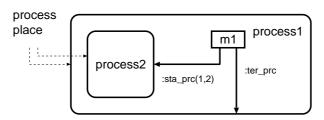

|   |             | 3.4                     | Process-Oriented Hierarchy                                                                                                   |                |

|   |             |                         | 3.4.1 Overview                                                                                                               |                |

|   |             |                         | 3.4.2 Graphical Representation                                                                                               |                |

|   |             |                         | 3.4.3 Textual Representation                                                                                                 |                |

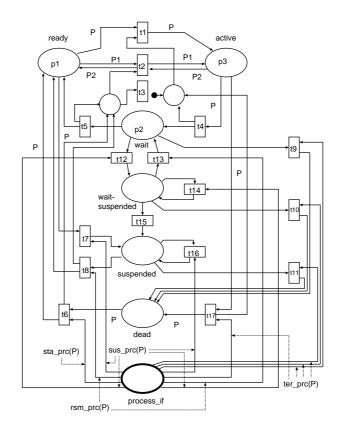

|   |             | 3.5                     | Process Scheduling Mechanism                                                                                                 |                |

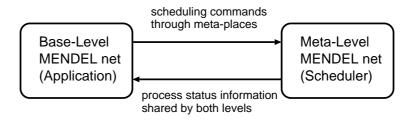

|   |             | 5.5                     | 3.5.1 Base-Level MENDEL Net                                                                                                  |                |

|   |             |                         | 3.5.2 Meta-Level MENDEL Net                                                                                                  |                |

|   |             | 3.6                     | Timer                                                                                                                        |                |

|   |             | 3.7                     | Macro Notations                                                                                                              |                |

|   | 4           |                         | e Example                                                                                                                    |                |

|   | 5           |                         | ed Works: Petri Nets and Hierarchy                                                                                           |                |

|   | 6           |                         | ary                                                                                                                          |                |

|   | Ü           | ~ 411111                |                                                                                                                              |                |

| 8 | Pet         | ri-Net-                 | Oriented Design Methodology 12                                                                                               | 7              |

|   | 1           | Petri-l                 | Net-Oriented Design Methodology                                                                                              | 7              |

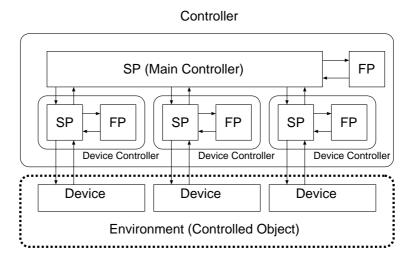

|   | 2           | Softwa                  | are Architecture of Control Systems                                                                                          | 8              |

|   | 3           | Causa                   | lity Matrix                                                                                                                  | 8              |

|   | 4           |                         | n Method                                                                                                                     |                |

|   | 5           | Exam                    | ple: Lift Control System                                                                                                     | 3              |

|   |             | 5.1                     | Problem                                                                                                                      | 3              |

|   |             | 5.2                     | Observation of actual design process                                                                                         | 3              |

|   |             | 5.3                     | Qualitative Evaluation                                                                                                       | 39             |

|   | 6           | Relate                  | ed Works                                                                                                                     | 9              |

|   | 7           | Summ                    | ary                                                                                                                          | lO             |

| _ |             |                         |                                                                                                                              | _              |

| 9 |             |                         | S ZONE: Petri-Net-Based Programming Environment  14                                                                          |                |

|   | 1           |                         | luction                                                                                                                      |                |

|   | 2           | _                       | rements for Programming Environment                                                                                          |                |

|   | 3           |                         | DELS ZONE                                                                                                                    |                |

|   |             | 3.1                     | Graphical MENDEL Net Editor                                                                                                  |                |

|   |             | 3.2                     | Causality Matrix Editor                                                                                                      |                |

|   |             | 3.3                     | Software Reuse Support Tool                                                                                                  |                |

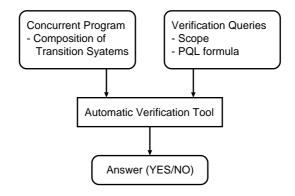

|   |             | 3.4                     | Verification and Adjustment Tool                                                                                             |                |

|   |             | 3.5                     | Program Execution on Multi-PSI                                                                                               |                |

|   | 4           |                         | are Development Process in MENDELS ZONE                                                                                      |                |

|   | 5           |                         | ple: Power Plant Control System                                                                                              |                |

|   | 6           |                         | ed Works                                                                                                                     |                |

|   |             | 6.1                     | Comparison with STATEMATE                                                                                                    |                |

|   |             | 6.2                     | Comparison with Other Petri Net Tools                                                                                        |                |

|   | 7           | Summ                    | ary                                                                                                                          | ,4             |

| 10 Con | nclusion               | 155 |

|--------|------------------------|-----|

| 1      | Review of Developments | 155 |

| 2      | Current Status         | 155 |

| 3      | Future Works           | 155 |

# List of Practical Examples of Reactive and Concurrent Systems

The following middle-scale examples are relatively practical and used to show that the techniques proposed in this thesis can be applicable to actual systems.

```

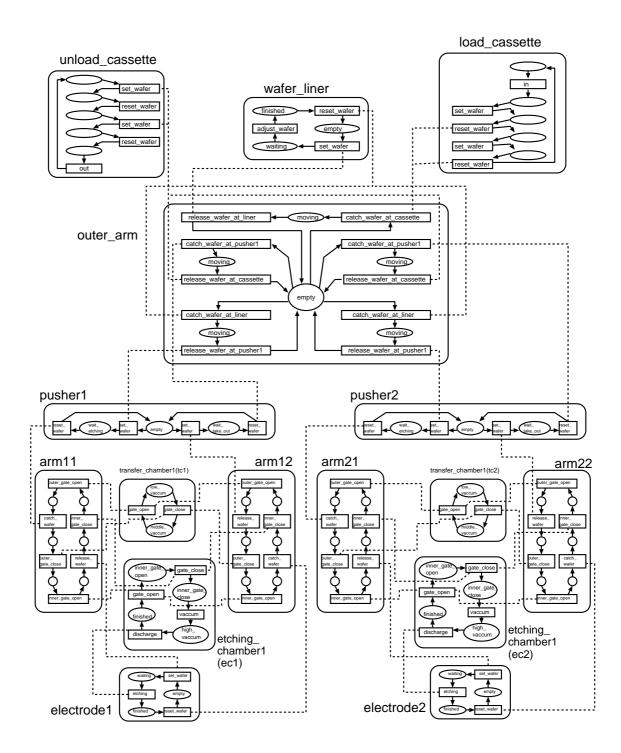

Manufacturing machine control system

compositional verification (Chapter 5)

transition system + temporal logic (PQL)

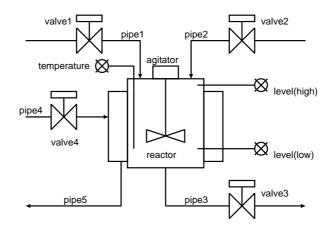

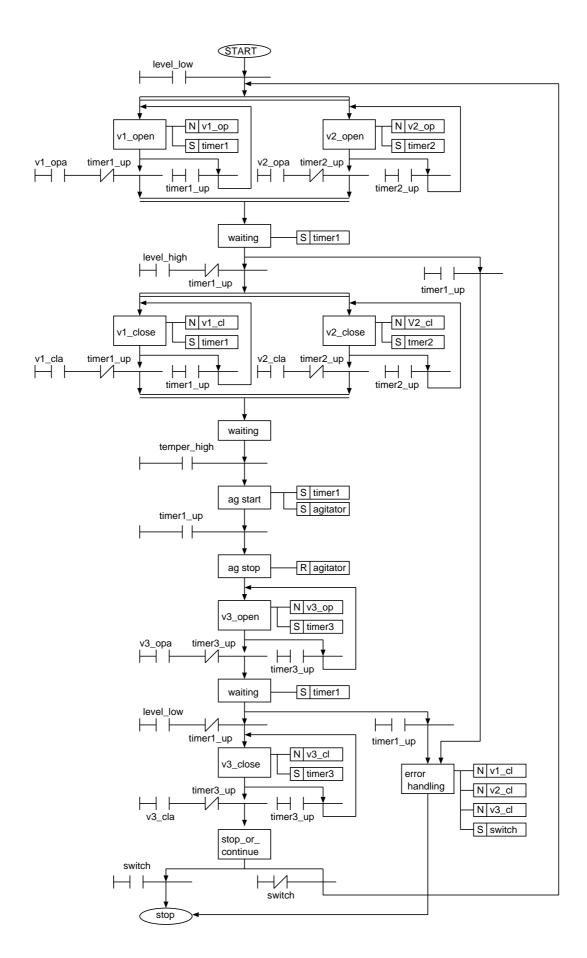

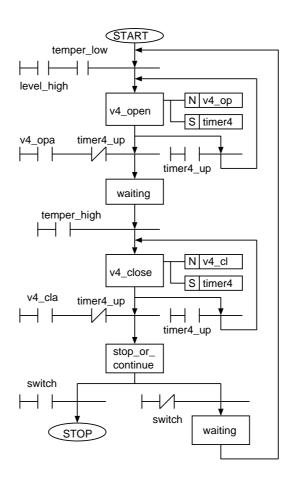

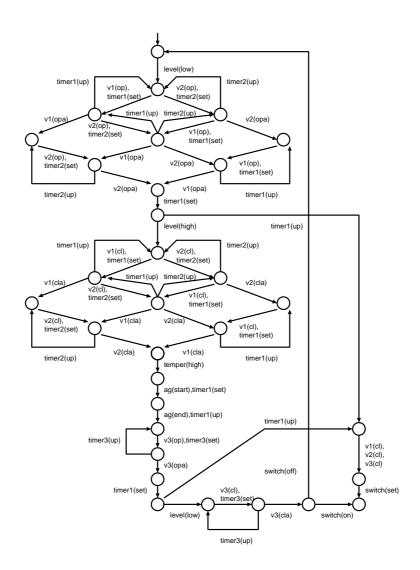

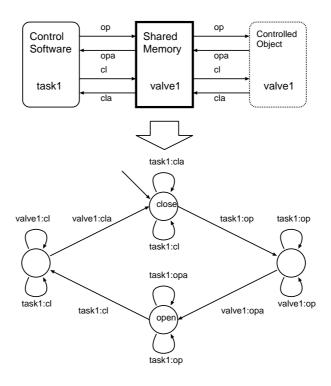

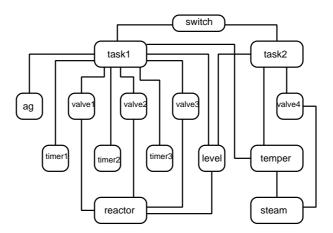

Chemical plant control system

compositional verification (Chapter 5)

Petri net (SFC) + temporal logic (PQL)

Lift control system

Petri-net-oriented design methodology (Chapter 8)

Petri net (MENDEL net) + temporal logic (PLTL)

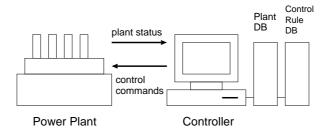

Power plant control system

MENDELS ZONE (Chapter 9)

Petri net (MENDEL net) + temporal logic (PLTL)

```

# Glossary

| Notation                             | Meaning                                                             |

|--------------------------------------|---------------------------------------------------------------------|

| $\delta$                             | transition function (transition system)                             |

| $\perp$                              | disabled                                                            |

| ρ                                    | transition function (automaton)                                     |

| au                                   | unobservable internal action                                        |

| heta                                 | action/transition sequence (run)                                    |

| $\eta$                               | label sequence (word)                                               |

| $\stackrel{\gamma}{\Delta}$          | deadlock                                                            |

| arepsilon                            | empty sequence                                                      |

| $X^*$                                | a set of finite sequences over $X$                                  |

| $X^{\omega}$                         | a set of infinite sequences over $X$                                |

| $\chi^{\infty}$                      | $X^{\infty} = X^* \cup X^{\omega}$                                  |

| $\frac{X^{\infty}}{\overline{X}}$    | a complementary set of $X$                                          |

| $X_1 \setminus X_2$                  | $X_1 \setminus X_2 = X_1 \cap \overline{X_2}$                       |

| T                                    | $A_1 \setminus A_2 = A_1 \cap A_2$<br>a set of transitions          |

| A                                    |                                                                     |

| Act                                  | a set of actions                                                    |

| S                                    | $Act = A \cup \{\tau\}$                                             |

| $\Sigma$                             | a set of states                                                     |

|                                      | alphabet                                                            |

| $TS = (S, P, A, \pi, \delta, s_0)$   | state attribute assignment function                                 |

| $N = (P, T, w, m_0)$                 | transition system Petri net                                         |

| $m_1[\theta > m_2]$                  | $m_1$ is reachable from $m_2$ by a transition sequence $\theta$     |

| $\Delta(\theta)$                     | differential vector                                                 |

| $\lambda$                            | labeling function                                                   |

| $LN = (N, \lambda)$                  | Labeled Petri net                                                   |

| $P = (S, A, L, \delta, \pi, s_0, F)$ | finite state process (FSP)                                          |

| L/A                                  | sequences of $L$ where all elements except $A$ are deleted          |

| L(LN)                                | Petri net language                                                  |

| $L_{\omega}(LN)$                     | Petri net infinite language                                         |

| $L_{\Delta\omega}(LN)$               | Petri net infinite language with deadlock                           |

| $L^{fair}_{\Delta\omega}(LN)$        | Petri net fair infinite language with deadlock                      |

| $TS_1 \mid TS_2$                     | process composition                                                 |

| $s \uparrow$                         | divergence                                                          |

| $TS_1 \approx_{\pi\tau\omega} TS_2$  | $\pi\tau\omega$ -bisimulation equivalence                           |

| f                                    | formula                                                             |

| $\Box f$                             | f is always true.                                                   |

| $\Diamond f$                         | f will be eventually true.                                          |

|                                      | f will be true at the next time.                                    |

| $f_1 U f_2$                          | $f_1$ continues to be true until $f_2$ becomes true.                |

| $TS \models f$                       | TS is a model of $f$                                                |

| $\ll a \gg f$                        | f will be sometime true after $a$ is occurred (minimum fixed point) |

| $\ll a \gg^+ f$                      | f will be sometime true after $a$ is occurred (maximum fixed point) |

| $[[a]]^{-}f$                         | f will be always true after $a$ is occurred (minimum fixed point)   |

| $[[a]]^+ f$                          | f will be always true after $a$ is occurred (maximum fixed point)   |

| רר זו י                              | , (                                                                 |

| apat f | f is true at all time in all paths  |

|--------|-------------------------------------|

| apet f | f is true at some time in all paths |

| epat f | f is true at all time in some path  |

| epet f | f is true at some time in some path |

# Chapter 1

# Introduction

#### 1 Motivation

Computer systems have been moving rapidly toward parallel, distributed, and reactive computing during the past decade. There is an increasing demand for programmers who can design concurrent programs for these systems. However, generally speaking, compared with sequential programming it is not so easy to produce correct and efficient concurrent programs. In particular, the cost of testing and debugging becomes a heavy burden. Moreover, most reactive systems (e.g. embedded control systems, process control systems) require high reliability. Therefore, some kind of computer-aided concurrent programming environments are necessary to enable ordinary programmers to develop concurrent programs while achieving high productivity and high reliability. The programming environment means tools for verification, debugging, performance evaluation, and methods to synthesize correct and efficient programs.

To achieve both high productivity and high reliability, a formal method is the most promising approach in the long run. In the formal method, specifications and programs (implementation) are described using some formal language, the semantics of which is formally defined. Then, the formal method provides verification and synthesis methods for these specifications and programs. Many formal methods have been proposed for concurrent systems. For example, they include models of programs (e.g., transition system, Petri net, automaton), logics of programs (e.g., Hoare logic, temporal logic, dynamic logic, process logic), and algebras of programs (e.g., CCS, CSP, ACP). Temporal logic is a especially useful formal framework for specification, verification, and synthesis for concurrent programs. Therefore, the application of temporal logic to computer science has been actively investigated by many researchers all over the world from the late 1970's to the present.

This thesis concentrates on reactive and concurrent systems. The purpose of this thesis is to establish theories, methods and tools (programming environment) for these systems using temporal logic. Especially, much consideration is given to practical techniques in order to apply temporal logic to actual reactive and concurrent systems.

To apply temporal logic to the actual development of reactive and concurrent systems, the following issues should be considered.

#### 1. Actual systems cannot be fully described by temporal logic

Standard temporal logic is too inconvenient to describe actual reactive and concurrent systems. Therefore, a syntactical extension of temporal logic for practical use or combination with other complementary formal languages is required.

#### 2. Cost of verification and synthesis is beyond practical computing power

Generally speaking, computing cost of verification and synthesis based on formal methods becomes very huge due to "state explosion problem". Consequently these methods are often applicable only to "toy programs". Techniques to avoid state explosion and reduce computing cost are required.

#### 3. Formal methods do not support the whole development process

The formal method is not an all-around player. It can support a few parts of the whole development process. Remaining parts of the process are done by traditional and informal methods. There is an obvious gap between formal methods and traditional and informal methods. Therefore, a design

methodology (guidelines) is required to specify how to utilize formal methods and informal methods complementarily in the development of reactive and concurrent programs. Furthermore, the programming environment is required to mechanically support the design methodology throughout the entire development process.

This thesis proposes the following solutions for above problems.

#### 1. Fusion of Petri nets and temporal logic

Temporal logic is appropriate for specifying the properties and constraints of programs, but inappropriate for explicitly specifying the behavioral structures of programs. In other words, temporal logic is declarative and not operational. On the other hand, Petri nets can specify the behavioral structures operationally. In this thesis, a fusion of Petri nets and temporal logic is proposed as a specification language for reactive and concurrent systems.

#### 2. Compositional verification and adjustment

A temporal logic model-checking method is actually useful to verify reactive and concurrent systems. However, as the scale of the programs increases, the computation costs for verification increase exponentially. To reduce the computation costs, this thesis introduces a compositional approach into model-checking, and proposes a new modal logic, PQL, and a compositional verification method based on PQL.

Since it seems that the conventional program generation approach from temporal logic specification is impractical, a new approach "program adjustment" is proposed, in which a target program made by programmers is automatically adjusted (tuned up) to satisfy given temporal logic constraints. Since this also causes the state explosion problem, compositional program adjustment is proposed in this thesis.

#### 3. Petri-net-based design methodology and its programming environment

As a software design methodology for reactive and concurrent systems, several methods have been proposed which include OOAD and RTSAD. However, few are based on Petri nets. Since Petri nets are used as a specification language in our approach, a Petri-net-based design method is proposed which gives guidelines for deriving detailed Petri nets from ambiguous requirements, and then verifying and adjusting programs using Petri nets and temporal logic.

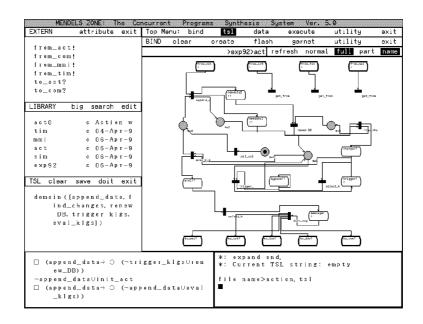

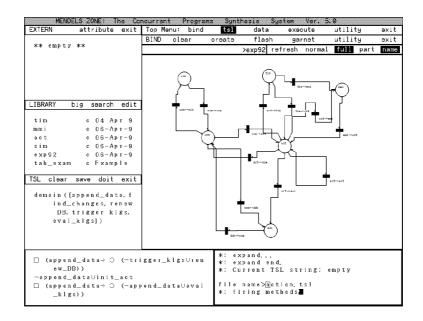

MENDELS ZONE is a programming environment for reactive and concurrent systems, which supports the software development process from first to last, including verification, adjustment, and Petri-net-based design method.

## 2 Background

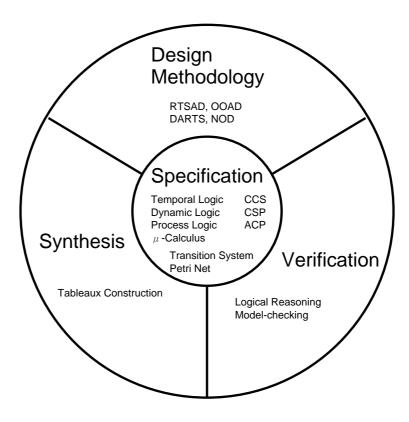

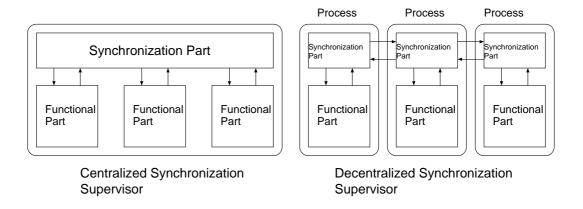

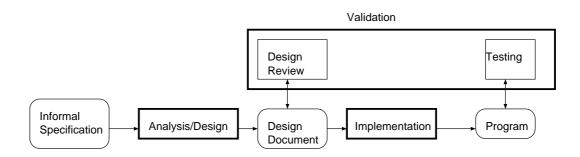

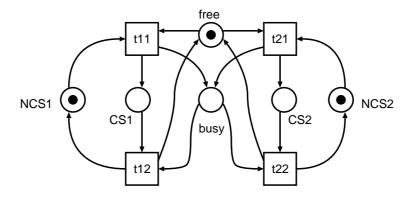

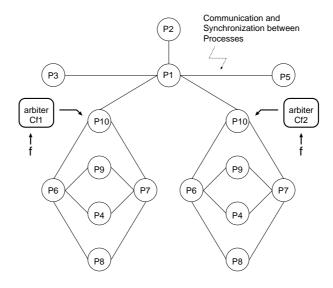

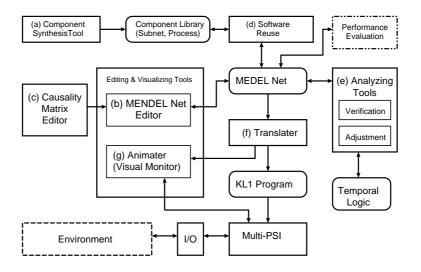

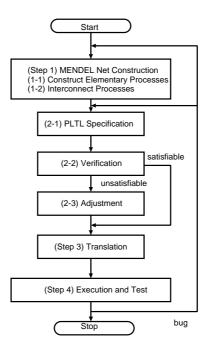

To providing the background for this thesis, this section presents a brief survey of software development techniques for reactive and concurrent systems. Especially, focusing on formal techniques including specification, verification, synthesis, and design methodology (Fig. 1).

#### 2.1 Formal Specification for Reactive and Concurrent Systems

Specifying systems formally is an effective way to recognize and clarify ambiguous parts of the system requirement/specification, and is necessary to verify the specification and synthesize programs from the specifications. A lot of specification languages for reactive and concurrent systems have been proposed. Roughly speaking, they can be classified into operational approaches and declarative approaches.

#### • Operational Approach

In an operational approach, reactive and concurrent systems are modeled with specification models/languages which are executable on the abstract machine. The operational (i.e., executable) specification models for reactive and concurrent systems include transition systems, state machines, automata, Statechart and Petri nets. These models will be described in detail in Chapter 2. However, these models are too primitive to describe practical systems. Therefore, several practical specification languages which are based on some primitive model and extended from a practical point of

Figure 1. Software Development Techniques for Reactive and Concurrent Systems

view. These specification languages include PAIZLey [Zave 82, Zave 91], SDL, and Coloured Petri Net [Jensen 92, Jensen 95].

#### • Declarative Approach

In a declarative approach, systems are modeled by logical formulas or algebraic terms, and then axioms of the logics or algebras give the semantics of the systems. For concurrent systems, a lot of declarative formalisms have been proposed, which include modal/program logic (Dynamic Logic, Temporal Logic, Process Logic, Modal  $\mu$ -calculus, UNITY logic, etc.) and process algebra (CCS, CSP, ACP,  $\pi$ -calculus, etc.).

In this thesis, we focus on  $Temporal\ Logic$ . Temporal logic is a kind of modal logic in which modal operators represent the topology of time. While the truth-values of propositions are constant in classical logic, the truth-values of propositions can be changed with time in temporal logic. For example, a statement "if a proposition p is true now, p will have to be false at the next time" can be represented by a temporal logic formula,

$$p \supset \bigcirc \neg p$$

,

where  $\bigcirc$  is a temporal operator representing the next time. This cannot be done directly by the classical logic.

From a historical point of view (see [Rescher 71]), temporal logic was initially investigated by philosophers and logicians since Prior constructed the first  $tense\ logic$  in the 1950s. Then, since the 1970s, temporal logic has been applied to computer science, especially, artificial intelligence<sup>1</sup> and software engineering<sup>2</sup>. Temporal logic is an especially useful formal framework for specification, verification, and synthesis for reactive and concurrent systems. The application of temporal logic to these systems has been actively investigated by many researchers all over the world from the late 1970's to the present. The historical background of temporal logic was well surveyed by Galton [Galton 81].

For example, McDermott's Temporal Logic, and Allen's Theory of Time.

<sup>&</sup>lt;sup>2</sup> Pnueli initially systematized temporal logic [Pnueli 77] in software engineering.

In this thesis, we adopt temporal logic as a formal specification language for reactive and concurrent systems for the following reasons.

- The modality of temporal logic is intuitive and easy for software designers to understand.

- A temporal logic formula can be translated into an equivalent  $\omega$ -automaton which is compatible with a state transition system and can be easily manipulated in verification and synthesis.

- Most reactive and concurrent systems can be basically modeled by state transition systems.

Temporal logic has been applied to *specification*, *verification*, and *synthesis* for reactive and concurrent systems. First, the research background on specification by temporal logic is briefly surveyed.

There are several variants of temporal logic. The variant initially presented by Pnueli is *linear time temporal logic*, which has been investigated chiefly by Pnueli, Manna, and their group [Pnueli 77, Pnueli 81, Manna 81a, Manna 81b, Pnueli 86, Manna 92] for specification and verification of concurrent programs. A second common version of temporal logic is *branching time temporal logic* [Ben-Ari 83, Emerson 85a]. Each logic assumes a different underlying nature of time, as follows [Emerson 90a].

- Linear time temporal logic: The course of time is linear; at each moment there is only one possible future moment.

- Branching time temporal logic: Time has a branching, tree-like nature; at each moment, time may split into alternate courses representing different possible futures.

Linear time temporal logic is suitable for specification for program synthesis, while branching time temporal logic is suited to describe queries for verification. Besides these two popular version, there are several versions of temporal logic for concurrent programs (e.g., Partial Order Temporal Logic [Pinter 84], Interval Temporal Logic (ITL) [Moszkowski 86]).

These logics are sufficient to consider the essential features of reactive and concurrent systems, but not expressive enough to describe an entire system specification. There are two approaches to make temporal logic suitable for practical specifications; extension of temporal logic and combination of temporal logic with other formalisms (called dual-language approach in [Felder 94]).

With regard to the first approach, temporal logic can be extended by introducing the following features for practical specifications.

- regular expression [Wolper 83b]

- more than operator [Yoshimura 93]

- unbounded message buffers [Sistla 84, Koymans 87]

- modularity, compositionality and abstractness [Barringer 84, Josko 87, Yonezaki 91]

- nonmonotonicity for avoiding frame problem [Saeki 87]

- real-time [Alur 89, Ostroff 90]

Furthermore, several executable specification languages based on temporal logic have been proposed, influenced by logic programming (e.g. Tempula [Moszkowski 86]), in which operational semantics can be given to extended temporal logic formulas. These executable specification languages are useful for prototyping of reactive and concurrent systems [Hale 87]. However, in spite of these extensions, it is still difficult to describe an entire practical system by temporal logic. Moreover, these extensions often make automatic verification and synthesis difficult, and increase computing costs.

With regard to the second approach, temporal logic is combined with another formalism as a specification language. Since temporal logic is declarative, a combination of temporal logic and other formal language having operational semantics, like transition system and Petri net is effective. A combination of temporal logic and Petri net has been investigated recently by our group and others. These works will be surveyed in Chapter 4. The second approach appears promising and realistic for practical specification.

#### 2.2 Verification for Reactive and Concurrent Systems

The background on the research on verification by temporal logic is briefly surveyed. There are two approaches in verification for reactive and concurrent systems; logical reasoning and model-checking.

#### • Logical Reasoning Approach:

Both specification and implementation (program) are specified by temporal logic formulas. If the specification is represented by a formula  $f_s$  and the implementation is represented by a formula  $f_i$ , then the implementation is correct iff  $f_i \supset f_s$  is valid. Manna and Pnueli [Manna 81b, Pnueli 81] presented methods for proving  $f_i \supset f_s$  inductively using axioms and inference rules. Furthermore, Manna and Wolper [Manna 84] presented an automatic verification method based on refutation, where it is shown that  $\neg(f_i \supset f_s)$  is not satisfiable using tableaux construction.

#### • Model Checking Approach:

In a model-checking approach, the specification is represented by a temporal logic formula f, and the implementation is represented as a model M of temporal logic. The implementation is correct iff M is a model of f (i.e.,  $M \models f$ ). Transition systems are usually used to represent models (i.e, implementations). Clarke, Emerson, and Sistla [Clarke 86] initially proposed an automatic verification method of finite-state concurrent systems based on model-checking. They dealt with a branching time temporal logic called CTL (Computation Tree Logic).

Since the model-checking approach can provide a practical and widely applicable verification method as compared with the logical reasoning approach, much work based on model-checking has been done over the last decades. The early researches in this area are well surveyed in [Clarke 87]. The latest trends can be caught by watching the Annual Conference on Computer-Aided Verification (CAV). These works can be classified into two types;

- Extension of expressive ability of temporal logics and models (e.g., Fairness [Emerson 85b])

- Local model-checking for Petri nets [Bradfield 92]

- Proposal of efficient model-checking algorithms

Since model-checking can be regarded as a type of state space analysis method, the *state explosion* problem is usually the limiting factor in applying these algorithms to realistic systems. Therefore, an efficient model-checking algorithm is required. These efficient algorithms can be classified into the following three approaches.

- Symbolic Model Checking [Burch 90, McMillan 93]

- Partial Order Approach [Valmari 90, Godefroid 91a, Godefroid 96]

- Compositional Approach [Clarke 89]

This thesis will focus on the compositional approach, and propose a new compositional verification method.

#### 2.3 Synthesis for Reactive and Concurrent Systems

The first attempts to synthesize reactive and concurrent systems from temporal logic specifications were developed in [Manna 84] and [Emerson 82]. Propositional versions of linear time temporal logic and branching time temporal logic are used as the specification language in [Manna 84] and [Emerson 82], respectively. Both synthesis methods are based on tableaux construction representing models of the given temporal logic formula. The target finite-state program is generated from this tableaux.

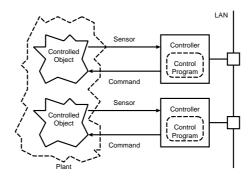

These pioneering synthesis method can be applied to the synthesis of *closed* reactive systems. The closed reactive system means a system in which all actions are observable and controllable. In contrast, *open* reactive systems has unobservable and uncontrollable actions. For example, a plant control system consists of a controller and controlled objects in which some actions and states are unobservable and uncontrollable from the controller. Pnueli and Rosner proposed a synthesis method for these open reactive systems [Pnueli 89a, Pnueli 89b, Pnueli 90].

These works made worthy contributions from the theoretical view point. However, from the practical point of view, they were suggestive but hard to apply to actual systems. The main reason is that it is too difficult and too expensive to describe a whole specification by temporal logic and then synthesize a whole program from it. Therefore, a more practical approach is proposed, "program adjustment", which modifies (adjusts) a given target program to satisfy a temporal logic specification instead of generating a whole program from it.

#### 2.4 Design Methodology for Reactive and Concurrent Systems

Software design methodology plays important part so that formal methods are utilized during the software development process. As a software design methodology for reactive and concurrent systems, several methods have been proposed; Real-Time Structured Analysis and Design (RTSAD), Object-Oriented Analysis and Design (OOAD), and Design Approach for Real-Time Systems (DARTS).

#### • Real-Time Structured Analysis and Design (RTSAD)

Real-Time Structured Analysis and Design (RTSAD) is an extension of Structured Analysis and Design for real-time systems. There are two popular variations which have been developed by Ward [Ward 85, Ward 86] and Hatley [Hatley 87], respectively. In RTSAD, functional requirements for the target system are hierarchically decomposed into several functions, which are described by data/control flow diagrams. In addition to the data/control flow diagrams, behavioral requirements are represented by state transition diagrams. Since the data flow diagram is familiar to designers and easy to understand, RTSAD has been used on a wide variety of projects and there is much experience in applying RTSAD. However, RTSAD is weak in its provision of task structuring guidelines which address how to structure the system into concurrent tasks.

#### • DARTS

In the reactive and concurrent system design, task structuring is given considerable weight. *DARTS* (Design Approach for Real-Time Systems), which was proposed by Gomaa [Gomaa 93], is a design method based on RTSAD and emphasizes the decomposition of a real-time system into concurrent tasks. DARTS provides a set of **task structuring criteria** for structuring a real-time system into concurrent tasks, as well as guidelines for for defining the interfaces between tasks.

#### • Object-Oriented Analysis and Design (OOAD)

Object-Oriented Analysis and Design (OOAD) [Booch 94, Rumbaugh 91] is a design method based on object-oriented paradigm. In OOAD, classes and objects are first identified by analyzing the problem domain, then **object diagrams** and **class diagrams** are developed to describe the relationships between classes and objects. After defining the object structure, behavior for each object is described by the **state transition diagram**. Finally, objects are classified into tasks (active objects) and packages (passive objects) of the concurrent programming language.

Generally speaking, each design method consists of several *charts* which represent functional, behavioral, and module structures of systems and *guidelines* (*criteria*) for deriving these charts. Data/control flow diagrams, state transition diagrams, and class/object diagrams are used as the design charts in the above methods.

Although a Petri net can be a promising design chart for reactive and concurrent systems, there are few design methods which use Petri nets as the design chart and give guidelines for manipulating them. Reisig [Reisig 92] proposed a design method based on Petri nets. It is very suggestive but not sufficiently mature. This thesis considers a Petri-net-oriented design method, which is called *Net-Oriented Design method* (NOD) [Honiden 92].

#### 2.5 Programming Environments for Reactive and Concurrent Systems

A lot of tools have been proposed which support formal methods for reactive and concurrent systems. Recently, these tools have become sophisticated and are of practical use $^3$ . The more well-known tools include the following.

<sup>&</sup>lt;sup>3</sup> Some of them can be easily obtained by INTERNET.

- Tools based on state transition systems (state machine, automata):

- STATEMATE<sup>4</sup> [Harel 90] and SPIN [Holzmann 91],

- Tools based on process algebra<sup>5</sup>:

Concurrency Workbench (CWB) [Cleaveland 93] and AUTO/AUTOGRAPH [Boudol 89],

• Tools based on Petri nets:

DESIGN/CPN [Jensen 92] and Cabernet [Ghezzi 93].

However, none of them is a comprehensive programming environment covering the overall development process which includes verification, synthesis, and a design methodology based on *Petri nets* and *temporal logic*.

#### 3 Synopsis

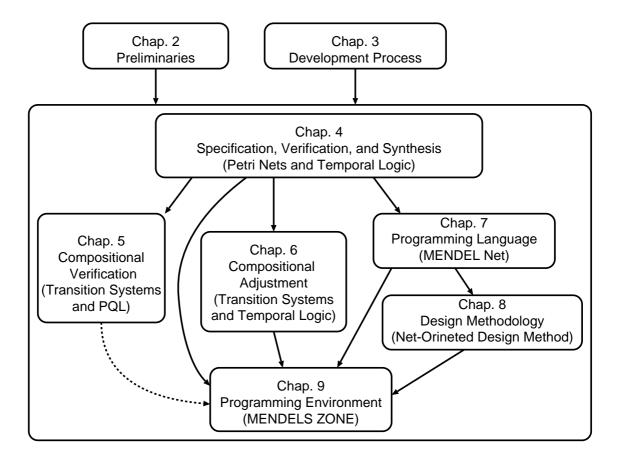

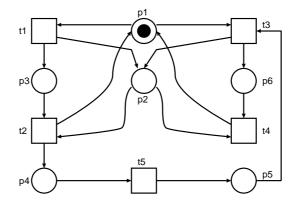

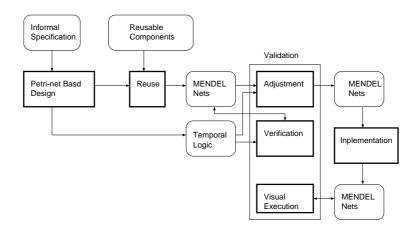

The organization of this thesis is as follows (Fig. 2).

Chapter 2 starts by providing definitions, models, and logics for reactive and concurrent systems as a preliminary section.

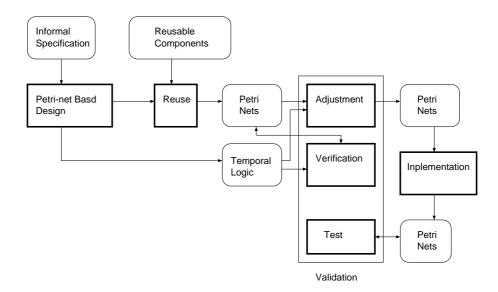

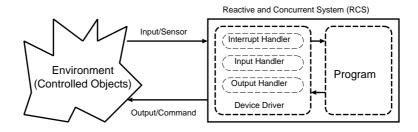

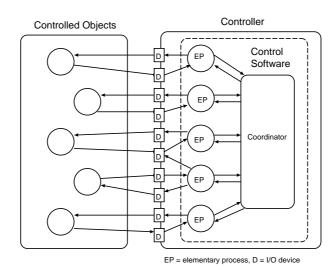

Chapter 3 considers a software development process for reactive and concurrent systems. In this chapter, a definition and the characteristics of reactive and concurrent systems and a development process for them are discussed. Finally, a software development process using Petri nets and temporal logic is conceptually proposed. According to this conceptual development process, detailed techniques are described in the following chapters.

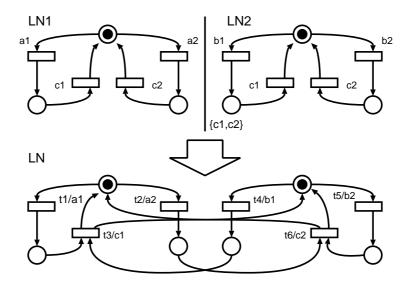

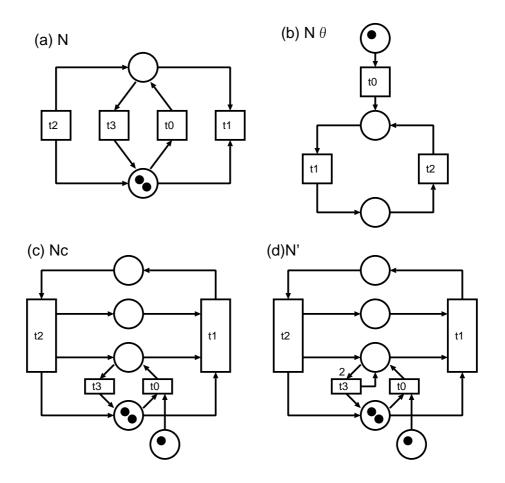

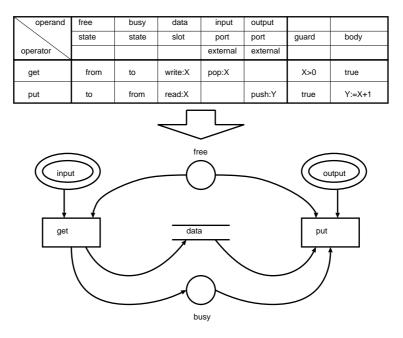

In **Chapter 4**, a fusion of Petri nets and temporal logic is proposed as a specification language for reactive and concurrent systems. Its expressive power and theoretical results are also considered. In succession, verification and synthesis methods are shown as an application of specification by Petri nets and temporal logic. Examples are provided to show the effectiveness of the verification and synthesis. The remarkable point is that proposed methods are for unbounded Petri nets, while former verification and synthesis methods were mainly for bounded (safe) Petri nets.

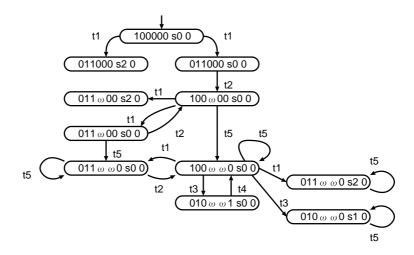

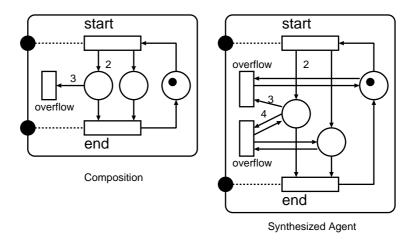

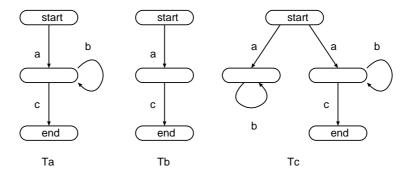

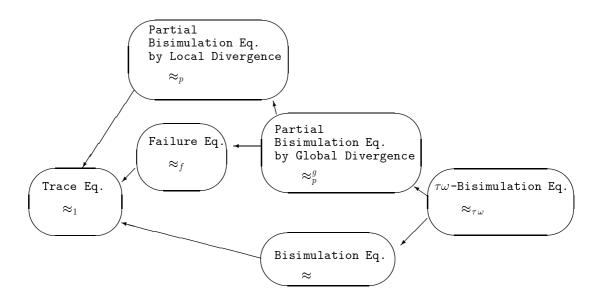

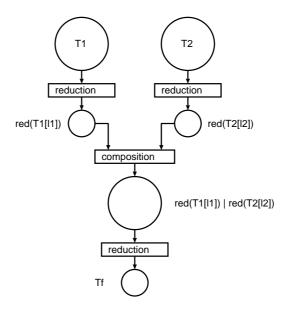

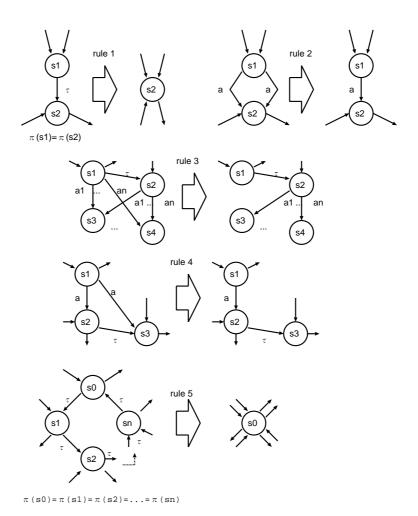

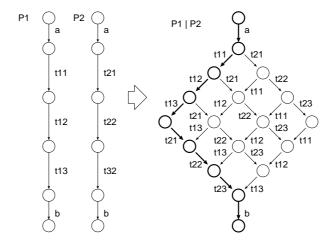

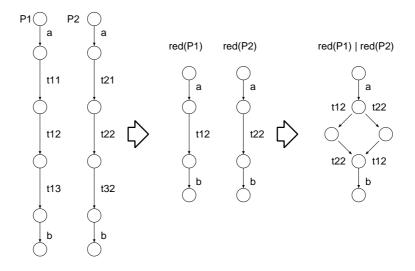

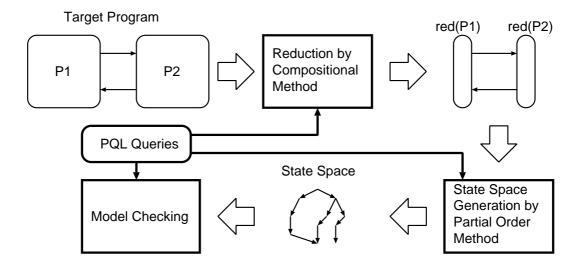

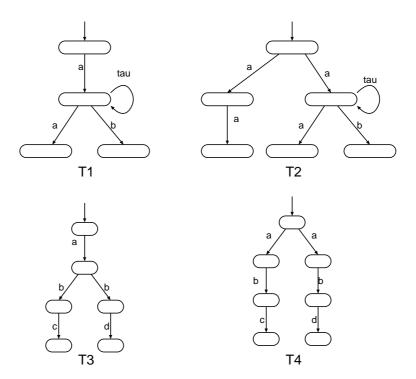

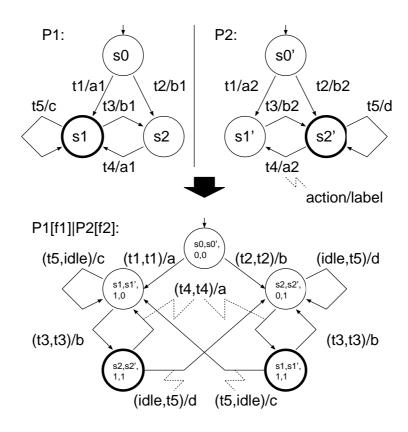

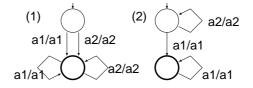

Chapter 5 considers an efficient and practical verification method, temporal logic model-checking, for finite-state (i.e. bounded) systems. The model-checking method is actually useful to verify reactive and concurrent systems. However, as the scale of the programs increases, the computation costs for verification increase exponentially due to the state explosion. To ease the state explosion, a compositional approach to model-checking seems promising and is adopted here. The point of compositional verification is to reduce (localize, minimize) the target program, leaving only essential information for each verification query. The reduction of the target program is formalized by process equivalence theory. This chapter introduces a new process equivalence relation ( $\pi\tau\omega$ -bisimulation equivalence) for compositional verification. This new relation is required because conventional bisimulation equivalence, which was used in other compositional verification, cannot deal with "divergence" explicitly. An explanation of why conventional bisimulation equivalence does not work well with divergence is given, and then  $\pi\tau\omega$ -bisimulation is defined. After this, Process Query Language (PQL) is proposed. PQL is a modal logic which is union of temporal logic and process logic, and the semantics of which is based on  $\pi\tau\omega$ -bisimulation equivalence. Then, this chapter proposes the compositional verification method using PQL with consideration of the divergence. Its effectiveness is demonstrated by means of some experimental results.

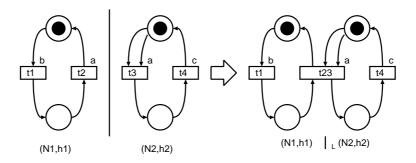

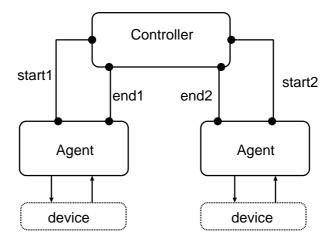

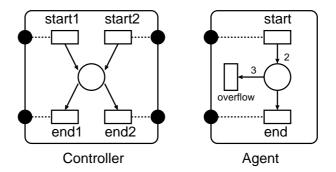

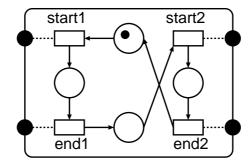

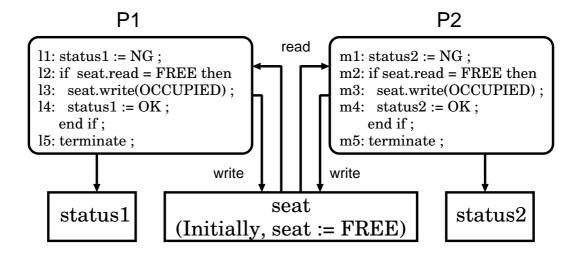

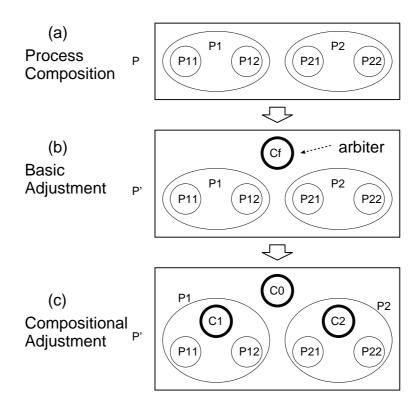

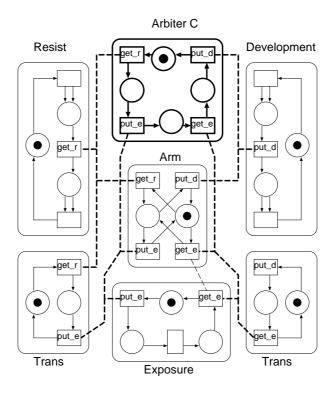

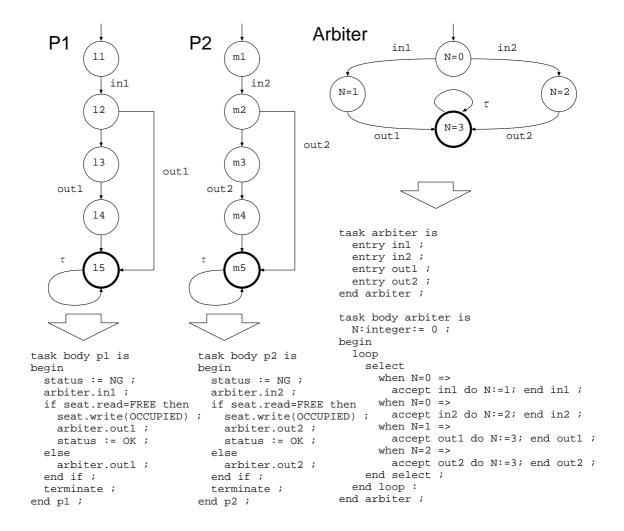

In Chapter 6, program synthesis using temporal logic is discussed. From the standpoint that the conventional program generation approach from temporal logic specification, which was initially proposed by Manna and Wolper [Manna 84], is impractical, this chapter proposes a new approach, "program adjustment". In program adjustment, a target program made by programmers, which may be functionally correct but may be imperfect in its timing, is automatically adjusted (tuned up) to satisfy given temporal logic constraints. To put it concretely, program adjustment is realized by adding an arbiter process which is synchronized with and restricts the behavior of the target program. It is more feasible for ordinary programmers to adopt the program adjustment approach compared to conventional program generation approach for the following reasons.

<sup>&</sup>lt;sup>4</sup> STATEMATE is a trademark of i-Logix

<sup>5</sup> These tools are also applicable for state transition systems which are equivalent to the process algebra.

- It is not very difficult for ordinary programmers to produce a target program, which satisfies at least the functional requirements. A more difficult task is to design and debug the timing of such programs.

- It is easy for ordinary programmers to specify timing constraints, such as deadlock-free and starvation-free constraints, as compared with implementing them.

- Computation cost of program adjustment is generally smaller than program generation.

Furthermore, when a target program becomes large, the arbiter synthesis may cause a computing cost explosion. Therefore, we propose compositional adjustment.

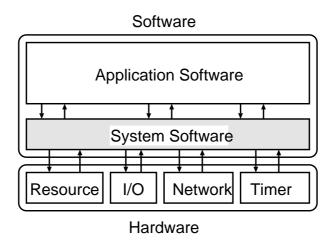

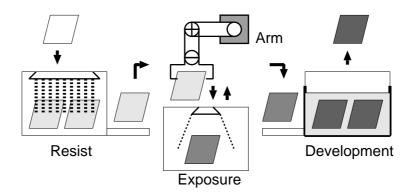

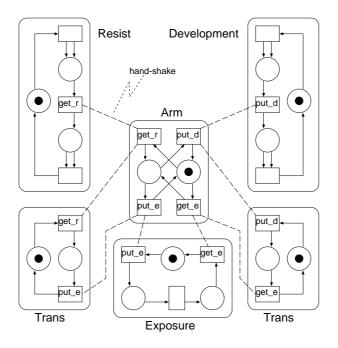

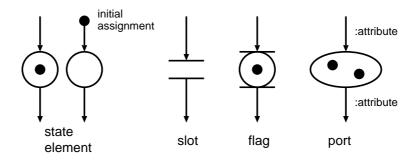

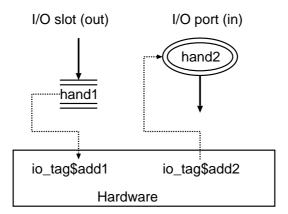

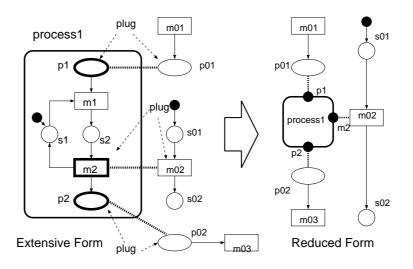

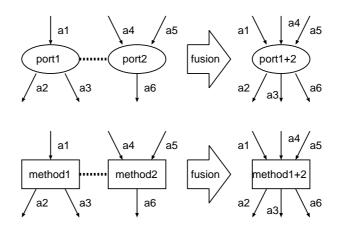

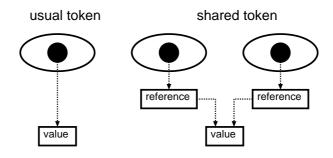

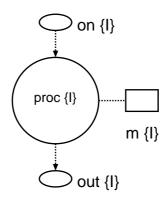

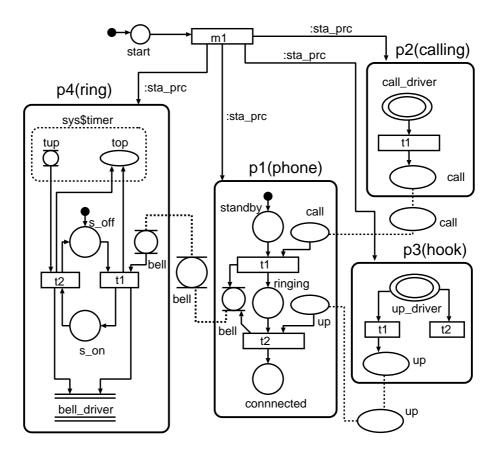

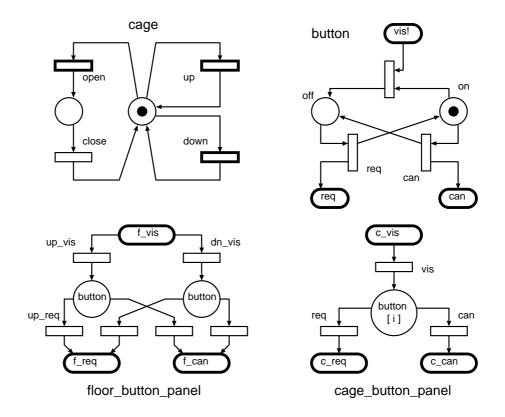

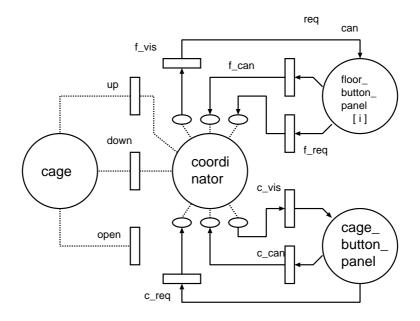

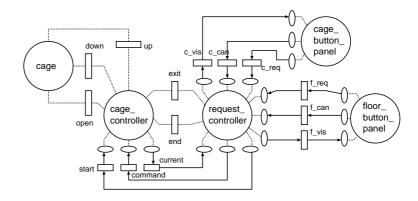

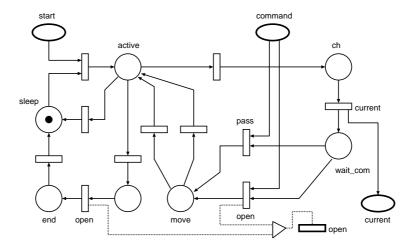

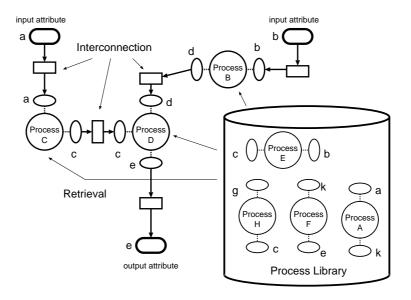

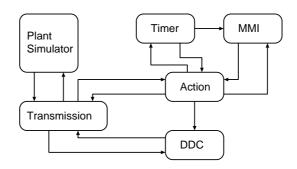

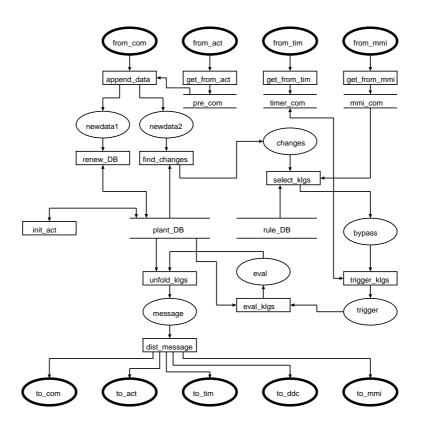

Chapter 7 considers Petri nets as a programming language instead of a specification language. First, it is discussed what properties are required for a programming language for reactive and concurrent systems, and what extensions are required to use Petri nets as a programming language. Then, a MENDEL net is introduced, which is a high-level Petri net for reactive and concurrent systems. A MENDEL net can be used not only for specification but also for programming (detail prototyping) owing to several extensions, an I/O interface with the environment, concurrent tasks, and a mechanism for their scheduling.

Chapter 8 proposes a software design methodology based on MENDEL nets and temporal logic, which is called Net-Oriented Design method (NOD). In this method, a causality matrix is introduced at an earlier design phase when the system structure is obscure and it is difficult to write MENDEL nets directly. According to the design method utilizing causality matrices, a designer can construct MENDEL nets systematically from an ambiguous requirement, then verify and adjust the MENDEL nets by methods based on temporal logic mentioned in earlier chapters.

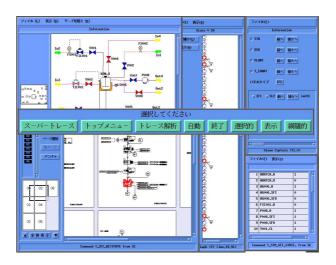

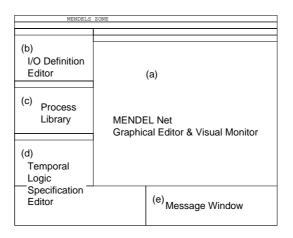

Chapter 9 shows an overview of a programming environment for reactive and concurrent systems, called *MENDELS ZONE*. MENDELS ZONE provides analysis tools based on formal methods (e.g., verification and adjustment tools) and a design support tool based on the informal design method (e.g., causality matrix editor) in addition to the usual programming tools such as graphical MENDEL net editor, simulator, and compiler. MENDELS ZONE has been implemented on the parallel machine, Multi-PSI.

Finally, Chapter 10 concludes this thesis, summarizing the research contributions, and presenting intentions for further work.

Related our publications are summarized as follows.

Chapter 4: [Uchihira 90b]

Chapter 5: [Uchihira 92a]

Chapter 6: [Uchihira 92c, Uchihira 95a]

Chapter 7: [Uchihira 96b]

Chapter 8: [Uchihira 92b]

Chapter 9: [Uchihira 87, Uchihira 88, Uchihira 90a, Uchihira 92b, Uchihira 95a]

Figure 2. Organization of The Thesis

# Chapter 2

# Preliminaries: Models and Logics for Reactive and Concurrent Systems

This chapter introduces several notations and definitions of models and logics for reactive and concurrent systems.

#### 1 Models for Reactive and Concurrent Systems

Many models have been proposed for reactive and concurrent systems. Most of them are based on state transition systems which may be extended about *concurrency* and *liveness*. Among them, this section shows Transition System, Büchi Sequential Automaton, Finite State Process, and Petri Net.

#### 1.1 Sequence

To begin with, we introduce several notations about sequences. In the context of this thesis, a sequence is used to represent the time series of actions which a reactive and concurrent system takes, and states which it stays in.

Let X be a set. The set of all finite sequences over X, including the empty sequence  $\varepsilon$ , is denoted by  $X^*$ . If there is no empty sequence  $\varepsilon$ , the set is denoted by  $X^+$ . The set of all infinite sequences over X is denoted by  $X^\omega$ ;  $\omega$  means "infinitely many".  $X^\infty$  is defined by  $X^\infty = X^* \cup X^\omega$ .  $\overline{X}$  means a complementary set of X.  $X_1 \setminus X_2 = X_1 \cap \overline{X_2}$

For a sequence  $\theta \in X^{\infty}$ ,  $\theta[i]$  means the *i*-th element in  $\theta$ ;  $\theta(k)$  means the prefix subsequence  $\theta[1]\theta[2]...\theta[k]$  of  $\theta$ , and  $|\theta|$  the length of  $\theta$ .

For  $A \subset X$  and  $L \subset X^{\infty}$ , L/A is defined as  $L/A \stackrel{def}{=} \{\theta' \mid \exists \theta \in L. \forall i. (\theta'[i] = \theta[i] \text{ if } \theta[i] \in A$ , otherwise  $\theta'[i] = \varepsilon)\}$ . "/" is a label restriction operator. Intuitively, L/A consists of sequences of L in which all elements except A are deleted.

#### 1.2 Transition System

Definition 1 (Transition System)

$TS = (S, P, A, \pi, \delta, s_0)$

$S:A\ set\ of\ states$

$P: A \ set \ of \ state \ attributes$

A: A set of actions

$Act = A \cup \{\tau\}$

au: an unobservable internal transition

$\pi: S \to 2^P$  A boolean function

$\delta: S \times Act \rightarrow 2^S$  A nondeterministic transition function

$s_0$ : An initial state

For  $TS = (S, P, A, \pi, \delta, s_0)$  and  $s, s' \in S$  and  $a \in A$ ,  $p \in \pi(s)$  means that a state attribute p is true in s, and  $s' \in \delta(s, a)$  means that the system which stays in s can move to the state s' after an action a.

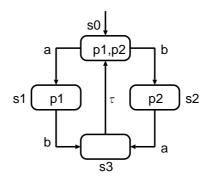

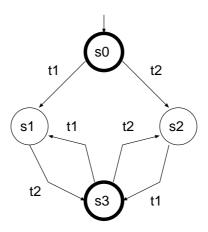

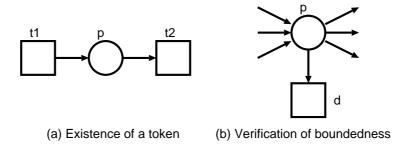

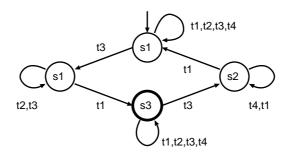

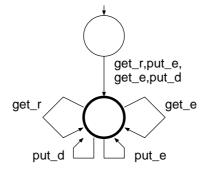

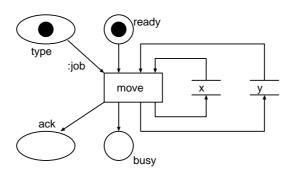

According to Milner's notation [Milner 89],  $\delta(s,a) \ni s'$  is expressed as  $s \stackrel{a}{\Rightarrow} s'$ ,  $s(\stackrel{\tau}{\rightarrow})^* \stackrel{a}{\rightarrow} (\stackrel{\tau}{\rightarrow})^*s'$  is expressed as  $s \stackrel{a}{\Rightarrow} s'$ . Also,  $\hat{a}$  expresses a when  $a \neq \tau$ , and  $\hat{a}$  expresses  $\varepsilon$  when  $a = \tau$ . Here,  $\varepsilon$  means an empty string, that is,  $s \stackrel{\hat{\tau}}{\Rightarrow} s' = s \stackrel{\varepsilon}{\Rightarrow} s' = s(\stackrel{\tau}{\rightarrow})^*s'$ . We show a simple example of a transition system in Figure 3.

**Example 1 (Transition System)**  $T = (\{s_0, s_1, s_2, s_3\}, \{p_1, p_2\}, \{a, b\}, \pi, \delta, s_0) \ where s_0 \xrightarrow{a} s_1, s_0 \xrightarrow{b} s_2, s_1 \xrightarrow{b} s_3, s_2 \xrightarrow{a} s_3, s_3 \xrightarrow{\tau} s_0, and \ \pi(s_0) = \{p_1, p_2\}, \pi(s_1) = \{p_1\}, \pi(s_2) = \{p_2\}, \pi(s_3) = \emptyset.$

Figure 3. Example of a transition system

#### Definition 2 (Finite Branching Condition)

A finite branching condition in  $TS = (S, P, A, \pi, \delta, s_0)$  is:

$\delta(s, a)$  is a finite set for  $\forall s \in S$  and  $\forall a \in A$ .

This finite branching condition is necessary for the fully automatic verification and synthesis for transition systems. When S, P, and A are finite, the finite branching condition is satisfied. We assume S, P, and A in TS are finite whenever we do not mention it explicitly.

#### 1.3 Büchi Sequential Automata

A transition system can model all possible (safe) behaviors of systems, but cannot model desirable behaviors. A finite automaton can express desirable (acceptable) behaviors explicitly using terminal states.

**Definition 3 (Finite Automaton)** A finite automaton is a tuple  $A = (\Sigma, S, \rho, s_0, F)$ , where

- $\Sigma$  is an alphabet,

- S is a set of states,

- $\rho: S \times \Sigma \to 2^s$  is a nondeterministic transition function,

- $s_0 \in S$  is an initial state, and

- $F \subset S$  is a set of terminal states.

A run of a finite automaton A over a finite word  $\theta = t_1 t_2 ... t_n \in \Sigma^*$  is a state sequence  $s_0, s_1, ..., s_n$ , where  $s_i \in \rho(s_{i-1}, t_i)$  for all  $i \geq 1$ . A run  $s_0, s_1, ..., s_n$  is accepting if  $s_n \in F$ . A finite word  $\theta$  is accepted by A if there is an accepting run of A over  $\theta$ . The set of all words, accepted by A, is denoted L(A).

A finite automaton treats only finite sequences (words). Since reactive and concurrent systems often takes infinite ongoing computation, a finite automaton on infinite sequences is necessary to model them.

**Definition 4 (Büchi Sequential Automaton )** Büchi sequential automaton is a tuple  $A = (\Sigma, S, \rho, s_0, F)$ , where

- $\Sigma$  is an alphabet,

- S is a set of states,

- $\rho: S \times \Sigma \to 2^s$  is a nondeterministic transition function,

- $s_0 \in S$  is an initial state, and

- $F \subset S$  is a set of designated states.

A run of a Büchi sequential automaton A over an infinite word  $\theta = t_1 t_2 ... \in \Sigma^{\omega}$  is a sequence  $s_0, s_1, ...,$  where  $s_i \in \rho(s_{i-1}t_i)$  for all  $i \geq 1$ . A run  $s_0, s_1, ...$  is accepting if for some  $s \in F$  there are infinitely many i's such that  $s_i = s$ . An infinite word  $\theta$  is accepted by A if there is an accepting run of A over  $\theta$ . The set of all words, accepted by A, is denoted L(A).

#### 1.4 Finite State Process

A finite state process [Kanellakis 90] is defined as a general model which includes both a transition system and an automaton. Therefore a finite state process can specify a transition system with *liveness conditions* as its acceptance condition.

**Definition 5 (Finite State Process)** A Finite State Process (FSP) is a seventuple  $P = (S, A, L, \delta, \lambda, s_0, F)$ , where:

- S is a finite set of states,

- A is a finite set of actions,

- L is a finite set of synchronization labels,

- $\delta: S \times A \to S \cup \{\bot\}$  is a **deterministic** transition function  $(\delta(s,t) = \bot \text{ means the action } t \in A \text{ is disabled in the state } s \in S)$ ,

- $\lambda: A \to (L \cup \{\tau\})$  is a labeling function,  $(\tau \text{ is an invisible internal action}),$

- $s_0 \in S$  is an initial state, and

- $F \subset S$  is a set of designated states.

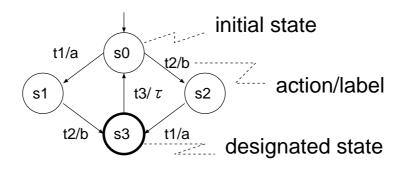

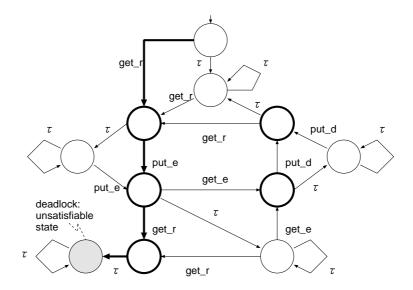

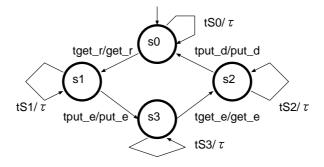

**Example 2 (Finite State Process)**  $P = (\{s_0, s_1, s_2, s_3\}, \{t_1, t_2, t_3\}, \{a, b\}, \delta, \lambda, s_0, \{s_3\})$  is a finite state process where  $\delta(s_0, t_1) = s_1, \delta(s_0, t_2) = s_2, \delta(s_1, t_2) = s_3, \delta(s_2, t_1) = s_3, \delta(s_3, t_3) = s_0, \lambda(t_1) = a, \lambda(t_2) = b, \lambda(t_3) = \tau$ . (Fig.4)

Figure 4. Finite State Process

Let  $P = (S, A, L, \delta, \lambda, s_0, F)$  be an FSP. A transition function can be extended such that  $\delta : S \times A^* \to S \cup \{\bot\}$ , i.e.,  $\delta(s, \theta a) \stackrel{def}{=} \delta(\delta(s, \theta), a)$ . Note,  $\delta(s, \varepsilon) = s$ . Since a transition function is deterministic, a current state can be uniquely determined from an initial state and an action sequence. We call an

action sequence a behavior. Similarly, we can extend a labeling function such that  $\lambda: A^* \to (L \cup \{\tau\})^*$ , i.e.,  $\lambda(\theta) = \lambda(\theta[1])\lambda(\theta[2])...\lambda(\theta[\mid \theta\mid])$ . In addition,  $\hat{\lambda}(\theta)$  is defined as the sequence gained by deleting all occurrences of  $\tau$  from  $\lambda(\theta)$ . The set of reachable states from a state s in P is defined as  $R_P(s) \stackrel{def}{=} \{s' \in S \mid \exists \theta \in A^*.s' = \delta(s,\theta)\}$ . Also, the set of all possible action sequences of P is defined as  $L(P) \stackrel{def}{=} \{\theta \in A^* \mid \delta(s_0,\theta) \neq \bot\}$ , and the set of all possible label sequences is defined as  $L_{\lambda}(P) \stackrel{def}{=} \{\hat{\lambda}(\theta) \in L^* \mid \theta \in L(P)\}$ . Since interest is in the infinite behavior of an FSP, we introduce a set of infinite action sequences  $L_{\omega}(P) \subset A^{\omega}$  and  $L_{\Delta\omega}(P) \subset (A^{\omega} \cup A^*\{\Delta\}^{\omega})$  where  $\Delta$  means deadlock:

$$L_{\omega}(P) \stackrel{def}{=} \{ \theta \in A^{\omega} \mid 1 \leq \forall k. \delta(s_0, \theta(k)) \neq \bot \}$$

$$L_{\Delta\omega} \stackrel{def}{=} \left\{ \begin{cases} \{\theta \in A^{\omega} \mid 1 \leq \forall k. \delta(s_0, \theta(k)) \neq \bot \} \cup \\ \{\theta \in A^* \{\Delta\}^{\omega} \mid \exists k. (\begin{cases} 1 \leq \forall i \leq k. \delta(s_0, \theta(i)) \neq \bot \text{ and} \\ \forall a \in A. \delta(\delta(s_0, \theta(k)), a) = \bot \text{ and} \\ \theta[j] = \Delta \text{ for } \forall j > k \end{cases} \right\}) \right\}$$

$L_{\Delta\omega}(P)$  is an extension of L(P) into a set of infinite action sequences where if  $\theta \in L(P)$  is a deadlock sequence (i.e., an inevitably finite sequence), then  $\theta$  is represented as  $\theta \Delta^{\omega} \in L_{\Delta\omega}(P)$ .

$L_{\Delta\omega}^{fair}(P) \subset L_{\Delta\omega}(P)$  is defined as  $L_{\Delta\omega}^{fair}(P) \stackrel{def}{=} \{\theta \mid \theta \in L_{\Delta\omega}(P) \text{ under the fairness condition}\}$  where the fairness condition means whenever a behavior  $\theta$  infinitely often passes through some state s, every action a enabled at s must appear infinitely often on  $\theta$  (i.e., if  $s = \delta(s_0, \theta(i))$ ) for infinitely many i and  $\delta(s, a) \neq \bot$ , then  $s = \delta(s_0, \theta(j))$  and  $\theta[j+1] = a$  for infinitely many j).

An FSP is a transition system with liveness conditions. In an FSP, liveness conditions are represented by designated nodes that indicate *satisfiable behavior* of an FSP as follows.

**Definition 6 (Satisfiable Behavior)** Let  $P = (S, A, L, \delta, \lambda, s_0, F)$  be an FSP.  $\theta \in A^{\omega}$  is a satisfiable behavior, if  $\delta(s_0, \theta(k)) \in F$  for infinitely many  $k \geq 1$ .  $L_b(P) \subset A^{\omega}$  is defined as a set of all satisfiable behaviors on P.

Note that a satisfiable behavior corresponds to an accepting run of Büchi automaton.

#### Definition 7 (Completeness of FSP)

Let

$$P = (S, A, L, \delta, \lambda, s_0, F)$$

be an FSP. P is complete if  $\forall s \in R_P(s_0) . \exists s' \in R_P^+(s)$  and  $s' \in F$ .  $\Box$

A state  $s \in R_P(s_0)$ , having no path to designated nodes from s, is called an *unsatisfiable state*. If P is complete, P has no unsatisfiable states. A behavior reaching an unsatisfiable state is called an *inevitably unsatisfiable behavior*.

**Lemma 1** If an FSP

$$P$$

is complete, then  $L_{\Delta\omega}^{fair}(P) \subset L_{sat}(P)$ .  $\square$