## T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

## 論文 / 著書情報 Article / Book Information

| 題目(和文)            | 低電力LSIに向けた薄膜 Box-SOI (SOTB) CMOSFET の研究                                                                                                                                                   |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | A study on Silicon-on- t hin-Box (SOTB) CMOSFET for low-power LSIs                                                                                                                        |

| 著者(和文)            | 石垣隆士                                                                                                                                                                                      |

| Author(English)   | Takashi Ishigaki                                                                                                                                                                          |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第8942号,<br>授与年月日:2012年9月25日,<br>学位の種別:課程博士,<br>審査員:岩井 洋                                                                                             |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第8942号,<br>Conferred date:2012/9/25,<br>Degree Type:Course doctor,<br>Examiner: |

| <br>学位種別(和文)      | 博士論文                                                                                                                                                                                      |

| Type(English)     | Doctoral Thesis                                                                                                                                                                           |

### **Doctorial Thesis**

# A Study on Silicon-on-Thin-BOX (SOTB) CMOSFET for Low-Power LSIs

Takashi Ishigaki

September, 2012

Supervisor: Prof. Hiroshi Iwai Co-supervisor: Prof. Nobuyuki Sugii

#### **Abstract**

Planar bulk CMOSFETs, which has led the device scaling trend so far, is going to end, because its large threshold voltage ( $V_{\rm th}$ ) variation significantly increases the power consumption of LSIs. Silicon-on-thin-BOX (SOTB) CMOSFET, which was fully depleted silicon on insulator (FD-SOI) with an ultrathin BOX, was proposed to realize high-performance and low-power LSIs by solving the  $V_{\rm th}$  variation issue. The studies described in this thesis were accomplished in order to realize SOTB CMOSFET for low standby power (LSTP) in 65-nm generation and show the effectiveness of SOTB technology for reducing the power consumption quantitatively. The studies for utilizing the SOTB technology such as peripheral circuits and reliability are also described.

Firstly, the scaling of CMOSFET and the power consumption issues of recent LSIs which are caused by the variability of conventional planar CMOSFETs are introduced in chapter 1. As a solution of the problem, the concept and features of SOTB CMOSFET are described. The previous works and the purpose of this thesis are also presented in detail.

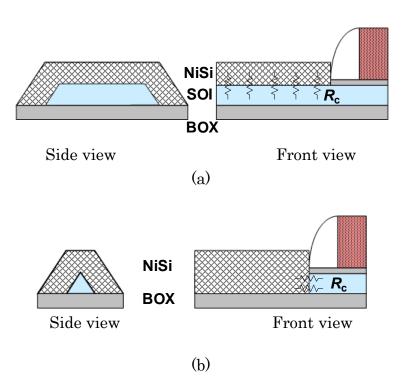

In chapter 2, the fabricating processes of SOTB CMOSFET in 65-nm generation are described. A simple fully silicided (FUSI) gate structure by using nickel silicide (NiSi) as the gate metal was combined with a raised source/drain (S/D) structure by using a selective epitaxial growth (SEG). The obtained desirable  $V_{\rm th}$  values and low parasitic S/D resistance ( $R_{\rm sd}$ ) result in better performance than those of planar bulk CMOSFETs in the same generation. The special features of SOTB CMOSFET, that is, low  $V_{\rm th}$  variation and wide-range back-bias control are also demonstrated.

In chapter 3, the reduction of power consumption by using SOTB technology is presented. Firstly, the off-current of SOTB CMOSFET was examined and the ultralow off-current less than 1 pA/ $\mu$ m was achieved by controlling the overlap length ( $L_{ov}$ ) between the gate and S/D extensions. A boosted performance by using back-gate biasing was experimentally demonstrated in this ultralow off-current case. The  $V_{th}$  variation of SOTB CMOSFET was

successfully reduced to half in comparison with conventional bulk CMOSFETs even under the wide-range back-biasing. The impact of the low  $V_{\rm th}$  variation can reduce the supply voltage of 6T-SRAM from 1.1 to 0.6 V. The reduction of standby power consumption in 6T-SRAM was also estimated to be reduced to 7%.

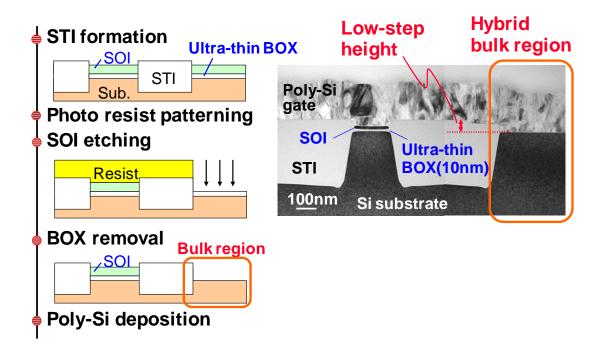

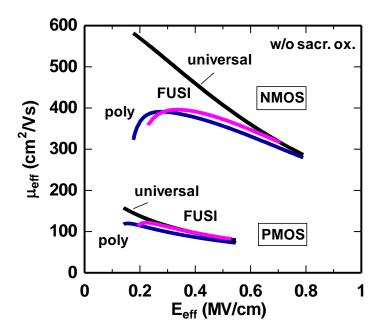

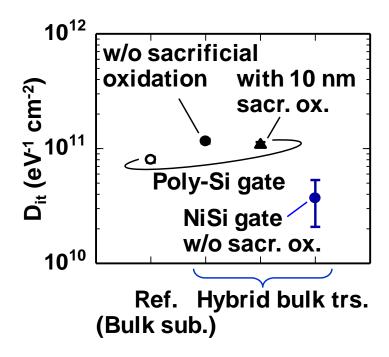

In chapter 4, a novel hybrid integration of SOTB and bulk CMOSFETs is introduced. By using the ultrathin SOI and BOX layers of SOTB structure, the conventional bulk CMOSFET for input/output (I/O) circuits was fabricated at the same time. There was a concern about the exposed Si substrate in this process. Hence, the quality and reliability of the gate dielectric were investigated. The comparable characteristics with conventional devices in the mobilities and time dependent dielectric breakdown (TDDB) are shown.

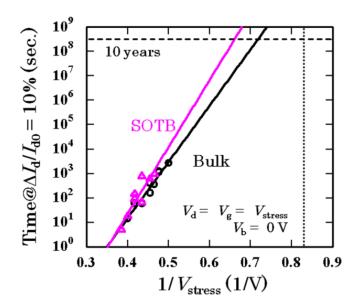

In order to put a new device structure in practical use, it is more important than anything to establish its reliability. Hot carrier injection (HCI) for SOTB NMOSFET and negative bias temperature instability (NBTI) for SOTB PMOSFET are investigated in chapter 5. The effects of the back-gate biasing for these phenomena were also analyzed. In this kind of device (FD-SOI with back-bias control), it is noted that these studies were the first trial. It is clarified that the intrinsic channel without halo implant of SOTB CMOSFET result in superior reliability to conventional bulk CMOSFETs. It is also presented that the back-biasing has impact on the HCI but on the NBTI with their mechanisms.

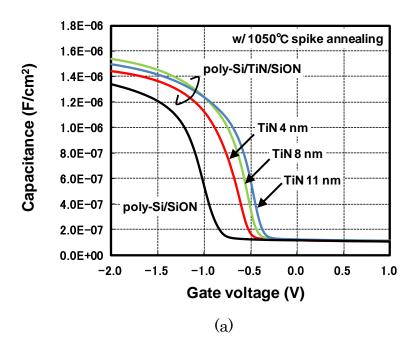

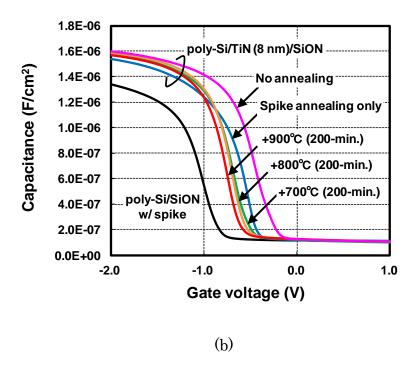

In late 2000s, trends of studies for metal gate technology were shifting toward metal-inserted polycrystalline-silicon (MIPS) gate structures. Since the FUSI gate process is hard to control its uniformity when mass production is assumed, the MIPS gate structure using TiN for SOTB CMOSFET is studied in chapter 6. The effective work function modulation was found in the case of conventional SiON gate dielectric. The way for obtaining the desirable  $V_{\rm th}$  values considering the SOTB process is shown. The difference of the narrow channel characteristics between FUSI and TiN gates were also analyzed.

Finally, the summary and conclusions of this study are described in chapter 7.

### Acknowledgments

I would like to thank to Prof. Hiroshi Iwai of Tokyo Institute of Technology for his guidance, encouragement and support for this thesis. I am also grateful to Prof. Kazuo Tsutsui, Prof. Kuniyuki Kakushima, Prof. Masahiro Watanabe, Prof. Shun-ichiro Ohmi, and Prof. Nobuyuki Sugii of Tokyo Institute of Technology for reviewing the thesis and for valuable advices.

All studies referred to in this thesis were performed at Hitachi Ltd. (Hitachi) during 2005-2009. I am indebted to everyone with whom I have worked at Hitachi over the years. Thanks are due to Dr. Shin'ichiro Kimura, Dr. Nobuyuki Sugii, Dr. Ryuta Tsuchiya, Dr. Yusuke Morita, and Dr. Hiroyuki Yoshimoto for their fruitful discussion and support of my studies.

I am also grateful the staff at Renesas Electronics Corp. (Renesas) for fabricating the devices in this thesis. I would like to express my thanks to Dr. Yasuo Inoue, Dr. Takashi Ipposhi, Dr. Hidekazu Oda, and Dr. Toshiaki Iwamatsu of Renesas for their assistance with the device fabrication.

I would like to express my appreciation to Dr. Takahiro Onai, Dr. Kazuyoshi Torii, Dr. Yasuhiro Shimamoto, and Dr. Masanori Odaka of Hitachi and Prof. Toshiro Hiramoto of University of Tokyo for their encouragement.

I would like to express sincere gratitude to laboratory secretaries, Ms. M. Nishizawa and Ms. A. Matsumoto for their invaluable assistance regarding administrative issues.

This work was partly supported by the Ministry of Education, Culture, Sports, Science and Technology of Japan.

## Contents

| Abstra  | act                                                      | i     |

|---------|----------------------------------------------------------|-------|

| Ackno   | wledgments                                               | iii   |

| List of | f Tables                                                 | viii  |

| List of | f Figures                                                | ix    |

| Symbo   | ols and Abbreviations                                    | xiv   |

| Chapt   | er. 1 Introduction – Background and Motive of This Study | 1     |

| 1.1     | MOSFET scaling                                           | 3     |

| 1.2     | Threshold voltage variation issues                       | 4     |

| 1.3     | Intrinsic-channel MOSFET                                 | 8     |

| 1.4     | SOTB CMOSFET                                             | 10    |

| 1.5     | Purpose of this study                                    | 11    |

| 1.6     | References                                               | 17    |

| 2.1     | Introduction                                             | 22    |

| 2.2     | Fabrication of SOTB CMOSFET                              |       |

| 2.3     | DC characteristics of SOTB CMOSFET for 1.2-V operation   | 27    |

| 2.4     | Wide-range back-biasing of SOTB CMOSFET                  | 31    |

| 2.5     | Conclusion                                               | 34    |

| 2.6     | References                                               | 34    |

| Chapt   | er. 3 Reduction of Power Consumption by Using SOTB Techn | ology |

|         | 36                                                       |       |

| 3.1     | Introduction                                             | 38    |

| 3.2     | Device design for GIDL reduction                         | 38    |

| 3.3     | Ultralow off-current                                     | 41    |

| 3.4     | Boosted performance by using back-gate biasing           | 42    |

| 3.5     | Variability of SOTB CMOSFET                              | 44    |

| 3.6   | Reduction of power consumption                                  | 47       |

|-------|-----------------------------------------------------------------|----------|

| 3.7   | Conclusion                                                      | 51       |

| 3.8   | References                                                      | 51       |

| Chapt | er. 4 Hybrid Integration of SOTB and Bulk CMOSFETs              | 53       |

| 4.1   | Introduction                                                    | 55       |

| 4.2   | Hybrid integration of SOTB and bulk CMOSFETs                    | 55       |

| 4.3   | Characteristics of hybrid bulk CMOSFET for I/O operation        | 57       |

| 4.4   | Conclusion                                                      | 62       |

| 4.5   | References                                                      | 63       |

| Chapt | er. 5 HCI and NBTI Reliability of SOTB CMOSFET                  | 64       |

| 5.1   | Introduction                                                    | 66       |

| 5.2   | Electrical characterization                                     | 66       |

| 5.3   | Hot carrier injection in SOTB NMOSFET                           | 68       |

| 5.4   | Effect of back-biasing in the case of hot-carrier injection     | 73       |

| 5.5   | Negative bias temperature instability in SOTB PMOSFET           | 76       |

| 5.6   | Effect of back-biasing in the case of negative-bias temperature | <b>;</b> |

| inst  | ability                                                         | 79       |

| 5.7   | Conclusion                                                      | 80       |

| 5.8   | 5.8 References                                                  |          |

| Chapt | er. 6 MIPS Gate Structure for SOTB CMOSFET                      | 83       |

| 6.1   | Introduction                                                    | 85       |

| 6.2   | Investigation of flat-band voltages in poly-Si/TiN/SiON gate st | tacks86  |

| 6.3   | Integration of poly-Si/TiN/SiON gate stack into SOTB CMOSE      | ETs 91   |

| 6.4   | Conclusion                                                      | 97       |

| 6.5   | References                                                      | 97       |

| Chapt | er. 7 Summary and Conclusions                                   | 99       |

| 7.1   | Summary                                                         | 101      |

| 7.2   | Conclusions                                                     | 102      |

| 7.3   | References                                                      | 105      |

| Publications and Presentations | 107 |

|--------------------------------|-----|

| Books                          | 109 |

## List of Tables

| Table 1.1 | The scaling rule [1.2]                                | 3  |

|-----------|-------------------------------------------------------|----|

| Table 1.2 | Subjects studied in this thesis                       | 13 |

| Table 2.1 | Comparison of the characteristics in 65-nm generation | 30 |

| Table 4.1 | Characteristics of fabricated hybrid CMOSFETs         | 60 |

| Table 6.1 | Process conditions for each device                    | 92 |

## List of Figures

| Fig. | 1.1         | Power dissipation trend of IT equipment in Japan                                            | . 4 |

|------|-------------|---------------------------------------------------------------------------------------------|-----|

| Fig. | 1.2         | Supply voltage $V_{\mathrm{dd}}$ roadmap by ITRS                                            | . 5 |

| Fig. | 1.3         | Classification of $V_{ m th}$ variation                                                     | . 6 |

| Fig. | 1.4         | Trend of $V_{\rm th}$ variation ( $\sigma V_{\rm th}$ ) [1.10]                              | . 7 |

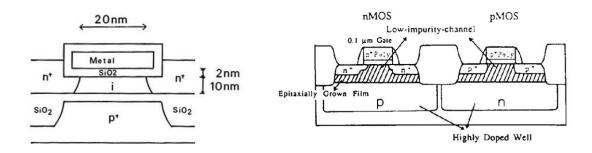

| Fig. | 1.5         | Intrinsic-channel devices [1.12], [1.13]                                                    | . 8 |

| Fig. | 1.6         | Schematic cross section of DELTA [1.14]                                                     | . 9 |

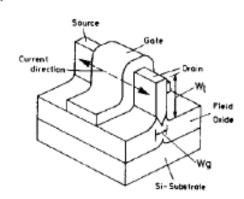

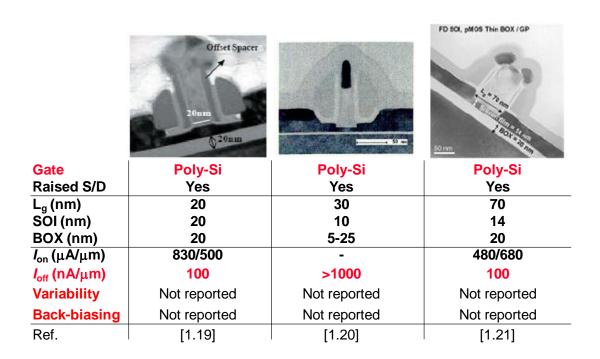

| Fig. | 1.7         | Schematic cross-sectional view of hybrid SOTB/bulk                                          |     |

|      | CMC         | OSFETs [1.18]                                                                               | 10  |

| Fig. | 1.8         | Previous works as for the same structure with SOTB                                          | 11  |

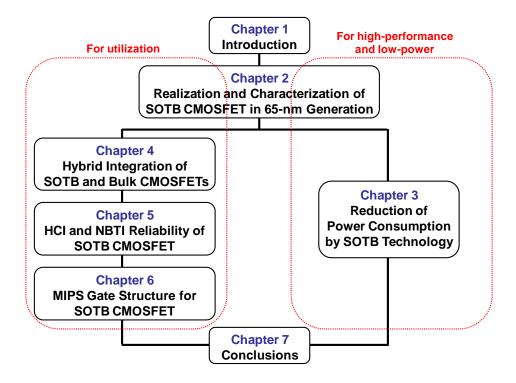

| Fig. | 1.9         | Configuration of this thesis                                                                | 14  |

| Fig. | 2.1         | Process steps of a FUSI-gate SOTB CMOSFET                                                   | 24  |

| Fig. | 2.2         | Relationship between on-current $I_{on}$ and external resistance                            |     |

|      | $R_{ m sd}$ |                                                                                             | 25  |

| Fig. | 2.3         | A cross-sectional TEM image of 50-nm-gate-length SOTB                                       |     |

|      | MOS         | FET                                                                                         | 26  |

| Fig. | 2.4         | Typical $I_{ m d}$ - $V_{ m g}$ characteristics of 50-nm-gate-length SOTB                   |     |

|      | CMC         | SFET                                                                                        | 27  |

| Fig. | 2.5         | Roll-off characteristics of SOTB NMOSFET                                                    | 28  |

| Fig. | 2.6         | Roll-off characteristics of SOTB PMOSFET                                                    | 28  |

| Fig. | 2.7         | $I_{\rm d}$ - $V_{\rm d}$ characteristics of 50-nm-gate-length SOTB CMOSFET.                |     |

|      | No se       | elf-heating is evident due to the thin BOX                                                  | 29  |

| Fig. | 2.8         | $I_{ m on}$ - $I_{ m off}$ characteristics of 50-nm-gate-length SOTB CMOSFET                | 1   |

|      | in co       | mparison with planar bulk CMOSFETs                                                          | 30  |

| Fig. | 2.9         | Dependences of $V_{\mathrm{th}}$ and $SS$ for a 50-nm-gate-length SOTB                      |     |

|      | CMC         | OSFET as a function of back-gate bias $V_{ m bb}$ at $V_{ m dd}$ = 1.2 V                    | 32  |

| Fig. | 2.10        | Dependences of $\mathit{V}_{th}$ and $\mathit{SS}$ for a 50-nm-gate-length SOTB             |     |

|      | CMC         | OSFET as a function of back-gate bias $V_{ m bb}$ at $V_{ m dd}$ = 1.2 V                    | 32  |

| Fig. | 2.11        | $V_{ m th}$ shift and variation reduction of poly-Si gate SOTB NMC                          | S   |

|      | using       | g back-gate bias $V_{ m bb}$ ( $V_{ m bb}$ : -1.2 < $V_{ m bb}$ < 1.2 V, increments = 0.2 V | J)  |

|      |             |                                                                                             | 33  |

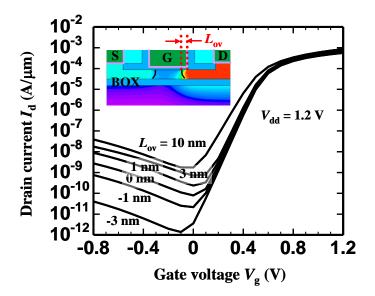

| Fig. | 3.1 Simulated NMOS $I_d - V_g$ characteristics as a function of gate                                            |

|------|-----------------------------------------------------------------------------------------------------------------|

|      | overlap length $L_{\rm ov}$ at $V_{\rm dd}$ = 1.2 V. The inset shows the potential                              |

|      | distribution in SOTB structure at $V_{\rm g}$ = -0.5 V                                                          |

| Fig. | 3.2 Simulated NMOS $I_{ m d}$ – $V_{ m g}$ characteristics as a function of gate                                |

|      | overlap length $L_{\rm ov}$ at $V_{\rm dd}$ = 1.2 V. The inset shows the potential                              |

|      | distribution in SOTB structure at $V_{\rm g}$ = -0.5 V                                                          |

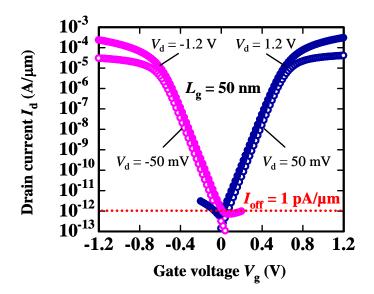

| Fig. | 3.3 $I_{\rm d}$ - $V_{\rm g}$ characteristics of 50-nm-gate-length SOTB CMOS with                               |

|      | controlled $L_{\rm ov}$ . The subthreshold slopes are 79 mV/decade for NMOS                                     |

|      | and 79 mV/decade for PMOS respectively 41                                                                       |

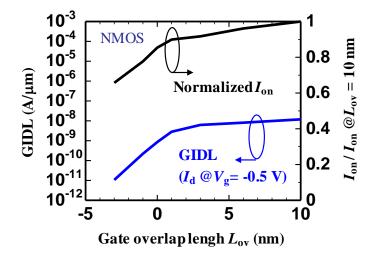

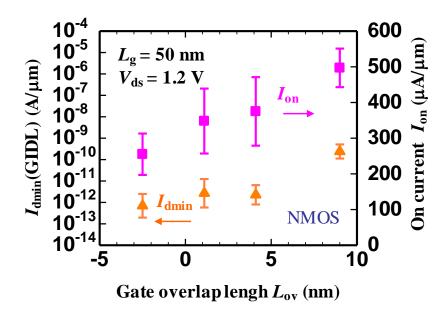

| Fig. | 3.4 Measured dependency of NMOS device performance on $L_{ m ov}$ at                                            |

|      | $L_{ m g}$ = 50 nm, and $V_{ m ds}$ = 1.2 V. GIDL current is expressed as minimum                               |

|      | drain current $I_{ m dmin}$ within the applied gate bias $V_{ m g}$                                             |

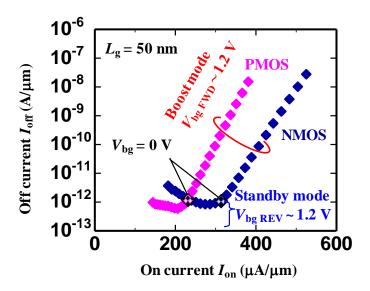

| Fig. | 3.5 Variable transistor performance of 50-nm-gate-length SOTB                                                   |

|      | CMOSFET using back-gate bias $V_{ m bg}$ . $V_{ m bg}$ applied from reverse 1.2 V                               |

|      | to forward 1.2 V, 0.1-V increments at $\mid V_{\rm ds} \mid$ = 1.2 V                                            |

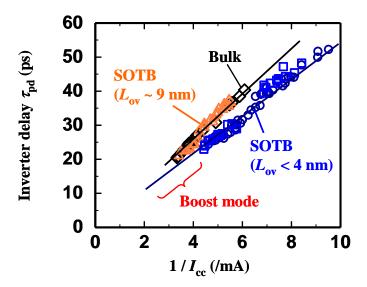

| Fig. | 3.6 Comparison of 61-stages-inverter delay $\tau_{\rm pd}$ between                                              |

|      | conventional bulk CMOSFETs and SOTB CMOSFETs with various $$                                                    |

|      | $L_{\rm ov}$ at $V_{\rm dd}$ = 1.2 V. The $	au_{\rm pd}$ value of an SOTB CMOSFET with $L_{\rm ov}$ of 9        |

|      | nm was slower than the ones of SOTB CMOSFET with $L_{\rm ov}$ < 4 nm,                                           |

|      | and the same as the bulk values despite the increase of on current                                              |

|      | because of high overlap capacitance                                                                             |

| Fig. | 3.7 Demonstration of die-to-die back-gate bias control to adjust                                                |

|      | $I_{ m on}/I_{ m off}$ variation. Forward back-gate bias can be effectively used in                             |

|      | SOTB schemes. 45                                                                                                |

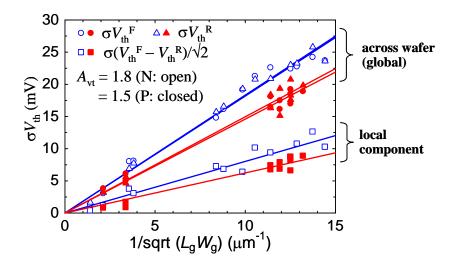

| Fig. | 3.8 Pelgrom plot of SOTB CMOSFETs for both global and local                                                     |

|      | components                                                                                                      |

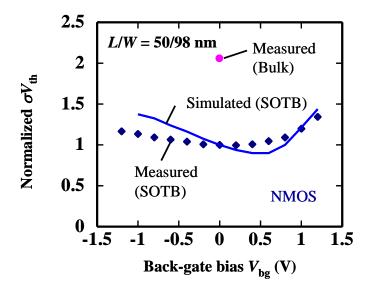

| Fig. | 3.9 $V_{\rm th}$ variation ( $\sigma V_{\rm th}$ ) as function of back-gate bias $V_{\rm bg}$ at $V_{\rm ds}$ = |

|      | 1.2 V. The solid lines are simulated $\sigma V_{th}$ using device simulator 47                                  |

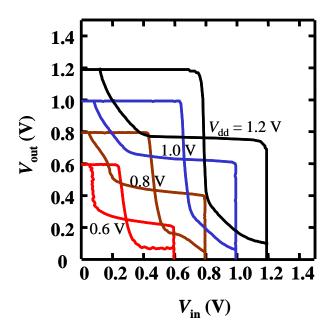

| Fig. | 3.10 Measured butterfly curves of 50-nm-gate-length SOTB SRAM                                                   |

|      | cell                                                                                                            |

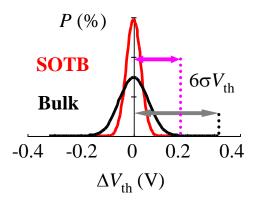

| Fig. | 3.11 Comparison of $V_{\rm th}$ distribution between conventional bulk                                          |

|      | CMOSFETs and SOTB CMOSFETs. The standard deviation ( $\sigma V_{ m th}$ )                                       |

|      | of SOTB devices is half of bulk devices. The range up to 6 $\sigma$ $V_{ m th}$ was                             |

|      | calculated50                                                                                                    |

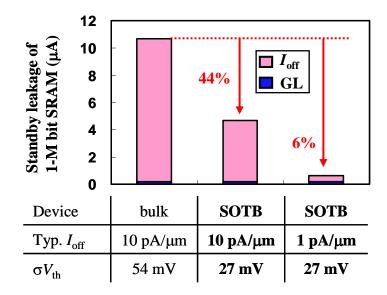

| Fig  | 3.12 Estimated standby leakage of 1-M bit SRAM taking V <sub>b</sub>                                            |

|      | variation into account. Gate leakage (GL) was calculated as                                     |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | constant and gate width was 90 nm 5                                                             | 0  |

| Fig. | 4.1 Process flow of hybrid SOI/bulk fabrication and a                                           |    |

|      | cross-sectional TEM image of poly-Si gate on hybrid SOI/bulk                                    |    |

|      | regions5                                                                                        | 6  |

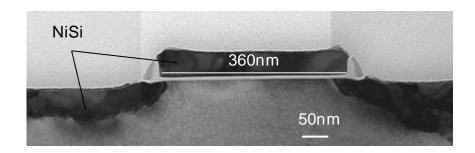

| Fig. | 4.2 A TEM image of a fabricated hybrid bulk MOSFET with a                                       |    |

|      | poly-Si gate5                                                                                   | 7  |

| Fig. | 4.3 A TEM image of a fabricated hybrid bulk MOSFET with a                                       |    |

|      | FUSI gate                                                                                       | 7  |

| Fig. | 4.4 Mobilities of hybrid bulk CMOSFETs for I/O operation 5                                      | 8  |

| Fig. | 4.5 $D_{\rm it}$ values of hybrid bulk MOSFETs 5                                                | 9  |

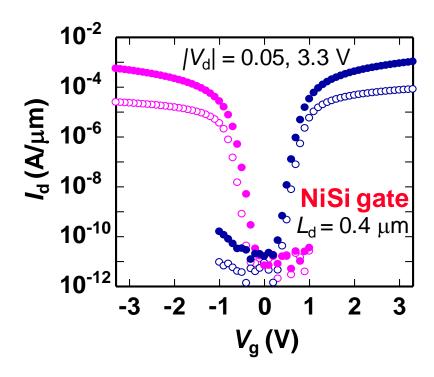

| Fig. | 4.6 $I_{\rm d}$ - $V_{\rm g}$ characteristics of FUSI-gate hybrid bulk CMOSFET 6                | 0  |

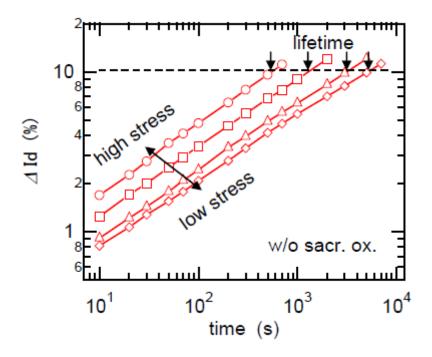

| Fig. | 4.7 HCI characteristics of hybrid bulk NMOS 6                                                   | 1  |

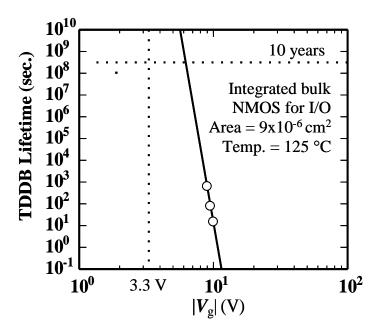

| Fig. | 4.8 TDDB lifetime of hybrid bulk NMOS for I/O operation 6                                       | 2  |

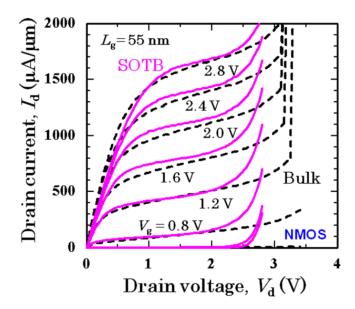

| Fig. | 5.1 Comparison of $I_{\rm d}$ - $V_{\rm d}$ characteristics between SOTB and bulk               |    |

|      | NMOSFETs6                                                                                       | 8  |

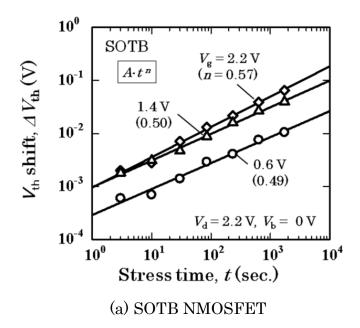

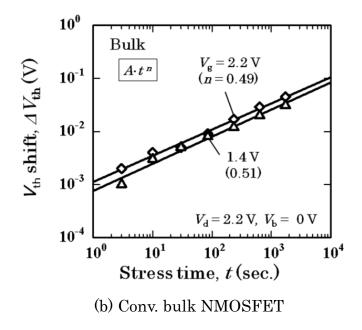

| Fig. | 5.2 Threshold-voltage shift ( $\Delta V_{th}$ ) with dependency on gate bias                    |    |

|      | ( $V_{\rm g}$ ) under HCI stress in (a) SOTB and (b) bulk NMOSFETs 7                            | 0  |

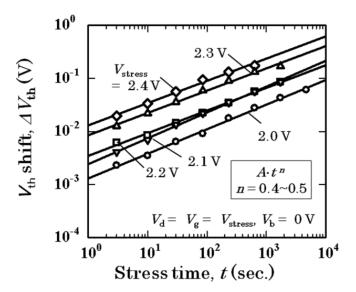

| Fig. | 5.3 Stress bias ( $V_{ m stress}$ ) dependence of HCI degradation in SOTB                       |    |

|      | device                                                                                          | 1  |

| Fig. | 5.4 Comparison of HCI lifetime between SOTB and bulk                                            |    |

|      | NMOSFETs for $V_d = V_g$                                                                        | 2  |

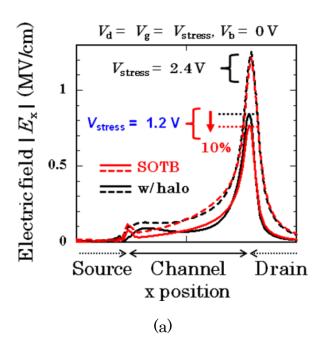

| Fig. | 5.5 (a) Simulated lateral electric-field strengths ( $E_x$ ) along the                          |    |

|      | channel surface in SOTB structures with or without halo implant $\boldsymbol{\epsilon}$         | ıt |

|      | $V_{\rm stress}$ = 2.4 V (dashed) and 1.2 V (solid). (b) Net doping profiles along              | g  |

|      | the channel surface in the $\operatorname{SOTB}$ structures with and without halo               |    |

|      | implant7                                                                                        | 3  |

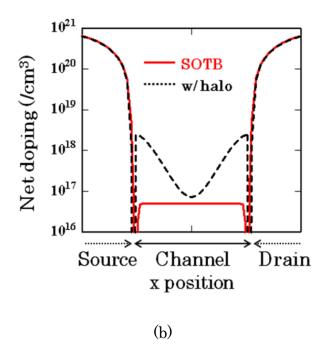

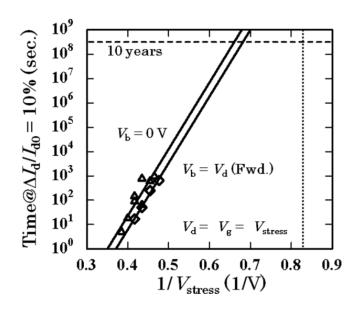

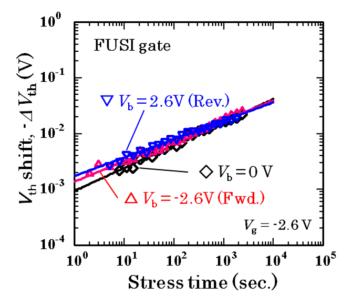

| Fig. | 5.6 Dependency of HCI characteristics on back-bias ( $V_b$ ) at $V_{\rm stress}$                | =  |

|      | 2.4 V                                                                                           | 5  |

| Fig. | 5.7 Simulated vertical electric-field strength $(E_y)$ along the                                |    |

|      | channel surface at forward, reverse, and no back-biasing under HC                               | Ί  |

|      | stress                                                                                          | 5  |

| Fig. | 5.8 HCI lifetime of SOTB NMOSFET under forward back-biasing                                     | ŗ  |

|      | (i.e., worst-case degradation)                                                                  | 6  |

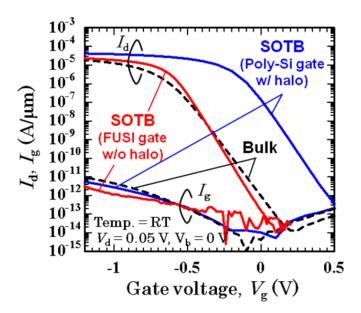

| Fig. | $5.9  I_{ m d},  I_{ m g}$ - $V_{ m g}$ characteristics of poly-Si-gate bulk (high-dose channel | 1  |

|      | with halo), poly-Si-gate SOTB (low-dose channel with halo), and                           |

|------|-------------------------------------------------------------------------------------------|

|      | FUSI-gate SOTB (low-dose channel without halo) PMOSFETs $\dots 77$                        |

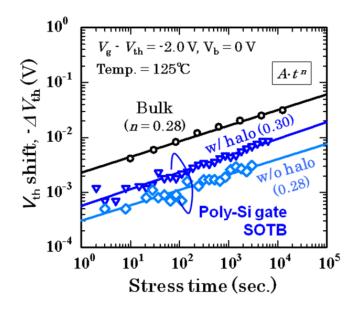

| Fig. | 5.10 Comparison between NBTI characteristics of SOTB and bulk                             |

|      | PMOSFETs                                                                                  |

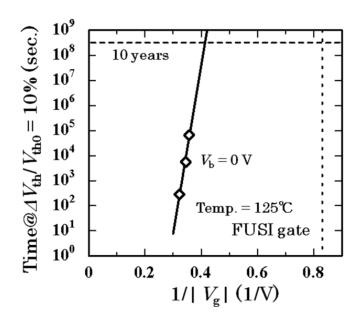

| Fig. | 5.11 NBTI lifetime of SOTB PMOSFET                                                        |

| Fig. | 5.12 Dependency of NBTI characteristics on back-bias ( $V_b$ ) 79                         |

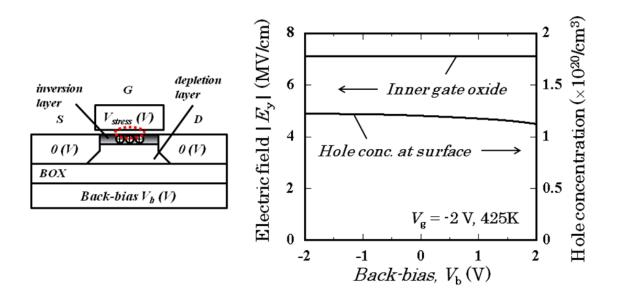

| Fig. | 5.13 Simulated vertical electric-field strength (E <sub>y</sub> ) and hole                |

|      | concentration under the gate as a function of back-bias ( $V_{ m b}$ ) under              |

|      | NBTI stress                                                                               |

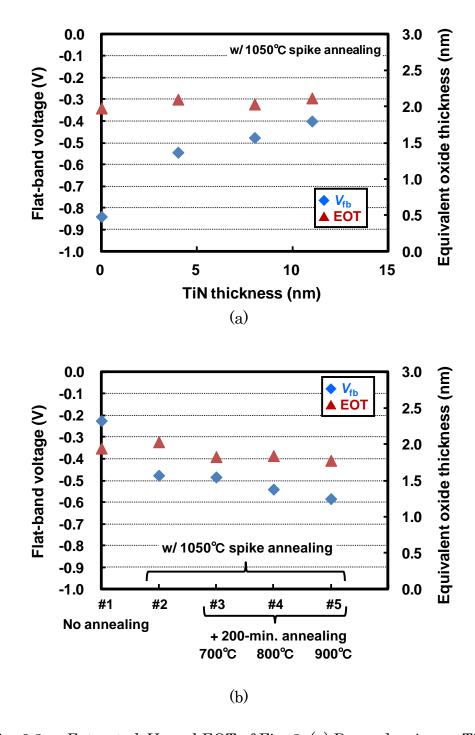

| Fig. | 6.1 C V characteristics of NMOS capacitors with                                           |

|      | poly-Si/TiN/SiON gate stacks. (a) Dependencies on TiN thicknesses                         |

|      | and (b) on thermal loads                                                                  |

| Fig. | Extracted $V_{\rm fb}$ and EOT of Fig. 2. (a) Dependencies on TiN                         |

|      | thicknesses and (b) on thermal loads                                                      |

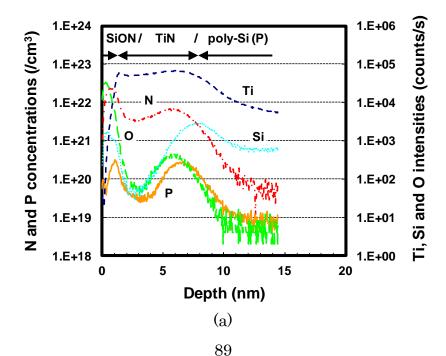

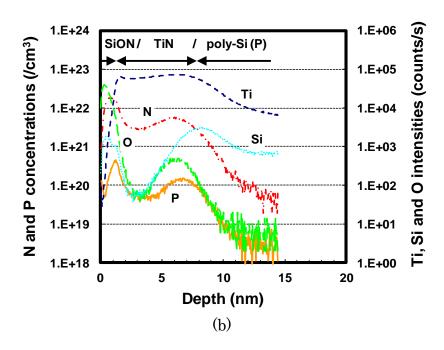

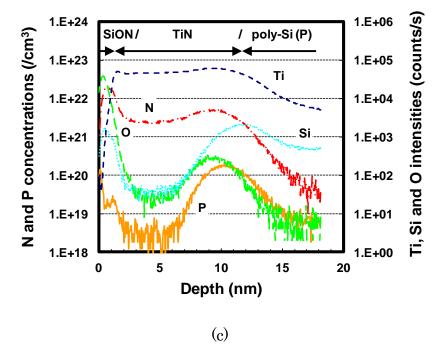

| Fig. | 6.3 Backside secondary ion mass spectrometry (SIMS) profiles. (a)                         |

|      | Poly-Si/TiN (8 nm)/SiON stack with 1050°C spike annealing, (b)                            |

|      | poly-Si/TiN (8 nm)/SiON stack with 1050°C spike annealing and                             |

|      | 900°C 200-min. annealing, and (c) poly-Si/TiN (11 nm)/SiON stack                          |

|      | with 1050°C spike annealing. Note that profiles are drawn from                            |

|      | bottom of gate dielectric film into gate electrode                                        |

| Fig. | 6.4 Cross-sectional transmission-electron-microscope (TEM)                                |

|      | image of TiN-gate SOTB transistor before silicidation. TiN                                |

|      | thickness was 8 nm and gate dielectric was SiON                                           |

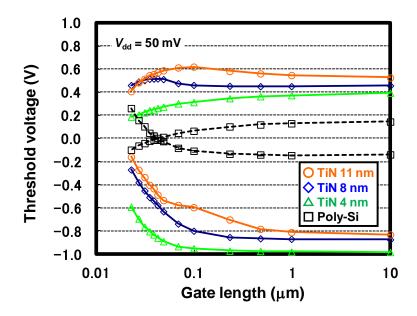

| Fig. | 6.5 Dependency of $V_{\rm th}$ roll-off characteristics on TiN thickness in               |

|      | TiN-gate SOTB CMOSFETs. $V_{\rm th}$ values were extracted by                             |

|      | extrapolating $I_{\rm d}$ - $V_{\rm g}$ curve at $V_{\rm ds}$ = 50 mV. Characteristics of |

|      | poly-Si-gate SOTB devices are also plotted                                                |

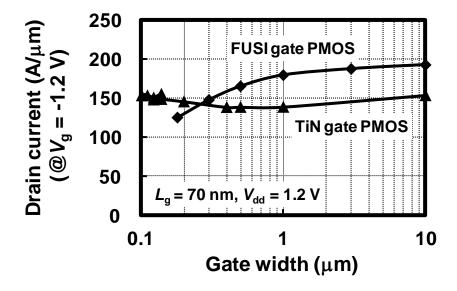

| Fig. | 6.6 Comparison of narrow-channel characteristics between                                  |

|      | TiN-gate and FUSI-gate SOTB PMOSFETs. Gate lengths $(L_{\rm g})$ were                     |

|      | around 70 nm and on-currents ( $I_{\rm on}$ ) were at $V_{\rm dd} = 1.2$ V                |

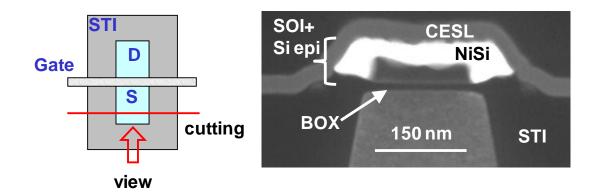

| Fig. | 6.7 TEM image of source/drain region (parallel to gate electrode)                         |

|      | in FUSI-gate SOTB PMOS                                                                    |

| Fig. | 6.8 Schematic cross-sectional view of SOTB structure with                                 |

|      | silicided source/drains. (a) wide channel (b) narrow channel 96                           |

| Fig. | 7.1 Design environment of SOTB technology for large scale                                 |

|      | integ | ration                         | 104 |

|------|-------|--------------------------------|-----|

| Fig. | 7.2   | A standard cell layout of SOTB | 105 |

## Symbols and Abbreviations

$A_{

m Vt}$  Pelgrom coefficient

BOX Buried oxide

BV Breakdown voltage

CHE Channel hot electron

CMOSFET Complementary metal oxide semiconductor field

effect transistor

CVD Chemical vapour deposition

CMP Chemical mechanical polishing

C-V Capacitance-Voltage characteristics

$C_{

m g}$  Gate capacitance  $C_{

m load}$  Load capacitance

DDD Double diffusion drain

DIBL Drain induced barrier lowering

$D_{\mathrm{it}}$  Interface trap density

EDS Energy dispersive X-ray spectroscopy

EOT Equivalent oxide thickness

ESD Electrostatic discharge

EWF Effective work function

$E_{

m g}$  Band gap energy  $E_{

m x}$  Lateral electric field  $E_{

m v}$  Vertical electric field

FBC Fail bit count

FD Fully depleted

FUSI Fully silicided

f frequency

GIDL Gate induced drain leakage

GL Gate leakage  $\gamma$  Back-bias factor

HCI Hot carrier injection

HF Fluoric acid

HTO High temperature oxide

IC Integrated circuit

IEDM International Electron Device Meeting

I/O Input/output

IRPS The International Reliability Physics Symposium

IT Information technology

ITRS International Technology Roadmap for

Semiconductors

$I_{

m cc}$  Through current  $I_{

m d}$  Drain current

$I_{\rm dmin}$  Minimum drain current

$I_{

m g}$  Gate current  $I_{

m gate}$  Gate current  $I_{

m leak}$  Leakage current

$I_{

m on}$  On current  $I_{

m off}$  Off current  $I_{

m s}$  Source current

$I_{

m standby}$  Standby current of 6T-SRAM

$I_{

m sub}$  Substrate current

$J_{\rm g}$  Gate current density

k Scaling factor

LDD Lightly doped drain

LER Line edge roughness

LOCOS Local oxidation of silicon

LPCVD Low Pressure CVD

LSI Large scale integrated circuits

LSTP Low standby power

$L_{

m eff}$  Effective channel length

$L_{\rm g}$  Gate length

$L_{\rm ov}$  Overlap length between gate and extensions

MIPS Metal inserted poly-Si

MOS Metal oxide semiconductor

MOSFET Metal oxide semiconductor field effect transistor

NBTI Negative bias temperature instability

n Number of transistors

n Power law slope

$N_{\! ext{A}}$  Acceptor concentration  $N_{\! ext{channel}}$  Channel impurity density

$N_{\rm D}$  Donor concentration

PD Partially depleted

PVD Physical vapour deposition

$egin{array}{ll} P & ext{Power consumption} \ \phi & ext{Electrostatic potential} \end{array}$

RDF Random dopant flactuation

RIE Reactive ion etching

RTA Rapid thermal annealing

$R_{\rm c}$  Contact resistance

$R_{\rm sd}$  Series source-drain resistance

SCE Short channel effect

S/D Source/drain

SEG Selective epitaxial growth

SEM Scanning electron microscope

SIA Semiconductor industry association SIMS Secondary ion mass spectroscopy

SNM Static noise margin

SoC System on a chip SOI Silicon on insulator SOTB Silicon on thin BOX

**SRAM** Statistic random access memory

STI Shallow trench isolation

SSSubthreshold slope

Time dependent dielectric breakdown **TDDB**

**TED** Transient enhanced diffusion

Transmission electron microscope TEM

**TEOS** Tetraethyl orthosilicate tetraethoxysilane

**BOX** thickness  $T_{\rm BOX}$

Epitaxial layer thickness  $T_{

m epi}$  $T_{\rm OX}$ Gate oxide thickness

SOI thickness  $T_{\rm SOI}$ Delay time  $au_{

m pd}$

Effective mobility  $\mu_{\rm eff}$

**VLSI** Very large scale integration

$V_{

m bb}$ Back-gate bias  $V_{

m bg}$ Back-gate bias  $V_{

m d}$ Drain voltage  $V_{

m dd}$ Supply voltage

$V_{

m ds}$ Drain-source voltage  $V_{

m fb}$ Flat band voltage

$V_{\mathfrak{G}}$ Gate voltage

$V_{\rm gs}$ Gate-source voltage

$V_{

m s}$ Source voltage  $V_{\rm stress}$ Stress voltage  $V_{

m th}$ Threshold voltage

$W_{\rm g}$ Gate width

Junction depth  $X_{j}$

xvii

# Chapter. 1 Introduction – Background and Motive of This Study

## Chapter.1 Introduction – Background and Motive of This Study

#### Contents

- 1.1 MOSFET scaling

- 1.2 Threshold voltage variation issues

- 1.3 Intrinsic-channel MOSFET

- 1.4 SOTB CMOSFET

- 1.5 Purpose of this study

- 1.6 References

#### 1.1 MOSFET scaling

Since the invention of the transistor in 1947, semiconductor industry has continued growing greatly for 60 years and large-scale-integrated circuits (LSIs) have made big changes to our life. It is now possible to realize a large-scale circuit by integrating over billion transistors on one chip. Continuation of these advances, at the pace dictated by Moore's Law in which the number of transistors on a chip will double roughly every year (a decade later, revised to every 2 years) [1.1], has been towed by downsizing Complementary Metal-Oxide-Semiconductor Field-Effect Transistor (CMOSFET).

This scaling rule of MOSFET as shown in Table 1.1 was proposed by Dennard [1.2]. According to this rule, the device parameters should be shrunk by the factor k. As a result, the internal electric field of MOSFETs remains constant regardless of the generation. This means the downsizing of MOSFETs can be realized without changing the device structure. Therefore the ideal scaling brings easily high integration and high performance of LSIs.

Table 1.1 The scaling rule [1.2]

| Device parameter                              |             |

|-----------------------------------------------|-------------|

| Feature size                                  |             |

| channel length, $L_{\mathrm{g}}$              | 1/ <i>k</i> |

| channel width, $W_{ m g}$                     | 1/ <i>k</i> |

| junction depth, $x_j$                         | 1/ <i>k</i> |

| gate oxide thickness, $T_{ m ox}$             | 1/ <i>k</i> |

| Channel dopant concentration, $N_A$ , $N_D$ k |             |

| Supply voltage, $V_{\rm dd}$ 1/A              |             |

However, the actual scaling of the device parameters has diverged somewhat from the ideal one. For example, the supply voltage was not reduced in the early phase of LSI generations so as to preserve compatibility with the supply voltage of conventional systems. This increased the internal electric field of the MOSFET and caused reliability problems such as hot carrier effect. To conquer this problem, the device structure with high breakdown voltage, such as double diffused drain (DDD) or lightly doped drain (LDD), has been developed [1.3]. As this example suggested, it could be concluded that various practical restrictions, which were not taken in consideration in the scaling rule, have caused subjects in device development.

#### 1.2 Threshold voltage variation issues

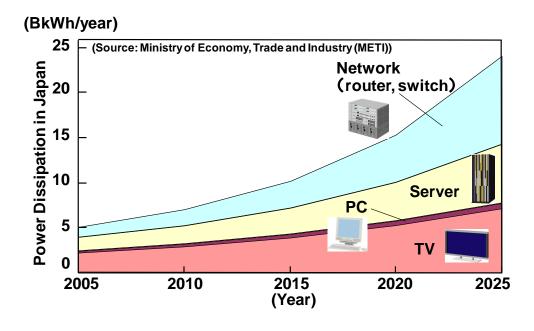

Today's our world is greedy for power. Social system is controlled by information technology (IT). Everything is connected by network and enormous information is computed at any time. Figure 1.1 shows the power dissipation trend of IT equipment in Japan. The power consumption might reach 24 billion kWh / year by 2025. This is the five times higher than the power consumed in 2005. To overcome the power crisis, "green IT" has been proposed. The "green IT" means a energy-saving of IT itself and a energy-saving of social system by IT. LSI technology can make great contribution to the sustainable and innovative society.

Fig. 1.1 Power dissipation trend of IT equipment in Japan

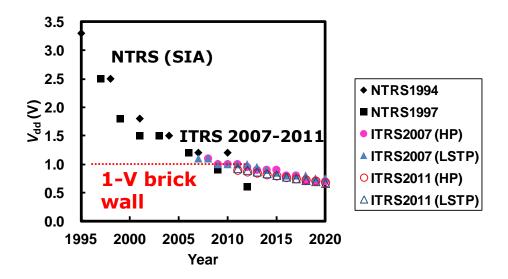

The scaling rule has been a paradigm for downsizing CMOSFETs in LSI circuits for a long period. In the ideal scaling rule, the supply voltage  $V_{\rm dd}$  should decrease in proportion to the downsizing of the transistor. In extremely scaled transistors such as those in the 45-nm logic node and beyond, however, it is very difficult to further decrease  $V_{\rm dd}$ . In the ITRS roadmap, the rate of  $V_{\rm dd}$  reduction below 1 V is forecasted to be extremely small as shown in Fig. 1.2. This problem is called as "1-V brick wall". Unless  $V_{\rm dd}$  is reduced with the scaling rule, the power consumption of the LSI will increase significantly due to an increase in both operational and standby-leakage power [1.4], [1.5].

Fig. 1.2 Supply voltage  $V_{\rm dd}$  roadmap by ITRS

The primary cause of this difficulty is widely recognized as the increase in threshold voltage ( $V_{\rm th}$ ) variation of CMOSFETs, because  $V_{\rm dd}$  should be set higher considering the margin to the increased  $V_{\rm th}$  variation [1.6]. Variation of transistor characteristics, primarily  $V_{\rm th}$  variation, is increasing substantially in sub-100-nm technologies. This makes the  $V_{\rm dd}$  reduction, required by the scaling rule, difficult, and significantly increases the power consumption of an LSI chip. Here, power consumption P of an inverter,

which is the representative unit of LSI circuit, is defined as

$$P = CV_{\rm dd}^2 f + I_{\rm leak} V_{\rm dd} \tag{1.1}$$

where C, f, and  $I_{\text{leak}}$  are load capacitance, operation frequency, and leakage current, respectively. The first and second terms on the right-hand side represent operational and standby power, respectively. As the scaling proceeds, C and  $I_{\text{leak}}$  decrease due to the size reduction of transistors, and f increases for higher performance. Since the miniaturization enables the number of circuits crammed onto a single chip to increase exponentially, it is extremely important to lower  $V_{\text{dd}}$  to maintain power consumption of an LSI chip [1.7].

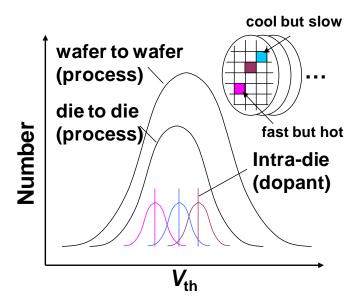

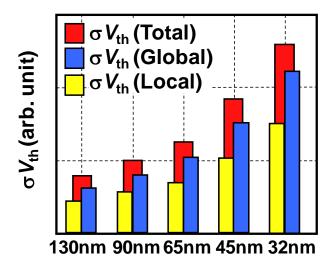

Figure 1.3 shows a classification of  $V_{\rm th}$  variation. The origin of the  $V_{\rm th}$  variation is not only due to lithographic variations and layer thicknesses, but also due to line edge roughness (LER) and random dopant fluctuation (RDF) [1.8], [1.9]. In particular, it has been pointed out that the  $V_{\rm th}$  variation caused by the number and spacial distribution of impurities in the channel of transistors (RDF) becomes serious with the scaling as shown in Fig. 1.4 [1.10]. The magnitude of the  $V_{\rm th}$  variation is described by standard deviation  $\sigma V_{\rm th}$ , since the distribution of  $V_{\rm th}$  usually shows a normal distribution.

Fig. 1.3 Classification of  $V_{\rm th}$  variation

Fig. 1.4 Trend of  $V_{\text{th}}$  variation ( $\sigma V_{\text{th}}$ ) [1.10]

The  $V_{\text{th}}$  variation becomes small with the wider area of the gate because the impurity distribution should be random. This relationship is well known [1.11] and is defined as

$$\sigma V_{\rm th} = A_{\rm Vt} / (L_{\rm g} W_{\rm g})^{1/2}$$

(1. 2)

where  $L_g$  and  $W_g$  are the length and width of a gate, and the gradient  $A_{Vt}$  is called the Pelgrom coefficient. Moreover, in conventional bulk CMOSFETs, the following relationship exists

$$A_{\rm Vt} \propto T_{\rm ox} (N_{channel})^{1/4}$$

(1.3)

where  $T_{\text{ox}}$  and  $N_{\text{channel}}$  are the thickness of a gate oxide and a channel impurity density. Hence, the following relationship is drawn

$$\sigma V_{\rm th} \propto T_{\rm ox} (N_{channe})^{1/4} / (L_{\rm g} W_{\rm g})^{1/2} \propto k^{1/4}$$

(1.4)

where k is the scaling factor. Because  $N_{\text{channel}}$  has increased to suppress the

short channel effect (SCE), the  $V_{th}$  variation increases with scaling inherently. Thus, it is understood that the present  $V_{th}$  variation problem is inevitably caused by the conventional bulk CMOSFETs' miniaturization.

#### 1.3 Intrinsic-channel MOSFET

To solve these problems, it is necessary to first decrease the  $V_{\rm th}$  variation due to size variations by suppressing SCE, and secondly to decrease RDF by lowering the impurity densities of the channel. However, intrinsic or low-dose channel devices must have some sort of countermeasure against SCE.

Fukuma proposed an intrinsic-channel MOSFET in 1988 [1.12]. The MOSFET (Fig. 1.5 left-hand side) has a thin channel and a p+ substrate under the channel through SiO<sub>2</sub> layer to prevent punch through. However, the device was just proposed and had no way to fabricate, for example, a very thin channel on the SiO<sub>2</sub> layer. A device with a 0.1-μm gate length as shown on the right-hand side in Fig. 1.5 was fabricated by using an epitaxial growth technology in 1990 [1.13]. For sub-100-nm technology node, however, a thinner epitaxial channel and dopant diffusion from the well under the channel by annealing become critical issue.

Fig. 1.5 Intrinsic-channel devices [1.12], [1.13]

Fully-depleted (FD) MOSFETs have strong immunity from SCE without increasing the impurity density of the channel because of their structures. By using commercially available silicon-on-insulator (SOI) wafers, FD-SOI

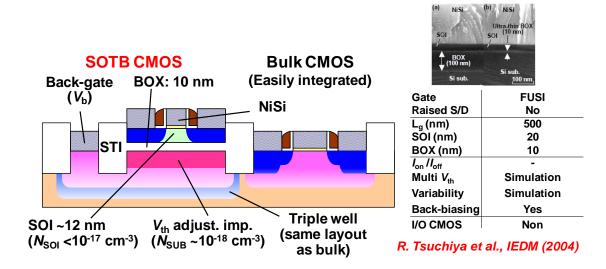

MOSFETs can be easily fabricated. Conventional SOI wafers are consisted of thick (above 100 nm) buried oxide (BOX) and SOI layers. The thickness of the SOI layer can be thinned by thermal oxidation and wet-etching. Another FD MOSFET is so called FinFET, which originally proposed as fully depleted lean-channel transistor (DELTA) by Hisamoto et al. in 1989 [1.14], as shown in Fig. 1.6. The three-dimensional gate structure is so effective against SCE. The effectiveness of these structures for  $V_{\rm th}$  variation was reported in sub-100-nm node [1.15]. Detail comparisons with SOTB CMOSFET will be discussed in chapter 7.

Fig. 1.6 Schematic cross section of DELTA [1.14]

On the other hand, these FD devices have some inherent issues. To continue to both improve the speed and reduce the power from the system-LSI designer's viewpoint, it is necessary to set  $V_{\rm th}$  and  $V_{\rm dd}$  to the best value in every circuit block or set of transistors in LSI circuits. The multiple  $V_{\rm th}$  design, such as that with two or three kinds of  $V_{\rm th}$  setting, is already indispensable. In conventional bulk CMOSFETs, the multiple  $V_{\rm th}$  design can be easily obtained by adjusting the impurity density of the channel. The FD devices with intrinsic channels cannot use this way.

Additionally, a technique that controls  $V_{\rm dd}$  adaptively according to the state of operation has also been applied [1.16]. A technique to apply substrate bias  $V_{\rm bb}$  to control  $V_{\rm th}$  flexibly is used in some applications, also [1.17]. This  $V_{\rm bb}$  control technique is a strong tool that can minimize the performance deviation due to temperature fluctuation as well as the variation of each chip.

Even in present scaled bulk CMOSFETs, it is difficult to apply  $V_{bb}$  because of the increase in the junction leakage current between the source/drain (S/D) and the substrate. In FD devices, the thick BOX layer or the vertical channel structure block the  $V_{bb}$  influence.

#### 1.4 SOTB CMOSFET

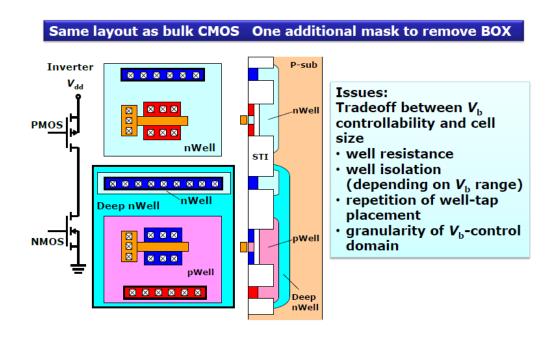

To solve the  $V_{\rm th}$  variation problem due to RDF and satisfy the demand from circuit designers, Tsuchiya et al. proposed silicon-on-thin-BOX (SOTB) CMOSFET [1.18]. Figure 1.7 shows a schematic cross-section of the SOTB structure. Ultrathin SOI and BOX layers make the transistor highly immune from SCE, and its intrinsic channel without halo implant suppresses the  $V_{\rm th}$  variation due to RDF. The thin BOX and impurity doping in the substrate just beneath the thin BOX enables a multiple  $V_{\rm th}$  design. This thin BOX and the doped region also enable the wide-range back-gate controllability which realizes optimization of both performance and power after fabrication. Furthermore, conventional bulk CMOSFET can be easily co-integrated by just removing the thin SOI and BOX layers.

Fig. 1.7 Schematic cross-sectional view of hybrid SOTB/bulk CMOSFETs [1.18]

After Tsuchiya proposed this concept, several groups reported the results of the same structure in sub-100-nm generations [1.19]-[1.21]. Their features are summarized in Fig. 1.8. Though they all have small raised S/D structure for obtaining low external S/D resistance ( $R_{\rm sd}$ ), their off-current ( $I_{\rm off}$ ) values are too large for low-standby power (LSTP) applications due to their low  $V_{\rm th}$  of the conventional poly-Si gates. Moreover, the special features of the SOTB structure such as low variability or back-biasing were not reported.

Fig. 1.8 Previous works as for the same structure with SOTB

#### 1.5 Purpose of this study

Although the scaling of planar bulk MOSFET has continued so far, the end is impending. This is because the power consumption of LSIs is significantly increasing due to  $V_{\rm th}$  variation issues as described in section 1.2. FD-SOI CMOSFETs or FinFETs are one of the most promising candidates for the issues because of their low-dose channel and high immunity from SCE.

However, they have some inherent problems, such as multi  $V_{\text{th}}$  design or back-biasing, as described in section 1.3.

The studies described in this thesis were accomplished in order to realize SOTB CMOSFET as a solution for the above stated problems, and thereby contributing to the realization of high performance and low power LSIs in the future generations. In order to sublimate SOTB from one of many candidates to the legitimate successor of the bulk planar CMOS, many problems need to be solved.

The studies of this thesis are classified roughly in two parts. Firstly, it is mentioned about the actual proof of superiority of SOTB CMOSFET to the conventional planar bulk CMOSFETs. For straight comparison with the bulk CMOSFETs, processes of SOTB CMOSFET needed to be developed in the 65-nm generation which was the latest node of those days. The characteristics of SOTB CMOSFET also needed to be examined in comparison with the ones of bulk CMOSFETs.

Another issue is solving the subjects for utilization. In order to put SOTB in practical use, it is very important that there is no inferior point to the conventional bulk CMOSFETs. However, there are following three subjects for the utilization of SOTB. The first subject is an integration of the transistor for high-voltage operation. In recent system on a chip (SoC), many functions are required to the one chip and the transistors for input/output (I/O) or analog applications are usually integrated with core transistors. The second subject is reliability issues such as hot carrier injection (HCI) and negative bias temperature instability (NBTI). The reliability of the conventional FD-SOI CMOSFETs in the advanced technology node has not been fully studied. In addition, the wide-range back-biasing of SOTB CMOSFET will be expected to influence the reliability. Lastly, the third subject is the ease of manufacturing. Though a fully-silicided (FUSI) gate process applied in SOTB fabrication for LSTP requirements is easy and simple, but the precise control of the manufacture variation is to be expected difficult especially for large scale integration. In the late 2000s, the mainstream of the gate structure to be studied had moved to the metal-inserted poly-Si (MIPS) gate structure. It is necessary to optimize the gate stack in order to applying for SOTB CMOSFET. These subjects described above are summarized in Table 1.2.

Table 1.2 Subjects studied in this thesis

| Subjects                                   | Targets                                                                                                                                                                                                             | Approaches                                                                                                                                                                                                                                  |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Realizing SOTB CMOSFET in 65-nm generation | $\cdot L_{\rm g}$ = 50 nm<br>•Desirable and multi $V_{\rm th}$ for LSTP<br>•Comparable $I_{\rm on}/I_{\rm off}$<br>•Less $V_{\rm th}$ variation<br>•Characterization of back-biasing                                | •Combine FUSI gate and high raised S/D •Adjust the dopant concentration of the substrate beneath the BOX •Suppress SCE and RDF by FD-SOI structure with low-dose channel •Propose a way of back-biasing                                     |

| Reduction of power consumption             | $ \begin{array}{c} \cdot \text{Ultralow off-current} \\ \cdot \text{Comparable inverter delay} \\ \cdot \text{Reduction of standby power} \\ \cdot \text{Reduction of } V_{\text{dd}} \text{ in SRAM} \end{array} $ | $ \begin{split} &\cdot \text{GIDL reduction by controlling } L_{\text{ov}} \\ &\cdot \text{Boosted performance in the case of ultralow } I_{\text{off}} \\ &\cdot \text{Ultralow } I_{\text{off}} \text{ and low variability} \end{split} $ |

| CMOSFETs for I/O operation                 | ·Comparable characteristics to<br>conventional bulk I/O CMOSFETs                                                                                                                                                    | ·Hybrid integration ·Investigate the quality of the exposed surface                                                                                                                                                                         |

| HCI and NBTI reliability                   | •Comparable lifetime to conventional<br>bulk CMOSFETs<br>•Clarify the mechanism                                                                                                                                     | •Analsis of the electric fields in SOTB<br>by using 2D simulator<br>•Investigate the influence of back-biasing                                                                                                                              |

| MIPS gate for SOTB                         | $ \begin{array}{c} \cdot \text{Desirable} \ V_{\text{th}} \ \text{for LSTP} \\ \cdot \text{Non-degraded narrow channel} \\ \text{characteristics} \end{array} $                                                     | •SiON/TiN/poly-Si gate •Less silicidation process                                                                                                                                                                                           |

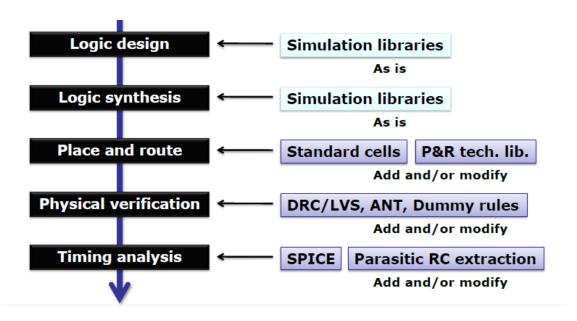

Figure 1.9 shows the configuration of this thesis. Chapter 2 covers the studies undertaken to develop the SOTB CMOSFET in 65-nm generation and examine the characteristics. The studies of reduction of the power consumption by using SOTB technology are covered in chapter 3. Chapter 4 covers the hybrid integration of SOTB and bulk CMOSFETs. Chapter 5 covers the analysis of HCI and NBTI of SOTB CMOSFET. Chapter 6 covers the studies of MIPS gate stacks for SOTB CMOSFET. The studies referred to in each chapter were done in order to achieve SOTB CMOSFET with high performance, low power consumption, and high reliability for future generation. Details are as follows.

Fig. 1.9 Configuration of this thesis

## a) Realization and characterization of SOTB CMOSFET in 65-nm generation (Chapter 2)

In FD-SOI devices for 65-nm generation, an ultrathin SOI layer below 15-nm is required to suppress SCE. The thin SOI layer makes increase in parasitic S/D resistance  $R_{\rm sd}$ . A raised S/D structure by selective epitaxial growth (SEG) has been adopted for obtaining low  $R_{\rm sd}$ . The structure needs to be optimized for SOTB CMOSFET. Another main issue for FD-SOI devices is to control the  $V_{\rm th}$  value. The intrinsic channels of the FD-SOI devices require suitable metal gate technology. However, it usually increases process complexity.

Though some results of the SOTB structure in sub-100-nm generation had been shown from other groups, important concerns about this structure such as the  $V_{\rm th}$  control including multi  $V_{\rm th}$  design, variability, and back-biasing had not been reported. In chapter 2, a novel process to realize SOTB CMOSFET for LSTP specifications is presented with solving the many

trade-offs. The simple process makes a FUSI gate for desirable  $V_{\rm th}$  and relatively thick raised S/D for low  $R_{\rm sd}$  simultaneously. The superior characteristics of the fabricated SOTB CMOSFET to conventional bulk CMOSFETs in the same generation are shown. In addition, the special features such as low  $V_{\rm th}$  variation and wide-range back-biasing are demonstrated for the first time.

#### b) Reduction of power consumption by using SOTB technology (Chapter 3)

It was very difficult to decrease  $V_{\rm dd}$  in those days due to the increasing  $V_{\rm th}$  variation. And it has been continuing until now. Unless  $V_{\rm dd}$  is reduced with scaling, the power consumption of the LSI will significantly increase due to an increase in both operational and standby leakage power. Though FD-SOI devices were expected to be able to help the problem, there were few reports about the variability and power reduction at that time.

In chapter 3, studies of reduction of the power consumption by using SOTB technology are discussed. It is shown that how the low  $V_{\rm th}$  variation of the SOTB CMOSFET impacts on the reduction of the supply voltage. An ultralow off-current (1 pA/ $\mu$ m) SOTB CMOSFET was developed for reducing the standby power. It is demonstrated that the wide-range back-biasing is effective for the high performance in the case of the ultralow off-current devices. It is also presented that how much the standby power of the 6T-SRAM, as a representative unit in LSI circuits, can be reduced by SOTB technology.

#### c) Hybrid integration of SOTB and bulk CMOSFETs (Chapter 4)

One of inherent problem of FD-SOI devices is its low breakdown voltage. In conventional SoC, however, high-voltage transistors are usually integrated for I/O operation. A simple answer to this issue in FD-SOI devices is to integrate bulk transistors with the FD-SOI platform. A previous approach was such that the thick BOX layer was removed by dry-etching and a Si layer by SEG was used to compensate the height difference [1.22].

In chapter 4, novel hybrid integration is presented. The height difference between the core and I/O regions is kept small due to the ultrathin SOI and BOX layers of SOTB CMOSFET. Therefore, the devices for core and I/O operations can be fabricated simultaneously. The characteristics of the I/O devices are shown to be comparable to conventional I/O devices. In addition, the reliability of the exposed surface of the Si substrate is thoroughly investigated.

#### d) HCI and NBTI reliability of SOTB CMOSFET (Chapter 5)

The reliability of FD-SOI CMOSFETs in sub-100-nm generations has not been fully investigated. For SOTB CMOSFET, moreover, its wide-range back-biasing is expected to have much influence the reliability because the back-biasing modulates the electric fields and carriers in the device.

In chapter 5, the HCI and NBTI reliability of SOTB CMOSFET is examined for the first time. The characteristics are analyzed in comparison with conventional bulk CMOSFETs. The difference of electric fields between SOTB and conventional bulk CMOSFETs are also analyzed by using 2D device simulator. In addition, the mechanisms including the effects of back-biasing are discussed in detail.

#### e) MIPS gate structure for SOTB CMOSFET (Chapter 6)

There is a concern regarding the mass production of SOTB with FUSI gate because the phase and the thickness of NiSi are hard to be controlled precisely. On the other hand, MIPS gate structures were widely studied in combination with high-κ gate dielectrics in the late 2000s. For LSTP applications of 65-nm generation, however, the high-κ gate dielectric is not required intensely because the EOT is around 2 nm.

In chapter 6, a reliable MIPS gate structure using conventional SiON gate dielectric for SOTB CMOSFET is presented. It was found that the characteristics of the FUSI gate SOTB CMOSFET degraded in the narrow channel due to the excess silicidation. The configuration of the MIPS gate stack is studied to obtain the desirable  $V_{\rm th}$  with considering the processes of SOTB CMOSFET. It is also shown that the superior narrow channel characteristics of the MIPS gate SOTB CMOSFET.

Finally, the results obtained in these studies are summarized and conclusions are presented in chapter 7. In addition, the importance of SOTB CMOSFET for future LSIs is discussed with comparing the other technology such as FinFETs.

#### 1.6 References

- [1.1] G. E. Moore, "Progress in Digital Integrated Electronics" IEDM Tech. Dig. pp. 11, 1975.

- [1.2] R. H. Dennard et al., "Design of Ion-Implanted MOSFETs with Very Small Physical Dimensions" IEEE J. Solid-State Circuits, vol. SC-9, pp. 256-268, 1974.

- [1.3] E. Takeda et al., "Submicron MOSFET Structure for Minimizing Channel Hot-Electron Injection" Proceedings of VLSI technology symp., pp. 22-23, 1981.

- [1.4] T. Sakurai, "Perspectives of low-power VLSI's" IEICE Trans. Electron., E87-C, pp. 429-436, 2004.

- [1.5] T. C. Chen, "Where CMOS is going: trendy hype vs. real technology" Plenary of ISSCC, pp. 1-18, 2006.

- [1.6] K. Takeuchi et al., "Channel Engineering for the Reduction of Random-Dopant-Placement-Induced Threshold Voltage Fluctuation" Tech. Dig. Int. Electron Devices Meet., pp. 841-844, 1997.

- [1.7] G. E. Moore, "Are We Really Ready for VLSI?" Keynote Address of ISSCC, pp. 54-55, 1979.

- [1.8] A. Asenov et al., "Intrinsic parameter fluctuations in decananometer MOSFETs introduced by gate line edge roughness" IEEE Trans Electron Devices, 50, pp. 1254-1260, 2003.

- [1.9] T. Mizuno et al., "Experimental study of threshold voltage fluctuation due to statistical variation of channel dopant number in MOSFET's" IEEE Trans Electron Devices, 41, pp. 2216-2221, 1994.

- [1.10] M. Yamaoka et al., "Low Power SRAM Menu for SoC Application Using Yin-Yang-Feedback Memory Cell Technology" Proceedings of VLSI

- circuits symp., pp. 288-289, 2004.

- [1.11] M. J. M. Pelgrom et al., "Matching properties of MOS transistors" IEEE J. Solid-State Circuits, 24, pp. 1433-1439, 1989.

- [1.12] M. Fukuma, "Limitations on MOS ULSIs" Proceedings of VLSI technology symp., pp. 7-8, 1988.

- [1.13] M. Aoki et al., "0.1 µm CMOS Devices Using Low-Impurity-Channel Transistors (LICT)" Tech. Dig. Int. Electron Devices Meet., pp. 939-941, 1990.

- [1.14] D. Hisamoto et al., "A Fully Depleted Lean-channel Transistor (DELTA) -- A novel vertical ultra thin SOI MOSFET --" Tech. Dig. Int. Electron Devices Meet., pp. 833-836, 1989.

- [1.15] A. Thean et al., "Performance and Variability Comparisons between Multi-Gate FETs and Planar SOI Transistors" Tech. Dig. Int. Electron Devices Meet., pp. 881-884, 2006.

- [1.16] M. Nakai et al., "Dynamic voltage and frequency management for a low-power embedded microprocessor" IEEE J. Solid-State Circuits, 40, pp. 28-35, 2005.

- [1.17] M. Miyazaki et al., "A 1000-MIPS/W microprocessor using speed adaptive threshold-voltage CMOS with forward bias" Dig. Tech. Papers IEEE Int. Solid-State Circuits Conf., pp. 420-421, 2000.

- [1.18] R. Tsuchiya et al., "Silicon on thin BOX: a new paradigm of the CMOSFET for low-power and high-performance application featuring wide-range back-bias control" Tech. Dig. Int. Electron Devices Meet., pp. 631-634, 2004.

- [1.19] H.-Y. Chen et al., "Novel 20nm Hybrid SOI/Bulk CMOS Technology with 0.183 µm<sup>2</sup> 6T-SRAM Cell by Immersion Lithography" in Dig. VLSI Technol., pp. 16-17, Jun. 2005.

- [1.20] M. Fujiwara et al., "Impact of BOX Scaling on 30 nm Gate Length FD SOI MOSFETs" in Proc. IEEE International SOI Conf., pp. 180-182, Oct. 2005.

- [1.21] C. Gallon et al., "Ultra-Thin Fully Depleted SOI Devices with Thin BOX, Ground Plane and Strained Liner Booster" in Proc. IEEE International SOI Conf., pp. 17-18, 2006.

[1.22] M. Yang et al., "High Performance CMOS Fabricated on Hybrid Substrate with Different Crystal Orientations" Tech. Dig. Int. Electron Devices Meet., pp. 453-456, 2003.

# Chapter. 2 Realization and Characterization of SOTB CMOSFET in 65-nm generation

#### Abstract

SOTB CMOSFET for the target specification of 65-nm LSTP was firstly realized. A simple simultaneous silicide process for FUSI gate with relatively thick raised S/D was developed. This makes the gate fully silicided and prevents the excess silicidation in the S/D region at the same time. The characteristics such as the desirable multi  $V_{\rm th}$ , SCE, and  $I_{\rm on}/I_{\rm off}$  were studied. And they are shown to be superior in comparison with conventional bulk CMOSFETs. It was also demonstrated for the first time that the wide-range back-biasing of SOTB CMOSFET could optimize device performance and reduce in  $V_{\rm th}$  variation after device fabrication.

## Chapter.2 Realization and Characterization of SOTB CMOSFET in 65-nm generation

#### Contents

- 2.1 Introduction

- 2.2 Fabrication of SOTB CMOSFET

- 2.3 DC characteristics of SOTB CMOSFET for 1.2-V operation

- 2.4 Wide-range back-biasing of SOTB CMOSFET

- 2.5 Conclusion

- 2.6 References

#### 2.1 Introduction

FD-SOI devices have excellent characteristics, such as high SCE immunity, low subthreshold swing (SS), small junction capacitance and small floating body effect compared to bulk or partially-depleted (PD) SOI devices [2.1]. On the other hand, the threshold voltage needs to be controlled by the work function of the gate material. In addition, for sub-100-nm generations, parasitic source/drain (S/D) resistances (R<sub>sd</sub>) become a serious problem because of the ultrathin SOI layer, which is usually less than 25 nm.

After Tsuchiya proposed the concept of SOTB structure [2.2], several groups reported the results of the same structure in sub-100-nm generations [2.3]-[2.5]. They adopted thin SOI layer for SCE and raised S/D structure for low  $R_{\rm sd}$ . However, their  $V_{\rm th}$  values are too low for LSTP applications in their conventional poly-Si gates because there are few depletion layer charges in FD-SOI devices with low-dose channels. Metal gates with work function close to midgap, such as nickel silicide (NiSi), are suitable for the desirable  $V_{\rm th}$  values in FD-SOI devices [2.6]. However, a previous approach, in which the S/D and the gate are silicided separately by using a chemical mechanical polishing (CMP) technology, increases process complexity significantly [2.7].

In this chapter, a simple FUSI gate process without CMP for fabricating SOTB CMOSFET in 65-nm generation is presented. In this process, the gate and the raised S/D are silicided simultaneously by adjusting the heights of the gate and the raised S/D. The characteristics (SCE,  $V_{\rm th}$ ,  $I_{\rm on}/I_{\rm off}$ , and variability) of the fabricated SOTB CMOSFET are thoroughly investigated for the target specification. Moreover, the special feature of SOTB technology, that is, wide-range back-biasing, is demonstrated for the first time.

#### 2.2 Fabrication of SOTB CMOSFET

There are three key processes of fabricating SOTB devices. Firstly, one drawback of FD-SOI structure is the high parasitic series resistance of thin SOI layer. Elevated source/drain structure by using selective epitaxial growth (SEG) was adopted to reduce the parasitic resistance. Secondly, conventional poly- Si gate devices with lightly doped channel cannot be used

for LSTP applications, since their standby current is too large due to their low  $V_{\rm th}$ . In FD-SOI devices, one can obtain the desirable  $V_{\rm th}$  value for LSTP by using a single midgap metal both for NMOS and PMOS. In this chapter, NiSi was adopted as a gate metal. A metal-inserted poly-Si (MIPS) gate structure can also be adopted, which described in chapter 6. Moreover, a hybrid process in which bulk I/O devices are integrated with SOTB devices is indispensable for SoC architecture. It is described in chapter 4.

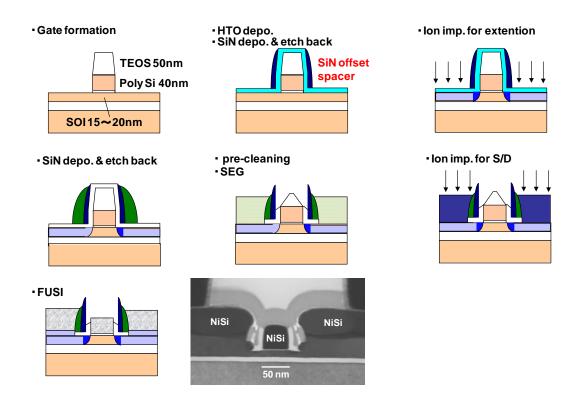

Figure 2.1 shows the process steps of a SOTB CMOSFET in 65-nm generation. Firstly, commercially available SOI wafers with ultrathin BOX ( $T_{\rm BOX}=10\,$  nm) [2.8] were thinned by sacrificial oxidation so that the thickness of the SOI layer reduced to 13 nm. By using the similar process steps as the conventional bulk CMOSFETs, shallow trench isolation (STI) formation and well implantation were done. For multi  $V_{\rm th}$  design, the substrate beneath the BOX layer was implanted while keeping the dopant of the channel low. A halo implantation is not necessary to prevent SCE in FD-SOI devices. In the gate oxidation process, SiON gate dielectrics were formed at an equivalent oxide thickness (EOT) of 1.9 nm for SOTB core CMOSFETs.

The gate stack was constituted with a thin poly-Si layer (40 nm) and a cap SiO<sub>2</sub> layer (consisted by tetraethyl orthosilicate tetraethoxysilane (TEOS)). After etching the gate stack, a thin high temperature oxide (HTO) and a SiN layers were deposited. When the SiN layer was etch-backed, the HTO layer was used as a stopper to protect the thin SOI layer from the etching damage. The formed SiN offset spacer was used to control overlap length between the gate and extensions  $(L_{ov})$  precisely in the S/D extension implantation. After forming a sidewall, an elevated S/D structure was formed by SEG to obtain low  $R_{\rm sd}$ . To prevent decrease in the SOI thickness in the S/D region, the conditions for etchings and pre-cleaning before the SEG were carefully optimized. It was also noted that the SiO<sub>2</sub> layer as a gate- capping was required to protect the poly-Si layer. Unless the poly-Si layer was exposed, an excessive Si layer over the gate was formed in the SEG. The height of the S/D was set to be higher than the gate poly-Si layer for the simultaneous FUSI. After an ion implantation for S/D region, a FUSI process was done as described below.

Fig. 2.1 Process steps of a FUSI-gate SOTB CMOSFET

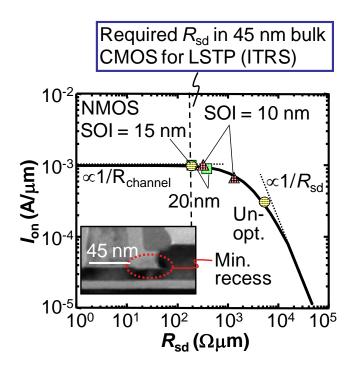

Fig. 2.2 Relationship between on-current  $I_{\rm on}$  and external resistance  $R_{\rm sd}$

Figure 2.2 shows extracted  $R_{\rm sd}$  values in several process conditions. The enough low  $R_{\rm sd}$  below 200  $\Omega/\mu m$  was obtained in the optimum condition, resulting in no degradation of the  $I_{\rm on}$  value. In the case of un-optimized condition such as excess recess in the SOI layer, the  $I_{\rm on}$  value degraded in proportion to the high  $R_{\rm sd}$ .

In low-power FD-SOIs with intrinsic channels, no dual metal technology between NMOS and PMOS gates, such as NiSi phase control [2.9], is required when using nickel silicide as a gate electrode material. Here, the gate needs to be fully silicided on one side. On another side, however, the S/D region must not be fully silicided. If the SOI layer under the NiSi were fully silicided, the  $R_{\rm sd}$  increases due to the small contact area between Si and NiSi [2.10]. Therefore, the gate poly-Si and the S/D epitaxial Si were set to their optimal heights before gate-cap removal and fully silicided simultaneously in a single step without using CMP. A deposited Ni thickness was carefully designed. To precise control the thickness of the formed NiSi layer, 2-step annealing was adopted. The first annealing was to control the thickness of

the NiSi layer, and the second annealing after removing the remained Ni layer was to control the phase of the NiSi layer.

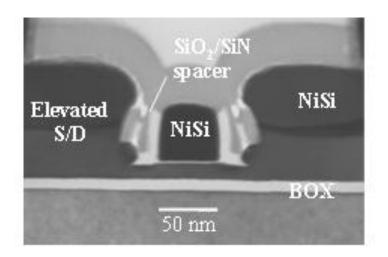

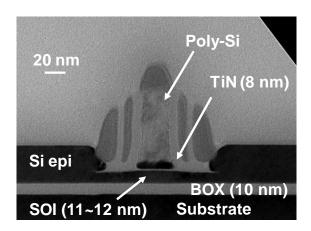

Figure 2.3 shows a cross-sectional TEM image of a fabricated 50-nm-gate-length SOTB MOSFET. Energy-dispersive X-ray spectroscopy (EDS) indicated that the NiSi atomic ratio for both the gate and the source/drain was 1:1.

Fig. 2.3 A cross-sectional TEM image of 50-nm-gate-length SOTB MOSFET

Regarding the isolation between transistors and back-gate contacts, this SOTB technology uses a conventional STI process similar to the bulk technology. The slight change is that the trench is formed by dry etching three layers: the SOI, BOX, and substrate. Consequently, the isolation between devices on the SOI and back-gate contacts is ensured by STI. The well region, acting as a back gate and ground plane, was formed beneath the BOX layer and connected to the region of the back-gate contact through the area underneath the STI. The back-gates for NMOS and PMOS are also isolated by STI. This back-gate contact structure in SOTB technology can be fabricated with the same mask layout as the conventional bulk CMOSFET. A triple-well structure is also adopted to prevent leakage for back-gate biasing.

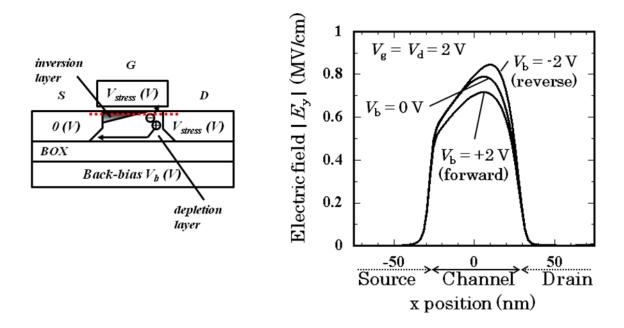

#### 2.3 DC characteristics of SOTB CMOSFET for 1.2-V operation

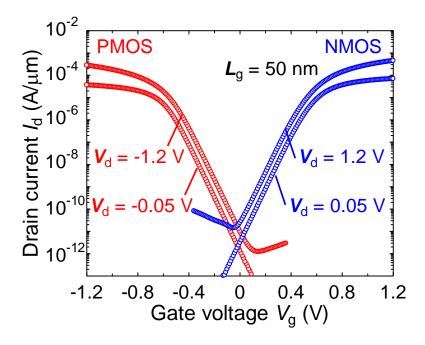

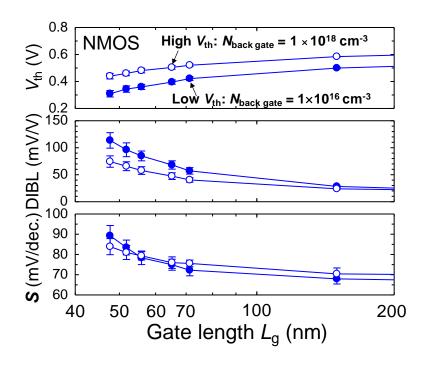

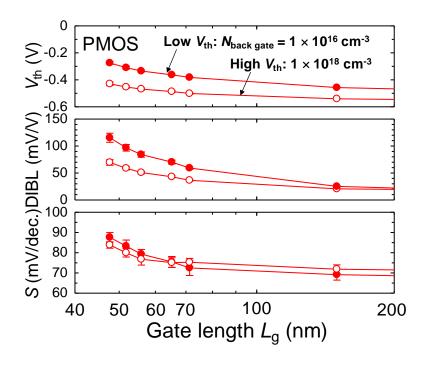

The typical subthreshold characteristics of the 50-nm-gate-length SOTB CMOSFETs at  $V_{\rm dd} = 1.2$  V are plotted in Fig. 2.4. The desired symmetrical characteristics were successfully obtained with a single Ni FUSI gate. Figures 2.5 and 2.6 show the roll-off characteristics of SOTB NMOSFET and PMOSFET, respectively. They have suppressed SCE even in low-dose channel without halo implant, resulting in SS less than 90 mV/decade and drain induced barrier lowering (DIBL) less than 120 mV/V. They also show that multi  $V_{\rm th}$  values are successfully achieved for LSTP specifications by selecting the dopant of the substrates of  $1 \times 10^{16}$  cm<sup>-3</sup>, respectively.

Fig. 2.4 Typical  $I_{

m d}$ -  $V_{

m g}$  characteristics of 50-nm-gate-length SOTB CMOSFET

Fig. 2.5 Roll-off characteristics of SOTB NMOSFET

Fig. 2.6 Roll-off characteristics of SOTB PMOSFET

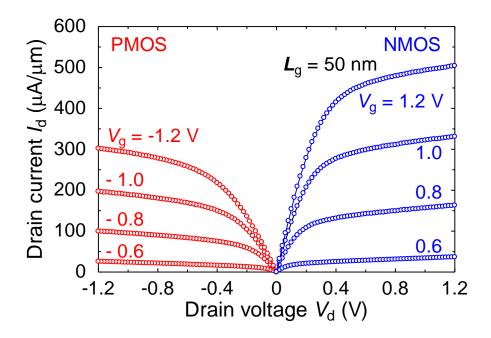

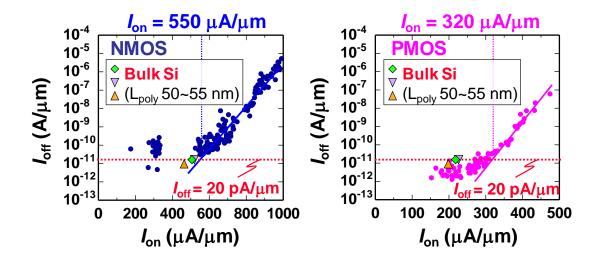

Figure 2.7 shows the output characteristics of SOTB CMOSFET. It is proven that the SOTB CMOSFET is free from the self-heating effect thanks to the ultrathin BOX. That is, negative drain conductance (decreasing  $I_{\rm d}$  with increasing  $V_{\rm d}$ ) was not observed. The off-state drain currents were less than 20 pA/ $\mu$ m due to the reduction of gate induced drain leakage (GIDL) with properly controlled  $L_{\rm ov}$ . At the same time, the on-currents of 550 and 320  $\mu$ A/ $\mu$ m for NMOS and PMOS are obtained. This is because FUSI suppresses gate depletion resulting in a 0.4 nm improvement, as evaluated by CV measurement. Additionally, it is possible that the volume expansion of FUSI gate causes compressive strain to the channel, which modulates carrier mobilities. These  $I_{\rm on}/I_{\rm off}$  values are in good agreement with the data based on bulk or FD-SOI technology for LSTP applications [2.11]-[2.13] as shown in Fig. 2.8. The above characteristics for the target specifications are summarized in Table 2.1.

Fig. 2.7  $I_d$ -  $V_d$  characteristics of 50-nm-gate-length SOTB CMOSFET. No self-heating is evident due to the thin BOX

Fig. 2.8  $I_{on}$ - $I_{off}$  characteristics of 50-nm-gate-length SOTB CMOSFET in comparison with planar bulk CMOSFETs

Table 2.1 Comparison of the characteristics in 65-nm generation

|                                       | [2.14]                    | [2.15]     | Target            | Results                  |

|---------------------------------------|---------------------------|------------|-------------------|--------------------------|

| Device                                | bulk                      | bulk       | ı                 | SOTB                     |

| $V_{\rm dd}$ (V)                      | 1.2                       | 1.2        | 1.2               | 1.2                      |

| $L_{\rm g}$ (nm)                      | 55                        | 50         | 50                | 50                       |

| EOT (nm)                              | 1.95                      | 2.45 (CET) | 1.9               | 1.9                      |

| Gate dielectric                       | SiON                      | HfSiON     | SiON              | SiON                     |

| $V_{ m th}$ (V)                       | 0.3                       | 0.3-0.5    | Multi $V_{ m th}$ | 0.35 (LVT)<br>0.45 (HVT) |

| $I_{\rm on}$ (NMOS) ( $\mu A/\mu m$ ) | 445                       | 510        | 500               | 550                      |

| $I_{\rm on}$ (PMOS) ( $\mu A/\mu m$ ) | 190                       | 220        | 300               | 320                      |

| $I_{\rm off}$ (NMOS) (pA/ $\mu$ m)    | 10                        | 20         | 20                | 20                       |

| $I_{\rm off}$ (PMOS) (pA/ $\mu$ m)    | 10                        | 20         | 20                | 20                       |

| Avt (NMOS)                            | 3~4                       |            | <2                | 1.8                      |

| Avt (PMOS)                            | (estimated as conv. bulk) |            | <2                | 1.5                      |

#### 2.4 Wide-range back-biasing of SOTB CMOSFET

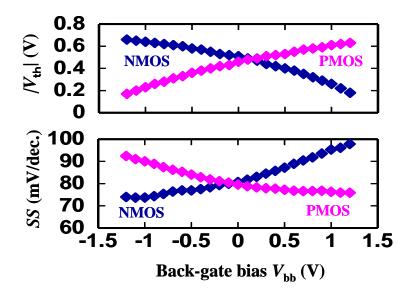

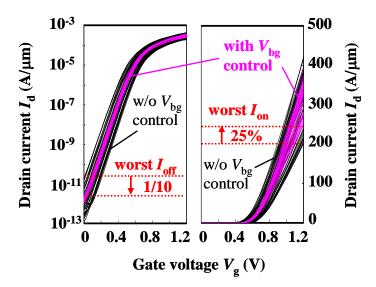

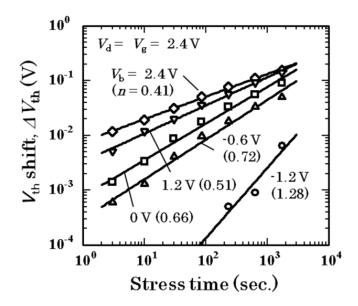

In the typical transistor design of SOTB, the  $V_{\rm th}$  without applying back-biasing can be controlled by changing the dopant concentration of the substrate beneath the thin BOX. While, time-to-time or area-to-area (including die-to-die or wafer-to-wafer) device characteristics can be widely controlled using the back-gate bias  $V_{\rm bb}$ . In particular, forward back-gate bias can be effectively used because there is no substrate leakage. Note that a forward bias higher than 0.6 V can never be applied in conventional bulk CMOSFETs owing to the significant increase in p-n junction leakage current from source to substrate. The dependences of  $V_{\rm th}$  and the SS of a 50-nm-gate-length SOTB CMOSFET on  $V_{\rm bb}$  at  $V_{\rm dd} = 1.2$  V are shown in Fig. 2.9. By applying a reverse  $V_{\rm bb}$ ,  $V_{\rm th}$  increased to above 0.6 V, and the SS decreased to less than 80 mV/decade. In contrast, by applying a forward back-gate bias of 1.2 V,  $V_{\rm th}$  can be lowered by more than 0.3 V while keeping the SS small. In such a high forward bias, there is no increase in the substrate leakage currents.

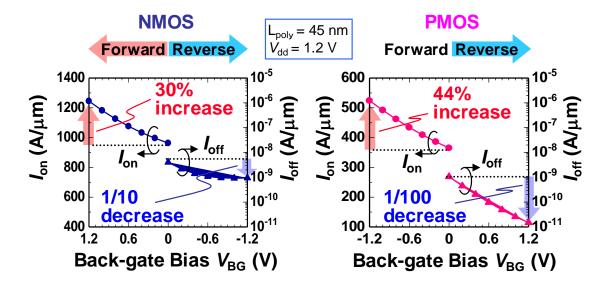

The back-gate bias dependences of the on- and off- currents of the SOTB CMOSFET are shown in Fig. 2.10. By applying a reverse back-gate bias of |1.2 V|,  $I_{\rm off}$  can be reduced to less than 1/100 in PMOSFET. However, in NMOSFET,  $I_{\rm off}$  cannot be decreased so much due to the large GIDL current. It will be considered extensively in chapter 3. On the other hand, the on-current of the SOTB CMOSFET can be increased by 30% for NMOS and by 44% for PMOS by applying a forward bias of |1.2 V|. This wide-range back-biasing can enable high-performance and low-power LSIs so that the forward biasing is used when faster speed is required, and the reverse biasing is used at the standby mode.

Fig. 2.9 Dependences of  $V_{\rm th}$  and SS for a 50-nm-gate-length SOTB CMOSFET as a function of back-gate bias  $V_{\rm bb}$  at  $V_{\rm dd}$  = 1.2 V

Fig. 2.10 Dependences of  $V_{\rm th}$  and SS for a 50-nm-gate-length SOTB CMOSFET as a function of back-gate bias  $V_{\rm bb}$  at  $V_{\rm dd}$  = 1.2 V

As for conventional bulk structures, reverse biasing can be used to reduce the standby leakage after fabrication. However, this is less effective because both  $V_{

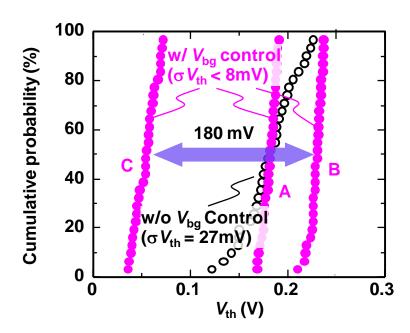

m th}$  variation and GIDL increases [2.15]. In the SOTB case, GIDL is sufficiently suppressed by the intrinsic channel and the controlled  $L_{ov}$ , and forward  $V_{\rm bb}$  is also effective in adjusting the  $V_{\rm th}$  variation. The die-to-die compensation for the  $V_{