# T2R2 東京工業大学リサーチリポジトリ

## Tokyo Tech Research Repository

### 論文 / 著書情報 Article / Book Information

| 題目(和文)            | メニーコアの協調キャッシュに関する研究                                                                                                                                                                       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | Research on many-core cooperative caching                                                                                                                                                 |

| 著者(和文)            | 藤枝直輝                                                                                                                                                                                      |

| Author(English)   | Naoki Fujieda                                                                                                                                                                             |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第9190号,<br>授与年月日:2013年3月26日,<br>学位の種別:課程博士,<br>審査員:吉瀬 謙二                                                                                            |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第9190号,<br>Conferred date:2013/3/26,<br>Degree Type:Course doctor,<br>Examiner: |

|                   | 博士論文                                                                                                                                                                                      |

| Type(English)     | Doctoral Thesis                                                                                                                                                                           |

### Research on Many-core Cooperative Caching

(メニーコアの協調キャッシュに関する研究)

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Engineering

### Naoki Fujieda

March 2013

Graduate School of Information Science and Engineering

Department of Computer Science

Tokyo Institute of Technology

### **Abstract**

The trend of progress in processor architectures has changed to increasing the number of processor cores in a single chip. The past fashion was improving the working frequency and/or the average number of instruction per cycle (IPC) they can execute, that is, the single-thread performance. However, this strategy does not match with the hardware cost and the power consumption any more. Multicore processors are now the majority of processors even for cell phones and handheld game consoles. If this trend continues, the era of many-core processors that have tens or hundreds of cores in a chip will come in the near future.

In the many-core era, there are increasing demands for efficient memory systems to realize high-performance processors. They usually have multiple levels of cache memories and each level has different function. The primary or L1 caches are the fastest and the smallest caches and thus supply the most common data as quickly as possible. On the other hand, the last level caches (LLCs) are the largest caches and expected to provide as many data from there, rather than from the main memory, as they can. Furthermore, they are not so sensitive to latency as the higher caches. Therefore, they can be complex and smart to meet the demand.

Recently, for the LLCs, the cooperative caching (CC) has been proposed. In the CC, each core keeps accessed data mainly in its own cache like private caches. The difference is that the CC allows cores transferring (or spilling) a part of their evicted cache lines to other cores. As a result, cores that are short of cache space can dynamically borrow some cache lines from other cores leaving most of their caches unused. However, to maximize the advantage of the CC, optimized methods of spilling are essential. Hence, there are a number of previous studies on them.

In this thesis, I propose a brand-new approach named ASCEND (Adaptive Spill Control with extra ENtries of Directory) for optimizing the CC. Not to mention high efficiency, high scalability — capability to apply the method to tens of cores — is also required for many-core processors. There were no past researches to achieve both of them; ASCEND is the first one.

The target architecture of my approach is the Distributed Cooperative Caching (DCC), a scalable variation of the CC. It has distributed organizations called Distributed Coherence Engines (DCEs) to keep shared cache lines coherent. An important discovery in my proposal is that they need some extra entries for preventing performance degradation. I find that the currently unused hardware that was

Abstract

invalidated is useful for analyzing characteristics of cores in detail, for it has the information of the cache lines that were recently removed from the chip. ASCEND extracts them by two kinds of units named Spiller Selectors and Receiver Selectors and control the spilling adaptively.

The contributions of this thesis are threefold. One of the secondary contributions is the classification of various recent studies to improve cache performance. I divide them into some categories by their targets or features. Since there are many studies on this field, it may be hard to hit upon a new idea when we persist on only one category. Instead, mixing knowledge of more than one category can become a hint of it. I believe my classification provides a wide view of cache optimization schemes and a clue of a novel approach for them.

The other secondary contribution is implementation of a useful infrastructure for research on many-core processors with shared memory. To evaluate the methods in the many-core environment, I am developing a simulator of many-core processors with the CCs named SimMccc. It utilizes SimMips, a simple and practical MIPS system simulator, and inherits the characteristics from this. Hence, it can be utilized as a great infrastructure of the CCs.

The most important contribution of this thesis is to show an efficient and scalable method for the CCs to spill effectively, through the proposal and the evaluation of ASCEND. It is expected to play an important role in the future many-core era. I evaluate various methods in both multicore and many-core environments. The results showed that my method was more efficient than an existing efficient but non-scalable method in the multicore environment. They also showed that it outperformed a scalable but not-so-efficient method in the many-core environment. That is to say, the evaluation of two confirmed that it is an efficient and scalable method.

## **Contents**

| 1   | Int                                                | roduction                                           | 1  |

|-----|----------------------------------------------------|-----------------------------------------------------|----|

| 1.1 | Motiv                                              | ation                                               | 1  |

| 1.2 | 2 Contribution                                     |                                                     | 4  |

| 1.3 | Outlin                                             | ne of this thesis                                   | 5  |

| 2   | Ba                                                 | ckground                                            | (  |

| 2.1 | Cache                                              | Optimization mainly for Single Thread               | 7  |

|     | 2.1.1                                              | Dead Block Prediction                               | 7  |

|     | 2.1.2                                              | Replacement Algorithm                               | 10 |

|     | 2.1.3                                              | Improving Associativity                             | 13 |

| 2.2 | Cache                                              | Optimization focusing on Multithread                | 15 |

|     | 2.2.1                                              | Thread-aware Replacement Algorithm                  | 15 |

|     | 2.2.2                                              | Cache Partitioning                                  | 16 |

| 2.3 | Towar                                              | rd Many-core Caching                                | 19 |

|     | 2.3.1                                              | Non-uniform Cache Architecture (NUCA)               | 19 |

|     | 2.3.2                                              | Scalable Coherence Control                          | 21 |

| 2.4 | Coope                                              | erative Caches and their Optimization               | 22 |

|     | 2.4.1                                              | Overview of Cooperative Caches                      | 22 |

|     | 2.4.2                                              | Distributed Cooperative Caching                     | 23 |

|     | 2.4.3                                              | Optimization of Spilling                            | 25 |

| 2.5 | Summ                                               | nary                                                | 28 |

| 3   | Pro                                                | oposal of Useful Simulation Infrastructure          | 29 |

| 3.1 | Target                                             | Architectures                                       | 30 |

|     | 3.1.1                                              | Modeling Modern Multicore                           | 30 |

|     | 3.1.2                                              | Modeling Future Many-core                           | 31 |

| 3.2 | Simul                                              | ation Infrastructure                                | 32 |

|     | 3.2.1                                              | SimMips: MIPS System Simulator                      | 32 |

|     | 3.2.2                                              | SimMccc: Simulator of Many-core Cooperative Caching | 34 |

| 3.3 | Comp                                               | arison with other infrastructures                   | 40 |

| 3.4 | Experimental methodology for Multicore Environment |                                                     | 41 |

| 3.5 |                                                    |                                                     | 4  |

| Contents | iv |

|----------|----|

|          |    |

| 4.1       |         | ssity of Extra Entries of Directory                         | . 57 |

|-----------|---------|-------------------------------------------------------------|------|

|           | 4.1.1   | Avoiding Replacement in directories                         | . 57 |

|           | 4.1.2   | Probabilistic Analysis                                      | . 60 |

|           | 4.1.3   | Preliminary Experiment                                      | . 64 |

| 4.2       | New     | Concept of Utilizing Extra Directory Entries                | . 65 |

|           | 4.2.1   | Dealing with Invalidated Entries                            | . 65 |

|           | 4.2.2   | Example of Two Kinds of I-Reference                         | . 67 |

| 4.3       | Archi   | itectural Organization of ASCEND                            | . 69 |

| 4.4       | Origi   | nal Method                                                  | . 71 |

|           | 4.4.1   | Spiller Selector                                            | . 71 |

|           | 4.4.2   | Receiver Selector                                           | . 72 |

| 4.5       | Highl   | ly-Precise Method                                           | . 76 |

|           | 4.5.1   | Spiller Selector                                            | . 76 |

|           | 4.5.2   | Receiver Selector                                           | . 77 |

|           | 4.5.3   | Weak Receiving — An Optional Extension of Receiver Selector | . 80 |

| 4.6       | Diffe   | rence with other spilling optimizations                     | . 82 |

| 4.7       | Sumr    | mary                                                        | . 83 |

| 5         | Ev      | valuation of ASCEND                                         | 84   |

| 5.1       | Evalu   | nation Results for Multicore Environment                    | . 84 |

| 5.2       | Evalu   | nation Results for Many-core Environment                    | . 88 |

| 5.3       | Hard    | ware Overhead                                               | . 90 |

| 5.4       | Discu   | assion                                                      | . 91 |

|           | 5.4.1   | How did ASCEND classify the demands in capacity?            | . 91 |

|           | 5.4.2   | Should we consider the distance between cores?              | . 93 |

| 5.5       | Sumr    | mary                                                        | . 95 |

| 6         | Co      | onclusions                                                  | 96   |

| 6.1       | Conc    | luding Remarks                                              | . 96 |

| 6.2       | Open    | Research Areas                                              | . 97 |

| Acknow    | vledgem | ents                                                        | 99   |

| Bibliog   | raphy   |                                                             | 100  |

| List of 1 |         | ions                                                        | 108  |

## **List of Figures**

| 1.1  | The change of processor improvement and its details                             | 1          |

|------|---------------------------------------------------------------------------------|------------|

| 1.2  | A conceptual model of many-core processors                                      | 2          |

| 1.3  | Cooperative LLCs that try to take advantage of both private LLCs and shared LLC | 3          |

| 2.1  | Differences between trace-based dead block predictor with and without sampler   | 8          |

| 2.2  | Organization of a typical time-based dead block predictor                       | 9          |

| 2.3  | Examples of some replacement algorithms                                         | 11         |

| 2.4  | An example of a 3-way Skewed-associative Cache.                                 | 13         |

| 2.5  | An example of a quest for candidates for eviction in the ZCache                 | 14         |

| 2.6  | An organization of the utility-based cache partitioning                         | 16         |

| 2.7  | An organization of the cache-partitioning aware replacement policy              | 17         |

| 2.8  | Different NUCA organizations in multicore processors                            | 20         |

| 2.9  | The organization and working examples of the Distributed Cooperative Caching    | 24         |

| 2.10 | Organization and virtual cache hierarchy of the ElasticCC                       | 26         |

| 2.11 | Samplings of sets in the DSR                                                    | 27         |

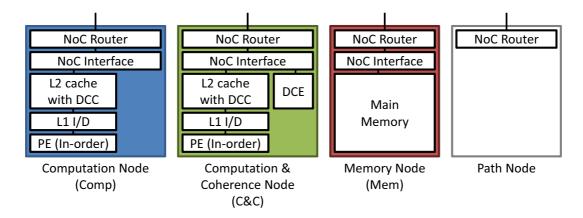

| 3.1  | The architectural model for the multicore environment                           | 30         |

| 3.2  | The architectural model for the many-core environment                           | 31         |

| 3.3  | Four types of node on the target many-core.                                     | 31         |

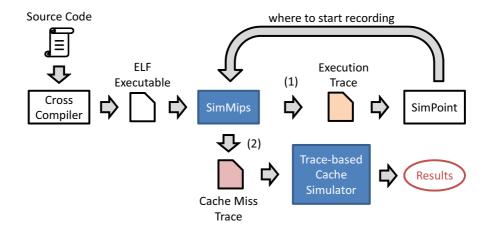

| 3.4  | Flow of the evaluation in the multicore environment                             | 32         |

| 3.5  | A part of the Mips::drive method that executes an instruction if possible       | 34         |

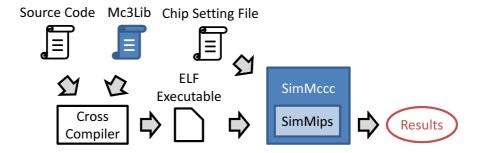

| 3.6  | Flow of the evaluation in the many-core environment                             | 35         |

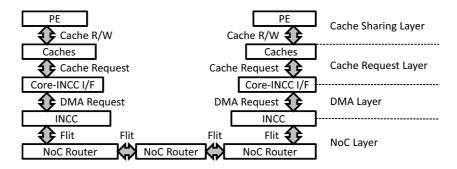

| 3.7  | Multiple layers of communication in SimMccc                                     | 36         |

| 3.8  | Typical relationship of each class between available cache size and performance | 43         |

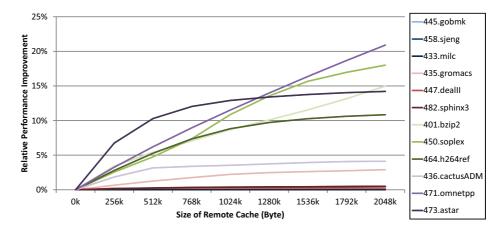

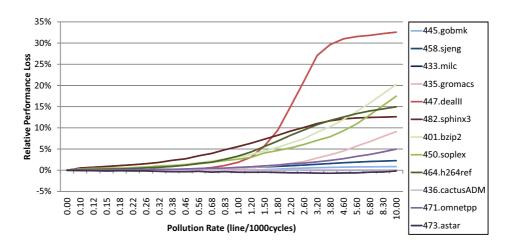

| 3.9  | The barometer of spill necessity of the applications                            | 44         |

| 3.10 | The barometer of pollution sensitivity of the applications                      | 44         |

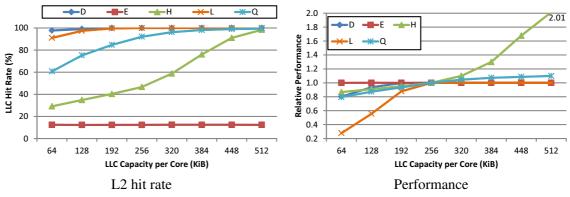

| 3.11 | Effects of cache size on benchmarks for evaluation                              | 47         |

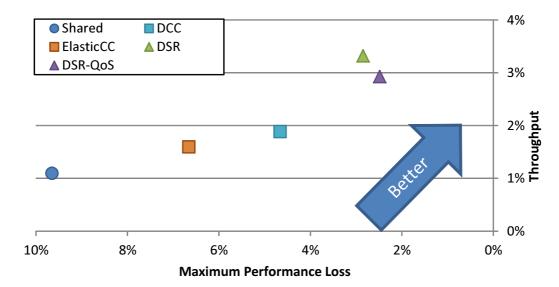

| 3.12 | Performance and QoS of various methods in the multicore environment             | 48         |

| 3 13 | Performance and OoS of various methods in the many-core environment             | <b>4</b> C |

List of Figures vi

| 4.1  | The review of the organization and the undesirable working example of the DCC              | 57 |

|------|--------------------------------------------------------------------------------------------|----|

| 4.2  | Cache lines and replicas of their tags in the centralized Coherence Engine                 | 59 |

| 4.3  | Cache lines in cores and directory entries in the DCEs                                     | 60 |

| 4.4  | The first assumption of set mapping.                                                       | 61 |

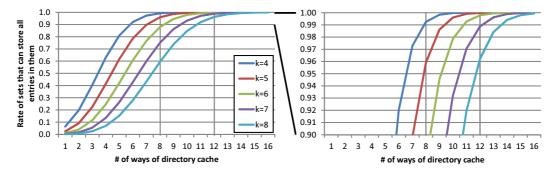

| 4.5  | Directory cache size vs. probability of having sufficient entries (in the first assump-    |    |

|      | tion, N=4)                                                                                 | 62 |

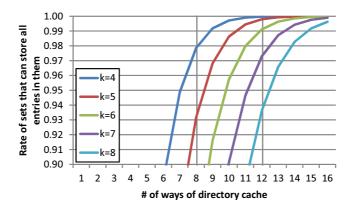

| 4.6  | The second assumption of set mapping                                                       | 63 |

| 4.7  | Directory cache size vs. probability of having sufficient entries (in the second assump-   |    |

|      | tion)                                                                                      | 63 |

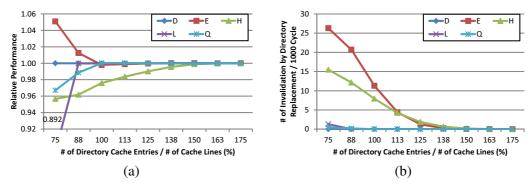

| 4.8  | Directory cache size vs. performance and invalidation frequency                            | 64 |

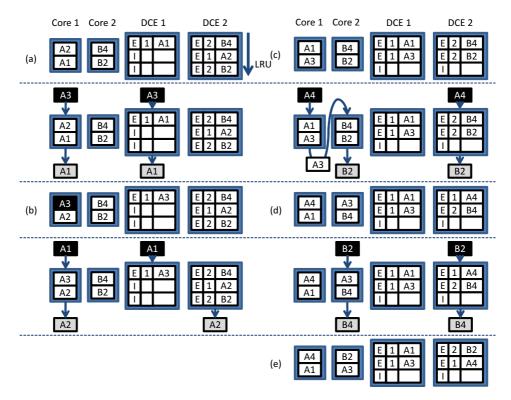

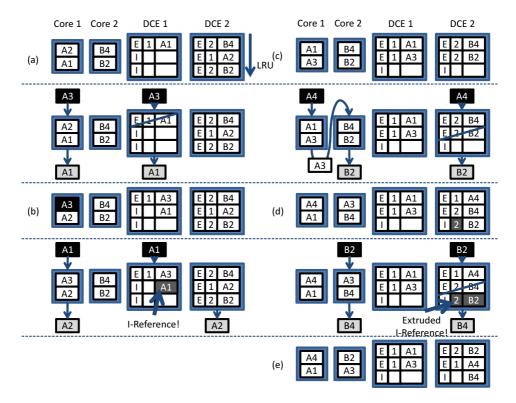

| 4.9  | Transition of tags when invalidated tags are removed                                       | 67 |

| 4.10 | Transition of tags when invalidated tags are preserved                                     | 68 |

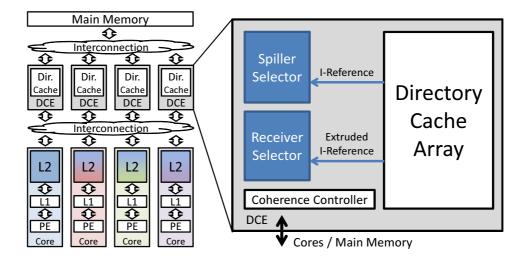

| 4.11 | Organization of the DCC with ASCEND                                                        | 70 |

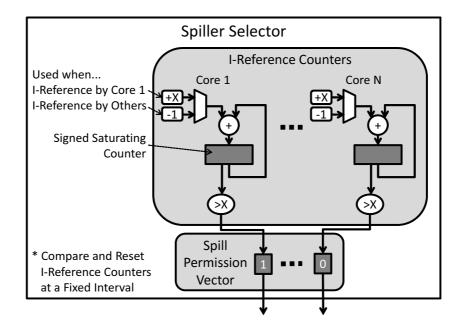

| 4.12 | Detailed organization of Spiller Selector in the original method                           | 72 |

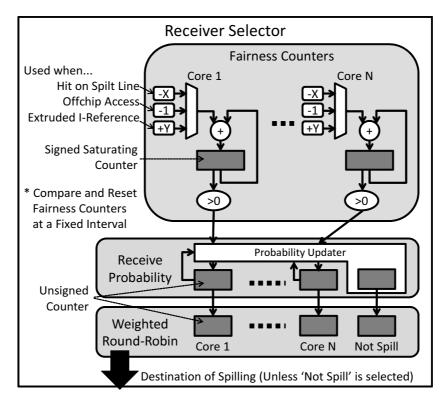

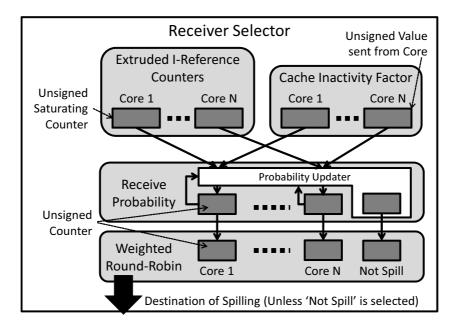

| 4.13 | Detailed organization of Receiver Selector in the original method                          | 74 |

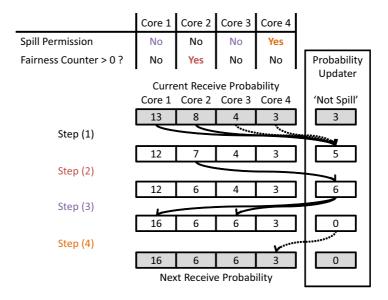

| 4.14 | Example of update process of receive probability registers                                 | 75 |

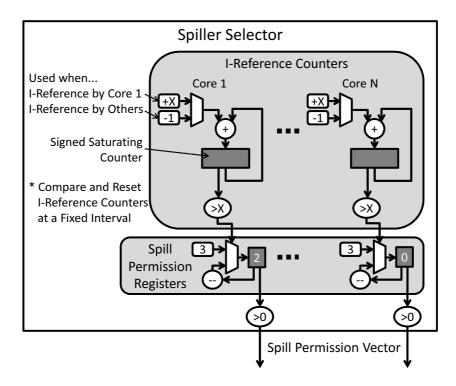

| 4.15 | Detailed organization of Spiller Selector in the highly-precise method                     | 76 |

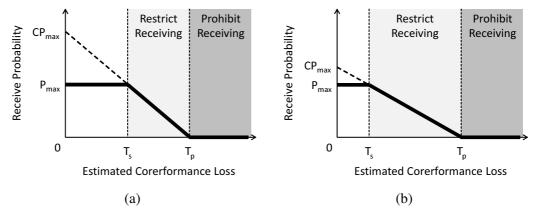

| 4.16 | Restriction and prohibition of receiving evicted lines                                     | 78 |

| 4.17 | Detailed organization of Receiver Selector in the highly-precise method                    | 79 |

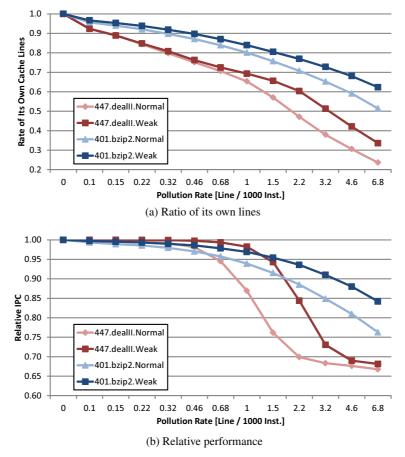

| 4.18 | Pollution rate vs. percentage of cache lines that are kept local and relative performance. | 81 |

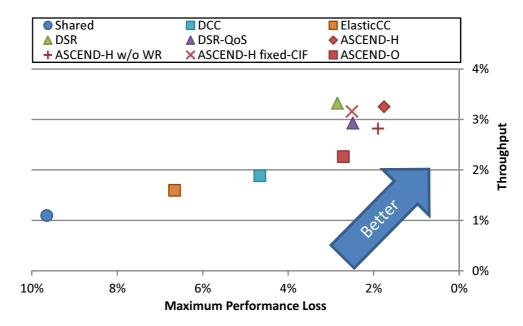

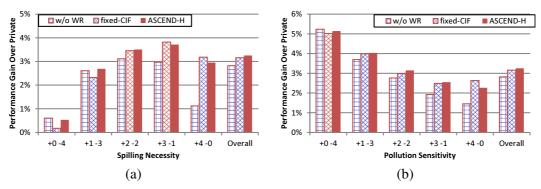

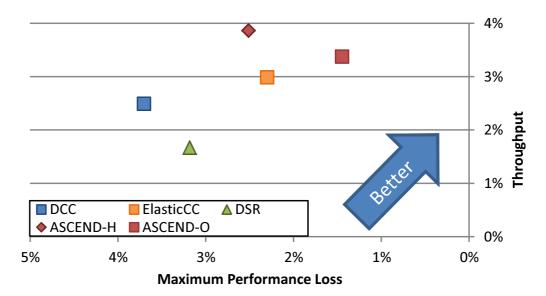

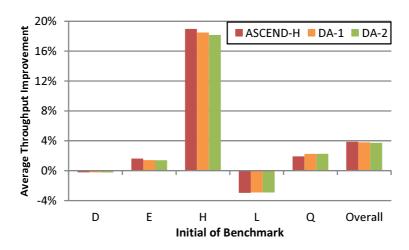

| 5.1  | Comparison of performance and QoS of ASCEND with the other methods in the                  |    |

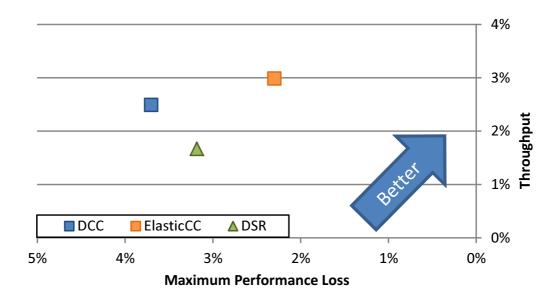

|      | multicore environment.                                                                     | 85 |

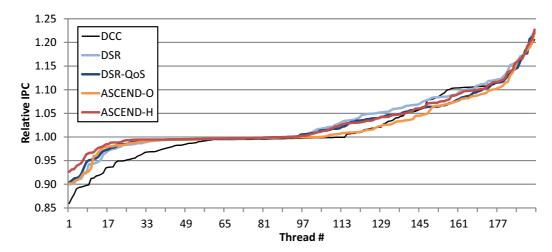

| 5.2  | Relative IPC distribution in the multicore environment                                     | 86 |

| 5.3  | Throughput variation with adopting options of ASCEND                                       | 87 |

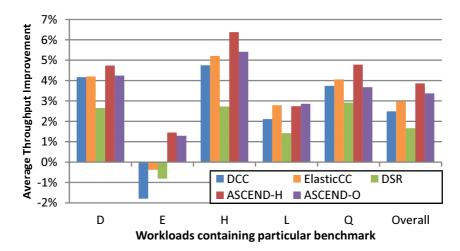

| 5.4  | Comparison of performance and QoS of ASCEND with the other methods in the                  |    |

|      | many-core environment                                                                      | 88 |

| 5.5  | Performance in the many-core environment. Workloads are grouped by included ap-            |    |

|      | plication                                                                                  | 89 |

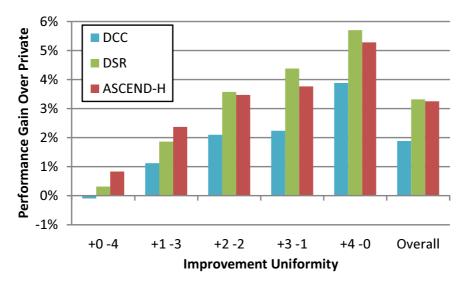

| 5.6  | Throughput in the multicore environment. Workloads are grouped by improvement              |    |

|      | uniformity                                                                                 | 91 |

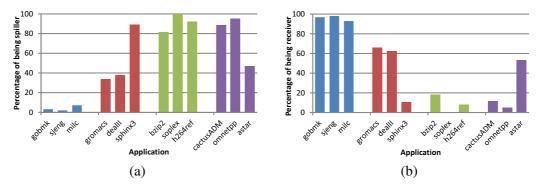

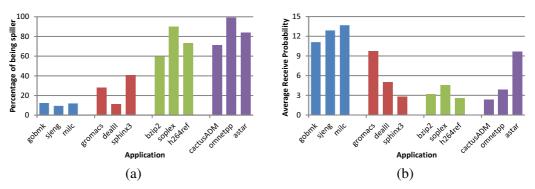

| 5.7  | The percentage of being spiller and that of being receiver in DSR                          | 92 |

| 5.8  | The percentage of being spiller and the average receive probability in ASCEND-H            | 92 |

| 5.9  | An example of the difference in latency by the distance between the requester and the      |    |

|      | holder                                                                                     | 93 |

| 5.10 | Throughput of distance-aware ASCEND                                                        | 94 |

## **List of Tables**

| 3.1  | Transition of L1 caches                                                  | 38 |

|------|--------------------------------------------------------------------------|----|

| 3.2  | Source code organization of SimMccc Version 0.9.8                        | 39 |

| 3.3  | Architectural parameters of the multicore environment                    | 41 |

| 3.4  | The list of applications and their classes                               | 42 |

| 3.5  | The classification of applications for the multicore workload            | 43 |

| 3.6  | The combinational patterns of classes for workload selection             | 45 |

| 3.7  | Evaluation parameters for the many-core environment                      | 46 |

| 3.8  | Benchmarks to evaluate many-core environment                             | 47 |

| 3.9  | Transition of L2 caches                                                  | 52 |

| 3.10 | Transition of directory caches                                           | 55 |

| 4.1  | The contrast between access frequency of caches and that of directories. | 58 |

## **Chapter 1**

## Introduction

#### 1.1 Motivation

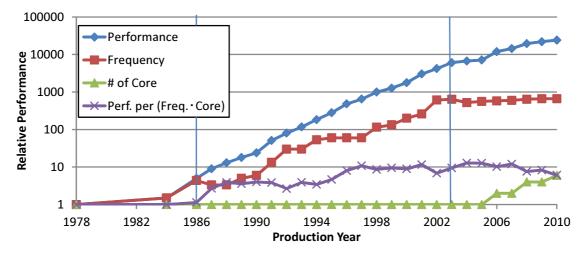

The rapid improvement in processor performance from the late 1980s to 2003 mainly came from the rise in operating frequency. Figure 1.1 shows the improvement in processor performance and its details. In addition to frequency, various architectural techniques improved the performance per clock cycle. These techniques include pipelining, branch prediction, and the theme of this thesis — efficient use of cache memories.

The trend of progress in processor technology has changed to increasing the number of processor cores in a single chip. In 2003, the rapid rise in frequency ended due to increasing power consumption and wire delay. Since the late 2000s, multicore processors that integrate multiple cores in a single chip have been widely used. If the trend continues, the era of many-core processors that have tens or hundreds of cores in a chip will come in the near future.

Figure 1.1 The change of processor improvement and its details. All values are relative to VAX-11/780 in 1978. Each point represents the performance of a specific processor that was shipped in the corresponding year. The data are quoted from [1]

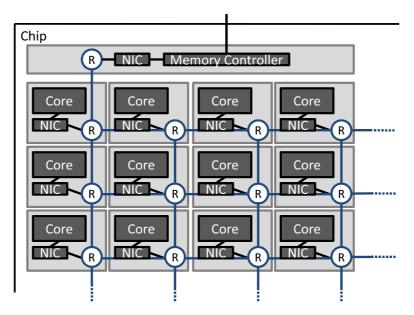

Figure 1.2 A conceptual model of many-core processors.

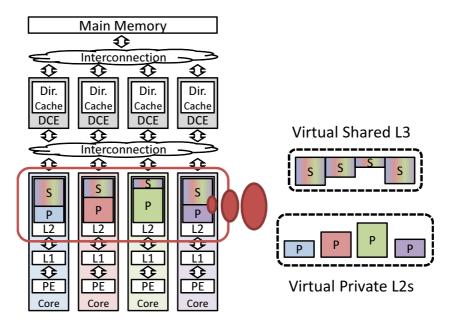

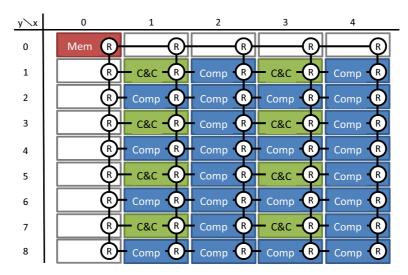

Figure 1.2 shows a typical conceptual model of many-core chip. In many-core, tens or hundreds of processor cores are connected in a two-dimensional mesh in a single chip. Each core is connected to a router (R in the figure) via a network interface controller (NIC). The memory controller is also connected to its corresponding router. My target many-core architecture assumes that each core has multiple levels of caches.

The problem with such progress in processor at all times is the increase of the gap of improvement between processors and main memories, or so-called memory wall. It turns memory bandwidth into more precious resources.

As a result, it is inevitable for high-performance processors to supply as many data from on-chip cache memories to save precious memory bandwidth. The best way to achieve it is to improve the performance of last level caches (LLCs) that are the largest caches and the closest to the main memory. There are a number of approaches for improving LLCs [2] [3] [4].

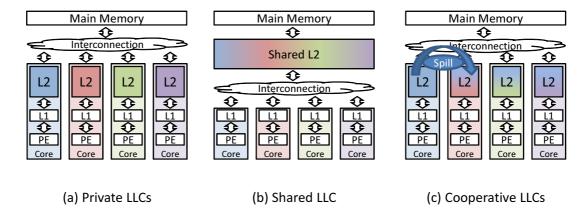

In multicore and many-core, an important design point is the organization of LLCs. Figure 1.3 shows three kinds of LLCs that have different organizations. The traditional cache organizations are private caches shown as (a) and a shared cache shown as (b). To exploit the advantage of both the organizations, cooperative caches [5] [6] shown as (c) are proposed. I explain their respective features below.

(a) in the figure shows the private LLCs. Each core stores data in its own small cache. Since the region to which a core refers is small, they keep the latency low. However, it is not flexible about capacity. That is, even if a core that is short of cache space is running with another core leaving most

Figure 1.3 Cooperative LLCs that try to take advantage of both private LLCs and shared LLC.

of its caches unused, the former core cannot use the unused cache region of the latter core.

(b) in the figure represents the shared LLC. All the cores access a single, large, and shared cache (shown in Shared L2). Though it is highly flexible about capacity, the average latency is longer than private caches, for all the cores must refer to the entire cache that is bigger and slower than private caches. To make matters worse, a harmful application may occupy most of the cache and contaminate the cache space for the other cores.

I now explain the cooperative caches shown as (c). The recently studied cooperative caches look like private caches, but they also permit the cores to store their own data to other cores. It is realized by allowing a part of cache lines evicted from one core forwarding (or *spilling*) to another core. Spilling overcomes the weakness of private caches and improves the overall performance by letting cores that require a large amount of frequently reused data borrow some cache lines from unused cache regions of other cores. Moreover, thanks to temporal locality, most cache references are done in local and thus the average latency is still small. However, adaptive spilling is essential for taking advantage of cooperative caches. In recent years, many of such spilling techniques [7] [8] [9] [10] have been proposed.

In this thesis, I propose a highly efficient and scalable approach named **ASCEND** (**Adaptive Spill Control with extra ENtries of Directory**) to control spilling. In addition to high efficiency, high scalability, or capability to apply the method to tens of cores, is also required for the future many-core era. Achieving both the properties is challenging, and ASCEND is the first method to realize it.

While existent methods use one kind of units to analyze the characteristics of applications, the method examines them in detail using two kinds of units with different criteria. Spiller selectors decide which cores should spill their evicted lines. Receiver selectors choose the destination of the spilled lines. These units analyze the characteristics precisely and forward lines adaptively. In addition, they are distributed in the chip and each unit makes a decision independently. It prevents concentration of

load and thus achieves high scalability.

I verify the effectiveness of ASCEND through evaluation using cycle-level simulation. In the evaluation, cores execute multiple applications that are different in demands on cache capacity at the same time. My approach detects the difference correctly and improves the performance by spilling cache lines from cores which want to borrow lines to those which have unused regions. Through the verification, I clarify a spilling method that achieves both high efficiency and scalability.

#### 1.2 Contribution

The contributions of this thesis are as follows:

- 1. to classify recent methods for cache optimization and show a direction to researches on this area;

- 2. to show the implementation of a useful simulation infrastructure for research on many-core processor with shared memory; and

- 3. to show a highly-efficient and scalable spilling to make use of the scheme of cooperative caches.

I refer to respective contributions below.

As one of the secondary contribution, I explain the aims and the features of a number of recent researches for improving caches and classify them. They include various topics and are not limited to cooperative caches and their optimization. Therefore, it is useful for researchers to get a wide perspective as an introduction to cache optimization. I also show a future direction of research on this area based on my classification.

The other secondary contribution is implementation of an infrastructure for research on many-core processors with shared memory. I make use of **SimMips** [11], a MIPS system simulator that we have developed, as a part of the infrastructure. Moreover, I am developing a new SimMips-based simulator named SimMccc (Simulator of Many-Core Cooperative Caching) \*1 to evaluate the target many-core. It can be utilized as a great infrastructure of cooperative caches.

The primary contribution is to show an efficient and scalable method for the cooperative caches through the proposal and evaluation of ASCEND. Some existing methods are not so efficient due to their insufficient analysis of demands on capacity. Others are not scalable with frequent broadcasts for the analysis. My proposal is distinctively different from them. It achieves almost the same efficiency as an existing high-performance method, without losing scalability. It is expected to play an important role in the future many-core era.

<sup>\*1</sup> It is pronounced as Sim-M-C-Three.

#### 1.3 Outline of this thesis

The outline of the subsequent chapters is as follows.

In Chapter 2, I explain various existing methods for efficient use of caches. As the trend of processors changed from single-core to multicore, optimization techniques began to need to be aware of multiple threads running in parallel. Moreover, scalability is becoming an important problem in anticipation of the many-core era. From these circumstances, I explain the methods for single-core, multicore, and many-core in order. Afterward, I refer to the target architecture, the Distributed Cooperative Caching (DCC), and its optimizations.

In Chapter 3, I propose a useful simulation infrastructure that centers on SimMips. To verify both efficiency and scalability, I define two respective simulation environments and describe how to simulate them with the proposed infrastructure. By comparison with other infrastructures, I clarify the advantage of ours. Afterward, I quantitatively show the problem of the existing optimizations for the DCC.

In Chapter 4, I propose ASCEND as an efficient and scalable optimization for the DCC. I first describe an important characteristic of the DCC, or that it needs some extra hardware being reserved. I then explain how my approach utilizes it by taking some examples. Afterward, I show the architectural organization of the DCC with ASCEND, two different ways to describe the additional units or the Spiller Selectors and the Receiver Selectors, and an optional extension named Weak Receiving.

In Chapter 5, I show the results of the evaluation of ASCEND and have some discussions from them. I also calculate the amount of the additional hardware after showing the results of the simulation.

I conclude this thesis in Chapter 6.

### **Chapter 2**

## **Background**

In this chapter, I mention various recent prior researches to make caches efficient. In the actual cache organization, it is natural to use a combination of methods across multiple categories rather than to rely on a single one. In addition, because some categories have been fairly researched, it may be difficult to propose a new idea focusing only on a single category. Instead, mixing up knowledge of other categories can be a hint of making cache management more efficient. For these reasons, I categorize related methods by their targets and features.

The primary classification in this chapter is based on the points that the methods focus on. They can be divided into three: characteristics of single-thread execution, interaction among multiple cores, or scalability for applying the methods to many-core. Each category has some subcategories of different features.

In Section 2.1, I refer to methods that exploit characteristics of single-thread execution. They consist of dead block prediction, replacement algorithm, and improving the efficiency of associativity.

In Section 2.2, I mention multicore-aware methods that consider the interaction among multiple cores that executes various applications. They are composed of thread-aware replacement algorithm and cache partitioning.

In Section 2.3, I state endeavors for future many-core processors. They need scalability or properties that their performance is not limited by the increase of the core count. They include Non-uniform Cache Architecture (NUCA) and improving directory-based coherence managements.

The Distributed Cooperative Caching (DCC) is a variation of cooperative caches that my approach is based on. Since it tries to improving scalability by distributing its organization over a chip, it can be included in the third category. However, its features and behavior is important for discussions in following chapters. Therefore, I devote Section 2.4 to cooperative caches and the DCC.

My approach ASCEND is an original method to control spilling in cooperative caches. Methods that focus on the difference in demands on capacity between cores and that manage spilling are considered as a form of cache partitioning, which is included in the second category. However, since they strongly depend on the scheme of cooperative caches and I have to discuss the features and the problem of

existing methods for spilling, I mention them later in Section 2.4.

#### 2.1 Cache Optimization mainly for Single Thread

#### 2.1.1 Dead Block Prediction

Lai et al. [12] first introduced the concept of dead block prediction. In the context of dead block prediction, if a cache line will be accessed again before it is evicted, then it is considered as *live*. In contrast, if it is no longer reused, it is considered as *dead*.

If we identify dead lines before the eviction, we benefit from them by invalidating, turning off, or replacing them, for they are no longer needed to be kept. To get this advantage, dead block predictors predict whether a line is live or dead, based on the information gathered on past access.

What kind of information predictors gather and how it is utilized vary greatly with methods. They can be divided into trace-based and time-based. I explain below how each kind of predictors make use of past information.

#### **Trace-based Prediction**

Trace-based predictors use traces of instructions, that is, the program counter (PC) of the instruction accessing a line or a set of PCs. When multiple lines are accessed by the same sequence of instructions, whether they are reused or not usually match each other. Many predictors aiming for performance adopt this strategy.

The first approach by Lai et al. [12] can be used for computer systems with symmetric multiprocessing (SMP). They added a trace-based predictor to a method, called Self-Invalidation [13], which a processor invalidated or wrote back cache lines voluntarily and earlier. Since wrong invalidation of lines that would be reused harmed the performance, they predicted dead lines and invalidate them in advance. Thus, they succeeded in reducing the latency on insertion without harmful effects.

A later proposal by Lai et al. [14] added the idea of dead block prediction to a prefetcher. Their predictor keeps not only traces when lines become dead but also the address of the lines that will be requested just before the dead lines are evicted. It enables the prefetcher to decide the prefetching address and its destination at the same time.

In contrast to these two methods, Virtual Victim Cache [15] does not consider the lines being expected to be dead as the immediate targets of invalidation. Instead, they are just marked as dead. When an inserted line causes an eviction afterwards, the cache searches for a line that is invalid or marked as dead in the secondary set of the evicted line. If such a line is found, the cache uses it as a shelter of the evicted line.

Bypassing the LLC or placing inserted lines only in the higher levels of caches is also possible. Sampling Dead Block Prediction (SDBP) [2] is a method that applies bypassing. In the SDBP, if the

Figure 2.1 Differences between trace-based dead block predictor with and without sampler

LLC does not have a spare line and a newly inserted line is predicted dead, it is placed only in the higher caches. This bypassing exploits the fact that the lines whose temporal locality can completely extracted by the higher caches have no necessity to be kept in the LLC.

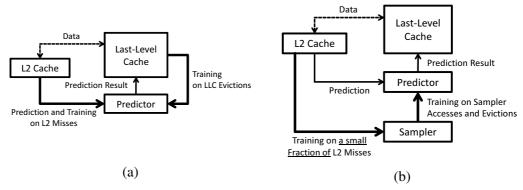

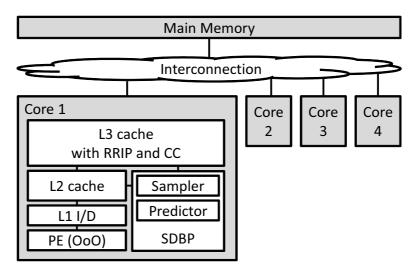

A distinct organization of this method is a small tag array as a sampler dedicated to dead block prediction. Not the main cache but the sampler is used for prediction. It greatly reduces the additional hardware and the power consumption. I show the difference between a conventional dead block prediction and the SDBP in Figure 2.1.

In a typical dead block predictor shown in Figure 2.1 (a), if a line misses in the L2 cache, the address of the line and the miss-causing PC are given to the predictor. The predictor sends the outcome based on the past information to the LLC. The miss-causing PCs are also sent to the LLC and stored in their tag array. When the missed line hits in the LLC, the predictor learns that the PC stored in the corresponding tag is likely to produce live lines, and then it updates the stored PC. Conversely, when a line is evicted from the LLC, the predictor learns that the stored PC is likely to cause dead lines.

In the SDBP shown in Figure 2.1 (b), on the other hand, the predictor traces the PCs of a small fraction of L2 misses using the sampler and updates the predictor table with the result. The reference to the table is done on every L2 miss. In addition, the tag array in the sampler can be different in the number of sets, the number of ways, replacement algorithm, etc. from that in the main cache. These features contribute to improving the accuracy of prediction.

#### **Time-based Prediction**

Time-based predictors utilize the elapsed time from the last access of each cache line. The predictors decide a threshold based on the past interval between accesses. If the elapsed time reaches the threshold, the line becomes predicted as dead.

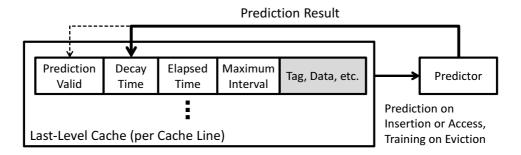

Figure 2.2 shows an organization of a typical time-based predictor. Other than the predictor itself, following per-line fields of additional metadata in the LLC are essential for time-based prediction:

Figure 2.2 Organization of a typical time-based dead block predictor.

- Prediction Valid that shows whether lines are treated differently by the prediction,

- **Decay Time** or the threshold of the elapsed time that is provided by the predictor,

- Elapsed Time that indicates the time from the last access, and

- Maximum Interval that shows the longest interval between accesses since the insertion of the line.

Other metadata are also added depending on the method.

The predictor expects the decay time (and whether the prediction is valid in some methods) and stores it into the cache line. The elapsed time is set to zero every time the line is accessed and incremented in method-specific conditions. If the prediction is valid and the elapsed time exceeds the decay time, the line is considered as dead. Besides, on every cache hit, the maximum interval is compared with the elapsed time and updated if needed. This field is sent to the predictor on eviction and used for training.

I explain methods using time-based predictors. IATAC [16] uses one to find which lines should be turned off to reduce leakage current. The predictor of IATAC uses the number of cycle as elapsed time and the prediction is based on the number of hits of the line since the insertion. Thanks to dynamic modification of the threshold, it shows high accuracy and thus succeeds in reducing leakage by turning off a large part of caches with a small penalty.

Counter-based predictors, such as one that was proposed by Kharbutli and Solihin [17], are sometimes classified differently from time-based predictors. However, I consider that these two kinds of predictors are essentially identical. Their predictor uses the number of scans through the set that a line belongs to as elapsed time. The prediction on insertion is based on the address of the line and the accessing PC. The result is valid only when the past two maximum intervals match. As done in many trace-based predictors, lines being predicted dead become the prior targets of replacement.

All the dead block predictors I have mentioned above use either one reference to the cache or passage of specific time from it as a trigger of prediction. However, more than one reference can be treated as a

single trigger. One of such ideas is called Cache Burst [18]. It treats a series of access to MRU (Most Recently Used) line, or a burst, as a trigger of prediction. This modification enables a prefetcher in the L1 cache to be precise and power-efficient. Unfortunately, it has less advantage in the L2 or lower caches because such extreme locality is filtered out in the L1 cache.

#### 2.1.2 Replacement Algorithm

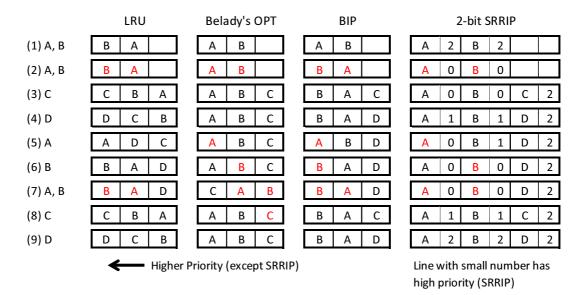

When there are no invalid lines in the same set as an inserted line, which line the cache selects for a victim of replacement has a significant influence on the cache performance. Figure 2.3 shows the behavior of some replacement algorithm that I mention in this section. In the figure, time-varying behavior of a 3-way cache (expressed in three blocks) given an access pattern of repetition of A, B, A, B, C, and D is shown. If the cache hits, the corresponding way is shown in red.

An LRU (Least Recently Used) replacement algorithm of choosing the line whose *last* access is the farthest from now and its approximation (called pseudo-LRU) are often used, for they are easy to implement and their average performance is not bad. However, the LRU performs poorly with some access patterns. One of the typical worst cases is repeatedly accessing a region slightly larger than the cache size. In this case, the victim lines are always what the processor will use next. As a result, the cache never gets hits.

In the leftmost column of Figure 2.3, the LRU is expressed as an algorithm placing an inserted line in the leftmost or most prioritized block. When D is inserted in the fourth row, the least prioritized line, A, is evicted, though it will be reused next. In similar, when A is inserted again in the fifth row, B, which is supposed to be reused in the sixth row, is removed. As a result, the LRU cache get only two hits per iteration (from sixth to eighth rows). In this section, I mention some methods to solve this problem and to aim for higher hit rates.

Belady found out the theoretically optimal replacement [19]. It is often called Belady's OPT algorithm. If the cache knew the complete sequence of future cache access, the optimal target for replacement would be the least imminent line or the line whose *next* access would be the farthest from now. The second column from the left in Figure 2.3 shows the optimal replacement. When D is inserted in the fourth row, for A, B, and C are reused earlier than D, D itself is the least imminent. Therefore, D is not stored in the cache. Consequently, the other lines receive hits and thus the hit count per iteration is five.

Unfortunately, this algorithm uses future information and thus is practically impossible to implement, even though we can get its outcomes a posteriori. For this reason, a number of near-optimal, implementable algorithms have been proposed in the recent years. Some of them try to emulate the optimal replacement, and others exploit the characteristics of processors or access patterns or both.

Figure 2.3 Examples of some replacement algorithms.

#### **Emulating the optimal replacement**

Shepherd Cache [20] tries to emulate Belady's OPT algorithm. It uses a FIFO (First-in First-out) cache called a Shepherd Cache along with the main cache. The Shepherd Cache temporarily suspends replacement of the main cache while inserted data are kept there. This allows the main cache artificially reproducing the ideal algorithm.

Keramidas et al. [21] proposed another approach to find the least imminent line. They got what time the block would be accessed next through prediction. Although I categorize it into a replacement algorithm, the idea is similar to trace-based dead block prediction.

#### Focusing on the characteristics of processors and/or cache access

MLP-aware Cache Replacement [22] notes that the effect of cache misses is not uniform in out-of-order processors because of memory-level parallelism (MLP). It prioritizes lines that have low MLP or have long latency on miss.

Bimodal Insertion Policy (BIP) [23] places most of the newly inserted lines on the LRU position, while a fraction of them are placed on the MRU position. If a line receives a hit, it is moved to the MRU. It is effective with the worst case of the LRU that I have mentioned above.

In the third column from left of Figure 2.3, all the inserted lines are placed on the LRU (the rightmost block) in BIP for ease of explanation. In the example, frequently used A and B tend to have higher priorities, but C and D do not. Since A and B hit twice, the number of hits per iteration is four. Practically, it sometimes places C and D on the MRU and thus the average number of hits is slightly smaller than four.

In both algorithms, they greatly outperform the LRU if access patterns match the method. However, if not, they can be less effective than the LRU. To deal with the shortcomings, some methods including them make use of tournaments with a small part of sets, called Set-Dueling. Set-Dueling fixes the replacement policy of tens of sets to the LRU and that of other tens of sets to the proposed scheme. The other sets follow one of the policies that cause fewer misses in the sampling sets. The methods with the Set-Dueling are named Sampling Based Adaptive Replacement (SBAR) for the MLP-aware Cache Replacement and Dynamic Insertion Policy (DIP) for the BIP.

To achieve higher efficiency with smaller hardware than the LRU, Re-Reference Interval Prediction (RRIP) [3] was proposed. It assumes a pattern of repeatedly accessing a small region while scanning a large region as a weakness of the LRU. It prioritizes frequently reused lines and slows the decline of priority to prevent the scan of the large region from evicting the small region. As a result, the cache gets a large number of hits despite existence of scans.

RRIP needs a priority counter of some bits called Re-Reference Prediction Value (RRPV) per cache line. Lines with small number of the counter have high priority and likely to be kept. Following explanation assumes 2-bit counters; the value of the counter with the lowest priority is 3. In Static RRIP (SRRIP), newly inserted blocks have the priorities of the second lowest or 2. They do not become the highest or 0 until the corresponding blocks are reused. Candidates for replacement are the lines with the priorities of 3. If there are no such lines, all the counters in the set are incremented and scanned again.

The rightmost column of Figure 2.3 shows an example of SRRIP. Numbers in the right of columns stand for the priorities. When A and B are reused in the second row, their priorities become 0. In contrast, C has the priority of 2, for it is not reused. Afterwards, on searching for a line to be replaced, it looks for a line with the lowest priority once. Since no such lines exist, all the counters are incremented. Now that the priority of C becomes the lowest, C is selected as the victim. As a result, A and B hits twice and the cache gets four hits per iteration. In addition, although the priorities of A and B are incremented twice in the second iteration (on the insertions of C and D), they are never evicted.

SRRIP has the same problem as the LRU on some access patterns. To cope with it, Bimodal RRIP (BRRIP), where a fraction of inserted lines are given the different priority, and Dynamic RRIP (DR-RIP), which compares SRRIP with BRRIP using Set-Dueling, are proposed. They correspond to the BIP and the DIP for the LRU.

SHiP [24] is based on the SRRIP, reflecting the results of dead block prediction. When inserted lines are predicted dead, they are given the lowest priority and soon will be removed.

Figure 2.4 An example of a 3-way Skewed-associative Cache.

Υ

5

4

0

H<sub>0</sub>

H1

H2

#### 2.1.3 **Improving Associativity**

An ideal full-associative cache, where a cache line can be placed in any block, is able to replace the least prioritized line in the cache at all times. However, common set-associative caches limit the placement of a line to the set (several blocks) according to its address It causes the inequity of usage and affects the efficiency. If frequently used sets and rarely used ones are mixed, fresh lines (likely to be reused) can be soon removed from the cache in one set, while stale lines (unlikely to be reused) stay there in another set.

An obvious way to mitigate the imbalance is to increase the number of ways. However, it has limitations of the rise of the latency and the power consumption, due to the increase of the number of lines accessed at once.

The other, more preferable way is to select the least prioritized line close to globally with keeping the number of ways small. I explain such designs to "improve associativity" [25].

One of the solutions to the inequity is to use a hash function that is randomized well. Considering a tradeoff between the randomness and the latency, it requires both hardware simplicity and enough randomness. It is possible design point to use bitwise XOR of multiple parts of the address rather than its single part. In fact, some commercial processors can use this kind of hash function [26].

Multiple hash functions further improve the inequity. Column-associative Cache [27] is based on a direct-mapped cache, where a cache line has only one candidate for placement, but each address has a primary set and a secondary set calculated by different hash functions. The cache is checked twice if a line is missed in its primary set.

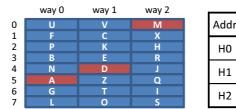

Skewed-associative Cache [28] was proposed almost at the same time as the Column-associative Cache. Each way has a different hash function, and a line has different placement of sets in each way. Figure 2.4 shows a 3-way Skewed-associative Cache which consists of eight sets. The left of the figure stands for the tag array. The characters shown in the array are assumption of the current placement. Each letter represents a different line. The right of the figure shows output of the hash functions. When we insert Y to this, the cache first calculates the set indexes in ways with their respective hash functions.

Figure 2.5 An example of a quest for candidates for eviction in the ZCache.

In the figure, hash functions H0, H1, and H2 correspond to way 0, way 1, and way 2, respectively. As the hash values to Y are 5 for H0, 4 for H1, and 0 for H2, the lines being accessed and becoming the candidates for replacement are set 5 in way 0, set 4 in way 1, and set 0 in way 2; that is, A, D, and M.

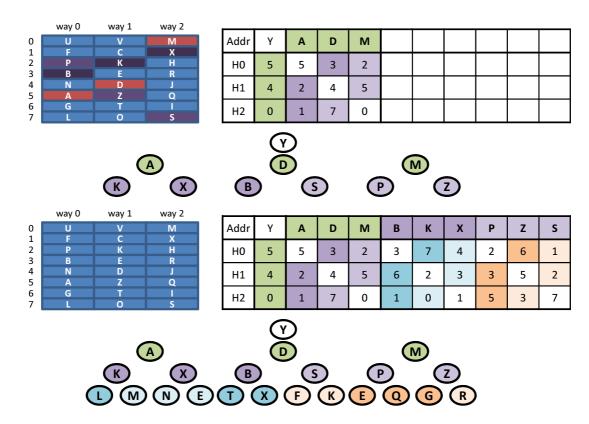

ZCache [25] extended this idea further. It determines the locations of blocks as the same way as the Skewed-associative Cache, it adds the candidates for eviction and thus improves the associativity.

In the Skewed-associative Cache, each line in the candidates for placement of an inserted block has different locations in the other sets than its current one. ZCache allows lines already stored being relocated to the other set. This enables the lines in the candidates for relocation to be added to the candidates for eviction.

Figure 2.5 shows how ZCache adds the candidates for eviction. The contents of the tag array and the inserted line Y are the same as Figure 2.4. First, it calculates the candidates the same way as the Skewed-associative Cache. As I have mentioned, they are A, D, and M. It then calculates their hash value to find their alternative locations. For example, when the hash values to A are 2 for H1 and 1 for H2, it may be relocated to either set 2 in way 1 or set 1 in way 2. This relocation leads to the eviction of K or X. Conversely, K and X are also considered as the candidates for eviction. In similar, B, S; P, and Z are added to the candidates.

Furthermore, by allowing multiple relocations and searching for candidates repeatedly, ZCache increases the number of candidates greatly. It also calculates the indexes of the additional candidates and adds the corresponding lines to the candidates for eviction, as shown in the lower of Figure 2.5. If a 3-way ZCache permits relocations up to twice at a time, the maximum number of candidates is 21. It selects an evicting line from many candidates with a global replacement policy. Afterwards, it replaces and relocates the lines as needed. Assume the evicted line is N, the third from the left in the bottom of the candidates represented in the figure. X is moved where N was; A is located where X was; and then Y is inserted where A was.

Although ZCache greatly improves the associativity with almost the same amount of hardware as set-associative caches, it needs frequent access to the tag array and thus the controller becomes much complex.

As another solution to the inequity, V-Way Cache [29] uses the dynamic cross-reference between tags and data. While tags and data have predefined one-to-one mapping in usual caches, V-Way Cache gives variable mapping with additional per-line storages keeping cross-reference.

The point is that the number of elements in tag array and data array are not necessarily the same. Since an invalid tag does not need to reference data, the number of tags can be bigger than the number of lines in the data array. Even if doing so, the amount of additional hardware is relatively small, for the hardware cost per entry in the tag array is smaller than that in the data array. The idea of having some additional tags is similar to the DCC, the target architecture.

Thanks to extra tags, the most common situation on insertion is that an invalid tag is found but the data array is full. In this case, V-Way Cache can use a global replacement policy (which is different from what I have mentioned in ZCache) to select a line to be evicted. After it decides the evicting line, it invalidates the corresponding tag with reference to the tag array, and then stores the inserted line where the evicted line was. As a result, it benefits from the global replacement, keeping the hit latency low.

#### 2.2 Cache Optimization focusing on Multithread

#### 2.2.1 Thread-aware Replacement Algorithm

The DIP that I have mentioned in Section 2.1.2 cannot apply efficiently to multiple cores or threads as it is. Applying either the LRU or the BIP to all the core implies that the performance of some cores sacrifices for that of the other. On the other hand, permitting each core to choose one of them freely means that the number of candidates for globally optimal policy increases to a power of 2. This makes it impractical or even impossible to sample all the candidates.

Thread Aware DIP (TADIP) [30] presents the multiple ways to find a near-optimal policy by sam-

Figure 2.6 An organization of the utility-based cache partitioning.

pling some of them. It reduces the number of sets needed for sampling to a proportional to the number of cores.

Meanwhile, though most replacement algorithms only focus on the priorities of inserted lines, Promotion/Insertion Pseudo Partitioning (PIPP) [31] also considers those of reused lines. It promotes reused blocks a little, rather than give them the highest priority. It also gets the effect of cache partitioning, which I mention next, with different priorities on insertion by the cores.

#### 2.2.2 Cache Partitioning

Cache partitioning, or allocating shared resource of cache capacity among cores, can be considered as a form of thread-aware replacement algorithms. However, this topic includes many related researches, and so I consider it as a different category.

The points of design of cache partitioning are threefold: an estimation of cache performance, a decision of requirements to be met, and a way to realize allocation.

#### How do they estimate the cache performance?

Dynamic modification to allocations is essential for efficient cache partitioning. The first step for achieving it is to estimate cache performance by the size.

Suh et al. [32] [33] conducted the first such attempts. They estimated the performance by the size with way-divided counters that are incremented on a hit in the corresponding way. A shortcoming of their method is its low precision because using the shared main cache leads to interference of the estimation of each other.

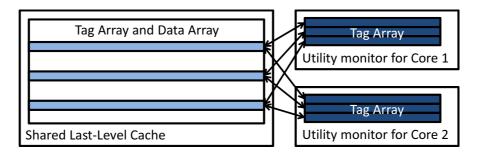

To overcome the flaw of their method, have per-core, independent tag arrays dedicated for estimation can be used. Nevertheless, arrays to the whole cache is impractical in terms of hardware cost. To reduce the cost, Utility-based Cache Partitioning (UCP) [4] and Cache-Partitioning Aware Replacement Policy (CPARP) [34] were proposed. They limit the region of the cache that requires access to the additional tag arrays in different ways.

Figure 2.6 and Figure 2.7 show organizations of the UCP and the CPARP, respectively. Tinted parts

Figure 2.7 An organization of the cache-partitioning aware replacement policy.

represent the portions of the cache used for estimation. Dark-colored parts stand for the additional tag arrays.

The UCP, shown in Figure 2.6, adds tag arrays to a small part of the sets in the cache. The arrays are called Utility Monitors. It reduces the cost of the conflict-free estimation. However, it requires either large amount of hardware or a help by software to decide partitions from them.

On the other hand, the CPARP, shown in Figure 2.7, limits the ways rather than the sets. In other words, it only estimates the performance of the caches when it increases or decreases the current allocations by one way. To estimate the performance on increased allocation, it makes additional tags called Shadow Tags keep the tag of the last evicted line in each set and counts the number of hits in the Shadow Tags. To estimate the performance on decreased allocation, it counts the number of hits in the LRU way of the current allocation. Like the UCP, the CPARP also reduce the hardware cost. Moreover, it is easier to decide new allocations than the UCP. Nevertheless, it gives the wrong estimations to applications that have non-convex relations between the capacity and the performance.

The use of such estimations is not limited to cache partitioning. CRUISE [35] is one of its examples. It reflects the results of the estimation into thread scheduling. It divides the threads into some categories by the estimation. If a pair of threads that harm each other is found, it prevents the threads from being allocated at the same time to cores sharing cache.

#### What is the goal of the partitioning?

Once the cache performance is estimated, what the partitioning methods should consider next is to decide which kind of requirements they aim for. The requirements include performance, fairness, quality of service (QoS), and combinations of them.

Methods for performance try to maximize the total throughput, or typically, to minimize the sum of the number of cache misses. A common barometer of improvement is the sum of the relative IPC (Instruction Per Cycle). They are the mainstream of related work; all the three methods mentioned

above aim for performance.

Methods for fairness want the threads improved equally. Therefore, a typical barometer is the equality of the relative reduction of the number of cache misses. Fair Cache Sharing [36] is one of them. It measures the barometer of performance of each core in a fixed period. If the difference of the barometers between the highest and the lowest exceeds a threshold, a move of partition between them occurs. It presents some different formulas as the barometers.

Some methods for QoS emphasize the elimination of cores that are heavily harmed. Hence, a common standard is the minimum of relative IPC. Some performance-oriented methods also present their QoS-aware variations where cache misses by cores whose performance declines are penalized.

Cooperative Cache Partitioning [37] allows sacrificing temporal performance for average performance. When there are several threads that benefit much from larger caches, it dares to bias the allocations temporarily and rotate them periodically. Although it improves both performance and QoS on average, it requires OS-based complex control.

The other methods for QoS look at its another aspect, that is, their goal is to make the behavior of the caches close to that according to predefined priorities. Iyer proposed a framework named CQoS [38] for caches considering this kind of QoS. It modifies the allocations of the cache according to percore priorities. He confirmed that his framework achieve the different behavior by priorities in some scenarios.

Virtual Private Caches [39] present a way to control allocations of not only the capacity but also the bandwidth of the cache according to priorities, after a method to guarantee QoS in a point of network bandwidth.

Incidentally, an OS-based method that was proposed by Lin et al. [40] is applicable to any of these purposes. It uses different algorithms and performance barometers by purpose. Hsu et al. [41] minutely analyzed interaction of the purposes, and relation between the purposes and performance standards.

#### How do you enforce the assignment?

When the allocation of capacity of each core is determined, the last consideration is how to realize it. The most common enforcement is to limit the number of ways where cores can place their line [42] [43]. It is often called way-partitioning.

Rafique [44] proposed a method to limit the number of lines rather than ways. It counts the current number of lines that belong to each core. When it exceeds the limit, lines in that core are replaced in preference.

Liu et al. [45] proposed a partitioning in bank granularity. They assumed caches that were divided into some banks. They limited banks that first responded to requests of each core so that it balanced performance with power consumption.

The OS-based method by Lin et al. [40], which I have mentioned above, adapts the idea of Page Coloring [46] that modifies mapping of logical address to physical address.

Vantage [47] is based on ZCache [25], which I have mentioned in Section 2.1.3. It divides the whole cache into managed and unmanaged regions. Evicting lines are usually chosen from unmanaged lines. It modifies the per-core threshold for demoting lines from the managed region to the unmanaged region in order to enforce the allocations.

The last kind of enforcements I mention is pseudo enforcements. They do not require precise partitions; they only need some criteria of allocations. Iyer's CQoS [38] presents one of them with probabilities of storing lines in addition to ordinary way-partitioning. PIPP [31] can be categorized here in the point of changing the priorities of inserted lines.

Spilling managements of cooperative caches, which my approach belongs to and I introduce later in this chapter, are also included in pseudo enforcements, though some of them combine way-partitioning.

#### 2.3 Toward Many-core Caching

#### 2.3.1 Non-uniform Cache Architecture (NUCA)

As caches get larger, increase of latency of a single large cache became a problem due to some limitations like wire delay. Instead, to divide it into multiple tiled banks has an advantage in the aspect of average latency, though latency of each access becomes different. These organizations are called Non-uniform Cache Architectures (NUCAs) [48] [49].

In NUCAs, dynamic migrations, which are utilized in D-NUCA [48], NuRAPID [49], etc., further reduces the average latency. It means that frequently accessed lines are relocated to banks that are close to the core, that is, has lower latencies.

Although the target of the first proposal of NUCA is large caches in single-core processors, they suit multicore or many-core processors with a large number of cores very well, because banked organizations prevent the concentration of loads. Therefore, most of the researches in this category adapt a NUCA to multicore and many-core.

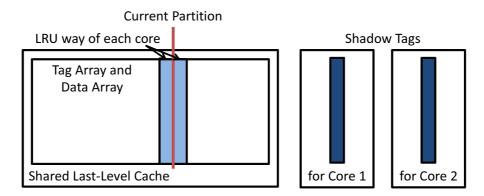

CMP-DNUCA [50] and NUCA Substrate [51] investigate dynamic migrations like D-NUCA in the different organizations of cores and banked cache. Figure 2.8 shows their respective organizations. Each Colored figure represents a bank or a group of banks in the cache.

In single-core processors, the only direction where frequently accessed lines are pulled is where the core is. In contrast, frequently shared lines can be pulled from multiple directions in multicore processors. As a result, such lines are placed in near the mean of locations of cores or close to the core that accesses the lines the most frequently. However, such frequent migrations are wasteful and may leads to inefficient placements.

Figure 2.8 Different NUCA organizations in multicore processors.

Migration-based NUCA, or M-NUCA [52], avoid the problem with frequent migrations. It first detects frequently shared lines, and then counts the number of access from each core to them. Actual migration is not occurred until the cache gathers sufficient information. Thus, it gets placements that are more efficient, in addition to reducing the number of migration.

Victim Replication [53] reduces the average latency not by dynamic migrations but by dynamic replications. When a line is evicted from an L1 cache and a proper placement is found in its local bank of the shared L2 cache, a replica of the evicted line (note that the original have been stored in a remote bank) is placed there. Replicas behave just like Victim Cache [54] of the L1. Since the other cores believe that the L1 in that core still holds the evicted line, the other cores send a request of invalidation or write-back in the usual way. Hence, it keeps coherency in the same way as conventional shared caches, except a part of invalidation or write-back requires a search in the local bank of the L2.

CMP-NuRAPID [55] combines migration and replication. Just like V-Way Cache [29] in Section 2.1.3, it has dynamic cross-reference between tag and data arrays. The tag arrays are private while the data arrays are banked and shared. The tag arrays have many entries for a situation a few cores occupy most of the cache. Proper managements of cross-reference enable migrations and replications. However, they make the coherency control much complex and difficult to implement. In addition, the maximum capacity available to each core is limited by the number of entries in the tag array.

Reactive NUCA [56] applies different strategies of locations by access tendencies with a help of software. It classifies data into instruction, private data, and shared data.

The key ideas of multicore or many-core NUCAs, that is, distributing loads with banked organization and improving the average latency by frequently used data close to the core are similar to those of ccNUMA (Cache Coherent Non-Uniform Memory Architecture) [57] and COMA (Cache-Only Memory Architecture) [58], which used to be studied actively in parallel computers with distributed shared

memory. They allow non-uniform latencies between the memory in a local node and those in the remote nodes. Since each node accesses to its local memory independently, the whole memories in the system are considered to be divided into many banks. Besides, in ccNUMA, a part of local memory is used as a cache to remote memory and thus it improves the average latency. COMA extends this idea. It does not specify the home node of a line: the entire local memory is treated as a cache to remote memory (even if there is only one node in the system that keeps a line). This reduces the number of replicas and thus improves the efficiency.

The difference between NUCAs and ccNUMA or COMA is the target of the ideas: ccNUMA and COMA apply them to main memories of multiprocessors; NUCAs apply them to on-chip caches of multicore or many-core processors. It connects to an important architectural choice. NUCAs hold caches to the main memory that in the slow off-chip location and on-chip caches are more costly resources than node memories. For these reasons, NUCAs have more serious necessity of efficient use of capacity than ccNUMA and COMA. Moreover, in multicore or many-core NUCAs, cores and/or banks of caches are connected via quite fast on-chip communications. Hence, they have a large room for improving the efficiency in capacity and reducing the latency with on-chip communications, like the dynamic migration techniques as I have mentioned.

#### 2.3.2 Scalable Coherence Control

When caches are shared among multiple cores, cache coherency is an important problem. Once a core writes something to a memory address, all the cores must read the written value from that address. In addition, when multiple cores write to the same address, the order of access observed from each core must be identical.

The two major ways to guarantee coherence are snoop-based and directory-based. In a snoop-based coherence scheme, all the caches watch for write operations broadcasted to a bus. If a cache finds a write operation whose address is the same as one of its own lines, it invalidates the stored line because it no longer keeps the latest data. In a directory-based scheme, an additional organization called a directory dedicates itself to coherence. All the cores beg permission from the directory before newly accessing the cache. The directory sends requests of invalidation or write-back to the corresponding cores if needed. After that, it gives permission to the requesting core.

While snoop-based schemes are preferred by processors with a small number of cores, directory-based schemes are favored by those with a large number of cores. Although snooping is good at latency, frequent broadcasts limit the scalability. In consequence, they suit a small core count. On the other hand, directories hardly harm the scalability but make the best-case latency longer, for all the requests must be done through the directories.

As cooperative caches seek the advantages of both private and shared caches, Token Coherence [59]

tried to achieve the advantages of both snoop-based and directory-based schemes. There coherency is controlled by a number of tokens managed by address. Permissions of read or write operations are given when the core has at least one token or all of the tokens, respectively. It is applicable to some interconnections where snooping is impossible or impractical. However, its properties are means between snoop-based and directory-based with the same interconnections, that is, it is not so good at either latency or scalability.

Most directory-based coherence schemes for multicore and many-core use directory caches, which store the directories corresponding only to the cached region in the memory. Some recent methods for directory caches try to reduce their hardware amount in anticipation of the future many-core era.

SPACE [60] regards it as a problem that each entry in conventional directory caches has a vector of the same bits as the number of cores, which represents the cores sharing the corresponding line. Since the number of typical sharing patterns is much smaller than that of possible patterns, it compresses the vector to reduce the length of the entry.

WAYPOINT [61] reduces the performance loss when directory caches are filled. To balance hard-ware cost with performance overhead, it enables information of directory caches to be stored to the regular caches too. My approach also has interest in conflicts in the directory caches. The difference of strategies between WAYPOINT and mine is described in Chapter 4 in detail.

Cuesta et al. [62] proposed an OS-based method that achieved both the reduced number of entries of directory caches and the improved performance by limiting the region managed by the directory caches. TLB (Translation Lookaside Buffer) keeps which pages have been shared. If the page that a requested line belongs to has been not shared, the cache can directly send a request of the line to the main memory. However, when such a page starts being shared, all the cached lines in the page must be managed by the directory caches through gathering information about them from the whole cache, or simply be discarded from the cache. After that, the lines start to be under the management of the directory caches as usual. This method works well especially if the private memory region of cores are divided in a unit larger than a page. Nevertheless, it does not suit the methods with replications or migrations, which I have mentioned in Section 2.3.1.

#### 2.4 Cooperative Caches and their Optimization

#### 2.4.1 Overview of Cooperative Caches

NUCAs for multicore or many-core processors, which I have explained in Section 2.3.1, are regarded as methods that enable shared caches to benefit from an advantage of low latency of private caches. In contrast, cooperative caches add an advantage of shared caches or flexibility on capacity to private caches.

Chang et al. proposed the Cooperative Caching [5], the first organization of cooperative caches. The term Cooperative Caching itself is invented in a context of caching of file systems [63], rather than that of processors. In this context, when a piece of cached information is about to be removed, the node transfers it to another node up to fixed times if no nodes have its replica. This enables file systems to store much unique data and to serve frequently used data quickly to the users. Chang et al. extend this idea to caching of processors. Namely, when a cache line is about to be evicted from the chip, the cache allows it being migrated (or *spilled*) to another cache if no other caches have its duplicate.

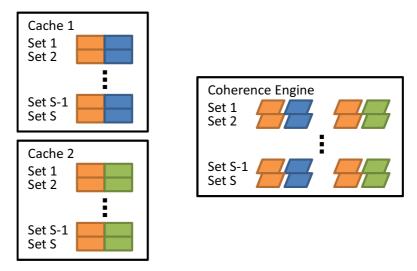

The Cooperative Caching has a single centralized organization called Coherence Engine, which stores duplicate tags of all the cache line in the chip. However, concentration of access to the centralized unit limits the scalability.

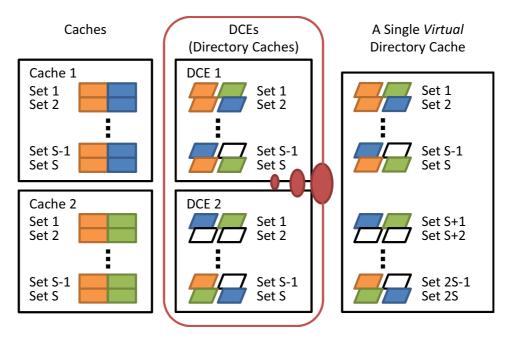

The Distributed Cooperative Caching (DCC) [6] divides the unit into a number of Distributed Coherence Engines (DCEs) and distributes them over the chip. Each DCE is partial directory cache, that is, it manages coherency of an interleaved part in the address space.

In the rest of this thesis, I often call a directory cache just 'a directory' to avoid the confusion with the regular caches. In addition, I use a term 'a line' or 'a cache line' for a block in the regular caches; I use 'an entry' or 'a directory entry' for an element in the directory caches (or the DCEs).

Although the CC and the DCC suppose directory-based coherence, the idea of spilling is also applicable to snooping, which is usually used for a small number of cores. Therefore, some methods to optimize spilling, which I mention in the next section, depend on snooping.

#### 2.4.2 Distributed Cooperative Caching

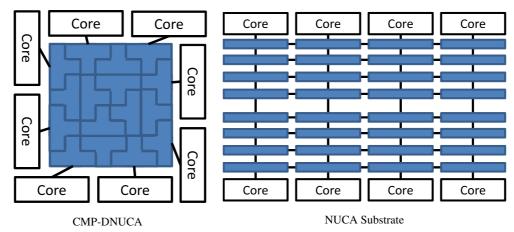

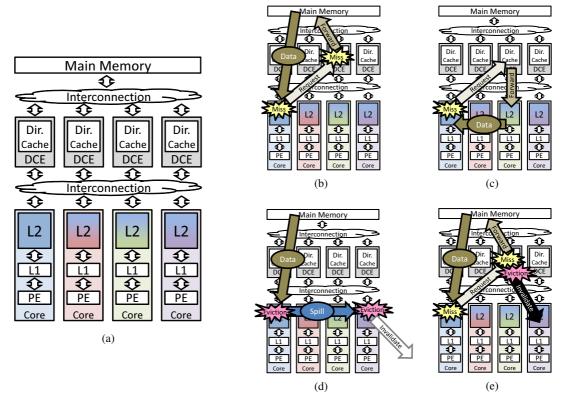

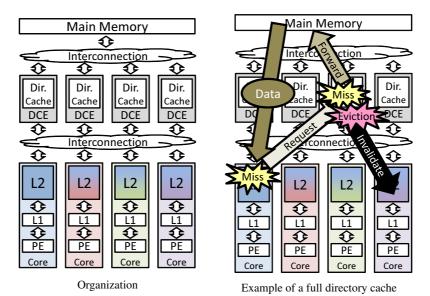

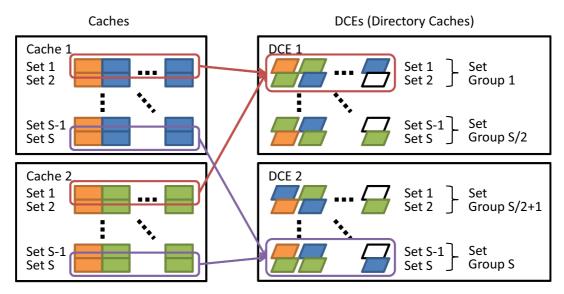

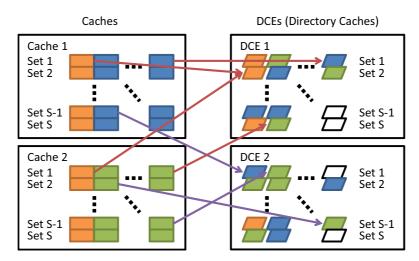

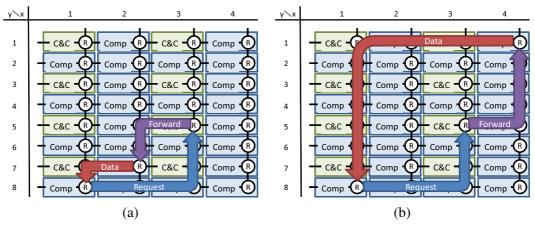

Figure 2.9 (a) shows the organization of the DCC, where L2 caches are the last level. Each core has a PE (Processing Element), L1 caches, and an L2 cache. DCEs are distributed over the chip. Although the number of cores and that of DCEs are not necessarily the same, both of them are 4 in Figure 2.9 for ease of the figure. The cores, the DCEs, and a main memory are connected via some interconnects.

I explain typical behavior of the DCC with from (b) to (e) in Figure 2.9.

First of all, I assume a situation that both an empty line in a cache and an empty entry in a DCE are found. Example (b) shows the behavior when a core misses in its own L2 and no other cores have the requested line. The core sends a request to one of the DCEs specified by the line address. The requested DCE searches for a valid entry corresponding to the line. However, it does not have such an entry. Therefore, it writes the tag and some supplementary information to an empty entry while it forwards the request to the main memory. The main memory supplies the required data to the core.

On the other hand, if the requested line hits in one of the remote core, that is, it has already been kept by another core (other cores), the behavior is like Example (c). The requested DCE checks its directory cache in the same way as Example (b). Since a valid entry is found this time, the request is forwarded

Figure 2.9 The organization and working examples of the Distributed Cooperative Caching.

to one of the sharer rather than the main memory. It modifies the entry so that the requester is added to the sharer. When the core receives the forwarded request, it transfers its own line to the requesting core via cache-to-cache interconnection. In this case, the cooperative caches avoid the access to the main memory, and thus reduce the latency.

Secondly, I assume that there is an empty directory entry but no empty cache lines are found. Example (d) shows the behavior in such a situation. To store the requested line, one of the lines in the same set as the requested line is chosen and evicted. The most important feature of the cooperative caches is to allow the evicted line spilled to another core. When doing so, the core forwards the line to one of the other cores of its choice and notifies the occurrence of spilling to the corresponding DCE . The DCE properly modifies the sharer stored in the entry.

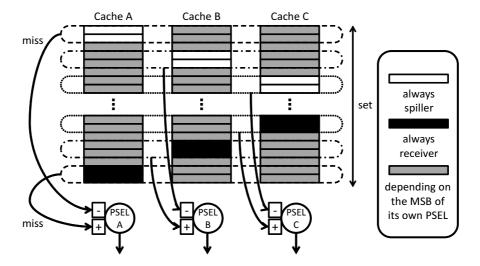

When the core receives a spilled line, if it has no empty lines in the set where the spilled line is going to be kept, one of the lines is also evicted. To avoid ripple effects, the hereby evicted line is prohibited from spilling: the line is just evicted from the chip.