### T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

#### 論文 / 著書情報 Article / Book Information

| 題目(和文)            |                                                                                                                                                                                                |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | Threshold voltage control technology in metal/high-k pFET consisting of high germanium content SiGe channel and fixed charge/oxygen vacancy control in gate stack                              |

| 著者(和文)            | 山口晋平                                                                                                                                                                                           |

| Author(English)   | Shimpei Yamaguchi                                                                                                                                                                              |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第10986号,<br>授与年月日:2018年9月20日,<br>学位の種別:課程博士,<br>審査員:若林 整,筒井 一生,渡辺 正裕,大見 俊一郎,角嶋 邦之                                                                        |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第10986号,<br>Conferred date:2018/9/20,<br>Degree Type:Course doctor,<br>Examiner:,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                           |

| Type(English)     | Doctoral Thesis                                                                                                                                                                                |

# Threshold voltage control technology in metal/high-k pFET consisting of high germanium content SiGe channel and fixed charge/oxygen vacancy control in gate stack

by

#### Shimpei Yamaguchi

Bachelor of Science, The University of Tokyo (2002)

Master of Science, The University of Tokyo (2004)

Submitted to the

Department of Electronics and Applied Physics

in partial fulfillment of the requirements

for the degree of

Doctor of Philosophy in Engineering

at the

TOKYO INSTITUTE OF TECHNOLOGY

July 27, 2018

| Signature of Autho | r                                                            |

|--------------------|--------------------------------------------------------------|

|                    | Department of Electronics and Applied Physics, July 27, 2018 |

|                    |                                                              |

|                    |                                                              |

| Certified by       |                                                              |

|                    | Hitoshi Wakabayashi, Professor, Thesis Supervisor            |

Threshold voltage control technology in metal/high-k pFET consisting of high germanium content SiGe channel and fixed charge/oxygen vacancy control in gate stack

by Shimpei Yamaguchi

Submitted to the

Department of Electronics and Applied Physics

on July 27, 2018, in partial fulfillment of the

requirements for the degree of

Doctor of Philosophy in Engineering

#### **Abstract**

In advanced complementary metal oxide semiconductor (CMOS) technology, metal gate electrode and high-k gate dielectric have been introduced from 45nm node to overcome gate leakage issue with conventional silicon dioxide (SiO<sub>2</sub>) film and enable further area scaling. One of the challenges associated with metal gate / high-k gate dielectric technology has been a control of threshold voltage of field effect transistor (FET), especially p-type FET (pFET). In gate-first integration, where metal gate / high-k dielectric stack is formed before junction formation, high thermal budget (activation anneal) is applied to gate stack and effective work function (eWF) of pFET typically shifts to mid-gap direction and cannot provide sufficiently low threshold voltage (V<sub>T</sub>). To achieve practical pFET V<sub>T</sub>, two solutions have been proposed against this problem, one is gate-last or replacement metal gate (RMG) technology where gate stack is formed after high thermal treatment by replacing dummy poly silicon gate and SiO<sub>2</sub> gate dielectric with metal gate and high-k gate dielectric. The metal gate and high-k dielectric stack doesn't receive high thermal budget, therefore effective work function can be kept high.

Another solution is to implement silicon germanium ( $Si_{1-x}Ge_x$ ) in the channel of pFET.  $Si_{1-x}Ge_x$  is typically grown on Si substrate by epitaxy. Thanks to its higher valence band energy, pFET  $V_T$  is reduced without modifying gate stack itself.

In first part of this thesis, eWF control technique using gate stack engineering is discussed. The base process is gate-last FinFET devices. Even with gate-last or RMG integration scheme, a recent report highlighted effective work function lowering (shift towards mid-gap) in scaled equivalent oxide thickness (EOT) region (EOT < 10 Å). Therefore, it is still highly important to push the eWF further towards valence band edge to achieve lower pFET V<sub>T</sub> at scaled EOT region. Here we identified post sacrificial-Si deposition anneal (called WF setting anneal in this thesis) as key enabler for low pFET V<sub>T</sub> at scaled EOT in this work. And we revealed two mechanisms to explain pFET V<sub>T</sub> reduction. One is fixed charge generation at the interface between high-k dielectric and metal gate electrode. The intermixed layer created in-between titanium nitride (TiN) electrode and hafnium dioxide (HfO<sub>2</sub>) gate dielectric during WSA has negative fixed charges and therefore they reduce pFET V<sub>T</sub>. The other mechanism is passivation of oxygen vacancies (positively charged) in the HfO<sub>2</sub> film by supplying oxygen from TiN electrode during WSA. We could achieve approximately 140 mV pFET V<sub>T</sub> reduction by optimizing WSA process without compromising device performance and scalability.

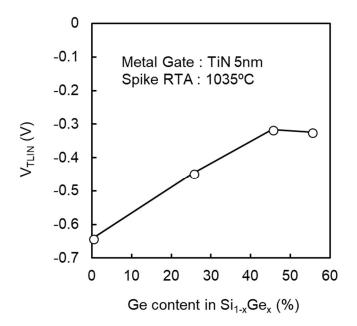

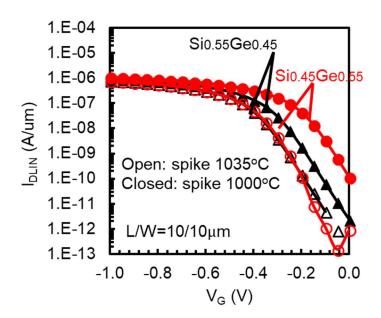

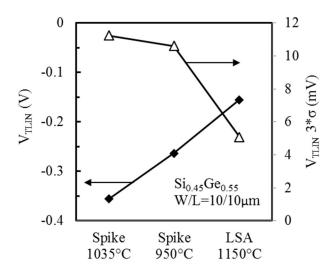

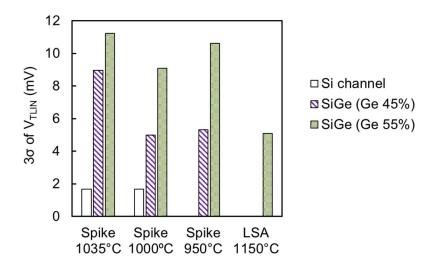

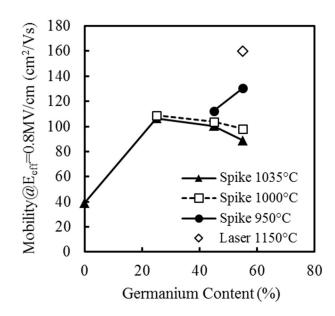

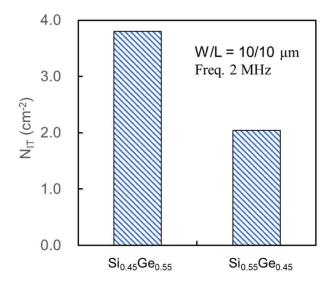

In second part of the thesis,  $Si_{1-x}Ge_x$  channel devices have been fabricated and pFET  $V_T$  reduction was pursued by increasing Ge contents in the channel and reducing process thermal budget concurrently. Although lower process temperature had been identified as process knob to enable low pFET  $V_T$  in  $Si_{1-x}Ge_x$  channel transistor, there were very few reports on successful integration to realize high performing devices at scaled gate length. Therefore, we also focused on the device scaling and performance boost for high Ge

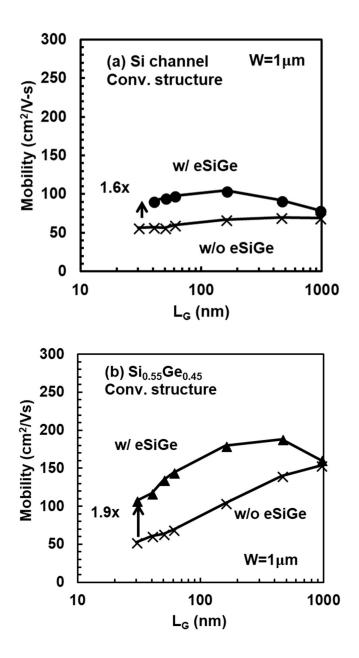

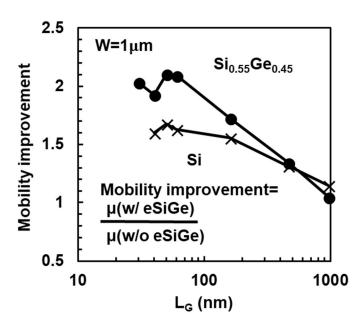

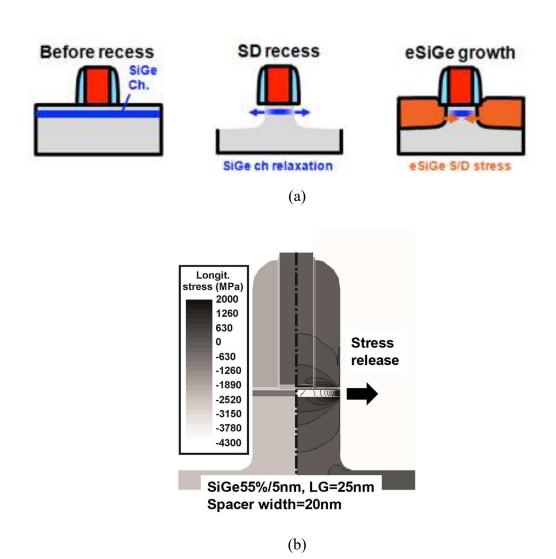

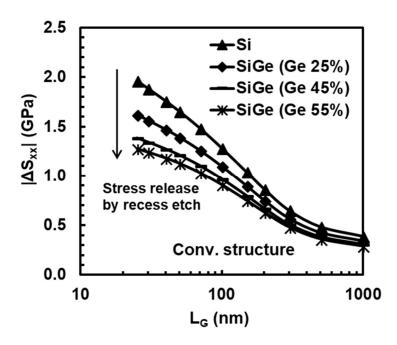

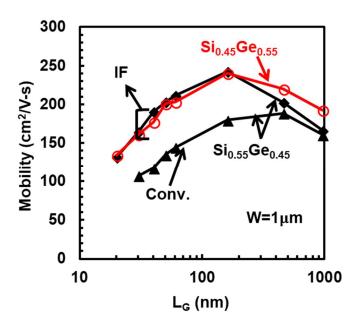

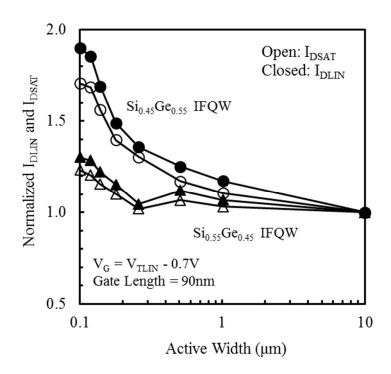

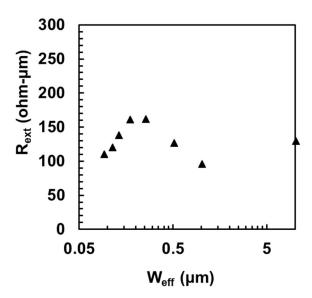

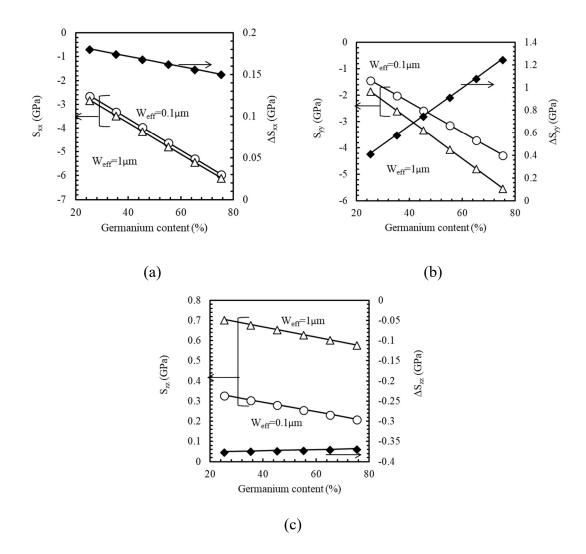

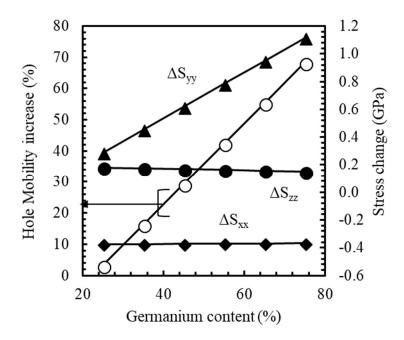

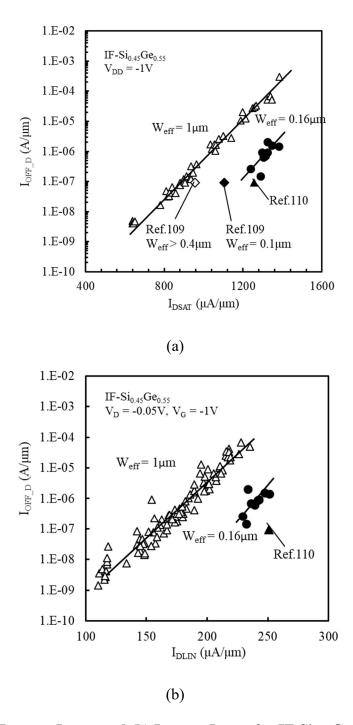

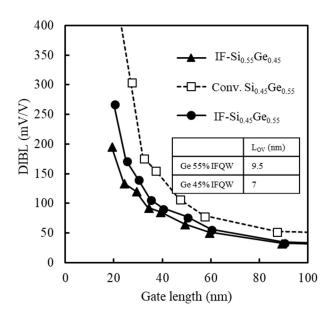

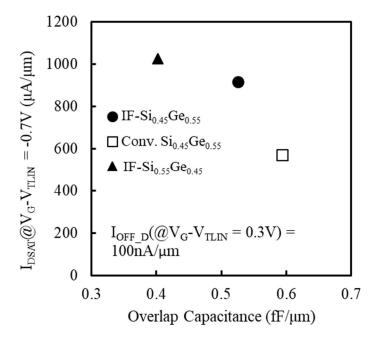

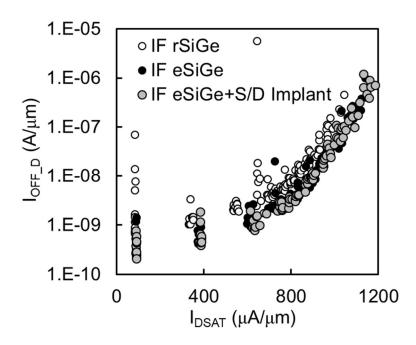

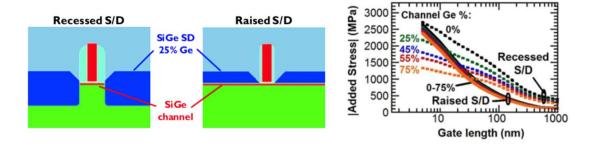

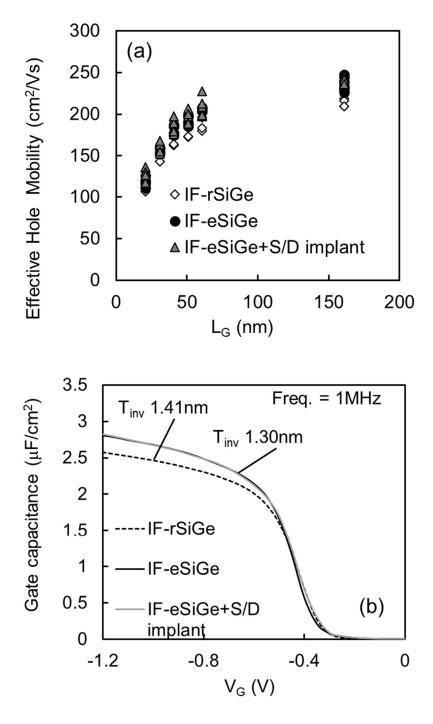

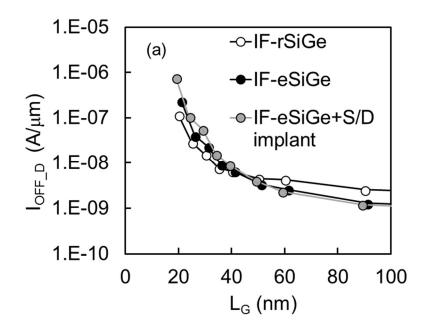

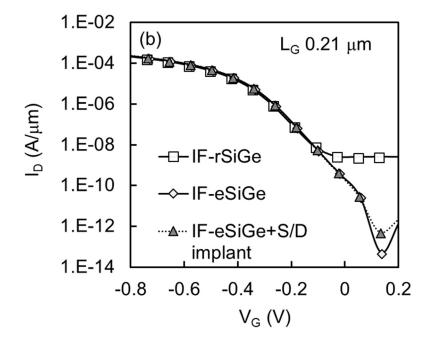

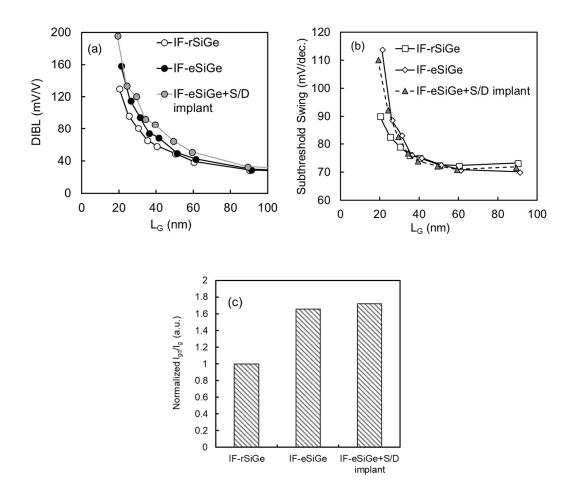

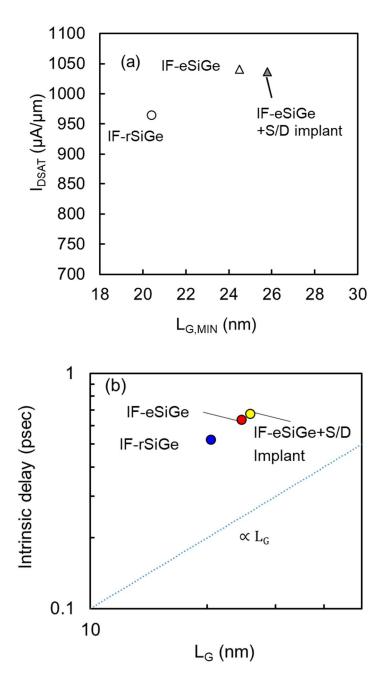

content (Ge > 50%) Si<sub>1-x</sub>Ge<sub>x</sub> pFET. We systematically investigated the impact from thermal budget and Ge content in Si<sub>1-x</sub>Ge<sub>x</sub> on pFET V<sub>T</sub>, carrier mobility, and off-state leakage current and found out that lower temperature process is also a key to achieve high mobility and performance on Si<sub>1-x</sub>Ge<sub>x</sub> channel devices. From this viewpoint, we set our focus on so-called implant free (IF) structure which has in-situ boron doped epitaxial layer as extension and source/drain hence doesn't need high temperature activation anneal. Furthermore, strain effects for Si<sub>1-x</sub>Ge<sub>x</sub> channel has been deeply investigated to enhance the device performance. One effect is an interaction between Si<sub>1-x</sub>Ge<sub>x</sub> channel and embedded silicon germanium (eSiGe) stressor. It was found that eSiGe stressor can give similar performance boost for Si<sub>1-x</sub>Ge<sub>x</sub> channel as well despite of the stress relaxation in longitudinal direction during cavity recess. The other effect is channel width dependence and we confirmed that hole mobility is significantly enhanced at narrower channel width thanks to the relaxation of channel strain in transvers direction. By utilizing these strain engineering, we could achieve the best-in-class performance with SiGe channel device with extremely high Ge content (55%). In the last section of Si<sub>1-x</sub>Ge<sub>x</sub> channel discussion, scalability of Si<sub>1-x</sub>Ge<sub>x</sub> channel device is discussed. We could demonstrate decent device performance at very short gate length (approximately 20nm, which is close to state-ofthe-art FinFET technology) thanks to shallow junction by IF structure with Ge 45% SiGe channel.

In summary, two independent approaches for pFET V<sub>T</sub> reduction in metal gate/high-k transistor were discussed. One is fixed charge and oxygen vacancy control by PSA process in gate-last process. Another is introduction of Si<sub>1-x</sub>Ge<sub>x</sub> channel with high Ge content in gate-first process. Integration of Si<sub>1-x</sub>Ge<sub>x</sub> channel with high Ge content was enabled by so-called IF structure by reducing thermal budget of the flow.

#### **Contents**

| Chapter 1 Research Background and Introduction of this work                                  | 3  |

|----------------------------------------------------------------------------------------------|----|

| 1.1 Complementary metal oxide semiconductor (CMOS) technology                                | 3  |

| 1.2 CMOS scaling (Dennard scaling, Moore's law)                                              | 5  |

| 1.3 Gate stack scaling, metal gate and high-k dielectric technology                          | 12 |

| 1.4 pFET V <sub>T</sub> control method                                                       | 18 |

| 1.5 The scope of this thesis                                                                 | 25 |

| Chapter 2 pFET effective work function control techniques in RMG                             | 27 |

| 2.1 Background                                                                               | 27 |

| 2.2 Device fabrication flow                                                                  | 27 |

| 2.3 Threshold voltage control by introduction of fixed charge layer                          | 29 |

| 2.4 Threshold voltage control by oxygen vacancy density modulation                           | 36 |

| 2.5 Summary                                                                                  | 43 |

| Chapter 3 Process temperature impact on Si <sub>1-x</sub> Ge <sub>x</sub> channel transistor | 47 |

| 3.1 Background                                                                               | 47 |

| 3.2 Transistor structures studied in this work                                               | 47 |

| 3.3 Device fabrication flow                                                                  | 49 |

| 3.4 Thermal stability of Si <sub>1-x</sub> Ge <sub>x</sub> channel                           | 52 |

| 3.5 Threshold voltage of Si <sub>1-x</sub> Ge <sub>x</sub> channel pFET                      | 56 |

| 3.6 High field hole mobility of Si <sub>1-x</sub> Ge <sub>x</sub> channel pFET               | 62 |

| 3.7 Off-state leakage for Si <sub>1-x</sub> Ge <sub>x</sub> channel pFET                     | 68 |

| 3.8 Summary                                                                                  | 71 |

| Chapter 4 Strain effect in Si <sub>1-x</sub> Ge <sub>x</sub> channel pFET                    | 73 |

| 4.1 Background                                                                               | 73 |

| 4.2 Interaction between Si <sub>1-x</sub> Ge <sub>x</sub> channel and eSiGe:B stressor                       |

|--------------------------------------------------------------------------------------------------------------|

| 4.3 Channel width dependence for IF-Si <sub>1-x</sub> Ge <sub>x</sub> pFETs due to elastic strain relaxation |

|                                                                                                              |

| 4.4 DC performance benchmark for IF-Si <sub>0.45</sub> Ge <sub>0.55</sub> channel pFETs with eSiGe stresso   |

| 92                                                                                                           |

| 4.5 Summary                                                                                                  |

| Chapter 5 Scalability of Si <sub>1-x</sub> Ge <sub>x</sub> channel pFETs                                     |

| 5.1 Background                                                                                               |

| 5.2 Short channel control comparison between conventional and IF-Si <sub>1-x</sub> Ge <sub>x</sub> channel   |

| pFET97                                                                                                       |

| 5.3 Short channel control comparison between IF-Si <sub>1-x</sub> Ge <sub>x</sub> channel pFET with and      |

| without eSiGe stressor                                                                                       |

| 5.4 Summary                                                                                                  |

| Chapter 6 Conclusions and Future Direction                                                                   |

| 6.1 Conclusions 113                                                                                          |

| 6.2 Future direction                                                                                         |

| References                                                                                                   |

| List of Publications and Presentations                                                                       |

| Acknowledgements                                                                                             |

### **Chapter 1 Research background and introduction of this work**

#### 1.1 Complementary metal oxide semiconductor (CMOS) technology

CMOSFET (Complementary Metal Oxide Semiconductor Field Effect Transistor) is the most commonly used technology for constructing very-large-scale-integration (VLSI) circuits, which was originally invented by Wanlass and Sah (Fairchild) in 1983 [1]. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for several analog circuits such as image sensors (CMOS sensor), data converters, and highly integrated transceivers for many types of communication.

CMOS has pairs of p-type and n-type MOSFETs (pMOSFET/pFET and nMOSFET/nFET, respectively), which are constructed simultaneously on the same Si substrate. A CMOS circuit typically consists of an nFET and pFET connected in series between the power supply terminals, so that there is negligible standby power consumption [2]. Since one transistor of the pair is always off, the series combination draws significant power only momentarily during switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other components of logic, for example transistor–transistor logic (TTL) and nMOSFET logic, which normally have some standing current even when not changing state. CMOS also allows a high density of logic functions on a chip, as circuits are designed to minimize active power dissipation. It was primarily for this reason that CMOS became the most used technology to be implemented in VLSI chips.

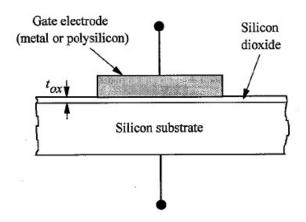

The basic MOS structure consists of a conducting gate electrode (metal or heavily

doped poly-Si) on top of a thin layer of SiO<sub>2</sub> grown on a Si substrate or deposited dielectric film, as shown in Figure 1-1 [3].

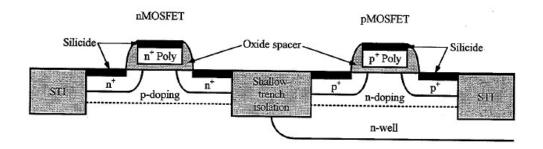

A typical cross section of modern CMOSFET is shown in Figure 1-2 [3]. On top of p-type Si substrate, nFET (conducting carrier is electron) and pFET (conducting carrier is hole) are fabricated simultaneously. nFET consists of n-type poly-Si gate electrode, gate oxide dielectric, p-type Si channel/well, and n-type source and drain electrode. Likewise, pFET consists of p-type poly-Si gate electrode, gate oxide dielectric, n-type Si channel/well, and p-type source and drain electrode. Metal silicide (typically NiSi<sub>x</sub>, TiSi<sub>x</sub>, and CoSi<sub>x</sub>) is formed on the poly-Si gate and on the source and drain areas. Each transistor is electrically isolated by shallow trench isolation (STI, SiO<sub>2</sub> is filled in the trench).

Figure 1-1 A schematic cross section for a MOS structure [3].

Figure 1-2 A schematic cross section for modern CMOS transistors [3].

#### 1.2 CMOS scaling (Dennard scaling, Moore's law)

CMOS technology evolution in past decades has been supported by transistor scaling which provides density, speed and power improvements simultaneously. Transistor scaling has been enabled by the continuous advancement of lithographic technology. Reducing the transistor channel length leads to so-called short channel effects. The most undesirable short channel effect is a reduction in the gate  $V_T$  at which the device turns on, especially at high drain voltages and resultant leakage current increase. For successful advancement of CMOS technology, not only the progress of lithographic technology but also the device architectural optimization has been required to suppress short channel effect.

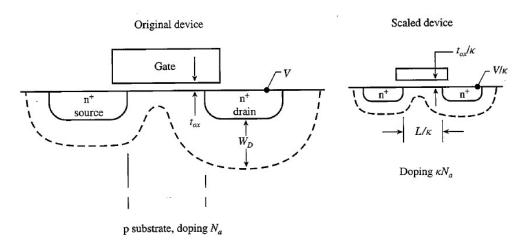

R. H. Dennard proposed constant-field scaling in 1974 [4], where one can keep short channel effects under control by scaling down the vertical dimensions (gate oxide dielectric thickness, junction depth, etc.) along with the horizontal dimensions, while also proportionally decreasing the applied voltages and increasing the substrate doping concentration (decreasing the depletion width). This is shown in Figure 1-3 [4].

Figure 1-3 Principles of MOSFET constant-field scaling [4].

Table 1-1 shows the scaling rules for various device parameters and circuit performance factors. The doping concentration  $(N_a, N_d)$  must be increased by the scaling factor  $\kappa$  in order to scale depletion layer width  $(W_d)$  by factor of  $1/\kappa$ , where  $W_d$  is expressed in approximate form as

$$W_D \sim \sqrt{\frac{2\varepsilon_{Si}V_{dd}}{qN_a}} \tag{1-1}$$

All capacitances scale down by  $\kappa$ , since they are proportional to area and inversely proportional to thickness. The drift current per MOSFET channel width,  $I_{drift}/W$

$$\frac{I_{drift}}{w} = Q_i v = Q_i \mu E \tag{1-2}$$

is unchanged with scaling, as inversion charge  $Q_i = CV$  is unchanged with scaling either. Therefore, the circuit delay,  $\tau = CV/I$  scales down by  $\kappa$ . This is the most important conclusion of constant-field scaling: once the device dimensions and the power supply voltage are scaled down, the circuit speeds up by the same factor. Moreover, power dissipation per circuit, which is proportional to VI, is reduced by  $\kappa^2$ , while power density remains unchanged in the scaled-down chip. The constant field scaling described above is known as Dennard's scaling.

Table 1-1 Constant field scaling: MOSFET device and circuit parameters [3, 4].

|                     | MOSFET device/circuit parameters              | Multiplicative        |

|---------------------|-----------------------------------------------|-----------------------|

|                     |                                               | factor $(\kappa > 1)$ |

| Scaling assumptions | Device dimensions $(t_{ox}, L, W, x_j)$       | $1/\kappa$            |

|                     | Doping concentration $(N_a, N_d)$             | $\kappa$              |

|                     | Voltage (V)                                   | $1/\kappa$            |

| Device parameters   | Electric field (E)                            | 1                     |

| Device parameters   | Carrier velocity (v)                          | 1                     |

|                     | Depletion-layer width (W <sub>d</sub> )       | $1/\kappa$            |

|                     | Capacitance ( $C = \varepsilon^A/t$ )         | $1/\kappa$            |

|                     | Inversion layer charge density (Qi)           | 1                     |

|                     | Current, drift (I)                            | $1/\kappa$            |

|                     | Channel resistance (R <sub>ch</sub> )         | 1                     |

| Circuit parameters  | Circuit delay time ( $\tau = CV/I$ )          | $1/\kappa$            |

|                     | Power dissipation per circuit ( $P \sim VI$ ) | $1/\kappa^2$          |

|                     | Power-delay product per circuit $(P\tau)$     | $1/\kappa^3$          |

|                     | Circuit density ( $\propto 1/A$ )             | $\kappa^2$            |

|                     | Power density (P/A)                           | 1                     |

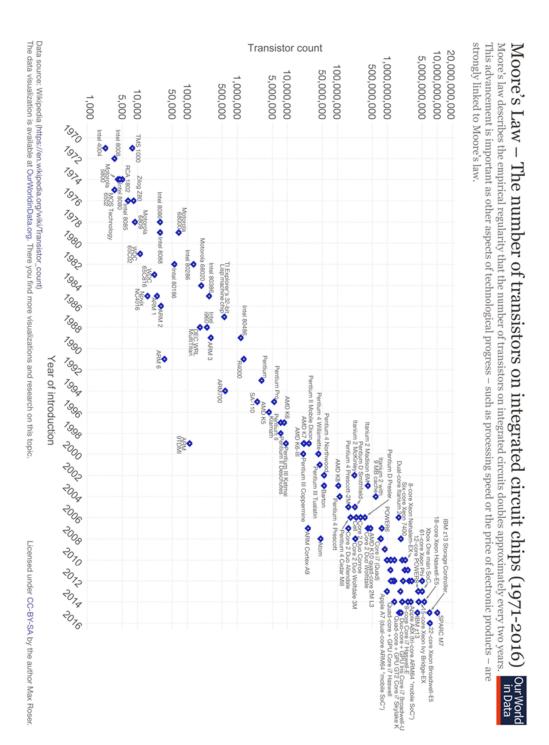

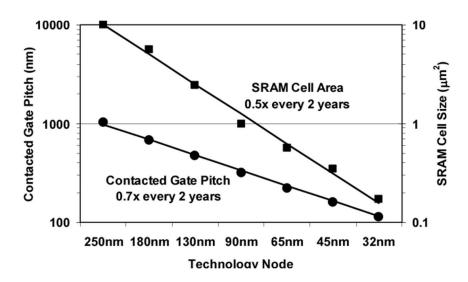

As a result of continuous device scaling, one could observe that the number of transistors in a VLSI circuit doubles about every 1.5 year as shown in Figure 1-4 [5], which is known as Moore's law, which was named after Gordon Moore, the co-founder of Fairchild Semiconductor and Intel [6]. Moore's law can be demonstrated in actual transistor size the best represented in form of contacted gate pitch (CPP) or SRAM cell size as shown in Figure 1-5 [7]. The dimensions of transistor typically have been scaled down by approximately 0.7x in each node, and SRAM cell size has been scaled down by 0.5x in each node. Moore's prediction proved accurate for several decades and has been used in the semiconductor industry to guide long-term planning and to set targets for research and development.

Figure 1-4 Transistor number per chip versus year of introduction demonstrating

Moore's law [5].

Figure 1-5 Contacted gate pitch (left axis) and SRAM cell size (right axis) versus technology node from 250 nm down to 32 nm node [7].

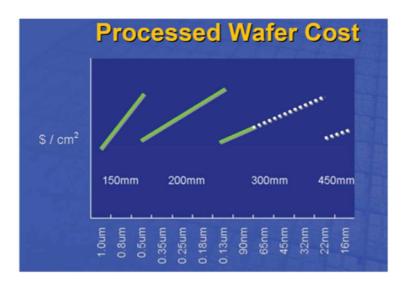

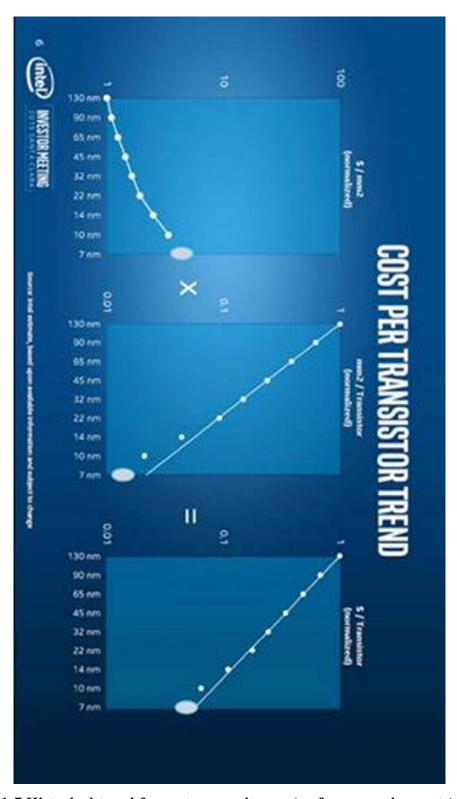

Moore's law can be rephrased as "costs per transistor is reduced by half about every 1.5 years, as long as wafer processing costs is identical", as the costs per transistor (CPT) can be expressed as CPT = (wafer processing costs) / (number of transistors on the wafer). Historically, wafer-processing costs tended to increase from one generation to the next due to multiple reasons such as introduction of new process, device structures, etc. This offset the increase in number of transistors per area by scaling and slowed down the scaling rate for CPT. Semiconductor industry has been dealing with this issue by migrating to larger wafer sizes, which could sharply reduce wafer processing costs. The net effect was nearly constant with only slight increases in wafer processing costs, as shown in Figure 1-6 (source: Intel). However, after migrating from 200 mm to 300 mm wafer in 130-nm or 90-nm node, the industry hasn't been able to migrate to 450 mm wafer. Therefore, wafer processing cost has kept increasing in every new technology node. Due to this issue, area scaling needs to be accelerated even more

than conventional area scaling, to keep CPT scaling. Figure 1-7 is historical trend for costs per unit area (wafer processing costs), area per transistor, and CPT presented by Intel. They accelerated the area scaling rate from 14 nm node technology to overcome the increasing wafer processing costs by introducing so-called hyper-scaling which can realize more shrinkage rate for standard cell than conventional CPP × MxP (MxP: Metal pitch) scaling.

Figure 1-6 Historical trend for wafer processing costs. The cost increase due to new process generation can be offset by introduction of larger wafer sizes (Source: Intel).

Figure 1-7 Historical trend for costs per unit area (wafer processing costs), area per transistor, and cost per transistor (source: Intel).

#### 1.3 Gate stack scaling, metal gate and high-k dielectric technology

In this section, we will review gate stack scaling ( $T_{inv}$  scaling) and introduction of metal gate/high-k dielectric technology. As described in Table 1-1,  $T_{inv}$  is scaled down continuously as part of the constant field scaling of the MOSFET. In constant field scaling, supply voltage  $V_{dd}$  scales down by factor of  $\kappa$ , therefore  $T_{inv}$  is scaled down as well by factor of  $\kappa$  to keep vertical electric field constant. Especially in advanced technology node,  $T_{inv}$  needs to be scaled down aggressively to enable gate length scaling and maintain manageable short channel effect.

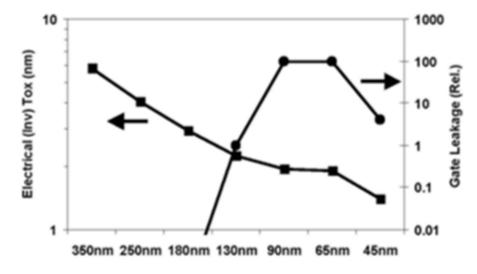

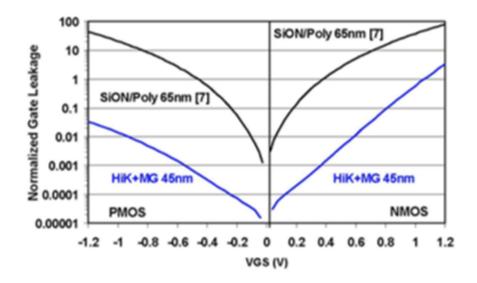

In earlier technology nodes, SiO<sub>2</sub> and silicon oxynitride (SiON) had been used as gate dielectric material thanks to its decent interfacial property at Si surface (low interfacial trap density) and large band gap. However, since around 90-nm node technology, SiON stopped scaling down further due to increasing gate leakage current, which is shown in Figure 1-8 [8]. From 180-nm node technology, gate leakage current increased exponentially due to direct tunneling current, which is dominant in this thickness regime (below 2 nm). SiON gate dielectric thickness reached its limit in 90 nm node technology and couldn't be scaled down further in 65 nm node due to severe gate leakage current which leads to high power consumption. To overcome this situation, high-k gate dielectric and metal gate electrode have been introduced from 45 nm node technology by Intel [8, 9]. High-k gate dielectric has larger dielectric constant than SiO<sub>2</sub> (dielectric constant 3.9) [10, 11, 12], therefore scaled T<sub>inv</sub> can be realized even with thicker physical thickness than SiO<sub>2</sub> and gate leakage current can be suppressed as shown in Figure 1-9 [8].

Development efforts have focused on finding a material with a requisitely high dielectric constant that can be easily integrated into a Si-based VLSI manufacturing process. Key considerations include band alignment to Si (which may alter gate leakage current) [13, 14], film morphology [15], thermal stability [16, 17, 18], maintenance of a high mobility of charge carriers in the channel and minimization of electrical defects in the film/interface [19, 20, 21]. In these regards, Hafnium-based dielectric (HfO<sub>2</sub>, HfSiO<sub>x</sub>) is now the most commonly used high-k dielectric material in the industry. Dielectric constant of HfO<sub>2</sub> is ranging approximately from 16 to 20 [10, 11, 12].

For the gate electrode, the industry had been using n+ or p+ poly-Si for nFET and pFET respectively. The problem of using n+/p+ poly-Si gate is depletion layer created in the poly-Si gate when the transistor is turned on, which became considerable portion of total  $T_{inv}$  in advanced node [22]. The depletion-layer thickness can be reduced by increase in implant dose so that the poly-Si is degenerated. However, strip of photo resist would be impossible with such implant dose due to severe crusting. Metal gate can completely eliminate depletion layer while avoiding this issue and promote further  $T_{inv}$  scaling.

Figure 1-8 Historical trend for  $T_{\rm inv}$  and gate leakage current over past several technology nodes from 350 nm node down to 65 nm node [8].

Figure 1-9 Gate leakage current for Poly-Si/SiON gate stack (65 nm node) and high-k/meal gate (45 nm node) showing significant reduction [8].

Among two integration schemes for metal gate/high-k technology (gate-first, gate-last/RMG), gate-first was the mainstream scheme in research phase because of their relatively lesser degree of integration difficulty especially when thin metal gate is inserted between poly-Si and high-k dielectric so that gate patterning RIE (reactive ion etching) is not severely affected (Metal Inserted Poly Silicon Gate: MIPS Gate) [23, 24].

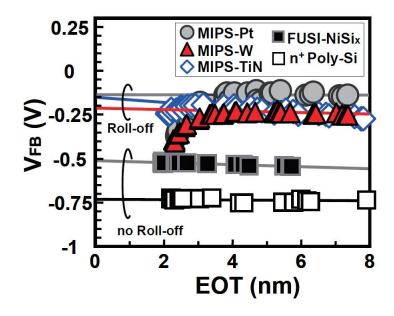

However, gate-first scheme had an issue that pFET V<sub>T</sub> gets higher (eWF gets closer to mid-gap) especially at scaled EOT region, compared to conventional p+ poly-Si case (fermi level for p+ poly-Si is only several tens of mV away from valence band edge of Si) [16, 25, 26, 27, 28, 29, 30, 31, 32]. Akiyama *et al.* reported flat band voltage (V<sub>fb</sub>) roll-off behavior in gate-first metal gate/high-k stack, where eWF of the gate stack shifts toward mid-gap direction and pFET V<sub>T</sub> shifts higher with thinner SiO<sub>2</sub>-IL (EOT less than 3 nm), as shown in Figure 1-10 [32]. They attributed this roll-off behavior to oxygen vacancy (positively charged) generation in HfO<sub>2</sub> layer (the dissolved oxygen atoms

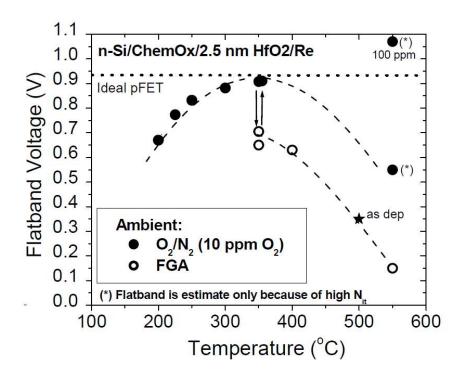

oxidize substrate and regrow the interfacial SiO<sub>2</sub> layer) during high temperature anneal (PDA, 800°C). When SiO<sub>2</sub>-IL is thinner than a certain thickness, oxygen can dissolve from HfO<sub>2</sub> and move to SiO<sub>2</sub>-IL/Si interface. However, if SiO<sub>2</sub>-IL is thick enough, this reaction can be suppressed. This mechanism can explain V<sub>fb</sub> shift at thin EOT region. Cartier et al. reported significant V<sub>fb</sub> modulation of various p-type metal gate (Ru, Re, and Pt) on HfO<sub>2</sub> by annealing conditions as shown in Figure 1-11 [26]. Although their vacuum work-function is approximately from 4.9 to 5.1 eV which is close to valence band edge, eWF of p-type metal/HfO<sub>2</sub> stack was modulated up to 0.75 eV (more than half of the Si band gap, 1.12 eV) with various anneal ambient and temperature. Oxidizing ambient (low O<sub>2</sub> partial pressure N<sub>2</sub>/O<sub>2</sub> mixture) shifts eWF toward valence band edge (positive V<sub>fb</sub> shift) and reducing ambient (N<sub>2</sub>/H<sub>2</sub> forming gas) acts oppositely and shifts eWF toward conduction band edge (negative V<sub>fb</sub> shift). They claimed this eWF/V<sub>fb</sub> behavior is due to modulation of oxygen vacancy concentration in HfO<sub>2</sub>. Oxygen in N<sub>2</sub>/O<sub>2</sub> mixture ambient can fill the oxygen vacancies and electrically neutralize them. As oxygen vacancies are positively charged and shifts V<sub>fb</sub> negatively, this reaction shifts back V<sub>fb</sub> in positive direction (eWF shifts toward valence band edge). On the other hand, reducing ambient (N<sub>2</sub>/H<sub>2</sub> forming gas) can create oxygen vacancy in HfO<sub>2</sub>, therefore V<sub>fb</sub> shifts negatively.

Figure 1-10  $V_{fb}$  as a function of EOT.  $V_{fb}$  roll-off behavior was observed for high WF metal [32].

Figure 1-11 V<sub>fb</sub> as a function of annealing temperature for Re/HfO<sub>2</sub> gate stack [26].

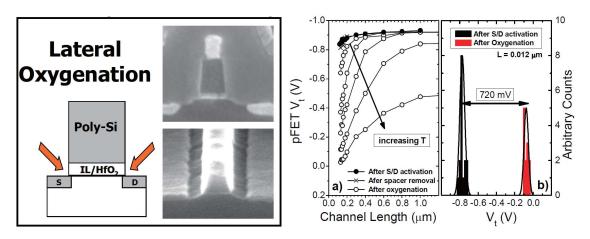

As metal gate/high-k stack cannot avoid receiving high temperature anneal in gate-first integration scheme (junction activation annealing), oxygen vacancy generation in HfO<sub>2</sub> and hence negative V<sub>fb</sub> shift (higher pFET V<sub>T</sub>) is supposed to be inevitable unless oxygen is supplied to HfO<sub>2</sub> in later stage of the processing to electrically neutralize them. Cartier *et al.* proposed lateral oxygenation technique [25]. After gate stack (poly-Si/metal/HfO<sub>2</sub>) patterning, oxygen anneal is conducted to supply oxygen to HfO<sub>2</sub> from the edge of the gate (Figure 1-12). This technique worked for short gate length devices as oxygen diffused from both sides of the gate edge can reach to the middle of the gate, then oxygen vacancies are neutralized all along the gate. On the other hand, at long channel gate devices, oxygen cannot reach to the middle of the gate length is too long. Therefore, this technique has pattern loading, which makes this technique very difficult to be applied to manufacturing.

Figure 1-12 (left) Concept of lateral oxygenation. (right) pFET  $V_T$  as a function of channel length. Oxygenation anneal can reduce pFET  $V_T$  at shorter gate length, but the effect of anneal becomes smaller with longer gate length [25].

#### 1.4 pFET $V_T$ control method

To overcome the high pFET  $V_T$  issue at scaled EOT, there have been several approaches to date which have been implemented in manufacturing.

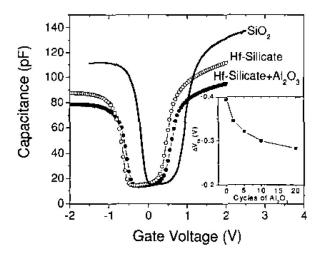

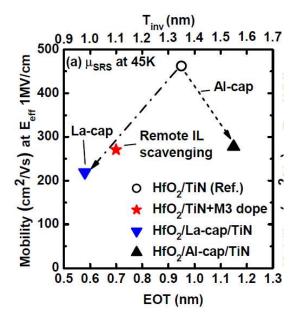

The most commonly accepted technique is to use Al<sub>2</sub>O<sub>3</sub> or Al capping layer deposited on top of Hf-based high-k [27, 33, 34, 35, 36]. The first report of Al<sub>2</sub>O<sub>3</sub> capping layer was from Cartier et al., where pFET V<sub>T</sub> could be reduced by approximately 100 mV with Al<sub>2</sub>O<sub>3</sub> deposited on top of HfSiO<sub>x</sub> (Poly-Si/Al<sub>2</sub>O<sub>3</sub>/HfSiO<sub>x</sub> gate stack) as shown in Figure 1-13. In Figure 1-13, C-V characteristics for Poly-Si/(Al<sub>2</sub>O<sub>3</sub>)/HfSiO<sub>x</sub> stack showed pFET V<sub>T</sub> reduction with Al<sub>2</sub>O<sub>3</sub>. Tatsumura et al. and Ando et al. proposed the physical model of explaining pFET V<sub>T</sub> modulation by Al<sub>2</sub>O<sub>3</sub> cap in ref. [35] and [36], respectively. In their model, Al and Si atoms form electrical dipole moment at HfO<sub>2</sub>/SiO<sub>2</sub>-IL interface. Although they reported approximately 150~200 mV of pFET V<sub>T</sub> reduction with Al<sub>2</sub>O<sub>3</sub> capping layer which is encouraging, T<sub>inv</sub> increase and hole mobility degradation were confirmed at the same time (Figure 1-14). As dielectric constant for Al<sub>2</sub>O<sub>3</sub> is approximately 10 and lower than that for HfO<sub>2</sub> (16-20), T<sub>inv</sub> increase with the additional Al<sub>2</sub>O<sub>3</sub> layer is understandable. Regarding hole mobility degradation with Al<sub>2</sub>O<sub>3</sub> capping layer, this is in good contrast with La<sub>2</sub>O<sub>3</sub> capping layer for nFET application (La<sub>2</sub>O<sub>3</sub> cap shifts V<sub>T</sub> negatively), where no extrinsic mobility degradation with La<sub>2</sub>O<sub>3</sub> cap was observed [35, 36]. Their hypothesis is that the Al-Si dipoles are densely distributed at HfO<sub>2</sub>/SiO<sub>2</sub>-IL interface, so that hole mobility is degraded due to remote Coulomb scattering. In case of La<sub>2</sub>O<sub>3</sub> cap, on the other hand, La-O-Si network is formed at the top of SiO<sub>2</sub>-IL (La silicate formation) along the depth direction of the gate stack and creates longer and lower density dipole moments. Therefore, the mobility degradation by remote Coulomb scattering can be minimized. As described above, although the V<sub>T</sub> shift amount is significant, Al-based capping layer has inherent disadvantage of performance degradation due to  $T_{\rm inv}$  and mobility degradation.

Figure 1-13 C-V characteristics for Poly-Si/(Al<sub>2</sub>O<sub>3</sub>)/HfSiO<sub>x</sub> stack showing pFET  $V_T$  reduction with Al<sub>2</sub>O<sub>3</sub> [27].

Figure 1-14 Carrier mobility as a function of EOT for La-based cap and Al-based cap [36].

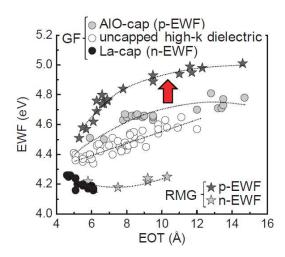

Gate-last (or RMG) integration scheme is another approach to mitigate pFET V<sub>T</sub> issue, although it requires significant change in the CMOS fabrication flow [8, 9, 37]. In RMG process flow, final gate stack is formed after junction activation anneal by replacing dummy poly-Si gate and SiO<sub>2</sub> gate dielectric with metal gate and high-k gate dielectric. Relatively lower pFET V<sub>T</sub> and eWF closer to valence band edge have been consistently confirmed in many literatures [38, 39, 40, 41, 42], as shown in Figure 1-15. This is supposedly due to absence of high temperature anneal on metal/high-k stack (less amount of oxygen vacancies in HfO<sub>2</sub>) in case of RMG, although HfO<sub>2</sub> PDA (typically 700-900°C RTA) is still needed for densification in gate-last flow as well.

RMG based metal gate/high-k technology was firstly industrialized by Intel Corporation in their 45nm node technology [8, 9] and currently most companies are using RMG based metal gate/high-k technology.

Figure 1-15 eWF as a function of EOT comparing gate-first and gate-last (from [39]).

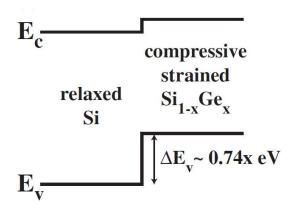

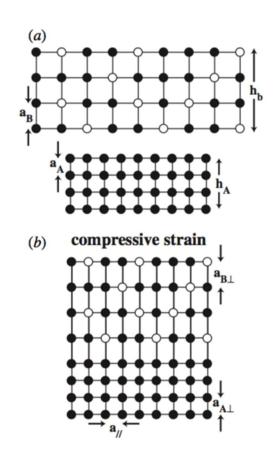

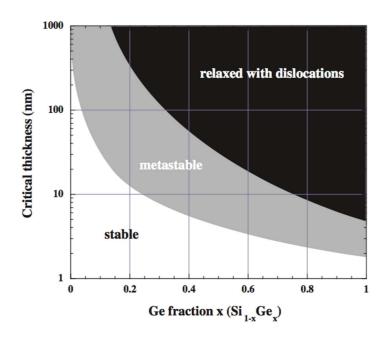

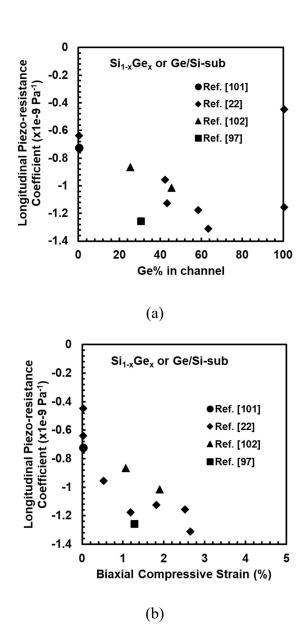

The other approach is to use epitaxial  $Si_{1-x}Ge_x$  film as a channel material instead of conventional Si channel [43, 44, 45, 46] to shift valence band edge energetically higher so that inversion layer can be formed with relatively lower gate voltage.  $Si_{1-x}Ge_x$  film is typically epitaxially-grown on Si substrate in pFET active area by masking nFET area with hard mask [47]. The band alignment for strained  $Si_{1-x}Ge_x$  grown on bulk Si substrates is shown in Figure 1-16. The valence band edge is shifted higher depending on the Ge content in the  $Si_{1-x}Ge_x$  channel ( $\sim 0.74x$  eV). The bandgap for strained  $Si_{1-x}Ge_x$  grown on bulk Si substrates and for unstrained  $Si_{1-x}Ge_x$  is shown in Figure 1-17 [48]. Experimentally measured bandgaps have been fitted to two quadratic equations for the Si-like and Ge-like parts of the band structure as described as below in ref. [48, 49]

$$E_g = 1.155 - 0.43x + 0.0206x^2$$

(eV) for x < 0.85 (1-3)

$$E_g = 2.010 - 1.27x \text{ (eV) for } x > 0.85$$

(1-4)

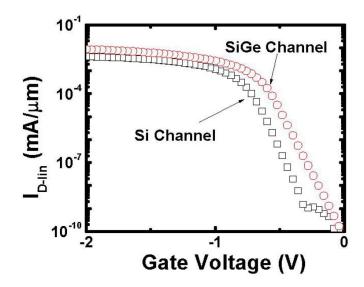

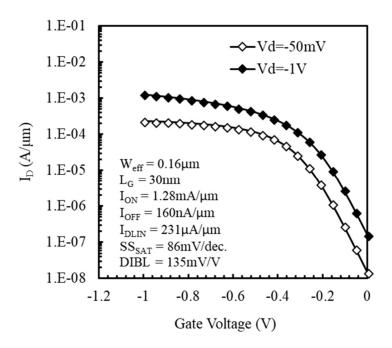

Figure 1-18 shows  $I_d$ - $V_g$  characteristics for Si and  $Si_{1-x}Ge_x$  channel pFET [43], demonstrating pFET  $V_T$  reduction with  $Si_{1-x}Ge_x$  channel.  $Si_{1-x}Ge_x$  channel has been introduced in manufacturing successfully by IBM in their 28nm node technology with a significant effort to overcome its integration challenges like interface quality between gate dielectric and  $Si_{1-x}Ge_x$  channel [46].

Figure 1-16 The band alignments for a compressively strained- $Si_{1-x}Ge_x$  heterolayer grown on relaxed Si [48].

Figure 1-17 Bandgap for strained  $Si_{1-x}Ge_x$  grown on bulk Si substrates and for unstrained  $Si_{1-x}Ge_x$  [48].

Figure 1-18  $I_d$ - $V_g$  characteristics for Si and  $Si_{1-x}Ge_x$  channel [43].

Transistor gate voltage  $V_{\mbox{\scriptsize g}}$  in subthreshold region is expressed by

$$V_g = V_{fb} + \psi_s - \frac{Q_s}{C_{ox}} = V_{fb} + \psi_s + \frac{\sqrt{2\varepsilon_{Si}qN_d\psi_s}}{C_{ox}}$$

(1-5)

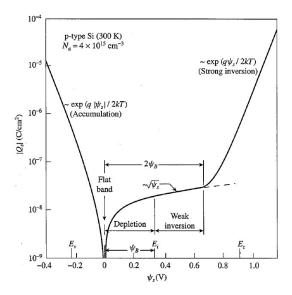

where  $\psi_s$  is surface potential in Si,  $Q_s$  is total charge per unit area in Si,  $C_{ox}$  is oxide capacitance per unit area,  $\varepsilon_{Si}$  is Si permittivity, q is electronic charge,  $N_d$  is donor impurity density. In case of Si channel, strong inversion starts where  $\psi_s$  reaches to  $2\psi_B$  ( $\psi_B$  is difference between Fermi level and intrinsic level in Si) as shown in Figure 1-19. If we use Si<sub>1-x</sub>Ge<sub>x</sub> as a channel material, the necessary surface band bending will be reduced by

$$\Delta E_v/q \equiv \frac{1}{q} (E_v^{SiGe} - E_v^{Si})$$

and (1-5) will be

$$V_T = V_{fb} + 2\psi_B - \Delta E_v/q + \frac{\sqrt{2\varepsilon_{Si}N_d(2q\psi_B - \Delta E_v)}}{c_{ox}}$$

(1-6)

V<sub>fb</sub> is given by

$$V_{fb} = \phi_{ms} - \frac{Q_{ox}}{C_{ox}} \tag{1-7}$$

$$\phi_{ms} \equiv \phi_m - \phi_s \tag{1-8}$$

where  $Q_{ox}$  is effective oxide charge per unit area at the gate dielectric and Si interface.  $\phi_m$  and  $\phi_s$  are work-function of metal gate and semiconductor (channel material), respectively. Using (1-7) and (1-8), (1-6) can be written as

$$V_T = \left(\phi_m - \frac{Q_{ox}}{C_{ox}}\right) - \phi_s + 2\psi_B - \Delta E_v / q + \frac{\sqrt{2\varepsilon_{Si}N_d(2q\psi_B - \Delta E_v)}}{C_{ox}}$$

(1-9)

The first term of RHS in (1-9) can be defined as eWF,

$$\phi_m^{EFF} \equiv \phi_m - \frac{Q_{ox}}{C_{ox}}$$

In case of techniques modulating the amount of electrical dipole (Al<sub>2</sub>O<sub>3</sub> cap) or fixed charge (RMG, where density of oxygen vacancy is supposedly smaller than gate-first scheme),  $\phi_m^{EFF}$  is modulated, whereas Si<sub>1-x</sub>Ge<sub>x</sub> channel is modulating  $\Delta E_v$  depending on Ge content.

Figure 1-19 Total charge density in Si as a function of surface potential  $\psi_s$  for pFET [3].

#### 1.5 The scope of this thesis

In this thesis, two kinds of pFET  $V_T$  modulation techniques will be discussed in detail. In Chapter 2, as a first topic, eWF control technique by gate stack engineering in RMG FinFET technology will be discussed. Even with gate-last or RMG integration scheme, recent reports highlighted eWF lowering in scaled EOT region (EOT < 10 Å) [39, 50]. Therefore, it is still highly important to push eWF further towards valence band edge to achieve lower pFET  $V_T$  at scaled EOT region. However, the solution for this problem has not been identified clearly yet. In this thesis, we conducted systematic study to investigate the impact from process condition on eWF or device  $V_T$ . Based on this result, we propose the practical method to reduce RMG pFET  $V_T$  in aggressively scaled EOT region (< 10 Å) by controlling effective oxide charge  $Q_{ox}$ .

From Chapter 3 to Chapter 5, as a second topic, device characteristics for  $Si_{1-x}Ge_x$  channel pFET will be discussed from various aspects. Although higher Ge content and lower process temperature had been already identified as a method to reduce pFET  $V_T$ , there was very limited report on successful integration of high Ge content  $Si_{1-x}Ge_x$  channel (x > 0.5) at scaled gate length (20-30 nm, necessary for sub-32nm node technology) at the time when we started research (2010), as shown in

Table 1-2. Therefore, in this thesis, we focused on demonstration of high performing  $Si_{1-x}Ge_x$  channel pFET with extremely high Ge content (x = 0.55) at scaled gate length (below 30 nm).

In Chapter 3, impact from thermal budget on various device characteristics such as  $V_T$ , carrier mobility, off-state leakage current will be discussed. In Chapter 4, strain effect in  $Si_{1-x}Ge_x$  channel pFET will be discussed and device performance boost elements will be shown. In the last section of  $Si_{1-x}Ge_x$  channel in Chapter 5, scalability of  $Si_{1-x}Ge_x$

channel pFET will be discussed and optimal device structure will be proposed.

Table 1-2 Benchmark for Ge content, gate length, and drive current performance  $for \ Si_{1-x}Ge_x \ channel \ pFET.$

| Reference | Year | Structure                                     | Ge content x | Minimum gate length | $I_{ON}@I_{OFF}=100 \text{ nA/}\mu\text{m}$                           |

|-----------|------|-----------------------------------------------|--------------|---------------------|-----------------------------------------------------------------------|

| [42]      | 2010 | Si <sub>1-x</sub> Ge <sub>x</sub> /Si-<br>sub | Approx. 25%  | NA                  | 0.68 mA/μm (V <sub>dd</sub> =-1V)                                     |

| [43]      | 2007 | $Si_{1-x}Ge_x/Si$ - sub                       | 70%          | 1 μm                | NA                                                                    |

| [44]      | 2007 | $Si_{1-x}Ge_x/Si$ - sub                       | 25%          | 80 nm               | $0.56 \text{ mA/}\mu\text{m} \text{ (V}_{dd}=-1.2 \text{ V})$         |

| [45]      | 2008 | $Si_{1-x}Ge_x/Si$ - sub                       | Approx. 50%  | 1 μm                | NA                                                                    |

| [51]      | 2010 | $Si_{1-x}Ge_x/Si$ - sub                       | 63%          | 100 μm              | NA                                                                    |

| [52]      | 2008 | $Si_{1-x}Ge_x/Si$ - sub                       | 55%          | 80 nm               | NA                                                                    |

| [53]      | 2010 | Si <sub>1-x</sub> Ge <sub>x</sub> /sSOI       | 40%          | 22 nm               | $0.3 \text{ mA/}\mu\text{m}$ $(V_G\text{-}V_T\text{=}V_d\text{=-}1V)$ |

| [54]      | 2009 | $Si_{1-x}Ge_x/Si$ - sub                       | 23%          | 100 nm              | NA                                                                    |

| [55]      | 2009 | $Si_{1-x}Ge_x/Si$ - sub                       | 25%          | 1 μm                | NA                                                                    |

| [56]      | 2010 | $Si_{1-x}Ge_x/Si$ - sub                       | 43%          | 10 μm               | NA                                                                    |

| [57]      | 2006 | $Si_{1-x}Ge_x/Si$ - sub                       | 30%          | > 60 nm             | $0.71 \text{ mA/}\mu\text{m} \text{ (V}_{dd} =  1.2\text{V)}$         |

| [58]      | 2010 | Strained<br>SGOI                              | 25-35%       | 20 nm               | $0.52 \text{ mA/}\mu\text{m} \text{ (V}_{dd} = -1 \text{ V)}$         |

## Chapter 2 pFET effective work function control techniques in RMG

#### 2.1 Background

In this chapter, we will discuss eWF control technique for RMG FinFET devices. As mentioned in Chapter 1, even with gate-last or RMG integration scheme which provides relatively low pFET  $V_T$  without a help from  $Si_{1-x}Ge_x$  channel or various capping techniques [38, 59], recent reports highlighted eWF lowering (higher pFET  $V_T$ ) in aggressively scaled EOT region (EOT < 10 A) [39, 50]. Therefore, it is still highly important to push the eWF further towards valence band edge to achieve lower pFET  $V_T$  at scaled EOT region on RMG devices. In this chapter, the eWF control methods are demonstrated for pFinFET RMG devices based on the process flow proposed in ref. [50] and [59], and the details of device fabrication flow will be discussed in Section 2.2. Section 2.3 and 2.4 will address experimental results and proposal for possible pFET eWF control techniques.

#### 2.2 Device fabrication flow

Fabrication process flow (only RMG part is shown which is relevant to the discussion here) is shown in Figure 2-1. We fabricated RMG bulk FinFET device. In this work, we investigated process condition dependence of gate stack properties to explore eWF control methods. In ref. [50], so-called WF setting anneal is done after sacrificial TiN (sac-TiN) and amorphous Si (a-Si) cap layer were deposited on HfO<sub>2</sub> gate dielectric. We followed the same process flow in this work, and we abbreviate this WF setting anneal as WSA in this thesis.

After dummy poly-Si gate and dummy gate oxide (SiO<sub>2</sub>) removal, SiO<sub>2</sub> interfacial layer (SiO<sub>2</sub>-IL) and HfO<sub>2</sub> are formed as gate dielectric. Post deposition anneal (PDA) is done right after HfO<sub>2</sub> deposition to densify the film [60, 61]. After that, 1st-TiN (TiN1) and a-Si cap layers are deposited on top of HfO<sub>2</sub> gate dielectric. Then, WSA is done at various temperature (T<sub>1</sub>, T<sub>2</sub>, and T<sub>3</sub>, spike RTA). We will discuss the impact from this WSA temperature on the gate stack properties such as V<sub>T</sub>, mobility, and reliability in Section 2.4. After WSA, a-Si cap and TiN1 are removed successively by wet etching (a-Si cap removal is done in all cases. TiN1 removal is optional). A-Si cap is removed with ammonium hydroxide (NH<sub>4</sub>OH), and TiN1 is removed with SC1 clean. In this experiment, TiN1 wet etch time was varied and the impact on gate stack properties were investigated. The result will be discussed in Section 2.3. After TiN1 removal (or after a-Si removal in case TiN1 is not removed), second-TiN (TiN2) is deposited in case of pFET as p-type WF (pWF) metal. In case of nFET, n-type WF (nWF) metal is deposited. All TiN and nWF metals are deposited with ALD.

The thickness of TiN1 is supposed to be thicker than critical thickness (T<sub>crit</sub>) discussed in ref. [59]. In ref. [59], T<sub>crit</sub> is defined as the TiN1 thickness above which eWF is stable over the air exposure time between a-Si layer removal and TiN2 deposition. We confirmed that eWF was very stable over long air exposure time.

After WF metal is deposited, gate trench is filled with CVD-W and W is planarized by CMP. Then standard BEOL process follows.

Dummy gate removal

SiO<sub>2</sub>-IL/HfO<sub>2</sub> formation

PDA

1st-TiN (TiN1)/a-Si deposition

WF-setting anneal

a-Si removal

TiN1 removal (optional)

2nd-TiN (TiN2) deposition (pFET)

nWF metal deposition (nFET)

W deposition and W-CMP

Figure 2-1 RMG process flow for FinFET devices.

#### 2.3 Threshold voltage control by introduction of fixed charge layer

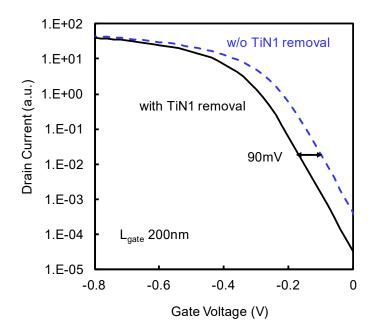

Figure 2-2 shows pFET linear  $I_D$ - $V_G$  curve comparison between devices with and without TiN1 removal process. Gate length is 200 nm, and  $V_D$  is -50 mV. Devices without TiN1 removal process have TiN1/TiN2 stack as WF metal, while devices with TiN1 removal have only TiN2 as WF metal. The WSA was done at temperature  $T_2$  unless mentioned otherwise. TiN1 removal over etch condition is 38x over etch. Devices without TiN1 removal process showed approximately 90 mV pFET  $V_T$  reduction compared to the ones with TiN1 removal process, even though both devices have same TiN as WF metal and eWF is supposed to be identical. This trend is actually opposite to the results of ref. [59], where pFET  $V_T$  is lowered by doing TiN1 removal process, though the process details in ref. [59] are not disclosed and their results cannot be directly compared to our results.

Regarding process uniformity of the TiN1 removal process, both devices show

comparable within wafer  $V_T$  variation (Within-Wafer (WiW) range of  $V_T$  is approximately 20 mV for both devices) and there was no uniformity degradation due to TiN1 removal process.

Figure 2-2 pFET linear  $I_D$ - $V_G$  curve comparison: devices with TiN1 removal (black) and without TiN1 removal (blue). WSA was done at  $T_2$  temperature. TiN1 removal over etch is 38x.

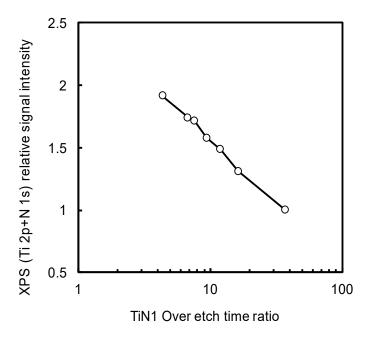

In order to explore the root cause of this considerable pFET V<sub>T</sub> reduction, TiN1 wet etch time has been systematically changed and HfO<sub>2</sub> surface was probed with X-ray photoemission spectroscopy (XPS) to investigate the interface between TiN1 and HfO<sub>2</sub>. Figure 2-3 shows summation of Ti 2p and N 1s XPS signal intensity (normalized to the value with the longest over etch time) as a function of TiN1 over etch time ratio with respect to no over etch case (over etch time ratio 1 means no over etch). Even though sufficient amount of over etch (more than ~5x over etch) has been applied, Ti and N

signals (well above detection limit) have still been detected and they are reduced very slowly over the etch time (while over etch time is increased from ~5x to ~38x, summation of Ti and N signal is only decreased by a factor of 2). This result strongly indicates that some interfacial layer is formed between TiN1 and HfO<sub>2</sub> (supposedly intermixed layer) by high thermal budget of WSA and this layer should have very slow etching rate to SC1 wet etch chemistry. For convenience, this interfacial layer is called HfTiON<sub>x</sub> in later part of the thesis.

Figure 2-3 XPS Ti 2p + N 1s signal intensity vs. over etch time ratio for TiN1 removal process with respect to no over etch case. XPS has been done after TiN1 wet etch process. WSA was done at T<sub>2</sub> temperature.

To investigate electrical properties of the  $HfTiON_x$  interfacial layer, we checked device characteristics as a function of  $HfTiON_x$  layer thickness. Devices were fabricated by removing TiN1 layer with various etching time, then nWF metal (nFET) or TiN2

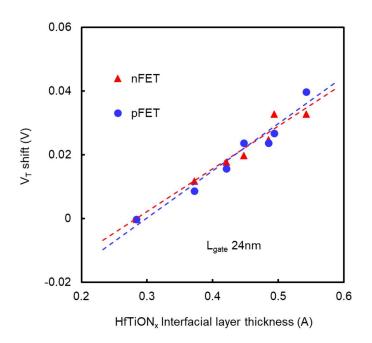

(pFET) was deposited as WF metal. HfTiON $_x$  thickness was calculated based on summation of Ti 2p and N 1s signal intensity measured by XPS. Figure 2-4 shows nFET and pFET  $V_T$  shift as a function of HfTiON $_x$  thickness. Gate length of the devices is 24 nm.  $V_T$  shift was calculated with respect to  $V_T$  at HfTiON $_x$  thickness of 0.28 Å (longest TiN1 over etch time, thinnest HfTiON $_x$  layer thickness). Linear  $V_T$  shift was observed as a function of HfTiON $_x$  thickness. Both nFET  $V_T$  and pFET  $V_T$  show positive shift with thicker HfTiON $_x$ , meaning nFET  $V_T$  increases and pFET  $V_T$  reduces. It should be noted that magnitude of  $V_T$  shift is almost same for n- and pFET at a given HfTiON $_x$  thickness. As seen in Figure 2-2, if this HfTiON $_x$  layer is not removed at all (in case of no TiN1 removal process), it gives approximately 90 mV  $V_T$  shift.

Figure 2-4 n- and pFET  $V_T$  shift vs. HfTiON<sub>x</sub> interfacial layer thickness. WSA was done at T<sub>2</sub> temperature.

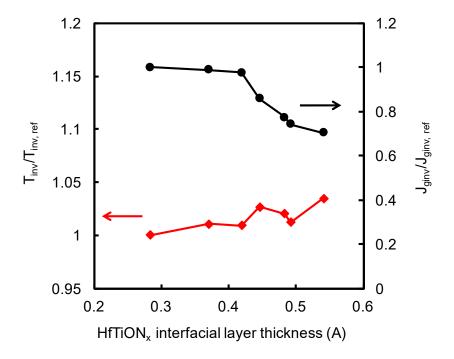

Figure 2-5 shows normalized  $T_{inv}$  and  $J_{ginv}$  (gate leakage in inversion) trend as a function of HfTiON<sub>x</sub> interfacial layer thickness.  $T_{inv}$  and  $J_{ginv}$  are normalized with respect to the ones at HfTiON<sub>x</sub> thickness of 0.28 Å.  $T_{inv}$  gets thicker and  $J_{ginv}$  becomes smaller with increasing HfTiON<sub>x</sub> interfacial layer thickness, which suggests that the interfacial layer is dielectric material, not metal. Therefore,  $V_T$  shift observed in Figure 2-4 is supposed to be caused by negative fixed charge in HfTiON<sub>x</sub> layer.

Based on the discussion so far, it can be concluded that WSA creates interfacial dielectric layer at  $TiN1/HfO_2$  interface (we call it  $HfTiON_x$  for convenience) and this layer has negative fixed charges which increases nFET  $V_T$  and reduces pFET  $V_T$  ( $V_T$  shift towards positive direction) as seen in Figure 2-4.

Fixed charge density (N<sub>f</sub>) in HfTiON<sub>x</sub> layer can be estimated from the equation

$$N_f = \frac{1}{e} C_g \times \delta V_T \tag{2-1}$$

where e is elemental charge,  $C_g$  and  $\delta V_T$  are gate capacitance per unit area and  $V_T$  shift, respectively. In this case,  $N_f$  was estimated to be approximately  $2 \times 10^{12}$  cm<sup>-2</sup>.

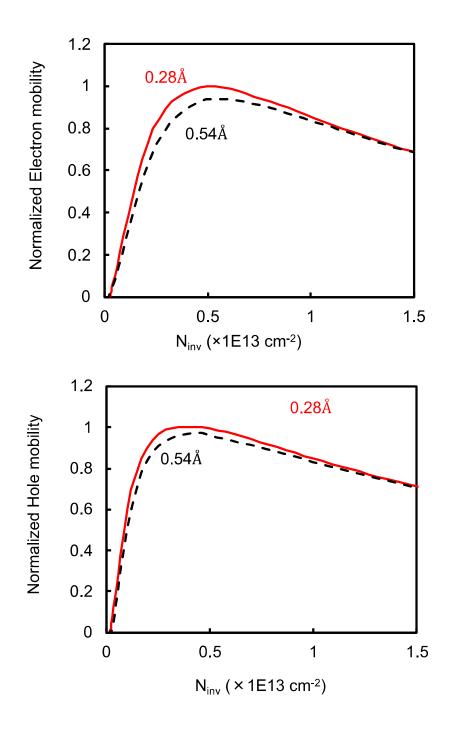

Figure 2-6 shows normalized electron and hole mobilities with various  $HfTiON_x$  interfacial layer thicknesses (0.28 and 0.54 Å). Normalization was done with respect to peak mobility of  $HfTiON_x$  0.28 Å sample. Although mobility at high effective field is all similar regardless of the  $HfTiON_x$  interfacial layer thickness, there is slight mobility degradation only at low  $N_{inv}$  region with thicker  $HfTiON_x$  interfacial layer, especially on nFET (electron mobility). This carrier mobility degradation is the most likely due to additional remote Coulomb scattering from the fixed charges in  $HfTiON_x$  interfacial layer, as it only affects lower effective field region. Practically, as we would either remove this  $HfTiON_x$  layer from nFET side or remove TiN1/a-Si stack from nFET side before WSA to have this  $HfTiON_x$  layer only on pFET when integrated into CMOS process flow,

relatively minor mobility degradation on pFET side may not be a concern from device performance point of view.

To conclude this section, we identified that the root cause of the  $V_T$  difference between devices with and without TiN1 wet etching is negatively charged dielectric layer which is supposedly formed by intermixing of TiN and HfO<sub>2</sub> layers during WSA. This charged layer can provide 90 mV pFET  $V_T$  reduction, although a certain amount of carrier mobility degradation was observed both on n- and pFET. These trade-off relations between various device characteristics are summarized in Table 2-1. To pursue lower pFET  $V_T$ , HfTiON<sub>x</sub> layer should be kept as thick as possible despite of  $T_{inv}$  and mobility degradation.

Figure 2-5 Normalized  $T_{inv}$  and  $J_{ginv}$  vs. HfTiON<sub>x</sub> interfacial layer thickness. WSA was done at  $T_2$  temperature.

Figure 2-6 Electron mobility (top) and hole mobility (bottom) for various  $HfTiON_x$  interfacial layer thickness (0.28, 0.54 Å). WSA was done at  $T_2$  temperature.

Table 2-1 Trade-off of device characteristics by introduction of  $HfTiON_x$  fixed change layer.

|                     | HfTiON <sub>x</sub> thickness ↑ |

|---------------------|---------------------------------|

| pFET V <sub>T</sub> | lower                           |

| Tinv                | thicker                         |

| Gate leakage        | lower                           |

| Hole mobility       | degraded                        |

## 2.4 Threshold voltage control by oxygen vacancy density modulation

In this section, impact from WSA temperature on gate stack properties will be discussed.

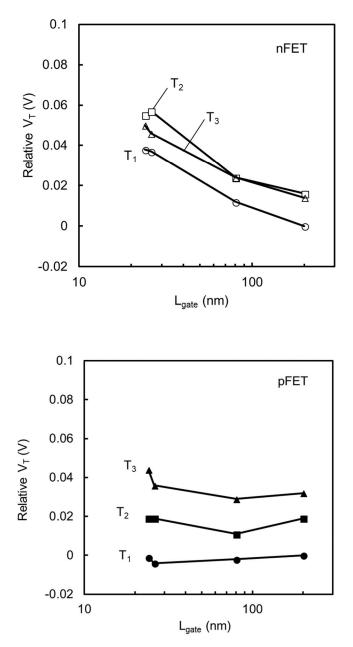

Figure 2-7 shows nFET and pFET relative saturation  $V_T$  (relative  $V_T$  with regard to  $V_T$  at  $L_{gate} = 2~\mu m$  and at  $T_1$  for WSA) as a function of gate length with various WSA temperature ( $T_1 < T_2 < T_3$ ). TiN1 was removed with the longest SC1 time in Figure 2-3 (38x over etching) for all samples. HfTiON<sub>x</sub> layer thickness probed with XPS for the samples with  $T_1$  and  $T_3$  temperature is matched to the one with  $T_2$ , approximately 0.28 Å. Therefore, the  $V_T$  shift by negative fixed charge in HfTiON<sub>x</sub> layer can be regarded identical for all samples. By increasing WSA temperature from  $T_1$  to  $T_3$ , pFET  $V_T$  is consistently reduced up to approximately 50 mV, while nFET  $V_T$  is only increased by 20 mV from  $T_1$  to  $T_2$ , and nearly no change was observed from  $T_2$  to  $T_3$ . Overall, nFET  $V_T$  looks less sensitive to WSA temperature. Within wafer  $V_T$  variation was similar for all temperatures (not shown).

In pFET,  $V_T$  shift happens evenly for all gate lengths (from 24 nm to 2  $\mu$ m), indicating this  $V_T$  shift is not driven by short channel effect (more dopant diffusion due to higher annealing temperature), but driven by gate stack modification. As mentioned earlier,

$HfTiON_x$  interfacial layer thickness after TiN1 removal is confirmed to be identical among all WSA conditions, therefore this  $V_T$  shift is not due to  $HfTiON_x$  layer thickness difference.

Figure 2-7 nFET (top) and pFET (bottom) Relative  $V_T$  vs  $L_{gate}$ .  $T_1$  (circle),  $T_2$  (square),  $T_3$  (triangle).

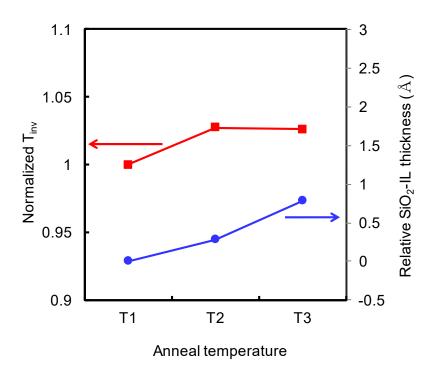

To figure out more what is happening on gate stack by WSA, SiO<sub>2</sub>-IL thickness (measured by XPS) and nFET T<sub>inv</sub> have been checked as a function of anneal temperature. The result is shown in Figure 2-8. As WSA temperature goes higher from T<sub>1</sub> to T<sub>3</sub>, SiO<sub>2</sub>-IL thickness was confirmed to get thicker, by approximately 0.8 Å. This SiO<sub>2</sub>-IL regrowth translates to thicker T<sub>inv</sub> with higher WSA. Figure 2-8 shows nFET T<sub>inv</sub>, but similar trend has been confirmed for pFET T<sub>inv</sub> as well. This SiO<sub>2</sub>-IL regrowth is due to oxidation of Si substrate, suggesting oxygen has been supplied from somewhere in the gate stack. Si atom in a-Si cap is isolated from HfO<sub>2</sub>/SiO<sub>2</sub>-IL by TiN1 layer, therefore Si atom should not be involving in the reaction.

Figure 2-8 Relative  $SiO_2$ -IL thickness and nFET  $T_{inv}$  trend as a function of WSA temperature.

To understand the mechanism of V<sub>T</sub> shift and SiO<sub>2</sub>-IL regrowth during WSA, XPS has been carried out on pre and post WSA samples (Si-substrate/SiO<sub>2</sub>-IL/HfO<sub>2</sub>/TiN1/a-Si) and the results are shown in Figure 2-9. Samples were prepared by sputtering a-Si cap layer close to a-Si/TiN1 interface after a-Si deposition (pre-anneal sample) or after WSA (post-anneal sample). The WSA was done at T<sub>2</sub>. Si 2p and Ti 2p XPS spectra are shown for pre- and post WSA. Take-off angle is 90 degrees (normal to the sample surface).

In Figure 2-9 (a), Ti 2p peaks mainly show components from TiN and TiO<sub>x</sub>. Peaks corresponding to TiN are at around binding energies of 455 eV and 461 eV, the peak at 455 eV comes from Ti 2p3/2 and the peak at 451 eV is from Ti 2p1/2 due to spin-orbit splitting. Peaks corresponding to TiO<sub>x</sub> are at around 458 eV and 464 eV from the above mentioned Ti 2p orbitals. Existence of TiO<sub>x</sub> peak suggests surface oxidation of TiN1 layer before a-Si layer is deposited, as no oxygen can be incorporated during deposition itself. This TiO<sub>x</sub> peak intensity is clearly reduced after WSA compared to pre-anneal sample both at 458 and 464 eV peaks. On the other hand, SiO<sub>2</sub> peak in Si 2p spectra (Figure 2-9 (b)) shows increase at post WSA.

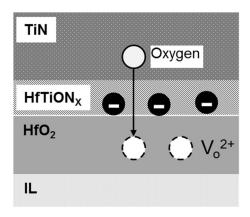

These XPS results indicate that oxygen atoms diffuse from TiN1 layer towards  $HfO_2/SiO_2$ -IL during WSA and some of them oxidize the Si fin and regrow the  $SiO_2$ -IL. If there are oxygen vacancies  $(V_0^{2+})$  in  $HfO_2$ , some of the diffused oxygen atoms should passivate and electrically neutralize them. As  $V_0^{2+}$  is positively charged defect [62], once neutralized,  $V_T$  should shift in positive direction. Oxygen vacancies are supposedly created during PDA [32]. Higher WSA temperature should diffuse more oxygen atoms from TiN1, therefore more  $V_0^{2+}$  should be passivated and more  $SiO_2$ -IL regrowth should happen. This model can explain larger positive pFET  $V_T$  shift and larger  $SiO_2$ -IL regrowth with higher temperature anneal observed in Figure 2-7 and Figure 2-8, respectively.

According to this model, magnitude of  $V_T$  shift should be comparable on nFET as there is no process difference up to this point between n- and pFET. Therefore, relatively insensitive  $V_T$  behavior observed in nFET cannot be explained clearly by this model. Difference in work function of metal gate electrode may play a role, but further study is needed for more complete understanding.

Figure 2-9 AR-XPS results (a) Ti 2p and (b) Si 2pspectra. Pre and post WSA (T<sub>2</sub>) are plotted.

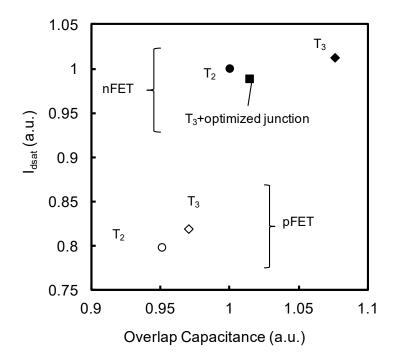

Although higher WSA temperature is favorable to pFET  $V_T$  reduction, one concern is degradation of short channel effect. Figure 2-10 is summary of drain current,  $I_{dsat}$  (at fixed off-current,  $I_{off\_d}$ ) versus overlap capacitance for nFET and pFET at WSA temperature of  $T_2$  and  $T_3$ . In pFET, overlap capacitance increase by WSA temperature increase is relatively small (approximately 2%) and not a major issue. In nFET, although overlap capacitance increases significantly with anneal temperature of  $T_3$  (approximately 8%), we could obtain comparable overlap capacitance and  $I_{dsat}$  to  $T_2$  by optimizing junction process.

Figure 2-10  $I_{dsat}$  vs. overlap capacitance for n- and pFET with WSA at  $T_2$ ,  $T_3$ , and  $T_3$  with optimized junction process.

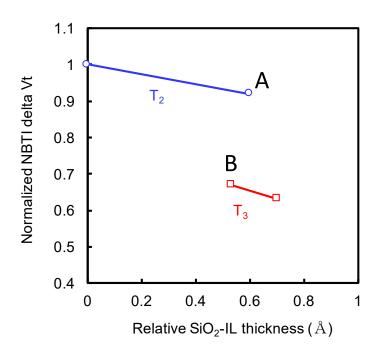

Figure 2-11 shows  $V_T$  shift of NBTI (Negative Bias Temperature Instability) stress as a function of relative  $SiO_2$ -IL thickness (characterized by XPS).  $SiO_2$ -IL thickness was varied by temperature of WSA and PDA, while  $HfO_2$  thickness was almost identical for all devices. It is clearly shown that higher WSA temperature significantly improves NBTI by approximately 30% at a given  $SiO_2$ -IL thickness.

One possibility is an improvement of SiO<sub>2</sub>/Si interface quality by higher temperature anneal. We checked interface trap density (D<sub>it</sub>) on device A and B in Figure 2-11 (A and B have almost identical SiO<sub>2</sub>-IL thickness) and they turned out to be comparable (D<sub>it</sub> is about  $1.1 \times 10^{11}$  cm<sup>-2</sup> for both devices). Therefore, NBTI improvement cannot be explained by interface quality improvement. It has been reported that NBTI is more dominantly affected by hole trapping in bulk HfO<sub>2</sub> rather than SiO<sub>2</sub>-IL/Si interface degradation when SiO<sub>2</sub>-IL is scaled down and direct tunneling from substrate to HfO<sub>2</sub> bulk starts to happen [63]. Based on that, this result suggests that higher WSA helps to reduce hole trap defects in HfO<sub>2</sub>. This might be related to passivation of oxygen vacancies, but further study is needed to get more-clear understanding.

Figure 2-11 NBTI  $V_T$  shift as a function of relative SiO<sub>2</sub>-IL thickness. WSA temperatures  $T_2$  and  $T_3$  are plotted ( $T_2 < T_3$ ).

#### 2.5 Summary

In this chapter, we have investigated the effect of WSA (high temperature annealing on a-Si/TiN/HfO<sub>2</sub> stack) on gate stack properties to achieve lower pFET  $V_T$  with more band-edge work function. The technique of pFET  $V_T$  control discussed in this work is illustrated in Figure 2-12. It was found that intermixed layer created in-between TiN and HfO<sub>2</sub> during WSA (HfTiON<sub>x</sub>) has negative fixed charges and it reduces pFET  $V_T$  (positive  $V_T$  shift) by about 90 mV. On top of that, it was also found that higher anneal temperature further reduces pFET  $V_T$  by about 50 mV (by increasing anneal temperature from  $V_T$  to  $V_T$  while keeping nFET  $V_T$  almost unchanged. This could be explained by passivation of oxygen vacancies (positively charged) in HfO<sub>2</sub> with oxygen atoms diffused from TiN1 layer. By combining these effects (HfTiON<sub>x</sub> interfacial layer and higher temperature

WSA), one can further push effective work function towards valence band edge by approximately 140 meV and achieve lower pFET V<sub>T</sub>.

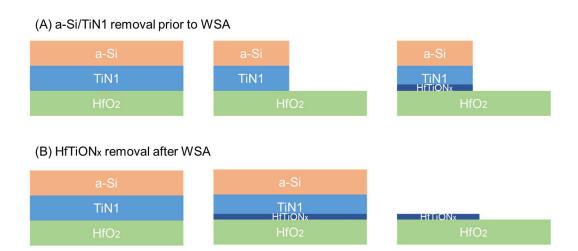

The pFET  $V_T$  reduction is extremely difficult in scaled EOT devices because conventionally used metal gate material cannot provide sufficiently low pFET  $V_T$ . This proposed technique has great value as it doesn't require change in work function metal material and integration hurdle is supposedly lower than changing metal material or its thickness. This technique can be applied to multi- $V_T$  integration as well as shown in Figure 2-13. For example, a-Si and TiN1 cap can be removed prior to WSA selectively from certain devices so that WSA modulates pFET  $V_T$  for devices which are covered with a-Si and TiN1 cap and  $V_T$  difference can be created (flow (A) in Figure 2-13). Alternatively, we can apply WSA for all devices and remove HfTiON<sub>x</sub> interfacial layer selectively from certain devices to create  $V_T$  difference. In this case, all devices will receive WSA anneal and we can expect NBTI benefit for all devices (flow (B) in Figure 2-13). For multi- $V_T$  integration, multiple work-function metal deposition and patterning [64] is conventional approach and Table 2-2 shows other representative multi- $V_T$  integration methods. The multi- $V_T$  integration method proposed in this work is different from any of those and hence original.

NBTI was significantly improved with higher WSA temperature likely due to reduction of hole trapping sites in HfO<sub>2</sub>. PDA is supposed to densify and crystalize HfO<sub>2</sub> film to some extent (depending on HfO<sub>2</sub> thickness and PDA temperature) before depositing TiN1 film, but the effect on reliability is relatively limited compared to WSA. WSA is necessary to improve reliability. Both anneal cause SiO<sub>2</sub>-IL regrowth but its thickness is still in acceptable range.

Figure 2-12 Schematic illustration of pFET  $V_T$  control techniques discussed in this work. Negative fixed charges in HfTiON<sub>x</sub> layer and passivation of oxygen vacancies with diffused oxygen from TiN (elimination of positive charges in HfO<sub>2</sub>) reduces pFET  $V_T$ .

Figure 2-13 Schematics for possible multi- $V_T$  integration using eWF control technique discussed in this work. (A) a-Si/TiN1 removal prior to WSA, (B) HfTiON<sub>x</sub> removal after WSA.

Table 2-2 Representative multi-Vt integration methods [65].

|   | Method                   |                    | Principle                  | N                          | Р                          |

|---|--------------------------|--------------------|----------------------------|----------------------------|----------------------------|

| 1 |                          | Separate Metal     | Unique Metal Work Function | Ta, Al, Hf                 | Pt, Ti, Mo                 |

| 2 |                          | Al Diffusion       | Al Concentration           | 0                          | 0                          |

| 3 | Gate<br>Work<br>Function | Capping Layer      | Dielectric Dipole Eng      | SrO, La2O3,<br>Lu2O3, Y2O3 | Al2O3, TiO2,<br>ZrO2, HfO2 |

| 4 | Function                 | SiH4 Soak          |                            | 0                          | 0                          |

| 5 |                          | Metal Gate Implant | N concentration            | 0                          | 0                          |

| 6 |                          | Channel Material   | Valence Band (SiGe)        | Х                          | 0                          |

| 7 | Fin                      | Fin Width          | Quantum Confinement        | 0                          | 0                          |

| 8 |                          | Channel Doping     | Depletion Charge           | 0                          | 0                          |

# **Chapter 3**

# Process temperature impact on $Si_{1-x}Ge_x$ channel transistor

# 3.1 Background

In this chapter, we first discuss fabrication process flow for Si<sub>1-x</sub>Ge<sub>x</sub> channel pFET. Base process is gate-first metal gate/high-k transistor (Si channel) developed in Interuniversity Microelectronics Centre (imec) described in ref. [66, 67, 68]. Si<sub>1-x</sub>Ge<sub>x</sub> channel pFET was fabricated by adding Si<sub>1-x</sub>Ge<sub>x</sub> epitaxy process on top of the base process flow [47, 69]. We also developed so-called implant free (IF-) Si<sub>1-x</sub>Ge<sub>x</sub> pFET which doesn't have ion implanted source/drain and extension [70, 71]. The details of process flow for those various type of transistor structures is discussed below.

#### 3.2 Transistor structures studied in this work

Summary for device structures studied in this work is shown in Table 3-1. As shown in the table, three kinds of device structure were fabricated. All devices are gate-first metal gate/high-k transistors.

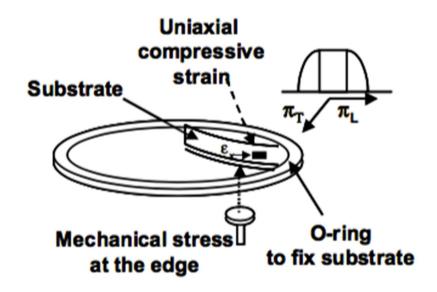

First type of device is Si channel as a reference. For Si channel device, extension, halo and source/drain were formed by ion implantation. We fabricated the device with and without embedded in-situ boron doped SiGe (eSiGe:B) stressor to compare the device performance between them. This technology was firstly introduced into manufacturing by Intel Corporation in their 90 nm node technology to boost pFET performance [72]. It was shown that hole inversion mobility was improved by applying uniaxial compressive strain to pFET channel [73].

Second type of device, so-called conventional Si<sub>1-x</sub>Ge<sub>x</sub> channel device also has ion implanted extensions and source/drain [47, 69]. We have fabricated this type of devices with and without eSiGe:B stressor similarly to Si channel case. The interaction between Si<sub>1-x</sub>Ge<sub>x</sub> channel and eSiGe:B stressor was systematically studied and will be discussed in Chapter 4.

The third device, IF-Si<sub>1-x</sub>Ge<sub>x</sub> channel device has very different device structure from the other two, distinct difference is extension structure. While Si channel and conventional Si<sub>1-x</sub>Ge<sub>x</sub> channel devices have extension created by ion implantation, in IF-Si<sub>1-x</sub>Ge<sub>x</sub> channel device, extension is formed by epitaxial growth of in-situ B doped Si<sub>1-x</sub>Ge<sub>x</sub> and raised from the channel (raised SiGe:B extension) [70]. IF-Si<sub>1-x</sub>Ge<sub>x</sub> devices were also fabricated with and without eSiGe:B stressor [71]. We compared device performance and scalability between IF-Si<sub>1-x</sub>Ge<sub>x</sub> with and without eSiGe:B stressor, the result will be discussed in Chapter 5. For IF-Si<sub>1-x</sub>Ge<sub>x</sub> channel device with eSiGe:B, we fabricated the devices with and without source/drain implant to see the impact on device performance and scalability.

Table 3-1 Summary of transistor structures studied in this work.

| Device type                                            | Channel<br>material               | Extension                   | eSiGe:B<br>Stressor | Source/Drain implant | Reference |

|--------------------------------------------------------|-----------------------------------|-----------------------------|---------------------|----------------------|-----------|

| Si channel                                             | Si                                | BF <sub>2</sub> implant     | ×                   | ×                    |           |

| Conventional Si <sub>1-x</sub> Ge <sub>x</sub> channel | Si <sub>1-x</sub> Ge <sub>x</sub> | BF <sub>2</sub> implant     | ×                   | ×                    | [70]      |

| IF-Si <sub>1-x</sub> Ge <sub>x</sub> channel           | Si <sub>1-x</sub> Ge <sub>x</sub> | Raised<br>SiGe:B<br>epitaxy | ×                   | ×                    | [71]      |

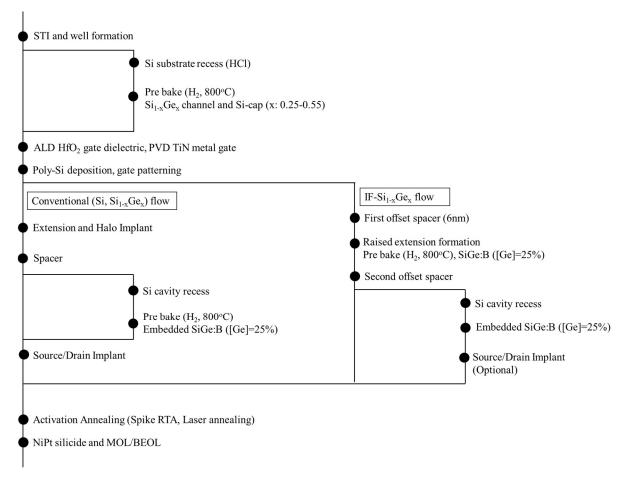

#### 3.3 Device fabrication flow

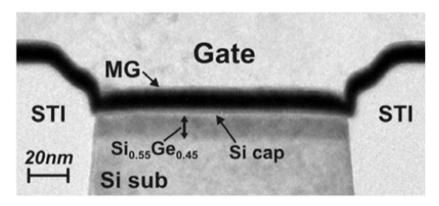

Figure 3-1 shows schematics for process flow for three types of devices summarized in Table 3-1. After STI is formed, well is created by ion implantation. Well anneal is done in furnace to cure the damage in the substrate created by ion implantation. Following the well annealing, Si substrate is recessed by HCl chemical etching before growing Si<sub>1-x</sub>Ge<sub>x</sub> channel. Prior to epitaxial growth of Si<sub>1-x</sub>Ge<sub>x</sub> layer, pre-bake treatment is done with H<sub>2</sub> ambient, at 800°C. This is to remove residual oxygen and moisture (H<sub>2</sub>O) from the Si surface and to achieve atomically clean surface. This helps to reduce potential abnormal epitaxial growth. Si<sub>1-x</sub>Ge<sub>x</sub> film with various Ge concentrations (ranging from 25% to 55%) is epitaxially grown, then Si capping layer follows. Si<sub>1-x</sub>Ge<sub>x</sub> layer and Si capping layer thickness are typically 3 to 7 nm and 1 to 3 nm, respectively. Substrate recess, prebake and epitaxial growth are processed successively in single chamber without air exposure. After Si<sub>1-x</sub>Ge<sub>x</sub> channel/Si-cap is grown, native oxide on top of Si capping is removed by diluted hydrofluoric acid (DHF) and SiO<sub>2</sub>-IL is grown with diluted HCl/O<sub>3</sub> mixture [74]. Thickness of SiO<sub>2</sub>-IL is about 0.8 nm. After SiO<sub>2</sub>-IL formation, HfO<sub>2</sub> is deposited on top of SiO<sub>2</sub>-IL as gate dielectric by ALD method. HfO<sub>2</sub> thickness is 1.8 nm. PDA is done in N2 ambient at 700°C. After PDA, TiN is deposited by physical vapor deposition (PVD) as metal gate electrode. TiN thickness is 2 nm. After TiN deposition, a-Si deposition by CVD and gate patterning follows. Figure 3-2 shows cross-sectional transmission electron microscopy (XTEM) image of Si<sub>1-x</sub>Ge<sub>x</sub> channel device, taken after HfO<sub>2</sub>/TiN and a-Si deposition.

In case of Si channel or conventional  $Si_{1-x}Ge_x$  channel device, extension and halo formation by ion implantation is done after the gate patterning. Ion implantation condition for Si channel device is B, 0.7 keV,  $7 \times 10^{14}$  cm<sup>-2</sup> and F, 10 keV,  $2 \times 10^{15}$  cm<sup>-2</sup> for extension,

As, 40 keV,  $3.5 \times 10^{13} \text{ cm}^{-2}$  for halo. For conventional  $\text{Si}_{1\text{-x}}\text{Ge}_x$  channel device,  $\text{BF}_2$ , 2 keV,  $1 \times 10^{15} \text{ cm}^{-2}$  was used as extension implantation. After extension and halo are formed, sidewall spacer is created to offset the channel and source/drain. In case of devices with eSiGe:B stressor, Si substrate is recessed by about 50 nm to create a cavity, then in-situ boron doped  $\text{Si}_{1\text{-x}}\text{Ge}_x$  is grown by epitaxy at 650°C (pre-bake condition is the same as the one for  $\text{Si}_{1\text{-x}}\text{Ge}_x$  channel growth,  $800^{\circ}\text{C}$ ). Ge concentration in eSiGe:B stressor is 25%, boron concentration is around  $1 \times 10^{20} \text{ cm}^{-3}$ . After eSiGe:B growth, source/drain is created by ion implantation, B, 3 keV,  $3 \times 10^{15} \text{ cm}^{-2}$ .

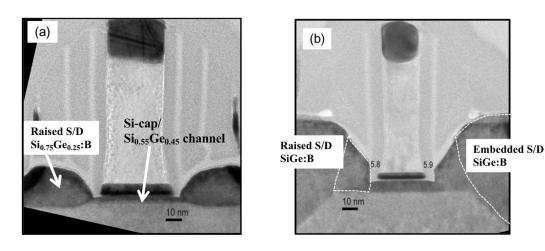

In case of IF-Si<sub>1-x</sub>Ge<sub>x</sub> channel devices, after the gate patterning, first offset spacer (6 nm) is formed and in-situ boron doped Si<sub>1-x</sub>Ge<sub>x</sub> is epitaxially grown as a raised extension. Ge concentration is 25% and boron concentration is around 1×10<sup>20</sup> cm<sup>-3</sup> (same as eSiGe:B stressor). Raised SiGe:B (we call this rSiGe:B in the rest of the thesis) extension thickness is 30 nm. After the rSiGe:B extension formation, second offset spacer is formed. In case of no eSiGe:B stressor, after the second spacer formation, activation anneal is done (this thermal treatment is not meant to activate the dopant but to create a certain amount of overlap between the channel and extension. This will be discussed later). In case eSiGe:B is added for IF-Si<sub>1-x</sub>Ge<sub>x</sub> channel devices, rSiGe:B and Si substrate is recessed (recess depth is 50 nm from gate dielectric – substrate interface) and eSiGe:B is again grown. It should be noted that IF-Si<sub>1-x</sub>Ge<sub>x</sub> channel devices do not receive any halo implantation.

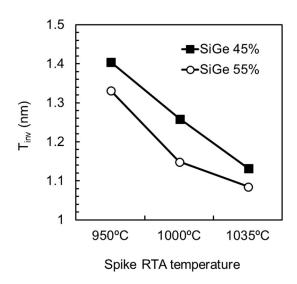

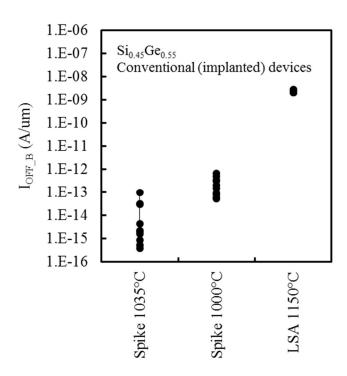

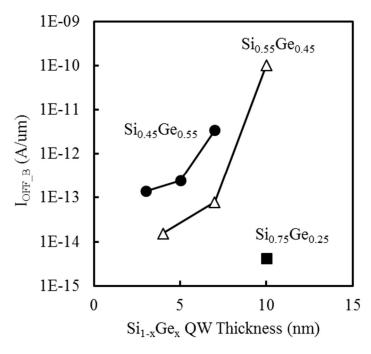

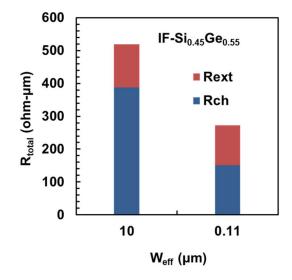

Activation annealing is done either by spike RTA or by laser annealing [66, 68]. Spike RTA temperature is ranging from 950°C to 1035°C. Laser annealing temperature is 1150°C. In case of Si channel and conventional Si<sub>1-x</sub>Ge<sub>x</sub> channel devices, this anneal is literally to activate dopants. On the other hand, in case of IF-Si<sub>1-x</sub>Ge<sub>x</sub> channel devices, this annealing is applied to diffuse boron from rSiGe:B extension and to create a certain

amount of overlap between the channel and extension. With this overlap, external resistance (R<sub>ext</sub>) can be lowered enough to have decent transistor performance.

Then, NiPt silicide is formed to have sufficiently low contact resistance between source/drain material (either Si or Si<sub>0.75</sub>Ge<sub>0.25</sub>) and substrate contact metal (Ti/TiN) [75, 76]. SiO<sub>2</sub> is deposited as ILD and planarized by CMP. MOL and BEOL process completes the device fabrication flow. Figure 3-3 shows XTEM images for (a) IF-Si<sub>1-x</sub>Ge<sub>x</sub> channel device w/o eSiGe:B and (b) w/ eSiGe:B after NiPt silicidation. It should be noted that rSiGe:B extension is still left next to the first offset spacer in case of devices with eSiGe:B.

Figure 3-1 Device fabrication flow.

Figure 3-2 XTEM image of Si<sub>1-x</sub>Ge<sub>x</sub> channel transistor (post metal gate and a-Si deposition) [69].

Figure 3-3 XTEM images of IF-Si<sub>1-x</sub>Ge<sub>x</sub> channel devices. (a) IF-Si<sub>1-x</sub>Ge<sub>x</sub> devices w/o eSiGe:B, (b) IF-Si<sub>1-x</sub>Ge<sub>x</sub> devices w/ eSiGe:B.

# 3.4 Thermal stability of Si<sub>1-x</sub>Ge<sub>x</sub> channel