## T2R2 東京工業大学リサーチリポジトリ Tokyo Tech Research Repository

## 論文 / 著書情報 Article / Book Information

| 題目(和文)            | FPGAとOpenCLによる高性能計算                                                                                                                                                                         |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | High Performance Computing with FPGAs and OpenCL                                                                                                                                            |

| 著者(和文)            | ハミド レザ ゾフーリ                                                                                                                                                                                 |

| Author(English)   | Hamid Reza ZOHOURI                                                                                                                                                                          |

| 出典(和文)            | 学位:博士(学術),<br>学位授与機関:東京工業大学,<br>報告番号:甲第11010号,<br>授与年月日:2018年9月20日,<br>学位の種別:課程博士,<br>審査員:松岡 聡,遠藤 敏夫,額田 彰,横田 理央,中原 啓貴                                                                       |

| Citation(English) | Degree:Doctor (Academic),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第11010号,<br>Conferred date:2018/9/20,<br>Degree Type:Course doctor,<br>Examiner:,,,, |

| <br>学位種別(和文)      | 博士論文                                                                                                                                                                                        |

| Type(English)     | Doctoral Thesis                                                                                                                                                                             |

# **High Performance Computing with FPGAs and OpenCL**

## Hamid Reza Zohouri

Supervisor: Prof. Satoshi Matsuoka

Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

Department of Mathematical and Computing Sciences

Tokyo Institute of Technology

#### **Abstract**

With the impending death of Moore's law, the High Performance Computing (HPC) community is actively exploring new options to satisfy the never-ending need for faster and more power efficient means of computing. Even though GPUs have been widely employed in world-class supercomputers in the past few years to accelerate different types of computation, the high power usage and slow power efficiency improvements of these devices remains a limiting factor in deploying larger supercomputers, especially on the path to Exascale computing. Field-Programmable Gate Arrays (FPGAs) are an emerging alternative to GPUs for this purpose. These devices, despite being older than GPUs, have rarely been used in the HPC industry and have mainly been employed in embedded and low-power markets. Since the traditional applications of FPGAs have vastly different requirements compared to typical HPC application, the usability, productivity and performance of FPGAs for HPC applications is unknown.

In this study, our aim is to determine whether FPGAs can be considered as a viable solution for accelerating HPC applications, and if so, how they fare against existing processors in terms of performance and power efficiency in different HPC workloads. We take advantage of the recent improvements in High Level Synthesis (HLS) that, unlike traditional Hardware Description Languages (HDL) that are known to be notoriously hard to use and debug, allow FPGAs to be more easily programmed by software programmers using familiar software programming languages. Specifically, we use Intel FPGA SDK for OpenCL that allows modern Intel FPGAs to be programmed as an accelerator, similar to GPUs.

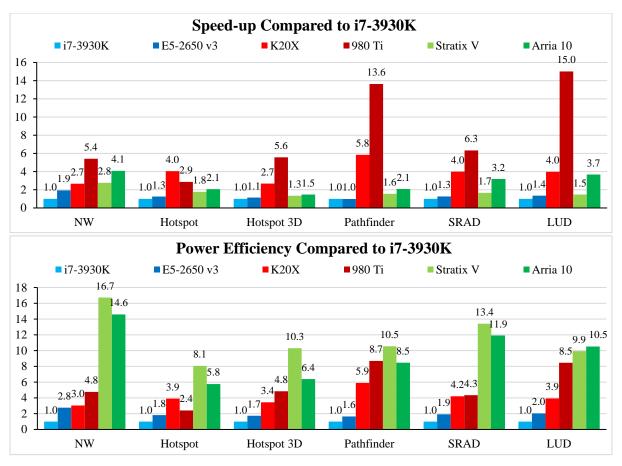

In the first step, we evaluate the performance and power efficiency of FPGAs in different benchmarks, each being a representative of a specific HPC workload. For this purpose, we port a subset of the Rodinia benchmark suite for two generations of Intel FPGAs, and then optimize each benchmark based on the specific architectural characteristics of these FPGAs. Then, we compare the performance and power efficiency of these devices against same-generation CPUs and GPUs. We show that even though a direct port of CPU and GPU kernels for FPGAs usually performs poorly on these devices, with FPGA-specific optimizations, up to two orders of magnitude performance improvement can be achieved, resulting in better performance to that of CPUs in all cases, and competitive performance to that of GPUs in most. Furthermore, we show that FPGAs have a clear power efficiency edge in every case, reaching up to 16.7 and 5.6 times higher power efficiency compared to their same-generation CPUs and GPUs, respectively.

Based on our experience from the initial evaluation, we determine that for stencil computation, which is one of the most important computation patterns in HPC, FPGAs can not only compete with GPUs in terms of power efficiency, but also in terms of pure performance. Taking advantage of the unique architectural advantages of FPGAs for stencil computation, we design and implement a parameterized OpenCL-based template kernel that can be used to

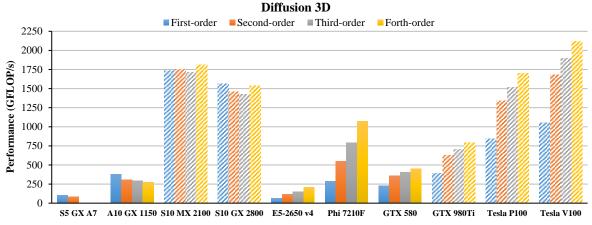

accelerate 2D and 3D star-shaped stencils on FPGAs regardless of stencil order. Our design, apart from using both spatial and temporal blocking, also employs multiple HLS-specific optimizations for FPGAs to maximize performance. Moreover, we devise a performance model that allows us to quickly tune the performance parameters of our design, significantly reducing the time and resources necessary for placement and routing. We show that our design allows FPGAs to achieve superior performance to that of CPUs, GPUs and Xeon Phi devices in 2D stencil computation, and competitive performance for 3D. Specifically, we show that using an Intel Arria 10 GX 1150 device, for 2D and 3D star-shaped stencils of first to fourth-order, we can achieve over 700 and 270 GFLOP/s of compute performance, respectively. Furthermore, we show that our implementation outperforms all existing implementations of stencil computation on FPGAs.

This thesis makes multiple contributions to the emerging field of using FPGAs in HPC, and the optimization techniques discussed in this work can be used as guidelines for optimizing most types of applications on FPGAs using HLS, even for non-HPC applications.

## Acknowledgements

I would like to thank my supervisor, Prof. Satoshi Matsuoka, for giving me the chance to study at Tokyo Tech and be a part of Matsuoka Lab., and providing me with valuable guidance throughout my PhD. I would also like to thank my mentors, Dr. Naoya Maruyama and Dr. Artur Podobas, for their valuable mentorship and helping me walk the path towards a successful PhD.

I would also like to express my gratitude to Matsuoka Lab. research administrators, especially Chisato Saito, for their continuous help and support regarding administration work and life in Japan. Furthermore, I would like to thank my friends and colleagues at Matsuoka Lab. for their help with the many different research and life-related problems I encountered during my stay in Japan.

I would like to thank MEXT for providing me with the scholarship that allowed me to come to Japan and study at Tokyo Tech, one of the best universities in the world. Furthermore, I would like to thank JST, JSPS and OIL for their generous fundings that allowed me to perform my research using state-of-the-art hardware and software. I would also like to thank Intel for donating software licenses through their university program that proved crucial in my research.

Finally, I would like to thank my parents for their continuous support of my life, and their patience and understanding during the years I had to be away from home so that I could focus on my studies; I certainly would not have been able to reach this point without them.

Hamid Reza Zohouri

August 2018

## **Table of Contents**

| A | ostract | •      |                                               | i   |

|---|---------|--------|-----------------------------------------------|-----|

| A | cknow   | ledg   | ements                                        | iii |

| 1 | Intro   | oduct  | tion                                          | 1   |

|   | 1.1     | Mot    | tivation                                      | 1   |

|   | 1.2     | Prol   | olem Statement                                | 2   |

|   | 1.3     | Proj   | posal and Contributions                       | 3   |

|   | 1.4     | The    | sis Outline                                   | 4   |

| 2 | Bacl    | kgroi  | und                                           | 6   |

|   | 2.1     | Fiel   | d-Programmable Gate Arrays (FPGAs)            | 6   |

|   | 2.1     | .1     | FPGA Architecture                             | 6   |

|   | 2.1     | .2     | FPGA Synthesis                                | 8   |

|   | 2.2     | Ope    | enCL Programming Language                     | 8   |

|   | 2.2     | .1     | OpenCL Threading Model                        | 9   |

|   | 2.2     | .2     | OpenCL Memory Model                           | 9   |

|   | 2.3     | Inte   | l FPGA SDK for OpenCL                         | 9   |

|   | 2.3     | .1     | Intel FPGA SDK for OpenCL Flow                | 10  |

|   | 2.3     | .2     | NDRange Programming Model on FPGAs            | 10  |

|   | 2.3     | .3     | Single Work-item Programming Model on FPGAs   | 11  |

|   | 2.3     | .4     | OpenCL Memory Types on FPGAs                  | 11  |

| 3 | Gen     | eral l | Performance Model and Optimizations for FPGAs | 13  |

|   | 3.1     | Gen    | eral Performance Model                        | 13  |

|   | 3.1     | .1     | Single-pipeline Model                         | 13  |

|   | 3.1     | .2     | Extension for Data Parallelism                | 15  |

|   | 3.1     | .3     | General Optimization Guidelines               | 16  |

|   | 3.1     | .4     | Single Work-item vs. NDRange Kernels          | 16  |

|   | 3.2     | HLS    | S-based Optimization Techniques for FPGAs     | 17  |

|   | 3.2     | .1     | Basic Compiler-assisted Optimizations         | 18  |

|   | 3.2     | .2     | Basic Manual Optimizations                    | 19  |

|   | 3.2     | .3     | Advanced Compiler-assisted Optimizations      | 22  |

|   | 3.2     | .4     | Advanced Manual Optimizations                 | 25  |

| 4 | Eval    | uatii  | ng FPGAs for HPC Applications Using OpenCL    | 31  |

|                 | 4.1 | Bac   | kground                                            | 31 |

|-----------------|-----|-------|----------------------------------------------------|----|

| 4.2 Methodology |     | Met   | hodology                                           | 31 |

|                 | 4.2 | 2.1   | Benchmarks                                         | 31 |

|                 | 4.2 | 2.2   | Optimization Levels                                | 32 |

|                 | 4.2 | 2.3   | Hardware and Software                              | 33 |

|                 | 4.2 | 2.4   | Timing and Power Measurement                       | 34 |

|                 | 4.3 | Res   | ults                                               | 35 |

|                 | 4.3 | 3.1   | Stratix V                                          | 35 |

|                 | 4.3 | 3.2   | Arria 10                                           | 51 |

|                 | 4.3 | 3.3   | CPUs                                               | 53 |

|                 | 4.3 | 3.4   | GPUs                                               | 54 |

|                 | 4.3 | 3.5   | Comparison                                         | 54 |

|                 | 4.4 | Rela  | ated Work                                          | 56 |

|                 | 4.5 | Pub   | lication Errata                                    | 60 |

|                 | 4.6 | Con   | clusion                                            | 60 |

| 5               | Hig | h-Per | formance Stencil Computation on FPGAs Using OpenCL | 62 |

|                 | 5.1 | Bac   | kground                                            | 62 |

|                 | 5.1 | .1    | Stencil Computation                                | 62 |

|                 | 5.1 | .2    | Spatial Blocking                                   | 63 |

|                 | 5.1 | .3    | Temporal Blocking                                  | 63 |

|                 | 5.2 | Rela  | ated Work                                          | 63 |

|                 | 5.3 | Imp   | lementation                                        | 65 |

|                 | 5.3 | 3.1   | Spatial Blocking on FPGAs                          | 66 |

|                 | 5.3 | 3.2   | Temporal Blocking on FPGAs                         | 69 |

|                 | 5.3 | 3.3   | FPGA-specific Optimizations                        | 70 |

|                 | 5.3 | 3.4   | Support for High-order Stencils                    | 72 |

|                 | 5.4 | Perf  | Formance Model                                     | 73 |

|                 | 5.5 | Met   | hodology                                           | 76 |

|                 | 5.5 | 5.1   | Benchmarks                                         | 76 |

|                 | 5.5 | 5.2   | Hardware Setup                                     | 77 |

|                 | 5.5 | 5.3   | Software Setup                                     |    |

|                 | 5.5 | 5.4   | Performance and Power Measurement                  | 81 |

|                 | 5 5 | 5 5   | Benchmark Settings                                 | 81 |

|    | 5.6     | Perf        | formance Tuning                       | 82  |

|----|---------|-------------|---------------------------------------|-----|

|    | 5.6     | 5.1         | Xeon and Xeon Phi                     | 82  |

|    | 5.6     | 5.2         | GPU                                   | 82  |

|    | 5.6     | 5.3         | FPGA                                  | 82  |

|    | 5.7     | Resu        | ults                                  | 84  |

|    | 5.7     | <b>'</b> .1 | FPGA Results                          | 84  |

|    | 5.7     | '.2         | Model Accuracy                        | 89  |

|    | 5.7     | '.3         | Performance Projection for Stratix 10 | 91  |

|    | 5.7     | '.4         | Comparison with Other Hardware        | 96  |

|    | 5.7     | '.5         | Comparison with Other FPGA Work       | 102 |

|    | 5.8     | Publ        | lication Errata                       | 104 |

|    | 5.9     | Con         | clusion                               | 105 |

| 6  | Sun     | nmary       | y and Insights                        | 109 |

|    | 6.1     | Sum         | nmary                                 | 109 |

|    | 6.2     | Insig       | ghts                                  | 110 |

| R  | eferen  | ces         |                                       | 113 |

| Ρι | ıblicat | tions.      |                                       | 121 |

## **List of Figures**

| 2-1 Intel Arria 10 FPGA architecture                                           | 6   |

|--------------------------------------------------------------------------------|-----|

| 2-2 Intel Arria 10 ALM architecture                                            | 7   |

| 2-3 Intel Arria 10 DSP architecture                                            | 7   |

| 2-4 Intel FPGA SDK for OpenCL flow                                             | 10  |

| 2-5 Pipeline generation for (a) NDRange and (b) Single Work-item kernels       | 11  |

| 2-6 NDRange (a) vs. Single Work-item (b) code example                          | 12  |

| 3-1 NDRange (a) vs. Single Work-item (b) pipeline model                        |     |

| 3-2 Pipeline model for data parallelism                                        | 16  |

| 3-3 Data sharing in (a) NDRange and (b) Single Work-item kernels               | 17  |

| 3-4 Shift register optimization for floating-point reduction                   | 20  |

| 3-5 Optimized floating-point reduction with unrolling                          | 21  |

| 3-6 Shift register inference                                                   | 26  |

| 3-7 Reducing Block RAM replication by using temporary registers                | 28  |

| 3-8 Reducing Block RAM replication by transposing the buffer                   | 28  |

| 3-9 Loop collapse optimization                                                 | 29  |

| 3-10 Exit condition optimization.                                              | 30  |

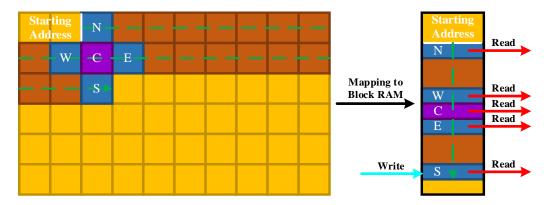

| 4-1 NW implementation                                                          | 36  |

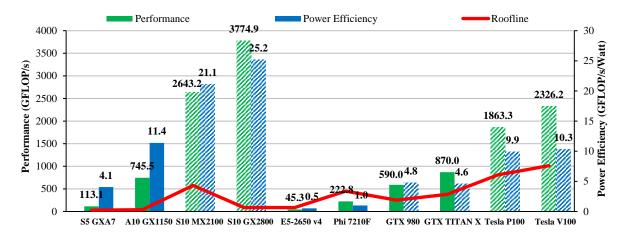

| 4-2 Performance and Power Efficiency Comparison Between Different Hardware     | 55  |

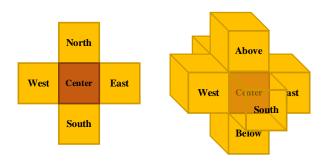

| 5-1 First-order 2D and 3D stencils                                             | 62  |

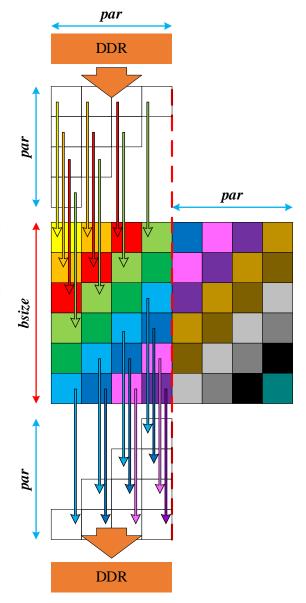

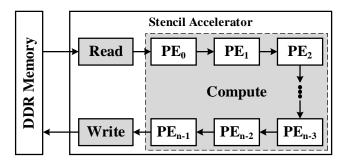

| 5-2 Overview of stencil accelerator                                            | 66  |

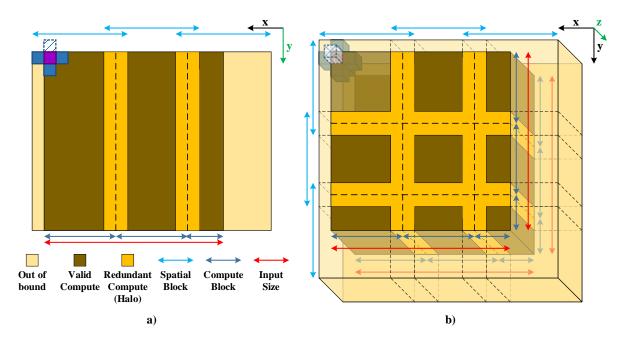

| 5-3 Spatial blocking in a) 2D and b) 3D stencils                               | 67  |

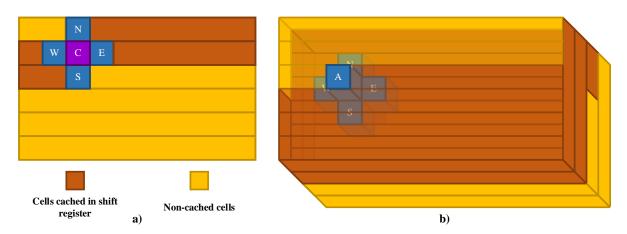

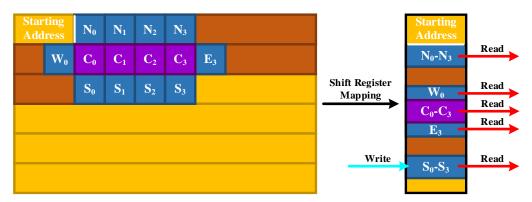

| 5-4 Shift register for spatial blocking in a) 2D stencils and b) 3D stencils   | 68  |

| 5-5 Spatial blocking with vectorization                                        | 68  |

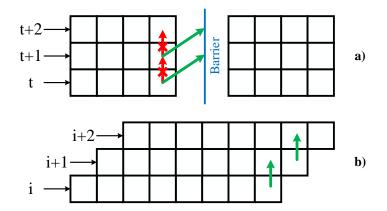

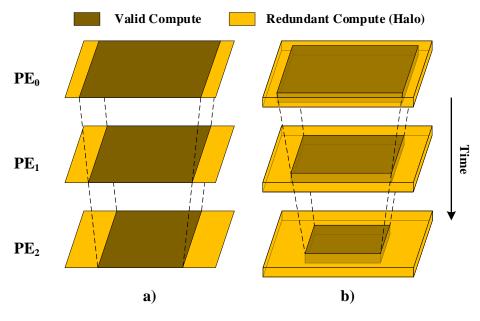

| 5-6 Temporal blocking for a) 2D stencils and b) 3D stencils                    | 69  |

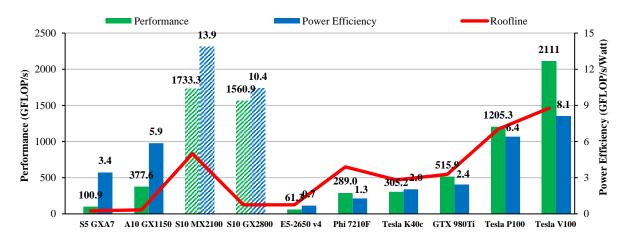

| 5-7 Performance results for first-order 2D stencil computation on all hardware | 96  |

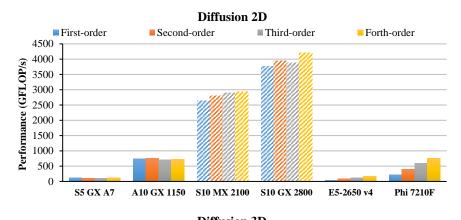

| 5-8 Performance results for first-order 3D stencil computation on all hardware | 97  |

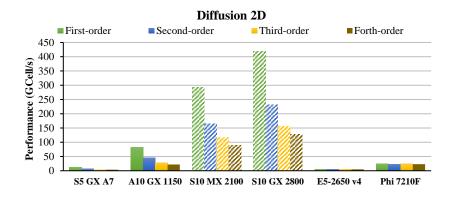

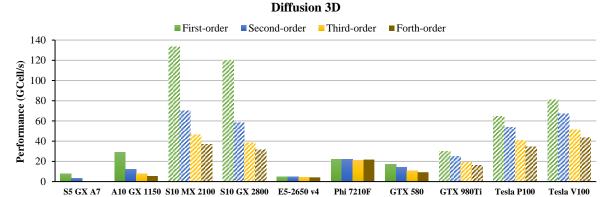

| 5-9 Performance of High-order Diffusion 2D and 3D in GCell/s                   | 101 |

| 5-10 Performance of High-order Diffusion 2D and 3D in GFLOP/s                  | 101 |

## **List of Tables**

| 4-1 FPGA Device Characteristics                                                  | 33 |

|----------------------------------------------------------------------------------|----|

| 4-2 Evaluated Hardware and Their Characteristics                                 | 34 |

| 4-3 Performance and Area Utilization of NW on Stratix V                          | 38 |

| 4-4 Performance and Area Utilization of Hotspot on Stratix V                     | 40 |

| 4-5 Performance and Area Utilization of Hotspot 3D on Stratix V                  | 42 |

| 4-6 Performance and Area Utilization of Pathfinder on Stratix V                  | 44 |

| 4-7 Performance and Area Utilization of SRAD on Stratix V                        | 47 |

| 4-8 Performance and Area Utilization of LUD on Stratix V                         | 50 |

| 4-9 Performance and Power Efficiency of All Benchmarks on Stratix V and Arria 10 | 52 |

| 4-10 Performance and Power Efficiency Results of All Benchmarks on CPUs          | 53 |

| 4-11 Performance and Power Efficiency Results of All Benchmarks on GPUs          | 54 |

| 5-1 Model Parameters                                                             | 74 |

| 5-2 Stencil Characteristics                                                      | 77 |

| 5-3 FPGA Device Characteristics                                                  | 78 |

| 5-4 Hardware Characteristics                                                     | 80 |

| 5-5 Number of DSPs Required for One Cell Update on Arria 10                      | 83 |

| 5-6 Configuration and Performance of First-order Stencils on FPGAs               | 85 |

| 5-7 Configuration and Performance of High-order Stencils on FPGAs                | 88 |

| 5-8 Performance Projection Results for Stratix 10                                | 94 |

| 5-9 Performance and Power Efficiency of High-order Stencil Computation           | 99 |

#### 1 Introduction

#### 1.1 Motivation

For many years, non-stop improvements in computer technology in terms of both performance and power efficiency have been driven by the Moore's Law [1] and Dennard Scaling [2]. However, with Moore's Law losing steam, and Dennard Scaling coming to an end, the age of Dark Silicon [3] is closer than ever. High Performance Computing (HPC), which relies on latest cutting-age hardware to satisfy the never-ending need for higher performance and power efficiency, is going to be most impacted by this new age. This has forced the HPC community to employ specialized accelerators in the past few years. So far, GPUs have been the most popular accelerator to be used for HPC applications. However, these devices are also impacted by the impending death of Moore's law just like CPUs. Apart from that, GPUs are power-hungry devices that can consume up to 300 Watts and power efficiency improvements in GPUs is reaching its limit. With power consumption and efficiency being the main bottleneck in designing and employing large HPC machines, the usability of GPUs in large supercomputers is subject to many power and cooling limitations.

FPGAs are one of the accelerators that are recently emerging as more power-efficient alternatives to GPUs. Even though these devices are older than GPUs, they have been traditionally designed for low-power and embedded markets and have had limited computational capabilities. Furthermore, these devices were traditionally programmed using Hardware Description Languages (HDL), mainly Verilog and VHDL, that are based on a vastly different programming model compared to standard software programming languages like C and Fortran. This issue has always been a major roadblock in adoption of FPGAs among software programmers.

For many years, High Level Synthesis (HLS) tools have been developed to make FPGAs usable by software programmers. Such tools allow software programmers to describe their FPGA design in a standard software programming language, and then convert this *high-level* description to a *low-level* description based on Verilog or VHDL. Many such tools have been developed since the inception of HLS; however, rarely any of them have been endorsed or supported by the major FPGA manufacturers, namely Intel PSG (formerly Altera) and Xilinx. Recently, Xilinx acquired AutoESL [4] and based on that, developed Vivado HLS [5] that allows conversion of C and C++ code to low-level FPGA descriptions. Later, Altera (now Intel PSG) introduced their OpenCL SDK [6] to provide a similar possibility for software programmers based on the open-source and royalty-free OpenCL programming language. Eventually, Xilinx followed suit and introduced their OpenCL SDK named SDAccel [7]. With official HLS tools being directly developed and supported by FPGA manufacturers, a sudden shift in the HLS ecosystem happened that enabled more widespread adoption of FPGAs among software programmers.

In 2014, the very first large-scale adoption of FPGAs in a cloud system was kick-started by Microsoft under the Catapult project [8]. Microsoft specifically chose to employ FPGAs instead of GPUs due to lower power and space requirement of FPGAs, which allowed them to achieve a notable improvement in the performance of the Bing search engine, with minimal changes in the design of their data center. Later, Intel introduced their new Arria 10 FPGA family which, for the first time in the history of FPGAs, included DSPs with native support for floating-point operations [9]. This radical change in FPGA architecture paved the way for adoption of FPGAs in the HPC market that largely relies on floating-point computation. Since the past year, FPGAs have also become available in commercial cloud platforms like Amazon AWS [10] and Nimbix [11].

#### 1.2 Problem Statement

FPGAs are relatively new in the HPC ecosystem and it is not clear how suitable they are for accelerating HPC applications. On top of that, existing HLS tools are much less mature compared to widely-used software compilers and hence, it is not known how well they perform on a given FPGA for different application types. Moreover, optimization techniques for different types of applications have been widely studied on CPUs and GPUs, while there is little existing work on optimizing HPC applications on FPGAs using HLS.

Despite the recent advancements in FPGA technology, these devices are still behind GPUs in terms of both compute performance and external memory bandwidth. For example, an Arria 10 GX 1150 FPGA with full DSP utilization operating at the peak DSP operating frequency of 480 MHz [9] provides a peak single-precision floating-point compute performance of 1.45 GFLOP/s. Furthermore, typical Arria 10 FPGA boards [12] are coupled with two banks of DDR4 memory running at 2133 MHz (1066 double data-rate), and a 64-bit bus to each bank, which provides only 34.1 GB/s of external memory bandwidth. Compared to the same-generation NVIDIA GTX 980 Ti GPU, with a compute performance of 6900 GFLOP/s and external memory bandwidth of 336.6 GB/s, the Arria 10 FPGA is at a 4.75x disadvantage in terms of compute performance, and a ~10x disadvantage in terms of external memory bandwidth. However, the TDP of the Arria 10 FPGA is 3.9x lower (70 Watts vs. 275 Watts), potentially allowing this FPGA to achieve better power efficiency than the GTX 980 Ti GPU if high computational efficiency can be achieved on the FPGA.

Considering the major architectural differences between FPGAs and CPUs/GPUs, it is not clear how well existing CPU and GPU code perform on FPGAs and how well typical CPU or GPU-based optimizations affect performance on FPGAs, if at all. Unlike CPUs and GPUs, FPGAs do not have a cache hierarchy; however, modern FPGAs provide a large amount of onchip memory (6.6 MB on Arria 10 GX 1150) which can be used as scratchpad memory. Furthermore, high-performance CPU and GPU applications largely rely on the multi-threading capabilities of these devices while being forced to align with SIMD and vectorization limitations of such hardware that is the result of their fixed architecture. However, no such restrictions exist on FPGAs due to their reconfigurable nature, giving the programmer much

more design flexibility at the cost of larger design exploration space and long placement and routing time.

### 1.3 Proposal and Contributions

In the first part of our study, to study the usability and performance of FPGAs in HPC, we evaluate FPGAs in a set of benchmarks that are representative of typical HPC workloads. We port a subset of the well-known Rodinia benchmark suite [13] for Intel FPGAs and compare the performance and power efficiency of two FPGA generations to that of their same-generation CPUs and GPUs. In this part of our study, we make the following contributions:

- We devise a general performance model for computation on FPGAs and use this model as a guide for optimizing FPGA kernels. Based on this model, we show that the traditional NDRange OpenCL programming that is used on GPUs and takes advantage of thread-level parallelism is usually not suitable for FPGAs. Instead, the Single Workitem model that takes advantage of pipelined parallelism matches better with the underlying FPGA architecture and achieves better performance in most cases.

- We present a comprehensive list of HLS-based optimization techniques for FPGAs, ranging from basic compiler-assisted optimizations to advanced manual optimizations, and describe how each of them is expected to affect performance on an FPGA based on our model.

- We show that a direct port of kernels that are optimized for CPUs and GPUs perform poorly on FPGAs. However, by using advanced optimizations techniques that take advantage of the unique architectural features of FPGAs, we can achieve over an order of magnitude performance improvement compared to direct ports.

- We show that in some applications, FPGAs can achieve competitive performance to that

of their same-generation GPUs, and in all of our studied applications, they achieve better

power efficiency up to 5.6 times higher. Furthermore, FPGAs can achieve better

performance and power efficiency compared to their same-generation CPUs in every

case.

Based on our experience from the first part of our study, we conclude that one of the computation patterns in HPC that FPGAs can excel at is stencil computation. Hence, we further focus on this computation pattern to maximize the performance of applications based on this type of computation on FPGAs. In this part of our study, we make the following contributions:

- We create an FPGA-based accelerator for stencil computation that uses two parameterized OpenCL template kernels, one for 2D stencils and one for 3D, to quickly implement different stencils. Apart from performance parameters, stencil radius is also parameterized in our kernel so that high-order stencils, which are widely used in HPC applications, can also be accelerated on FPGAs using our design.

- Unlike many previous work on accelerating stencil computation on FPGAs that take advantage of temporal blocking but avoid spatial blocking to achieve maximize performance at the cost of restricting the size of the input in multiple dimensions, we

- combine spatial and temporal blocking and show that it is possible to achieve high performance without such restrictions.

- We tackle the issues arisen from the added design complexity due to multiple levels of blocking and multiply-nested loops in our design by taking advantage of multiple HLSbased FPGA-specific optimizations.

- We devise a performance model for our FPGA-based stencil computation accelerator that allows us to quickly tune the performance parameters in our design and minimize the number of configurations that need to be placed and routed. This significantly reduces the amount of time and computational resources that is necessary for parameter tuning on FPGAs.

- We show that for first to fourth-order star-shaped 2D and 3D stencils, we can achieve over 700 GFLOP/s and 270 GFLOP/s of compute performance, respectively, on an Arria 10 GX 1150 device. This level of performance is superior to that of CPUs, Xeon Phi and GPUs for 2D stencil computation, and competitive or better in 3D. Furthermore, the FPGA remains the most power efficient device in nearly all cases.

- Using our performance model, we project the performance of our evaluated stencils for the upcoming Intel Stratix 10 FPGAs and show that these devices can achieve up to 4.2 TFLOP/s and 1.8 TFLOP/s of compute performance, for 2D and 3D stencil computation, respectively. This level of performance is expected to be superior to that of modern GPUs for 2D stencils, and competitive for 3D, with superior power efficiency in every case.

#### 1.4 Thesis Outline

The remaining chapters of this thesis are outlined as follows:

- **Background:** In this chapter, we briefly discuss the architecture of FPGAs, the OpenCL programming model and Intel FPGA SDK for OpenCL.

- General Performance Model and Optimizations for FPGAs: In this chapter, we first discuss our general performance model for computation on FPGAs and based on that, demonstrate the differences between NDRange and Single Work-item programming models and give guidelines as to which is preferred depending on the target application. Then, we present a set of code optimization techniques, ranging from basic compile-assisted optimizations to advanced manual optimizations and describe how each maps to our model.

- Evaluating FPGAs for HPC Applications Using OpenCL: In this chapter, we discuss the details of porting and optimizing a subset of the Rodinia benchmark suite based on the optimization techniques from the previous chapter and show the effect of different levels of optimization on performance. Then, we compare each benchmark on each FPGA with its same-generation CPU and GPU in performance and power efficiency.

- **High-Performance Stencil Computation on FPGAs Using OpenCL:** In this chapter, we first discuss our implementation of first-order stencil computation on FPGAs using combined spatial and temporal blocking. Then we extend this implementation to high-

order stencils. In the next step, we present our performance model for our stencil accelerator, which is used to prune our parameter search space. Finally, we project the performance of our evaluated stencils for the upcoming Stratix 10 FPGAs and compare the performance and power efficiency of our design on Stratix V, Arria 10 and Stratix 10 FPGAs with multiple CPU, GPU and Xeon Phi devices.

• **Summary and Insights:** In the final chapter, we summarize our work and present insights we obtained from the study.

## 2 Background

#### 2.1 Field-Programmable Gate Arrays (FPGAs)

#### 2.1.1 FPGA Architecture

FPGAs are generally regarded as a middle-ground between ASICs and general-purpose processors. This notion comes from the reconfigurable nature of these devices, making them more flexible than ASICs (at the cost of lower area and power efficiency) and more power efficient than general-purpose processors (at the cost of lower flexibility and more complex programming). Even though, deep down, FPGAs have a fixed architecture, they are largely composed of SRAM cells arranged in form of Loop-Up Tables (LUT), a plethora of registers, and programmable routing. Because of this, these devices can be rapidly reconfigured to implement different logic, just by changing the content of the LUTs and the routing configuration. Apart from the *soft-logic* LUTs, modern FPGAs also include *hard-logic* components such as Digital Signal Processors (DSP), large memory blocks (Block RAMs) and different I/O controllers (DDR, PCI-E, network, etc.). These components implement specialized logic that would otherwise take up too much space if implemented using LUTs.

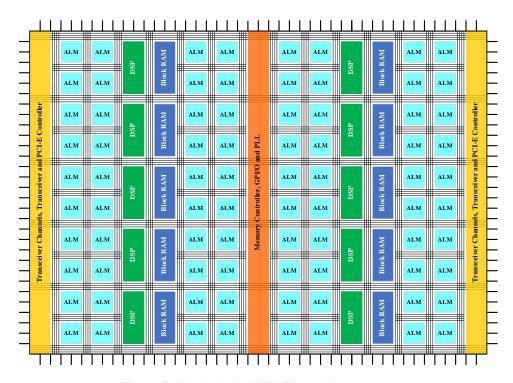

Fig. 2-1 shows the architecture of the Intel Arria 10 FPGA [14]. In this FPGA, the soft-logic consists of Adaptive Logic Modules (ALM), and the hard-logic consists of DSPs, Block RAMs, multiple controllers, Transceivers and Phase-Locked Loops (PLL).

Figure 2-1 Intel Arria 10 FPGA architecture

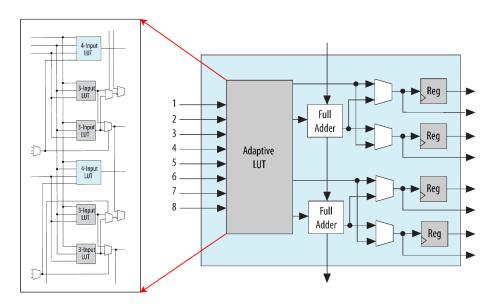

In the Arria 10 FPGA, each ALM consists of multiple-input LUTs, adders and carry logic, and registers (Flip-Flops). The internal architecture of the ALMs in the Arria 10 FPGA is depicted in Fig. 2-2. Each Adaptive LUT is capable of implementing multiple combinations of different functions including one 6-input function, two 5-input functions with two shared inputs, two 4-input functions with independent inputs, etc.

Figure 2-2 Intel Arria 10 ALM architecture; combined from Fig. 5 in [14] and Fig. 7 in [15]

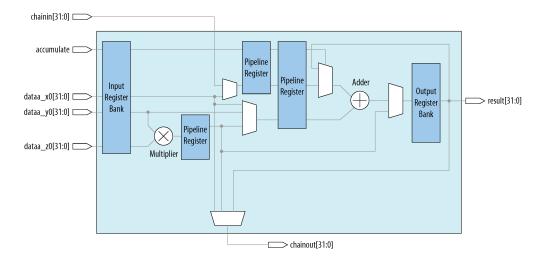

Fig. 2-3 shows the block diagram of the DSPs in the Intel Arria 10 FPGA. Each of these DSPs is capable of implementing an IEEE-754-compliant single-precision floating-point addition (FADD), multiplication (FMUL), or Fused Multiply and Add (FMA) operation, or one 27-bit-by-27-bit integer or fixed-point multiplication. Furthermore, multiple DSPs can be chained to implement dot products or other complex operations.

Figure 2-3 Intel Arria 10 DSP architecture; taken from Fig. 27 in [15]

Finally, each Block RAM in the Intel Arria 10 device, called an M20K block, is capable of storing a maximum of 20 Kbits of data. Each block has two ports that operate independently,

and can satisfy one read and one write operation simultaneously. Data can be stored in each block with a maximum width of 40 bits, in which case the address size will be 9 bits (512 addresses). Apart from implementing multiple-ported RAM or ROMs, each M20K can also be used to implement First-In First-Out buffers (FIFO) or shift registers. Multiple M20K blocks can also be chained to implemented larger buffers.

#### 2.1.2 FPGA Synthesis

Traditionally, to create an FPGA design, the application is described using a Hardware Description Language (HDL) like Verilog or VHDL, and then multiple steps are carried out until an FPGA bitstream is created. First, the hardware description is *synthesized* into a netlist. All coding errors are determined in this step. In the next step, the mapping process maps all functions in the netlist to functions that are available as hard-logic on the FPGA; any other function will be implemented using soft-logic (LUTs). After that, the placement process determines which of the multiple instances of each function on the FPGA should be used for implementing the functions that are required by the design. If a design requires more instances of a specific function than are available on the FPGA, placement will fail. In the next step, the routing process will determine which routing resources are used and how they are connected so that all functions are correctly connected to each other and all timing constraints are met. Since routing resources are limited, routing could also fail in case of routing congestion. Finally, the FPGA bitstream is generated. The bitstream is generally transferred to the FPGA using JTAG to implement the synthesized design on the hardware. This chain of operations is the equivalent of compilation for software programs, and all this functionality is provided by the FPGA manufacturers' tools. In case of Intel, these functions are provided by Intel Quartus Prime Software. For the Intel Stratix V FPGA, total synthesis time is typically 3 to 5 hours but can reach up to 8 hours, while for the larger Arria 10 device it is typically 8 to 12 hours but can take over a day for very large designs that suffer from severe routing congestion.

#### 2.2 OpenCL Programming Language

OpenCL [16] is an open-source and royalty-free standard for programming heterogeneous systems in a host/device fashion. An OpenCL-based application can be split into two separate parts: one is the *host* code that executes on the host CPU and can be written in any programing language as long as a compatible compiler exists, and the other is a C-based *device* code that is more commonly called the *kernel* code. OpenCL provides the necessary APIs for controlling the accelerator and communicating between the host processor and the accelerator. This programming language can be considered as a device-agnostic alternative to the NVIDIA CUDA programming language.

The typical flow of operation in OpenCL is that first, all necessary data is allocated in host memory. Then, this data is transferred to the device memory using the respective OpenCL functions. In the next step, the kernel is loaded and executed on the device, where inputs are read from and outputs are written to the device memory. Finally, output data is transferred from the device memory to the host.

#### 2.2.1 OpenCL Threading Model

In OpenCL, each thread is called a *work-item* and multiple work-items are grouped to form a *work-group*. To execute an application, the thread space is distributed over multiple work-groups. Within each work-group, work-items are synchronized using *barriers* and data can be shared between the work-items using the fast on-chip *local memory*. However, the only way to share data between different work-groups is through the slow off-chip memory. The number of work-items in a work-group is called the *local work size*, and the total number of work-items necessary to fully execute an application is called the *global work size*. Work-items and work-groups can be arranged in multiple dimensions, up to three, in an index space called an *NDRange*.

#### 2.2.2 OpenCL Memory Model

In OpenCL, multiple memory types are defined:

**Global:** This memory space resides on the device off-chip (external) memory and is generally the largest (up to a couple Gigabytes) but slowest memory that exists on an OpenCL-capable accelerator. The content of this memory space is visible to all work-items of all work-groups. Global memory consistency is only guaranteed after a kernel is executed completely.

**Local:** This memory space resides on the on-chip memory of the OpenCL device and can be used to share data between the work-items within a work-group. Each work-group has its own local memory space, and the local memory space of a work-group is not visible to other work-groups. The total amount of local memory available on OpenCL accelerators is typically a few to a couple Megabytes. Local memory consistency is only guaranteed at *barriers*.

**Constant:** This memory space resides on device external memory; however, this is a readonly memory space and is generally cached in device on-chip memory for faster access.

**Private:** Any work-item-specific buffer or array is of this memory type. Private data generally resides on the fast device registers; however, due to very limited size (a few hundred Kilobytes per device), data stored in this memory space can leak to global memory, incurring a large performance penalty.

#### 2.3 Intel FPGA SDK for OpenCL

Intel FPGA SDK for OpenCL provides the necessary APIs and run-time to program and use PCI-E-attached or System-on-Chip (SoC) FPGAs similar to a GPU or other accelerators. The necessary IP Cores to communicate between the FPGA, external DDR memory, and PCI-E, alongside with necessary PCI-E and DMA drivers for communication between the host and the FPGA are also provided by the board manufacturers in form of a Board Support Package (BSP). This relieves the programmer from the burden of having to manually set up the IP Cores and create the drives, as is done with traditional HDL-based FPGA designs. Some BSPs also provide the possibility to send and receive data using FPGA on-board network ports.

#### 2.3.1 Intel FPGA SDK for OpenCL Flow

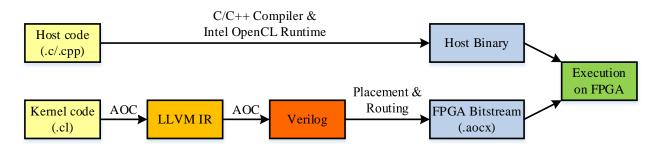

Fig. 2-4 shows the flow of Intel FPGA SDK for OpenCL (formerly Altera SDK for OpenCL) to compile the host code and convert the kernel code to an FPGA-compatible bitstream.

Figure 2-4 Intel FPGA SDK for OpenCL flow; AOC is Intel FPGA SDK for OpenCL Offline Compiler

Unlike CPUs and GPUs, run-time compilation of OpenCL kernels is not possible for FPGAs due to very long placement and routing time. Hence, the OpenCL kernel needs to be compiled offline into an FPGA bitstream, and then loaded at run-time by the host code to reprogram the FPGA and execute the application.

#### 2.3.2 NDRange Programming Model on FPGAs

GPUs typically consist of a set of coarse-grained processing units (called Compute Units in AMD GPUs and Streaming Multiprocessors in NVIDIA GPUs), with each such unit containing a fixed number of fine-grained shader processors and a fixed amount of scratchpad memory and L1 cache. In the NDRange programming model, a work-group is generally mapped to one of the coarse-grained units, and each work-item is mapped to one of the finegrained shared processors. However, the aforementioned decomposition to coarse and finegrained units does not exists on FPGAs. By default, using the NDRange programming model on FPGAs will *not* result in thread-level parallelism and instead, the compiler will generate one compute unit implemented as a deep pipeline, with all work-items from all work-groups executing on that pipeline. Each region between two barriers in an NDRange kernel will be mapped to a separate pipeline, with each pipeline being flushed at the barrier. The compiler also automatically performs work-group pipelining, allowing multiple work-groups to be inflight in the same compute unit simultaneously to maximize the efficiency of all the pipelines in the compute unit, at the cost of higher Block RAM usage. Fig. 2-5 a) shows how two consecutive threads/work-items are pipelined with a distance from each other, called the Initiation Interval (II). The initiation interval is adjusted at run-time by the run-time scheduler that the compiler implements on the FPGA to minimize pipeline stalls and maximize pipeline efficiency.

Intel FPGA SDK for OpenCL provides a SIMD attribute for the NDRange programming model that allows achieving work-item-level parallelism on the FPGA. Using this attributes, the pipeline is widened and pipeline stages are replicated so that multiple work-items can be

issued in parallel by the scheduler in a compute unit. This programming model also provide the possibly to replicate the compute unit so that work-group-level parallelism can be achieved. Mixing SIMD and compute unit replication allows the programmer to achieve a GPU-like architecture on an FPGA, with the compute units acting as the coarse-grained processing units, and each set of the vectorized pipeline stages acting as a fine-grained unit.

Figure 2-5 Pipeline generation for (a) NDRange and (b) Single Work-item kernels

#### 2.3.3 Single Work-item Programming Model on FPGAs

Apart from the NDRange model, Intel FPGA SDK for OpenCL also provides another programming model called the *Single Work-item* model. In the model, the entire kernel is executed by one work-item and instead, loop iterations are pipelined to achieve high performance. When this programming model is used, each set of nested loops in the kernel is mapped to a separate pipeline by the compiler. Fig. 2-5 b) depicts how two consecutive iterations of a loop are pipelined one after another. Using this model, no run-time scheduler will be created in the hardware anymore and instead, iteration scheduling is static and initiation interval is determined at compile-time depending on loop-carried and memory load/store dependencies. Iteration-level parallelization in form of vectorization can be achieved in this programming model by *loop unrolling*.

Fig. 2-6 a) shows a basic example of an NDRange kernel and b) shows its equivalent Single Work-item kernel. Converting an NDRange kernel to Single Work-item can be done by wrapping the NDRange kernel in a *for* loop from zero to global work size in every dimension.

#### 2.3.4 OpenCL Memory Types on FPGAs

Using Intel FPGA SDK for OpenCL, OpenCL **global** memory resides on the FPGA external memory, which is usually a few banks of DDR3 or DDR4 memory. OpenCL **local** and **private** memory, depending on the size and access pattern of the buffer, will be implemented using registers or Block RAMs. Finally, **constant** memory is also implemented using Block RAMs with a fixed size that can be controlled using a compilation argument.

```

__kernel void ndrange(__global float* a, __global float* b)

{

int i = get_global_id(0);

a[i] = b[i];

}

a)

__kernel void single_wi(__global float* a, __global float* b, int global_size)

{

for (int i = 0; i < global_size; i++)

{

a[i] = b[i];

}

}</pre>

```

Figure 2-6 NDRange (a) vs. Single Work-item (b) code example

# 3 General Performance Model and Optimizations for FPGAs

In this chapter, we will discuss our general performance model for FPGAs starting from a single-pipeline model and then extending it for data parallelism. Then, we outline the difference between the two programing models available in Intel FPGA SDK for OpenCL based on this model. In the next step, we discuss multiple HLS-based optimization techniques for FPGAs ranging from basic compiler-assisted optimizations to advanced manual optimizations, and explain how each relates to our model. The contents of this chapter have been partially published in [17].

#### 3.1 General Performance Model

#### 3.1.1 Single-pipeline Model

For a given pipeline with a depth of P, a loop trip count of L (i.e. number of inputs) and an initiation interval of II, the total number of clock cycles to finish computation is:

$$T_{cvcle} = P + II \times (L - 1) \tag{3-1}$$

Here, P cycles are required until the pipeline is filled and the first output is generated, and after that, a new output is generated every II cycles. To convert this value to time, we have:

$$T_{seconds} = \frac{T_{cycle}}{f_{max}} = \frac{P + II \times (L - 1)}{f_{max}}$$

(3-2)

In Eq. (3-2),  $f_{max}$  is the operating frequency of the FPGA that is determined after placement and routing and is typically between 150 to 350 MHz on Intel Stratix V and Arria 10 devices. Among the parameters in Eq. (3-2), P is controlled by the compiler; however, as a general rule of thumb, simpler code will result in a shorter pipeline and lower P. L is also application-dependent and cannot be directly controlled by the user.  $f_{max}$  is also generally a function of circuit complexity and size. Loop-carried dependencies and feedbacks in the design will adversely affect  $f_{max}$ . Moreover, the bigger the design is and the closer utilization of each resource is to 100%, the more  $f_{max}$  will be lowered due to placement and routing complications. In Section 3.2.4.4, we will show an advanced optimization technique that can significantly improve  $f_{max}$  in Single Work-item kernel. The only remaining parameter is II. This parameter is the one that can be most directly influenced by the programmer and hence, most of the performance optimization effort will be spent on improving this parameter.

II is influenced by multiple factors: loop-carried dependencies, shared on-chip resources like shared ports to local memory buffers implemented as multi-ported RAM/ROM, and accesses to/from external memory and on-chip channels since they can be stalled. These

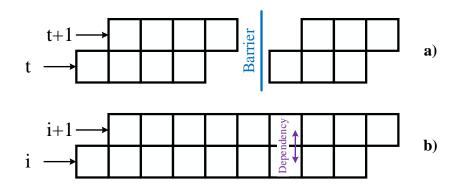

sources can be split into two groups: sources that affect compile-time initiation interval  $(II_c)$ , and sources that affect run-time initiation interval  $(II_r)$ . For Single Work-item kernels, the effect of loop-carried dependencies and shared on-chip resources is determined at compile-time and  $II_c$  is adjusted accordingly. In NDRange kernels, loops are *not* pipelined and hence, no such analysis is done and we can assume  $II_c = 1$ . However, in both kernel types, accesses to external memory and channels will still influence  $II_r$ . By default, the compiler inserts enough stages in the pipeline to hide the *minimum* latency of these operations, and accesses that take longer at run-time result in a pipeline *stall*. To estimate compile-time initiation interval  $(II_c)$ , we consider each kernel type separately (Fig. 3-1):

• Single Work-item kernels:  $II_c$  in this case depends on the number of stall cycles per iteration  $(N_d)$  determined by the compiler and will be equal to  $N_d + 1$ . Hence, Eq. (3-1) transforms into:

$$T_{cycle} = P + (N_d + 1) \times (L - 1)$$

(3-3)

• NDRange kernels: In these kernels, even though we can assume  $II_c = 1$ , we need to take the overhead of barriers into account. Total run time for an NDRange kernel with  $N_b$  barriers is:

$$T_{cycle} = \sum_{i=0}^{N_b} (P_i + L_i - 1) = \left(\sum_{i=0}^{N_b} P_i\right) + (N_b + 1) \times (L - 1)$$

$$= P + (N_b + 1) \times (L - 1)$$

(3-4)

In Eq. (3-4),  $P_i$  and  $L_i$  show the pipeline length and number of inputs (work-items) for each pipeline in an NDRange kernel. Since the number of work-items is fixed per kernel,  $L_i$  for every pipeline is the same and equal to L. Furthermore, we will call the accumulated length of all the pipelines, P. After simplifying the equation, we reach a statement that is very similar to Eq. (3-3). In practice, the number of barriers in an NDRange kernel plays a similar role to that of stalls inserted in the pipeline due to dependencies in a Single Work-item kernel, and we can assume  $II_c$  is equal to  $(N_b + 1)$  instead of one.

Figure 3-1 NDRange (a) vs. Single Work-item (b) pipeline model

To take the effect of external memory accesses into account and estimate run-time initiation interval  $(II_r)$ , we use a simple model for external memory. For  $N_m$  bytes read from and written to external memory per cycle and an external memory bandwidth per clock cycle of BW, we have:

$$II_r > \frac{N_m}{BW} \tag{3-5}$$

Here, BW is determined by the specifications of the external memory on the FPGA board. Furthermore, since our model is simplified and does not take coalescing, alignment and contention from different external memory accesses into account, the right-hand size of (3-5) only shows the *minimum*  $II_r$ .

Putting everything together, we have:

$$II > \max(II_c, II_r) \Rightarrow II > \max\left(\begin{cases} N_d + 1, \frac{N_m}{BW} \end{cases}\right)$$

(3-6)

We ignore the role of stalls caused by on-chip channels here since if the channels are deep enough and the rate of channel reads and writes is similar, channel stalls will be very rare.

#### 3.1.2 Extension for Data Parallelism

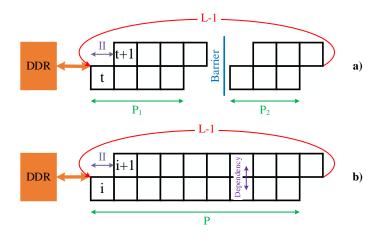

To extend our model for cases where data parallelism in form of loop unrolling, SIMD or compute unit replication is employed with a degree of parallelism of  $N_p$  (Fig. 3-2), run time can be calculated as:

$$T_{cycle} = P' + II \times \frac{\left(L - N_p\right)}{N_n} \tag{3-7}$$

In this case, the pipeline depth generally increases compared to the case where data parallelism is not present. However, for an  $L \gg P'$ , Eq. (3-7) points to a performance improvement of nearly  $N_p$  times since the loop trip count is effectively reduced by a factor of  $N_p$ . On the other hand, data parallelism also increases memory pressure by a factor of  $N_p$  and hence, II will be affected as follow:

$$II > \max\left(\begin{cases} N_d + 1, N_m \times N_p \\ N_h + 1, BW \end{cases}\right)$$

(3-8)

Based on Eq. (3-7) and (3-8), when data parallelism is present, assuming that sufficient external memory bandwidth is available, performance will improve by a factor close to  $N_p$ .

Figure 3-2 Pipeline model for data parallelism

#### 3.1.3 General Optimization Guidelines

Based on our model, we conclude that to improve performance for an HLS-based design on FPGAs, our optimization effort should be focused on:

- Reducing stalls ( $N_d$ ) in Single Work-item kernels

- Reducing number of barriers  $(N_b)$  in NDRange kernels

- Reducing external memory accesses  $(N_m)$

- Increasing data parallelism  $(N_p)$

#### 3.1.4 Single Work-item vs. NDRange Kernels

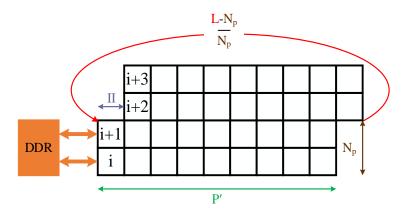

One important factor in OpenCL-based designs for Intel FPGAs is to decide whether to use Single Work-item or NDRange kernels. Fig. 3-3 shows the most important difference between these two kernel types. Even though we explained earlier that in NDRange kernels, threads are pipelined and no thread-level parallelism exists by default, the programming model itself assumes that threads are running in parallel and hence, the issue distance between the threads neither appears nor can be influenced in the kernel code. Due to this reason, local memorybased optimizations in NDRange kernels require barriers since there is no direct way of transferring data between threads in an NDRange kernel. In contrast, in Single Work-item kernels there is a minimum distance of one clock cycle between loop iterations. It is possible to take advantage of this issue distance to directly transfer data from one loop iteration to another, especially to resolve loop-carried dependencies. This type of communication can be realized using single-cycle reads and writes from and to the plethora of registers that are available in every FPGA. Based on this analysis, we conclude that in Single Work-item kernels, it might be possible to fully resolve iteration dependencies and reduce  $N_d$  to zero; however, in NDRange kernels where local memory-based optimizations are employed, barriers will always be required and  $N_b$  will never become zero. Hence, based on Eq. (3-6), a Single Work-item kernel can potentially have a lower effective II<sub>c</sub> compared to its NDRange equivalent. This shows the clear advantage of the Single Work-item programming model compared to NDRange for FPGAs. Moreover, shift registers, which are an efficient storage type on FPGAs, can only be inferred in Single Work-item kernels (Section 3.2.4.1).

Figure 3-3 Data sharing in (a) NDRange and (b) Single Work-item kernels

On the other hand, NDRange kernels also have their own advantages in certain applications. In cases where an  $II_c=1$  can be achieved, a Single Work-item kernel is preferred. However, for cases where this cannot be achieved, NDRange kernels could potentially achieve better performance. This difference stems from the fact that  $II_c$  in Single Work-item kernels is static and is determined based on the worst case loop-carried or load/store dependency at compile-time, while in NDRange kernels, initiation interval is determined at run-time by the thread scheduler. Because of this, in cases where  $II_c=1$  cannot be achieved in the Single Work-item implementation of an application, the thread scheduler in the NDRange equivalent might be able to achieve a lower average initiation interval by reordering the threads at run-time, compared to the Single Work-item equivalent with a fixed worst-case initiation interval.

In summary, the following points should be taken into account to decide whether to choose NDRange kernels for a design, or Single Work-item kernels:

- Applications with non-fully-pipelineable loops (e.g. loops with variable exit conditions or complex loop-carried/load/store dependencies) or random external memory accesses can potentially perform better using the NDRange programming model

- Every other application will potentially perform better using the Single Work-item programming model, especially if registers or shift registers can be used to efficiently resolve loop-carried dependencies.

#### 3.2 HLS-based Optimization Techniques for FPGAs

In this section, we will discuss multiple different optimization techniques for HLS-based designs on FPGAs, ranging from basic compiler-assisted optimizations to advanced manual optimizations that require significant code refactoring. The basic optimizations discussed here are techniques that are introduced in Intel's OpenCL documents [18, 19], while most of the advanced ones are not directly discussed in these documents. We only discuss kernel optimization here. Some of the discussed optimizations are only applicable to one kernel type; "NDR" and "SWI" are used to mark optimizations specific to NDRange and Single Work-item kernels, respectively. Optimizations applicable to both have been marked as "BOTH".

#### 3.2.1 Basic Compiler-assisted Optimizations

#### 3.2.1.1 restrict keyword (BOTH):

The *restrict* keyword can be added to global pointers in the kernel to prevent the compiler from assuming false pointer aliasing. This optimization usually has little to no effect in NDRange kernels; however, it is a crucial optimization in Single Work-item kernels, which, if not used, can result in very high initiation interval or even full sequential execution. This optimization can improve performance by reducing  $N_d$ , and consequently, reducing  $II_c$ .

#### 3.2.1.2 ivdep pragma (SWI):

The *ivdep* pragma is used to prevent the compiler from assuming false load/store dependencies on global buffers. This pragma in only applicable to Single Work-item kernels and should be used with extreme care since incorrect usage can result in incorrect output. Even though this pragma can also be used for local buffers, it is very rare for the compiler to detect a false dependency on such buffers. This optimization can improve performance by reducing  $N_d$ , and consequently, reducing  $II_c$ .

#### 3.2.1.3 Removing thread scheduler (SWI):

The run-time thread scheduler is only needed for NDRange kernels and is not required for Single Work-item kernels. However, in cases where a Single Work-item kernel is launched from the host using the *clEnqueueNDRangeKernel()* function, the scheduler is required for correct kernel launch. On the other hand, for cases where the *clEnqueueTask()* function is used to launch such kernel, a compiler-provided attribute can be used to remove the scheduler to save some FPGA resources. The only downside of this optimization is that *clEnqueueTask()* has been deprecated in OpenCL 2.0. This optimization does not directly affect performance and only reduces area utilization by a small amount.

#### 3.2.1.4 Setting work-group size (NDR):

Intel FPGA SDK for OpenCL Offline Compiler provides attributes for NDRange kernels to set the exact or maximum kernel work-group size. This allows the compiler to minimize the size of local memory buffers based on the user-supplied information. Furthermore, the SIMD attribute can only be used if the exact work-group size is set by the programmer. If this information is not supplied, the compiler will assume a default work-group size of 256, potentially wasting valuable Block RAM resources if a smaller work-group size is used at runtime. Using this attribute comes at the cost of kernel execution failure if the run-time-provided work-group size supplied by the host does not align with the information supplied to the compiler in the kernel. This optimization does not have a direct effect on performance; however, the area reduction from this optimization can potentially allow performance improvement by using more data parallelism or larger block size.

#### 3.2.1.5 Data parallelism (BOTH):

For NDRange kernels, data parallelism can be achieved by using the SIMD or num\_compute\_units() attributes. SIMD will provide work-item-level parallelism, while

num\_compute\_units() provides work-group-level parallelism. Using SIMD has a lower area overhead since it does not require full compute unit replication, and only the pipeline stages are replicated so that multiple work-items can be issued and processed in parallel. Furthermore, internal and external memory accesses can be coalesced in this case, allowing higher internal and external memory bandwidth with minimum amount of contention and area overhead. However, using this attribute is subject to multiple limitations. First, the SIMD length must be a power of two up to maximum of 16 (which is an artificial compiler limitation since any arbitrary SIMD length should be implementable on an FPGA). Second, no thread-id-dependent branches should exist in the code. Finally, work-group size should be set by the programmer (Section 3.2.1.4) and be divisible by SIMD length. Using num\_compute\_units() has neither of these limitations; however, it comes at the cost of higher area overhead due to complete compute unit replication, and lower memory throughput compared to SIMD due to multiple narrow accesses competing for the external memory bandwidth instead of one wide coalesced access. For Single Work-item kernels, a SIMD-like effect can be achieved using loop unrolling, without any of the limitations that exist for using SIMD. However, area overhead of loop unrolling will be minimized when a loop with a trip count known at compile-time is either fully unrolled, or partially unrolled with a factor that the trip count is divisible by. As explained in Section 3.1.2, these techniques can improve performance by a factor close to the degree of parallelism if sufficient external memory bandwidth is available.

A direct effect of data parallelism in form of SIMD for NDRange kernels and unrolling for Single Work-item kernels is that external memory accesses which are consecutive in the dimension that SIMD or unrolling is applied on will be coalesced by the compiler into wider accesses at compile-time, allowing better utilization of the external memory bandwidth. Compared to having multiple narrow accesses per iteration to external memory, a few wide accesses result in much less contention on the memory bus and much more efficient utilization of the external memory bandwidth. However, using SIMD and unrolling over non-consecutive external memory accesses could instead lead to many narrow access ports and lower performance due to large amount of contention on the memory buss. Using either of these techniques also has a similar effect on local memory buffers. Using SIMD and unrolling over consecutive local memory accesses leads to access coalescing and data interleaving with minimal area overhead, while applying these over non-consecutive accesses will result in high replication factors for local buffers and waste of FPGA area.

#### 3.2.2 Basic Manual Optimizations

#### 3.2.2.1 Shift register for floating-point reduction (SWI):

On most FPGAs, floating-point operations cannot be performed in one clock cycle (unless at the cost of extremely low operating frequency). Because of this, for floating-point reduction operations where the same variable appears on both sides of the assignment (i.e. the reduction variable), data dependency on this variable prevents pipelining with an initiation interval of one and instead, the initiation interval equals the latency of the floating-point operation (e.g. 8 clocks for floating-point addition on Intel Stratix V). As suggested in Intel's documents [18], this dependency can be eliminated by inferring a shift register with a size equal to the latency

of the floating-point operation. In this case, in every iteration data is read form the head of the shift register and written to its tail, with the shift register being shifted afterwards. The use of an array of reduction variables instead of just one such variable effectively eliminates the dependency, reducing  $N_d$  to zero and consequently, reducing  $II_c$  to one for the reduction loop. To obtain the final output, another reduction is needed on the content of the shift register. It is worth noting that unlike what is suggested in [18], the size of the shift register does not need to be one index bigger than the latency of the reduction operation and in our experience, even if the size is exactly equal to the latency of the operation, the dependency can be eliminated without lowering operating frequency. The transformation from an unoptimized floating-point reduction to optimized version with shift register is shown in Fig. 3-4.

```

float final sum = 0.0f;

for (int i = 0; i < size; i++)

final_sum += in[i];

a)

#define FADD_LATENCY

8 // latency of floating-point operation

// shift register definition and initialization

float shift_reg[FADD_LATENCY] = {0.0f}, final_sum = 0.0f;

for (int i = 0; i < size; i++)

// add and write to shift register

shift_reg[FADD_LATENCY - 1] = shift_reg[0] + in[i];

// shifting

#pragma unroll

for (int j = 0; j < FADD_LATENCY - 1; j++)</pre>

shift_reg[j] = shift_reg[j + 1];

}

//final reduction

#pragma unroll

for (int i = 0; i < FADD_LATENCY; i++)</pre>

final_sum += shift_reg[i];

b)

```

Figure 3-4 Shift register optimization for floating-point reduction

This optimization is usually not enough to provide good performance on its own and it needs to be followed by data parallelism (Section 3.2.1.5). Even though the resulting optimized loop can be partially unrolled by using the unroll pragma to further improve the performance, doing so will break the shift register optimization and requires that the size of the shift register is increased further to accommodate for the unrolling. With large unroll factors, this method can result in large area overhead to implement the shift register. As a much better optimized alternative, it is possible to add data parallelism to the optimized code from 3-4 b) by performing manual unrolling as depicted in Fig. 3-5. In this case, the original loop is split into

two loops, with the inner loop being fully unrolled and having a trip count equal to the unroll factor, and the exit condition of the outer loop being adjusted accordingly. In this case, the shift register optimization is not required for the inner loop since full unrolling effectively eliminates the dependency on the reduction variable, and it only needs to be applied to the outer loop. This method makes it possible to achieve efficient data parallelism alongside with the shift register optimization for floating-point reduction, without needing to increase the size of the shift register.

```

#define FADD LATENCY

8 // latency of floating-point operation

#define UNROLL

16 // unroll factor

// shift register definition and initialization

float shift_reg[FADD_LATENCY] = {0.0f}, final_sum = 0.0f;

// loop exit condition calculation

int exit = (size % UNROLL == 0) ? (size / UNROLL) : (size / UNROLL) + 1;

for (int i = 0; i < exit; i++)

// unrolled addition

float sum = 0.0f;

#pragma unroll

for (int j = 0; j < UNROLL; j++)

int index = i * UNROLL + j;

sum += (index < size) ? in[index] : 0.0f;</pre>

// write to shift register

shift_reg[FADD_LATENCY - 1] = shift_reg[0] + sum;

// shifting

#pragma unroll

for (int j = 0; j < FADD_LATENCY - 1; j++)

shift_reg[j] = shift_reg[j + 1];

}

}

//final reduction

#pragma unroll

for (int i = 0; i < FADD_LATENCY; i++)</pre>

final_sum += shift_reg[i];

```

Figure 3-5 Optimized floating-point reduction with unrolling

As a final note, on the Intel Arria 10 FPGA, it is possible to use single-cycle floating-point accumulation and hence, the shift register optimization is not required on this FPGA. However, due to the requirements for correct inference of single-cycle accumulation by the compiler on Arria 10, it is required that data parallelism is implemented using the aforementioned method rather than applying partial unrolling directly to the reduction loop.

#### 3.2.2.2 Calculating constants on host instead of kernel (BOTH):

For cases where a value is calculated on the kernel and remains constant throughout the kernel execution, calculation of this constant can be moved to the host code to save FPGA area. This optimization is specifically useful in cases where calculation of a constant involves

complex mathematical functions (division, remainder, exponentiation, trigonometric functions, etc.) and could use a significant amount of FPGA area. This optimization does not directly lead to performance improvements; however, area savings from this optimization could allow more parallelism or higher  $f_{max}$ .

#### 3.2.2.3 Avoiding branches on global memory addresses and accesses (BOTH):

For cases where in a kernel, the external memory address that is accessed could change based on run-time variables, instead of choosing the correct address using branches, it is best if both accesses are performed and results are stored in temporary variables and instead, the correct output is chosen from the temporary variables. This will prevent dynamic addressing and potentially allow the compiler to coalesce accesses when SIMD or unrolling is used. A similar problem exists when a branch involves choosing a value from two different global memory addresses. Also in this case, moving the accesses out of the branch and storing their value in two temporary variables, and instead using the temporary variables in the branch could allow correct coalescing when SIMD or loop unrolling is used. Apart from the area saving due to lower number of ports going to external memory, this optimization could also improve performance by decreasing  $N_m$  and consequently, reducing  $II_r$ . However, for cases where SIMD or unrolling are not used and compile-time coalescing is not required, the best choice is to choose the correct address and only perform one access to global memory to minimize the number of access ports.

#### 3.2.3 Advanced Compiler-assisted Optimizations

#### 3.2.3.1 Manual external memory banking (BOTH):

By default, Intel FPGA SDK for OpenCL Offline Compiler interleaves all the global buffers between the two (or more) DDR memory banks available on an FPGA board so that the bandwidth of all the banks is efficiently shared between all the buffers. In cases where multiple global buffers exist with different access rates, or a few narrow accesses to global memory exist in the kernel, this automatic interleaving achieves best memory performance. However, in our experience, for cases where only two wide global memory accesses (with or without some accompanying narrow ones) exist in the kernel, each to a different global buffer, this automatic interleaving does not perform optimally and disabling it can improve performance if the buffers are each pinned to a different memory bank. To achieve this, the kernel should be compiled with a specific compiler switch to disable automatic interleaving [19], and the global buffers in the host code should be created with an additional flag that allows the user to manually determine which buffer should reside on which memory bank. In this case, performance is improved by increasing the effective BW from Eq. (3-5), and consequently, reducing  $II_r$ . Furthermore, for cases where multiple global memory types exist on the board (DDR, QDR, HBM, etc.), this technique can be used to manually allocate some of the global buffers on the non-default memory type(s).

#### 3.2.3.2 Disabling cache (BOTH):

By default, Intel FPGA SDK for OpenCL Offline Compiler generates a private cache for every global memory access in a kernel if it cannot determine the exact access pattern. This cache is implemented using FPGA Block RAMs and is *not* shared between different accesses to the same global buffer. Despite its simplicity and small size (512 Kbits), this cache can be effective for designs that have good spatial locality that is not exploited by the programmer. However, in two cases this cache not only will not improve performance, but can potentially even reduce it:

- In cases where random accesses exist in the kernel with minimal spatial locality, the cache hit-rate will be very low and hence, disabling it can improve performance by avoiding the overhead of the cache mechanism. The hit-rate of the cache can be determined by using Intel FPGA Dynamic Profiler for OpenCL.

- In cases where data locality is manually exploited by the programmer by using on-chip memory, which will be the case for all well-optimized designs, the cache will not be required anymore and using it will only waste valuable Block RAM resources. In such cases, the cache can be disabled to save area.

To selectively disable the cache for a global buffer, it can be *falsely* marked as *volatile* in the OpenCL kernel. To completely disable the cache for all global buffers in a kernel, "--optarg -nocaching" can be added to the kernel compilation parameters. In our experience, this cache is usually not created in NDRange kernels but it is nearly always created in Single Workitem.

#### 3.2.3.3 Autorun kernels (SWI):

Intel FPGA SDK for OpenCL provides a specific *autorun* attribute for Single Work-item kernels that do not have an interface to the host or the FPGA external memory but can communicate with other *autorun* or *non-autorun* kernels using on-chip channels [19]. This kernel type does not need to be invoked from the host and automatically launches as soon as the FPGA is programmed. Furthermore, the kernel is automatically restarted whenever it finishes execution. This type of kernel has two main use cases:

- For designs in which data is sent and received directly via the FPGA on-board peripherals, and no interaction from the host is required, this kernel type can be used so that the FPGA can act as a standalone processor. This type of design is specifically useful for network-based processing where data is streamed in and out through the FPGA onboard network ports.

- For streaming designs that require replication of a Single Work-item kernel, this attribute can be used alongside with the multi-dimensional version of the num\_compute\_units() attribute (different from the single-dimensional one used for NDRange kernels). In this case, a get\_compute\_id() function is supplied by the compiler that can be used to obtain the unique ID of each kernel copy at compile-time and then, each kernel copy can be customized using this ID. This attribute is specifically useful for streaming designs in form of multi-dimensional systolic array or single-dimensional ring architectures. Apart from the obvious area reduction duo to lack of interface to host and memory for this kernel type, in our experience, using this kernel type also results in efficient floor-planning and good scaling of operating frequency even with tens of kernel copies.

#### 3.2.3.4 Flat compilation (BOTH):