# T2R2 東京工業大学リサーチリポジトリ

# Tokyo Tech Research Repository

#### 論文 / 著書情報 Article / Book Information

| 題目(和文)            |                                                                                                                                                                                               |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | A Study of Bluetooth Low Energy Transceiver Using Ultra-Low-Power Fractional-N Digital PLL Based on Digital-to-Time Converter                                                                 |

| 著者(和文)            | Liu Hanli                                                                                                                                                                                     |

| Author(English)   | Hanli Liu                                                                                                                                                                                     |

| 出典(和文)            | 学位:博士(学術),<br>学位授与機関:東京工業大学,<br>報告番号:甲第11024号,<br>授与年月日:2018年12月31日,<br>学位の種別:課程博士,<br>審査員:岡田 健一,髙木 茂孝,廣川 二郎,阪口 啓,伊藤 浩之,飯塚 哲也                                                                 |

| Citation(English) | Degree:Doctor (Academic),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第11024号,<br>Conferred date:2018/12/31,<br>Degree Type:Course doctor,<br>Examiner:,,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                          |

| Type(English)     | Doctoral Thesis                                                                                                                                                                               |

# A Study of Bluetooth Low Energy Transceiver Using Ultra-Low-Power Fractional-N Digital PLL Based on Digital-to-Time Converter

by

#### Hanli Liu

A Ph. D. dissertaion submitted in partial satisfaction of the requirements for the degree of

#### **Doctor of Philosophy**

in

#### **Department of Physical Electronics**

in the

#### **Graduate School of Science and Engineering**

of

#### **Tokyo Institute of Technology**

Supervised by

Prof. Kenichi Okada

Autumn 2018

To my family,

### Acknowledgment

This thesis stands on the generous help and support that I have received over the two years of the mater study and the three years of the Ph.D. study. I would like to take this chance to acknowledge the people who have helped me throughout my entire five year's integrated doctor course in Tokyo Institute of Technology.

First of all, I would like to thank Prof. Kenichi Okada and Prof. Akira Matsuzawa for giving me a wonderful chance to become a member of Matsuzawa and Okada Laboratory and Tokyo Institute of Technology.

I would like to give sincere thanks to my advisor, Prof. Kenichi Okada, for his valuable advice both in my research and my life in Japan. Throughout these five years, he always squeezed sufficient time from his extremely tight schedule to give me his advice and encouragement. With no doubt, without his guidance and trust, this work could not be finished.

I would also like to thank Prof. Akira Matsuzawa for his kindly inviting to his house every year, which gave me many wonderful life experiences in Japan. During talking with him, he always delivery a lot of genius thoughts to me and broad my vision.

I would like to thank Assist. Prof. Masaya Miyahara for his valuable advice and technical support. And also I would like to thank Yoshino Kasuga and Makiko Tsunashima for their kindly helps with applications, documents. Their advices and explanations are always very helpful.

I would also like to show my gratitude to the Ph.D. committee members, Prof. Shige-taka Takagi, Prof. Jiro Hirokawa, Prof. Kei Sakaguchi, Prof. Hiroyuki Ito, and Prof. Tetsuya Iizuka for taking the time out of their busy schedule to examine my dissertation. Especially thanks to Prof. Pietro Andreani from Lund University who spends his precious time for attending my examine.

I would especially like to express my gratitude to my senior, Teerachot Siriburanon, Aravind Tharayil Narayanan, Deng Wei, Rui Wu for all their kind help and rich knowledge that they have shared with me. I would thank the colleagues in Toshiba Cooperated Research and Development Center during my three months' internship. Especially thanks to my manager Akihide Sai and my advisor Hidenori Okuni who gave me lots of hands-on

experiences and technical support for my assigned project.

I would give thanks to my group members: Zheng Sun, Dexian Tang and Hongye Huang for their supporting work and discussions. We cooperated as a group towards the same goal which made the researches no more boring and frustrating anymore. Without their help, this work cannot be done without a doubt.

Finally, I would like to thank my girlfriend, Yin Ge, for sharing the wonderful five years with me in Japan. Without her, I may not continue my Ph.D. study after I graduated with my master degree. And also thank my pet cat, Pai Gu, who always being able to make me smile, no matter how good or bad a day I am having. And I would like to express my deepest gratitude to my parents, who have always given me love and support. They give birth to me and give me a good education in life. They teach me the spirit of never surrender. And they also teach me how to enjoy life.

#### **Abstract**

This thesis presents an ultra-low-power wireless transceiver for Bluetooth Low-Energy standard. For achieving an ultra-low-power operation with a low sensitivity and a high blocker immunity of the presented transceiver, architecture considerations and key building blocks are discussed. A wide loop-bandwidth fractional-N DPLL plays a central role in the presented transceiver, *i.e.*, a frequency modulator for the transmitter and a local oscillator, an analog-to-digital converter, a frequency and phase synchronizer for the receiver. To obtain better jitter and spur performances of the DPLL while maintaining low power operation, techniques such as the isolated constant slope digital-to-time converter and TDC gain calibration are also discussed in this thesis.

vi Abstract

# **Contents**

| A  | Acknowledgment |          | ii                                                |    |

|----|----------------|----------|---------------------------------------------------|----|

| Al | ostrac         | et       |                                                   | v  |

| 1  | Intr           | oductio  | on                                                | 1  |

|    | 1.1            | Intern   | et-of-Things and Its Available Wireless Standards | 1  |

|    | 1.2            | Blueto   | ooth Low-Energy and its Applications              | 3  |

|    |                | 1.2.1    | Beacon Mode of Bluetooth Low-Energy               | 4  |

|    |                | 1.2.2    | Mesh Network of Bluetooth Low-Energy              | 5  |

|    | 1.3            | Challe   | enges for BLE Transceiver Design                  | 5  |

|    |                | 1.3.1    | Transmitter Design and its Challenges             | 6  |

|    |                | 1.3.2    | Receiver Design and its Challenges                | 7  |

|    | 1.4            | Overv    | iew of the Thesis                                 | 12 |

| 2  | Fra            | ctional- | N Digital PLLs for Wireless Communication         | 15 |

|    | 2.1            | Analo    | g-Type Fractional-N PLLs                          | 15 |

|    | 2.2            | Types    | of Fractional-N DPLLs                             | 16 |

|    | 2.3            | Buildi   | ng Blocks of Fractional-N DPLL                    | 19 |

|    |                | 2.3.1    | Time-to-Digital Converter(TDC)                    | 19 |

|    |                | 2.3.2    | Digital-to-Time Converter(DTC)                    | 23 |

|    |                | 2.3.3    | LC-Oscillator and Oscillator Phase Noise          | 28 |

| 3  | Sub            | -mW D    | rigital PLL Using Digital-to-Time Converter       | 33 |

|    | 3.1            | Propo    | sed DPLL System Architecture                      | 36 |

|    | 3.2            | Propo    | sed Isolated Constant-Slope DTC                   | 41 |

|    |                | 3.2.1    | Concept of Operations                             | 41 |

|    |                | 3.2.2    | Nonlinear Sources and Circuit Implementations     | 44 |

|    |                | 3.2.3    | Simulation Results                                | 46 |

|    | 3 3            | Circui   | t Implementation                                  | 40 |

viii CONTENTS

|   |             | 3.3.1    | Path-select TDC and TDC Gain Calibration              | . 49  |

|---|-------------|----------|-------------------------------------------------------|-------|

|   |             | 3.3.2    | Reference Doubler and Duty Cycle Calibration          | . 54  |

|   |             | 3.3.3    | Digital Controlled Oscillator                         | . 54  |

|   |             | 3.3.4    | Coarse PLL Loop                                       | . 55  |

|   | 3.4         | Measu    | rement Results                                        | . 58  |

|   | 3.5         | Fractio  | onal-N DPLL Towards $200\mu W$                        | . 64  |

|   | 3.6         | Conclu   | usion                                                 | . 66  |

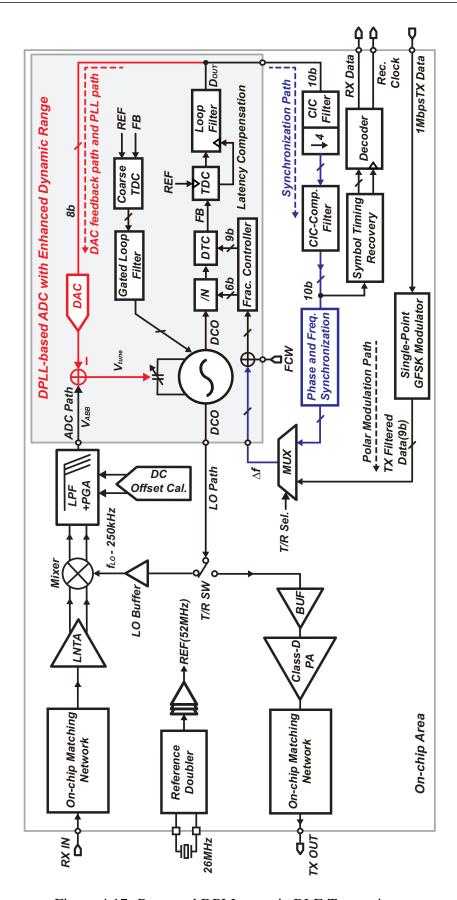

| 4 | Blue        | tooth L  | Low Energy Transceiver Using Digital PLL              | 69    |

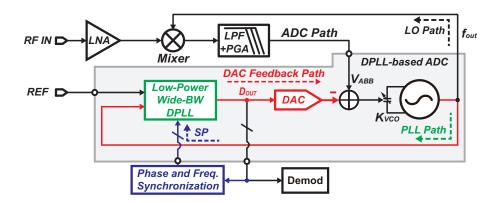

|   | 4.1         | DPLL-    | -Centric Receiver                                     | . 72  |

|   |             | 4.1.1    | DPLL-based ADC with Dynamic Range Enhancement         | . 72  |

|   |             | 4.1.2    | Wide Loop-Bandwidth Fractional-N DPLL                 | . 82  |

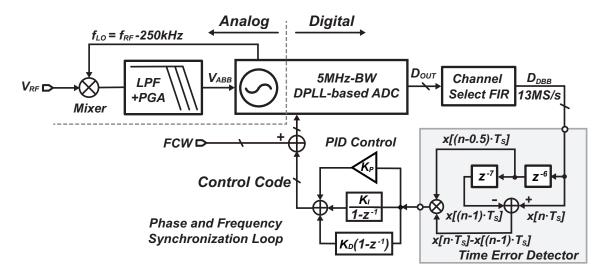

|   |             | 4.1.3    | Hybrid-loop RX with Phase and Frequency Recovery Loop | . 86  |

|   | 4.2         | Buildin  | ng Blocks of The BLE Transceiver                      | . 87  |

|   |             | 4.2.1    | Receiver Front-End Design                             | . 89  |

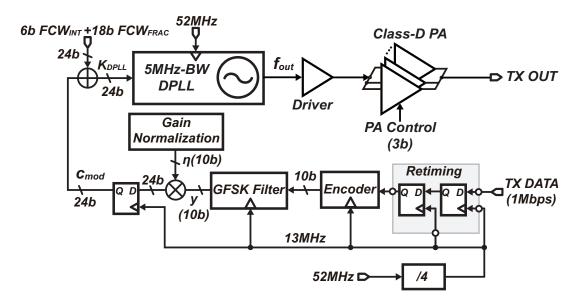

|   |             | 4.2.2    | Single-Point Polar-TX                                 | . 93  |

|   | 4.3         | Measu    | rement Results                                        | . 94  |

|   | 4.4         | BLE T    | Transceiver Towards 5.0                               | . 102 |

|   | 4.5         | Conclu   | usion                                                 | . 105 |

| 5 | Con         | clusion  | and Future Directions                                 | 107   |

|   | 5.1         | Conclu   | usion                                                 | . 107 |

|   | 5.2         | Future   | Direction                                             | . 109 |

|   |             | 5.2.1    | Fractional-N DPLL                                     | . 109 |

|   |             | 5.2.2    | Bluetooth Low-Energy Transceiver                      | . 110 |

| A | Pub         | lication | List                                                  | 121   |

|   | <b>A.</b> 1 | Journa   | d Papers                                              | . 121 |

|   | A.2         | Interna  | ational Conferences and Workshops                     | . 121 |

|   | A.3         | Domes    | stic Conferences and Workshops                        | . 122 |

|   | A.4         | Co-Au    | ıthor                                                 | . 123 |

|   |             | A.4.1    | Conferences                                           | . 123 |

|   |             | A.4.2    | Journal Papers                                        | . 124 |

|   |             | A.4.3    | Domestic Conferences and Workshops                    | . 124 |

|   |             | A.4.4    | Books                                                 | . 126 |

# **List of Figures**

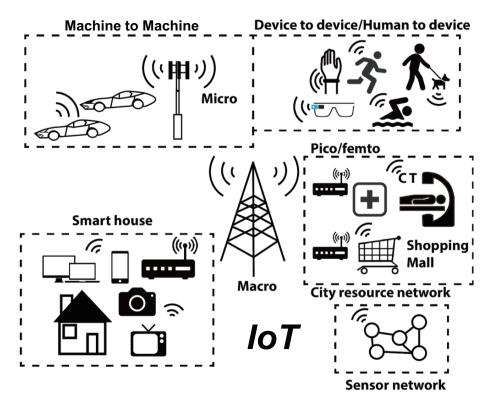

| 1.1  | The concept of the Internet of Things                                      | 2  |

|------|----------------------------------------------------------------------------|----|

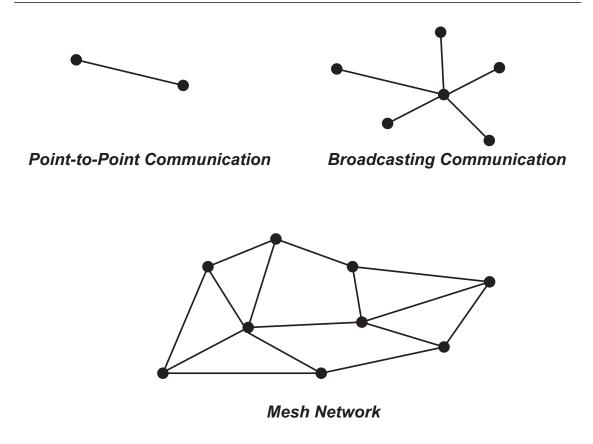

| 1.2  | Variety types of communications that BLE supports                          | 6  |

| 1.3  | Power consumption of the breakdown of a Texas Instruments CC26XX           |    |

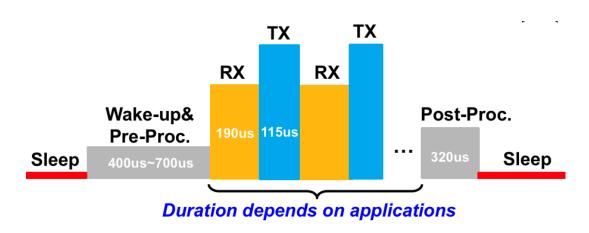

|      | BLE device during a connection event                                       | 6  |

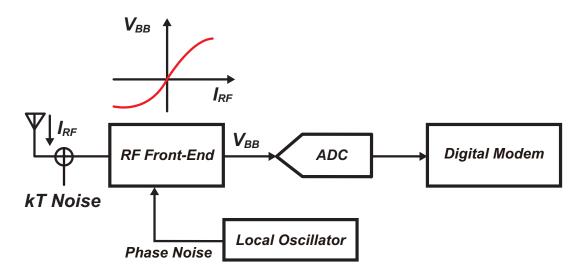

| 1.4  | The basic receiver architecture                                            | 8  |

| 1.5  | Wanted and unwanted signals down-converted by a mixer and LO               | 10 |

| 1.6  | (a) Conventional data digitization process by the full-range TDC (b) Phase |    |

|      | domain diagram.                                                            | 11 |

| 1.7  | Battery life of the state-of-the-art BLE RX and our target                 | 12 |

| 2.1  | Topology of CPPLL                                                          | 16 |

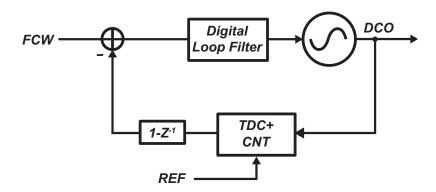

| 2.2  | Phase-domain fractional- <i>N</i> DPLL                                     | 16 |

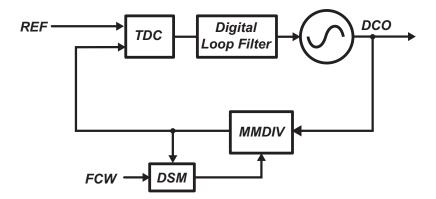

| 2.3  | Divider-based fractional-N ADPL                                            | 17 |

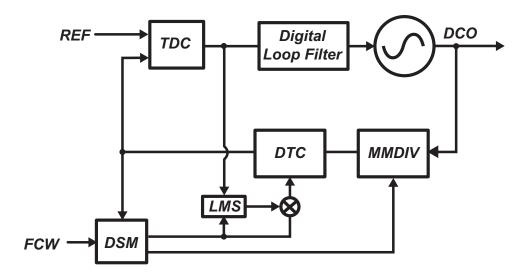

| 2.4  | DTC-based fractional-N DPLL implementation                                 | 18 |

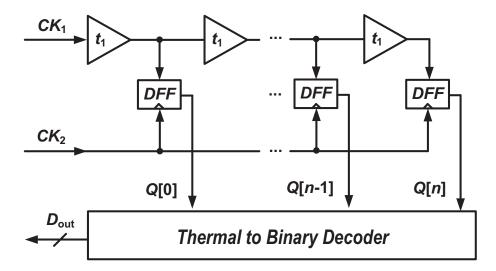

| 2.5  | Delay line based flash TDC                                                 | 20 |

| 2.6  | Vernier-chain TDC                                                          | 21 |

| 2.7  | Linear passive interpolated TDC                                            | 21 |

| 2.8  | Charge domain TDC using SAR ADC                                            | 22 |

| 2.9  | Single-slope TDC                                                           | 23 |

| 2.10 | GRO TDC                                                                    | 24 |

| 2.11 | Concept of DTC                                                             | 24 |

| 2.12 | Concept of DTC                                                             | 25 |

| 2.13 | Constant slope DTC vs variable slope DTC                                   | 26 |

| 2.14 | Constant slope DTC                                                         | 27 |

| 2.15 | Continues time comparator with a variable $V_{\text{TH}}$ control          | 27 |

| 2.16 | Three types of LC-VCO topology: (a) NMOS type LC-VCO; (b) CMOS             |    |

|      | type LC-VCO; (c) PMOS type LC-VCO                                          | 28 |

| 2.17 | LC-VCO model                                                               | 29 |

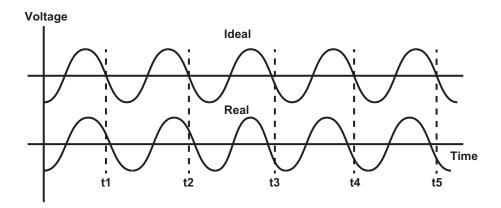

| 2.18 | Output waveforms of an idea and a real oscillator                          | 30 |

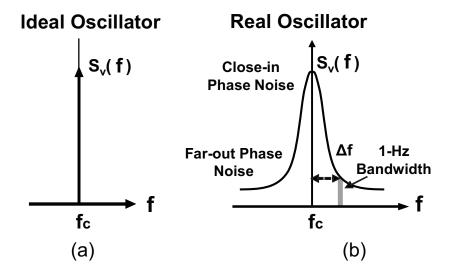

| 2.19  | Output spectrum of (a)ideal and (b) real oscillator                                                                       | 31  |

|-------|---------------------------------------------------------------------------------------------------------------------------|-----|

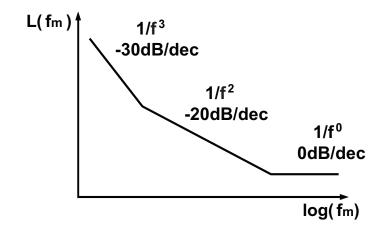

| 2.20  | Phase noise spectrum of the LC oscillators                                                                                | 31  |

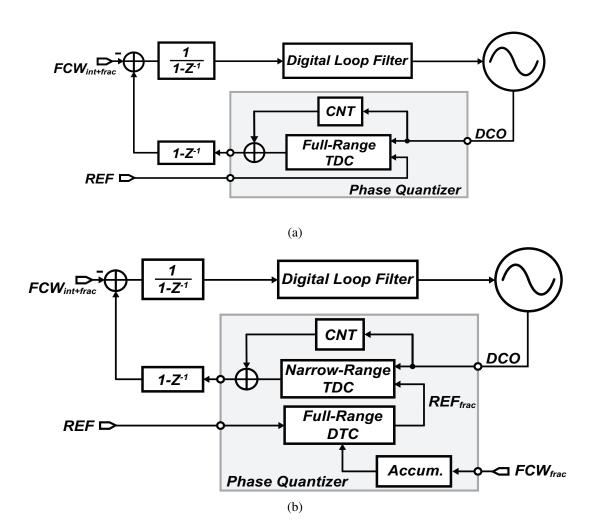

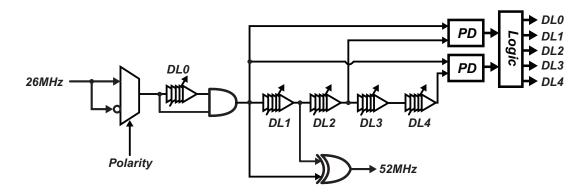

| 3.1   | (a) DPLL with the full-range TDC to perform fractional-N operation (b)                                                    |     |

|       | DPLL with the full-range DTC to perform fractional-N operation which                                                      |     |

|       | reduces total power consumption                                                                                           | 34  |

| 3.2   | Detailed block diagram of the proposed ULP DPLL with the proposed                                                         |     |

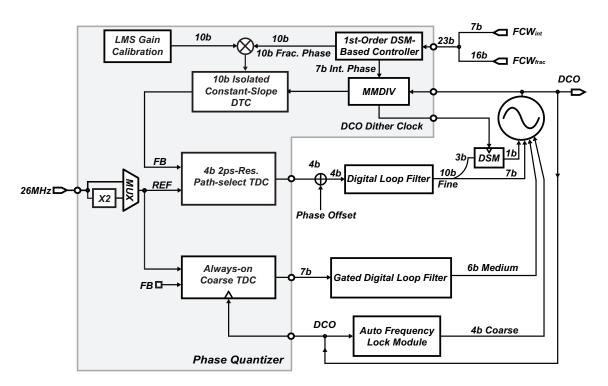

|       | 10b isolate constant-slope DTC                                                                                            | 36  |

| 3.3   | (a) DSM-based fractional controller. (b) Phase models of MMDIV and                                                        |     |

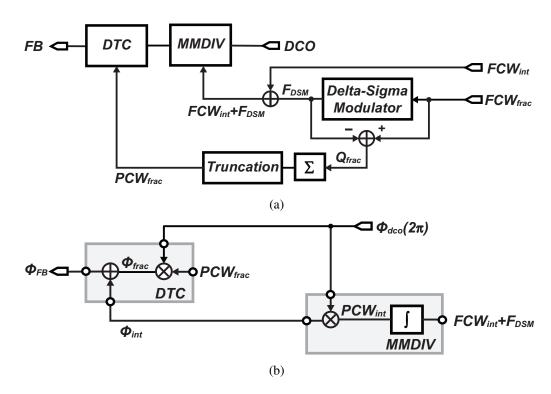

|       | DTC                                                                                                                       | 37  |

| 3.4   | System level analysis of 1st-order and 2nd-order DSM-based fractional                                                     |     |

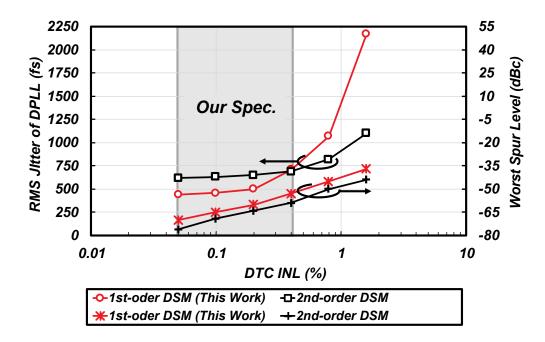

|       | controller for low-power DPLL                                                                                             | 38  |

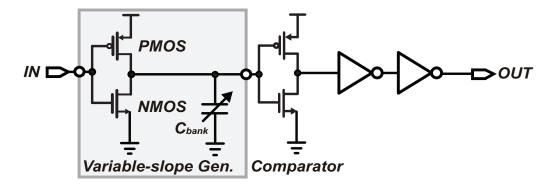

| 3.5   | Variable-slope DTC                                                                                                        | 39  |

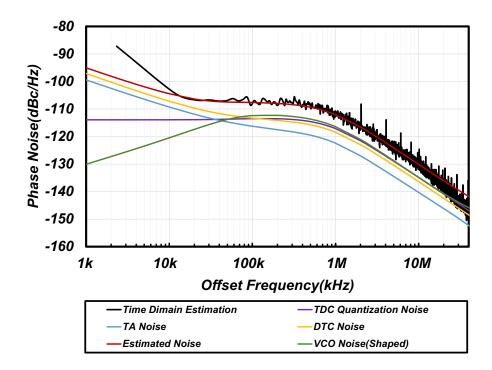

| 3.6   | Phase noise estimation of the DPLL in the phase domain (without frac-                                                     |     |

|       | tional spurs) and the time-domain phase noise simulation at 2442MHz                                                       |     |

|       | using 52MHz reference (with fractional spurs)                                                                             | 40  |

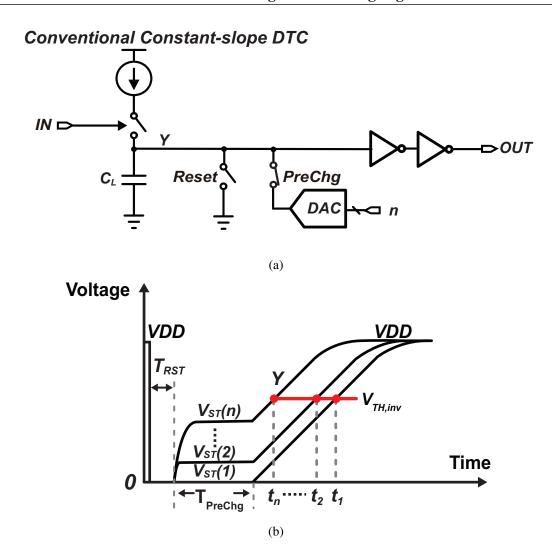

| 3.7   | (a) Conventional constant-slope DTC (b) operations of the conventional                                                    |     |

|       | constant-slope DTC                                                                                                        | 42  |

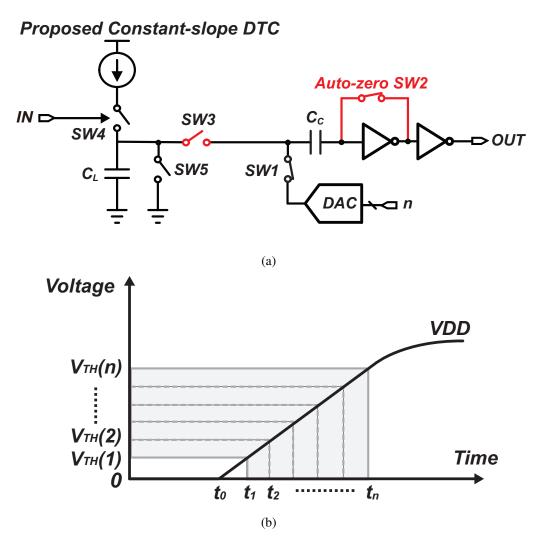

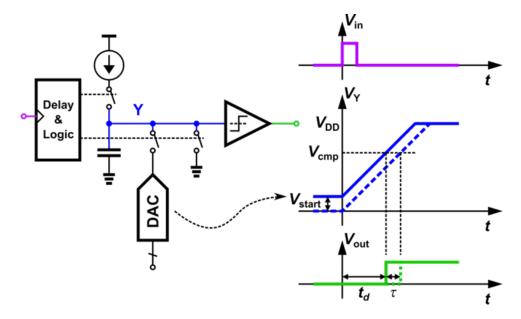

| 3.8   | (a) Proposed isolated constant-slope DTC (b) concept operation of the                                                     |     |

|       | proposed DTC                                                                                                              | 43  |

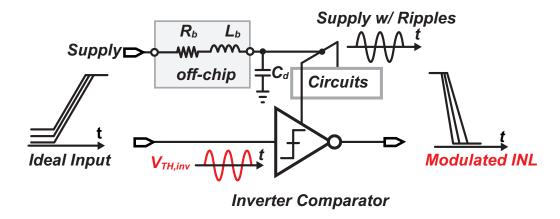

| 3.9   | $V_{\text{TH}}$ offset caused INL which induced by noisy supply                                                           | 44  |

| 3.10  | Conceptual operation diagrams of proposed 10b isolated constant-slope                                                     |     |

|       | DTC (a) $C_L$ is isolated from DAC during DAC operation (Pre-charge step)                                                 |     |

|       | (b) Charge in $C_C$ is shorted to ground which set new $V_{ST}$ at node B (Set                                            |     |

|       | step) (c) Constant slope with new $V_{ST}$ is compared in inverter(Compare                                                | 4.5 |

| 2 1 1 | step)                                                                                                                     | 45  |

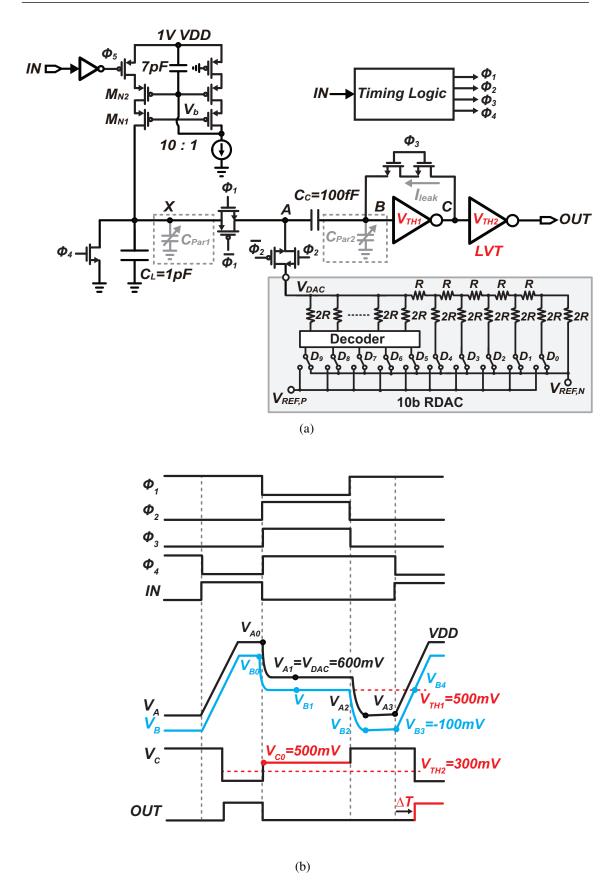

|       | Detailed circuit of (a) isolated constant-slope DTC and (b) its timing chart.                                             | 47  |

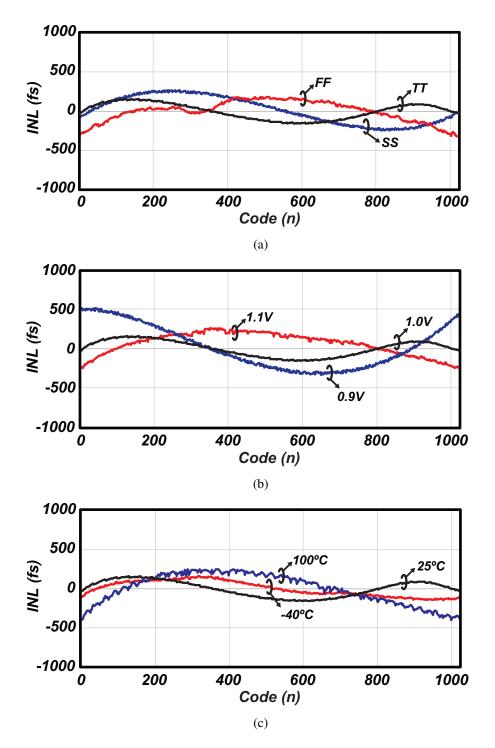

| 3.12  | Post-layout INL simulations of the proposed DTC with (a) Corner condi-                                                    | 40  |

| 2 12  | tions (b) Supply voltage variations (c) Temperature variations                                                            | 49  |

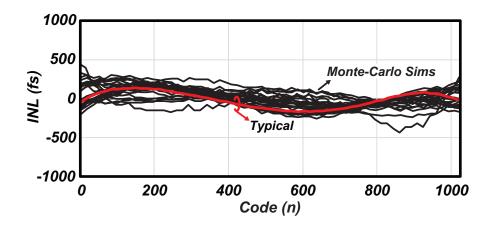

|       | The Monte-Carlo simulations of the proposed DTC INL                                                                       | 50  |

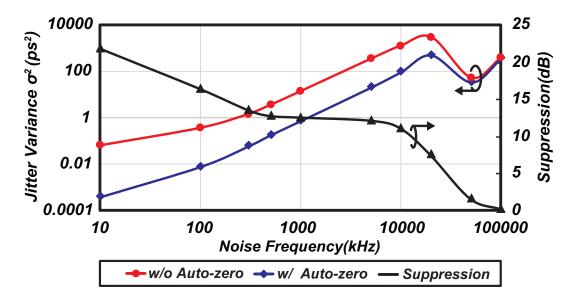

| 3.14  | Simulated deterministic jitter power w/ and w/o auto-zero switch when                                                     |     |

|       | noisy supply with different frequencies are presented, and the deterministic jitter power suppression w/ auto zero switch | 50  |

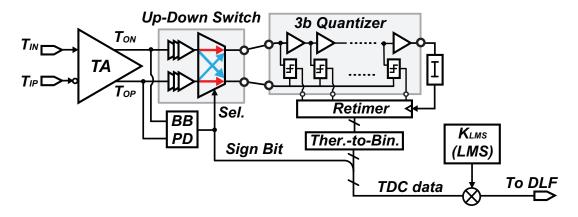

| 3 15  | Path-select TDC                                                                                                           | 51  |

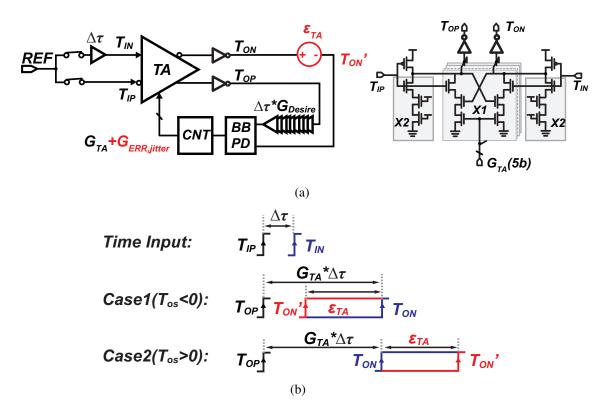

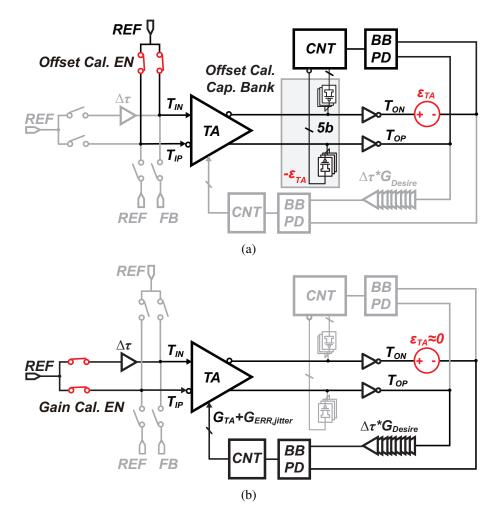

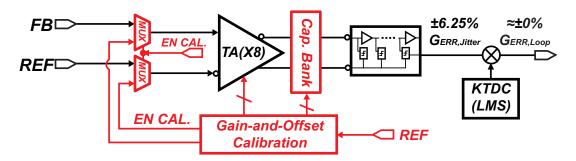

|       | (a) Conventional TA calibration (b) TA time-offset induced gain error                                                     | 52  |

|       | Proposed TA gain-and-offset calibration technique (a) TA time-offset cal-                                                 | 52  |

| 3.17  | ibration (b) TA gain calibration                                                                                          | 53  |

|       | ioration (b) IA gain canoration                                                                                           | 55  |

LIST OF FIGURES xi

| 3.18 | Proposed TDC gain calibration for minimizing PLL output jitter variation |     |

|------|--------------------------------------------------------------------------|-----|

|      | and PLL loop-bandwidth variation                                         | 53  |

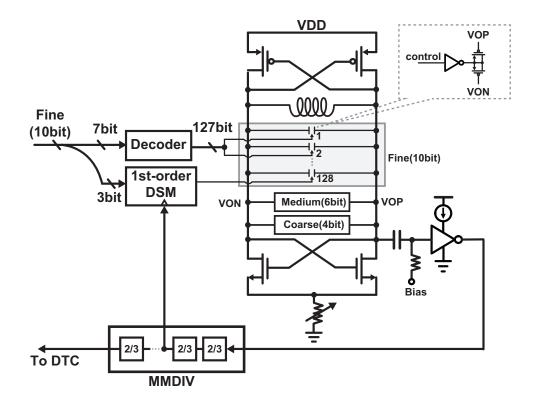

| 3.19 | Schematic of the DCO, buffer and MMDIV                                   | 54  |

| 3.20 | Schematic of the DCO, buffer and MMDIV                                   | 55  |

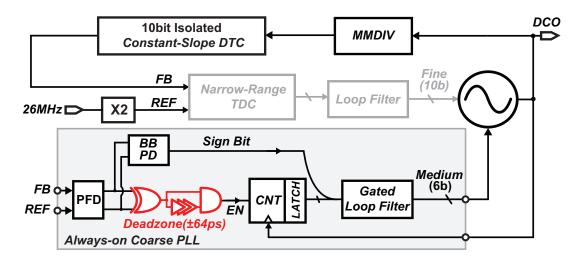

| 3.21 | Always-on coarse PLL with a dead zone of ±64ps which consumes almost     |     |

|      | zero power after phase locked                                            | 56  |

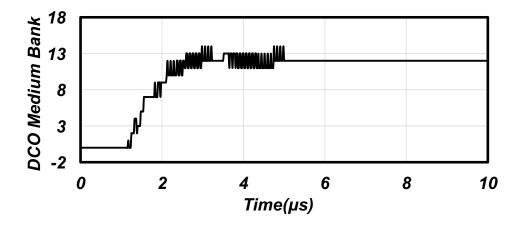

| 3.22 | Simulated lock transient of the proposed coarse-DPLL                     | 56  |

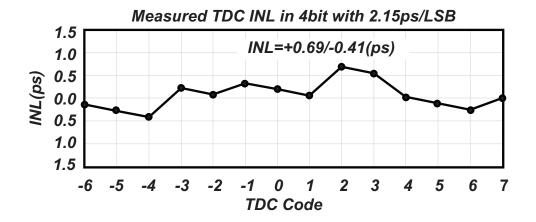

| 3.23 | Measurement result of the 4bit TDC at 52MS/s                             | 57  |

| 3.24 | Measurement result of the proposed DTC at 52MS/s                         | 57  |

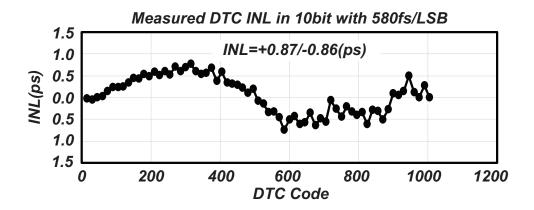

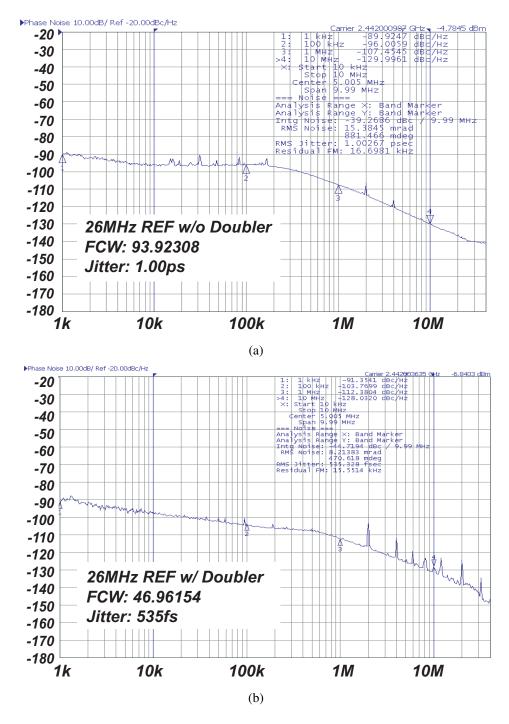

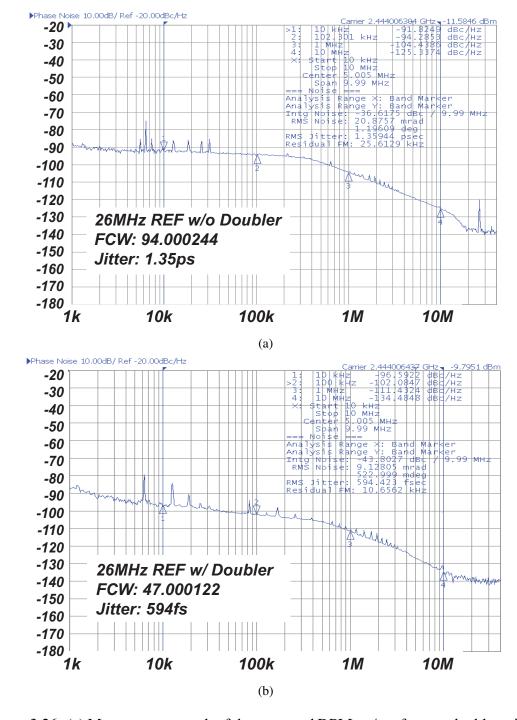

| 3.25 | (a) Measurement result of the proposed DPLL w/o reference doubler (b)    |     |

|      | Measurement result of the proposed DPLL w/ reference doubler             | 58  |

| 3.26 | (a) Measurement result of the proposed DPLL w/o reference doubler with   |     |

|      | in-band fractional spur (b) Measurement result of the proposed DPLL w/   |     |

|      | reference doubler with in-band fractional spur                           | 59  |

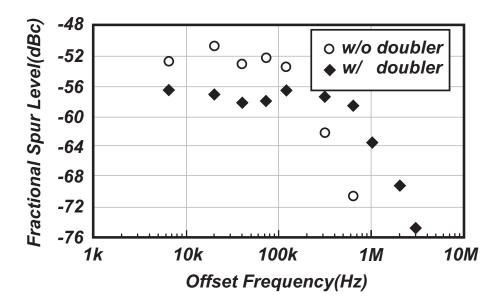

| 3.27 | Measurement result of the fractional spurs vs spur frequencies           | 60  |

| 3.28 | (a) Measurement of the TA gain calibration under voltage variations (b)  |     |

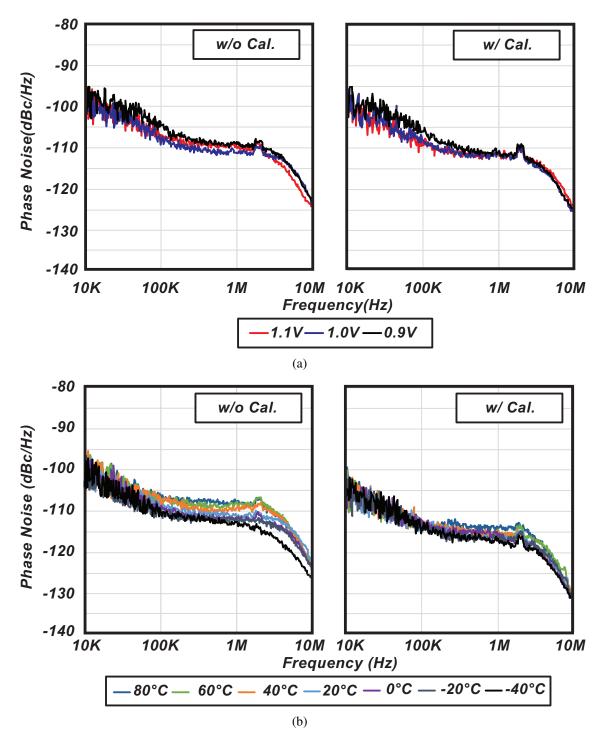

|      | Measurement of the TA gain calibration under temperature variations      | 61  |

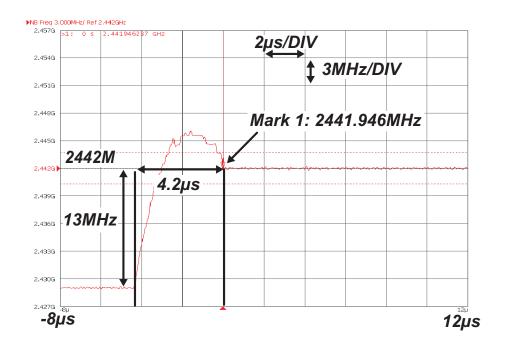

| 3.29 | Measured lock transient from an initial frequency error of 13MHz         | 62  |

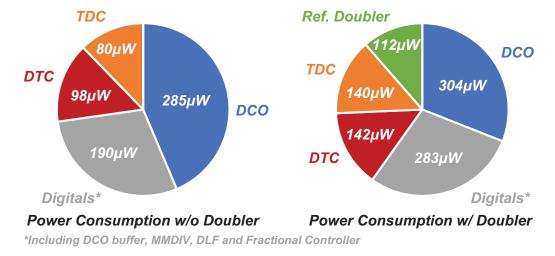

| 3.30 | Measured power break down of the proposed fractiona-N DPLL               | 62  |

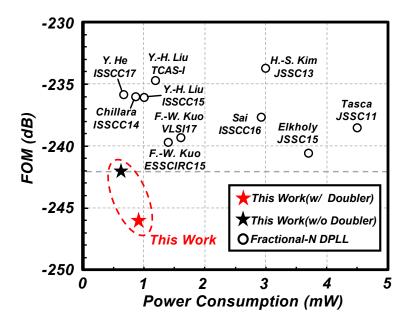

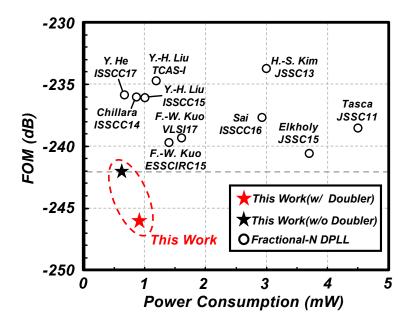

| 3.31 | FOM comparison with the state-of-the-art fractional DPLLs under 5mW      | 64  |

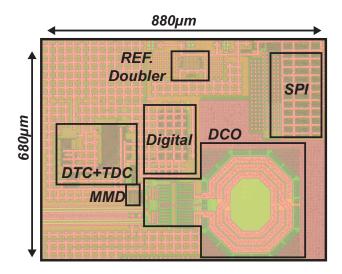

| 3.32 | Chip micrograph                                                          | 65  |

| 3.33 | Conventional constant slope DTC                                          | 66  |

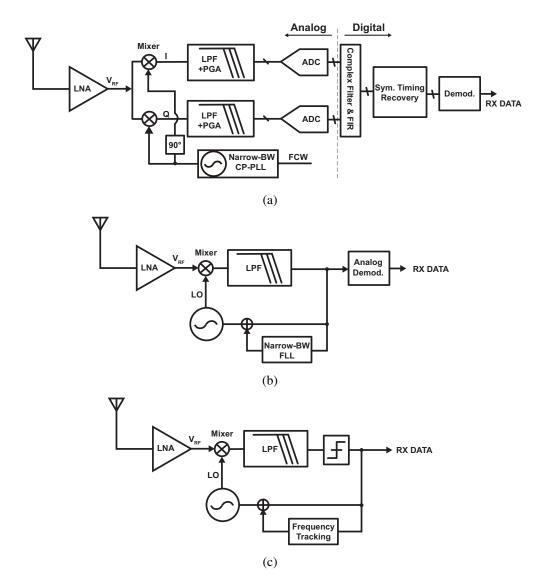

| 4.1  | (a) Low-IF receiver architecture (b) Conventional analog phase tracking  |     |

| 1.1  | RX (c) Conventional digital phase tracking RX                            | 70  |

| 4.2  | (a) Conventional hybrid-loop RX with the DPLL-based ADC (b) Pro-         | , 0 |

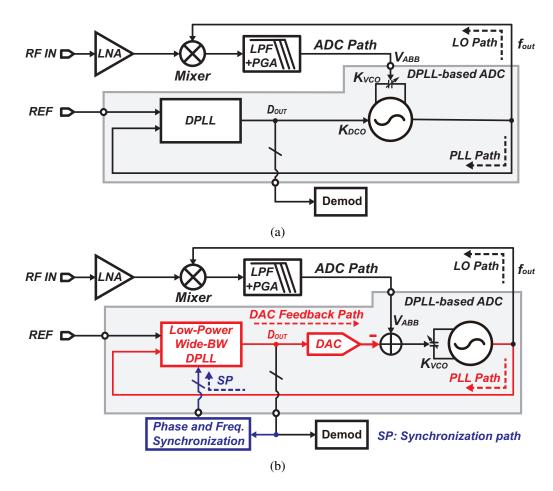

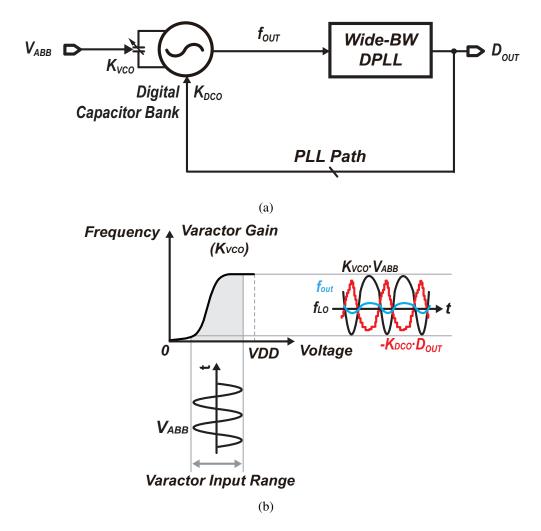

|      | posed hybrid-loop RX with the dynamic-range enhanced DPLL-based ADC.     | 71  |

| 4.3  | (a) Concept of conventional open-loop DPLL-based ADC (b) Conversion      |     |

|      | diagrams.                                                                | 74  |

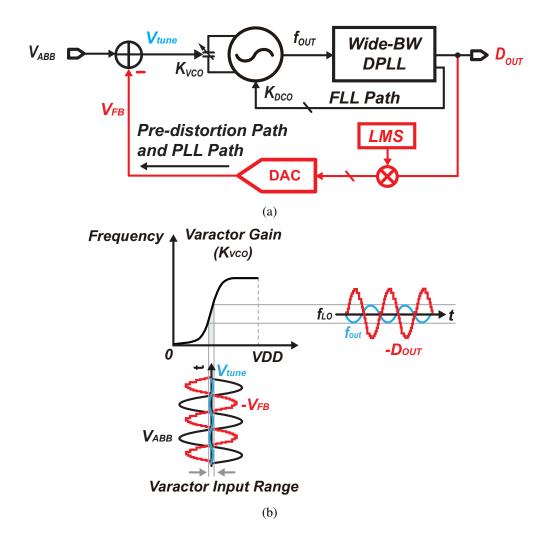

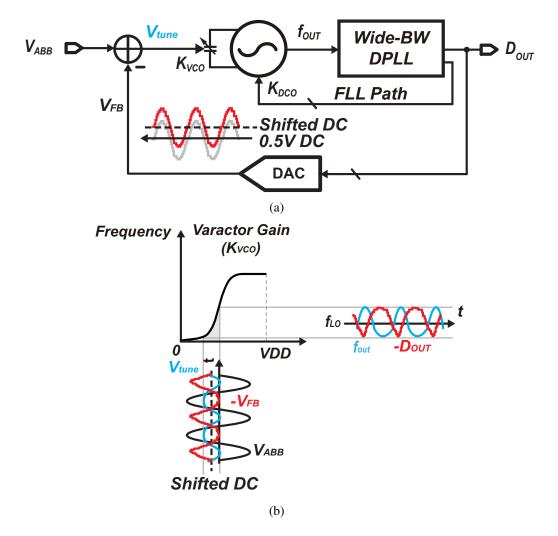

| 4.4  | (a) Proposed closed-loop DPLL-based ADC with improved varactor lin-      |     |

|      | earity (b) Conversion diagrams                                           | 75  |

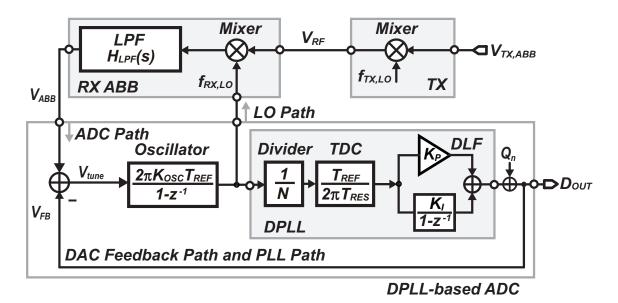

| 4.5  | The discrete-time model of the proposed DPLL-based ADC                   | 76  |

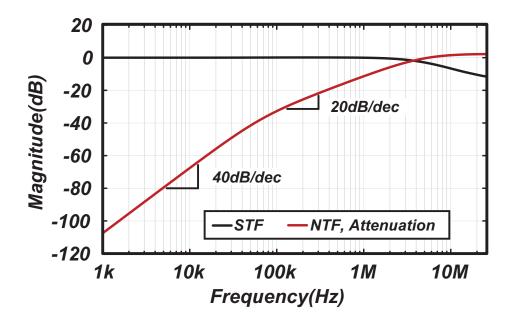

| 4.6  | Plots of the STF, NTF and the attenuation factor with a DPLL bandwidth   |     |

|      | of 5MHz                                                                  | 77  |

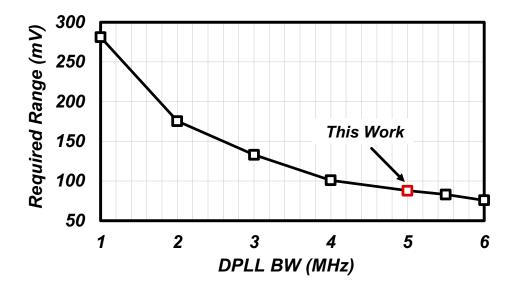

| 4.7  | Simulated required varactor linear range vs DPLL bandwidth               | 77  |

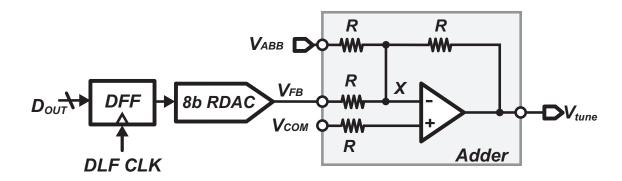

| 4.8  | Schematic of the DAC feedback path                                       | 79  |

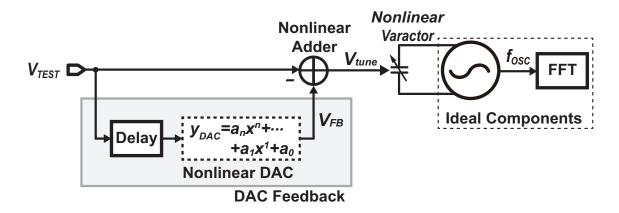

| 4.9  | Test bench of the V2F conversion gain                                    | 79  |

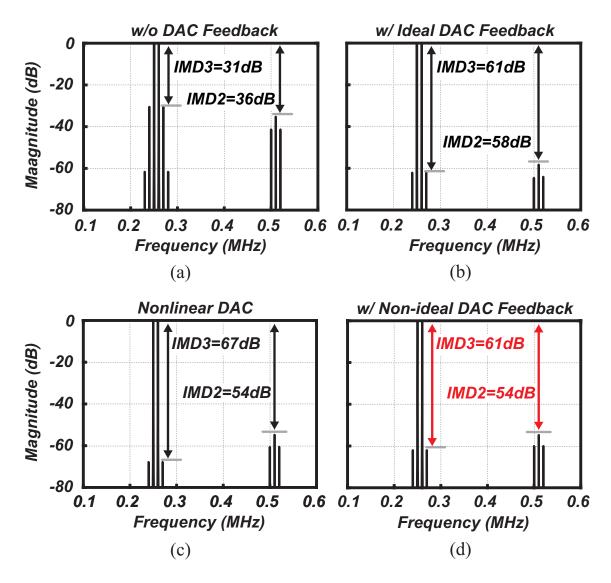

| 4.10 | Simulated linearity of (a) V2F conversion w/o DAC feedback (b) V2F                              |     |

|------|-------------------------------------------------------------------------------------------------|-----|

|      | conversion w/ ideal DAC feedback (c) nonideal DAC (d) V2F conversion w/ non-ideal DAC feedback. | 80  |

| 4.11 |                                                                                                 | 80  |

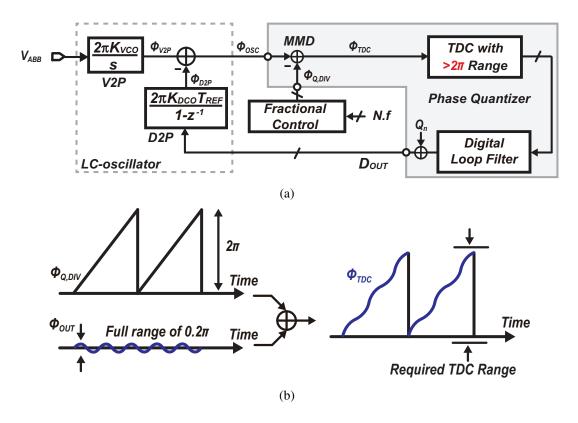

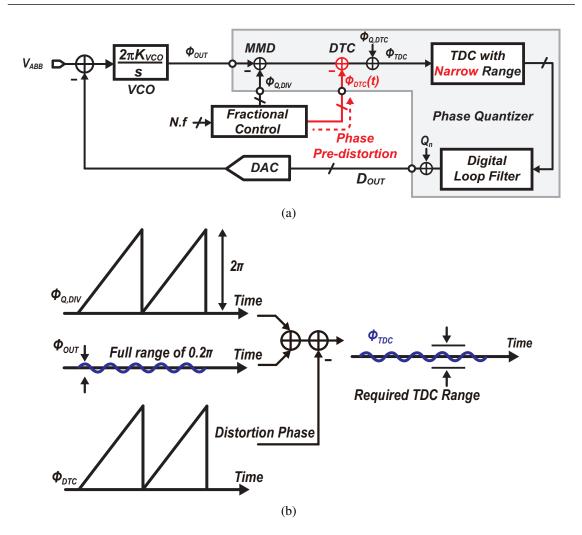

| 4.11 | domain diagram                                                                                  | 82  |

| 4.12 | _                                                                                               | 02  |

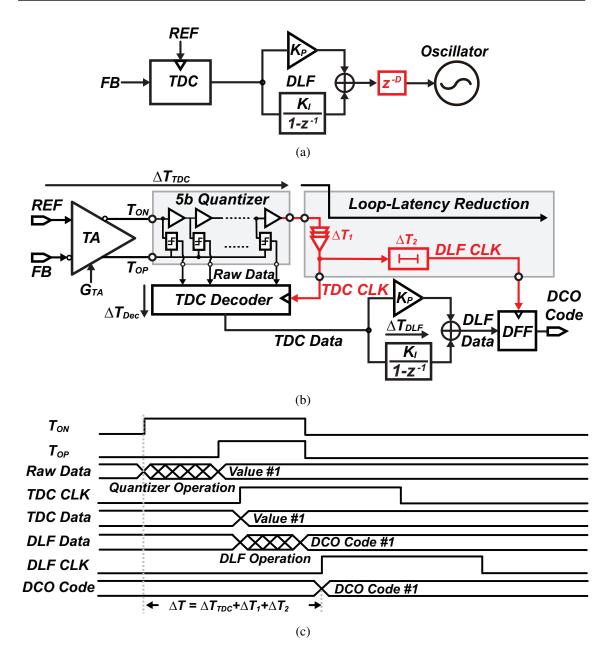

| 1,12 | diagram                                                                                         | 83  |

| 4.13 | _                                                                                               | 0.0 |

|      | posed loop-latency reduction (c) Timing chart of the loop-latency reduction.                    | 84  |

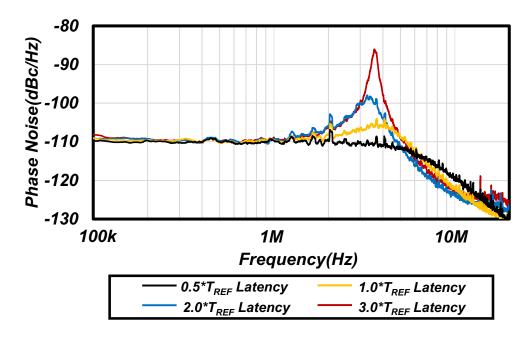

| 4.14 | Phase noise simulations of 5MHz-BW DPLL with different loop latencies.                          | 85  |

|      | Proposed BLE RX baseband with DPLL-based ADC and phase/frequency                                |     |

|      | synchronization loop                                                                            | 85  |

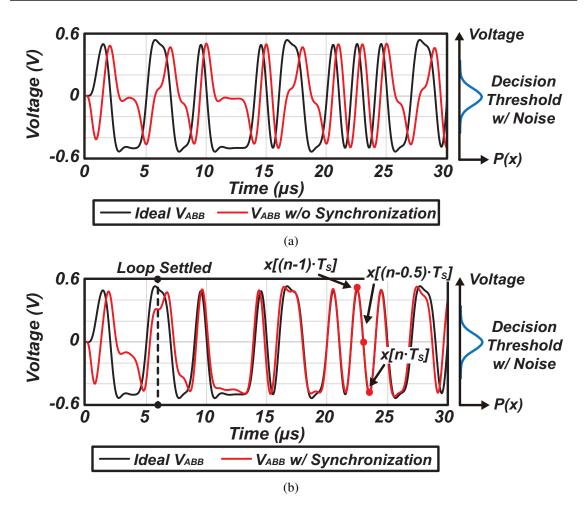

| 4.16 | Simulated result w/o frequency and phase synchronization loop. (b) Sim-                         |     |

|      | ulated results w/ frequency and phase synchronization loop                                      | 86  |

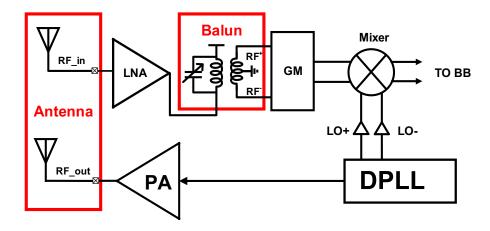

| 4.17 | Proposed DPLL-centric BLE Transceiver                                                           | 88  |

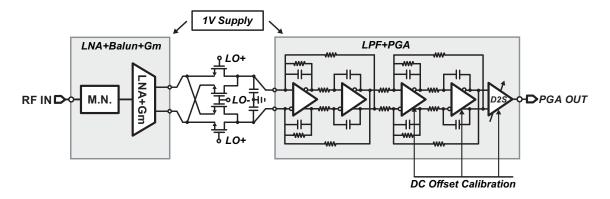

| 4.18 | RX front-end implementation with entire 1V-supply                                               | 89  |

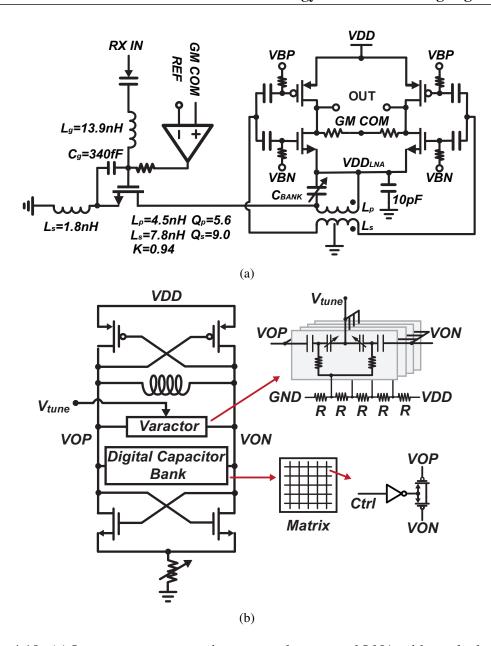

| 4.19 | (a) Low power consumption source degenerated LNA with stacked gm-                               |     |

|      | cell (b) LC-Oscillator                                                                          | 90  |

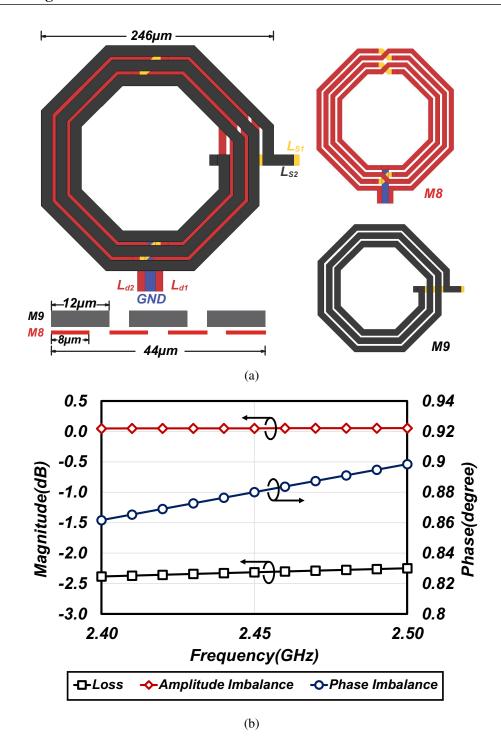

| 4.20 | (a) Small area and highly balanced stacked balun (b) EM simulation of                           |     |

|      | stacked balun                                                                                   | 91  |

| 4.21 | Block diagrams of single-point polar TX                                                         | 93  |

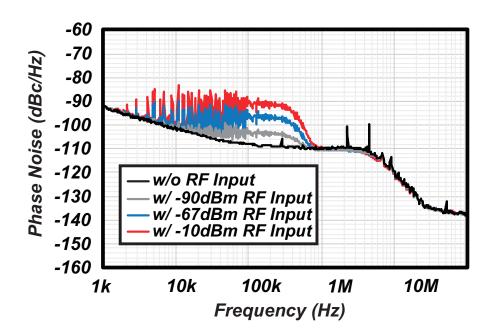

| 4.22 | Measured DPLL phase-noise at 2441.75MHz with TX/RX off                                          | 95  |

| 4.23 | Measured stability of the RX when the large in-band blockers and the                            |     |

|      | desired signal are fed to the RX                                                                | 96  |

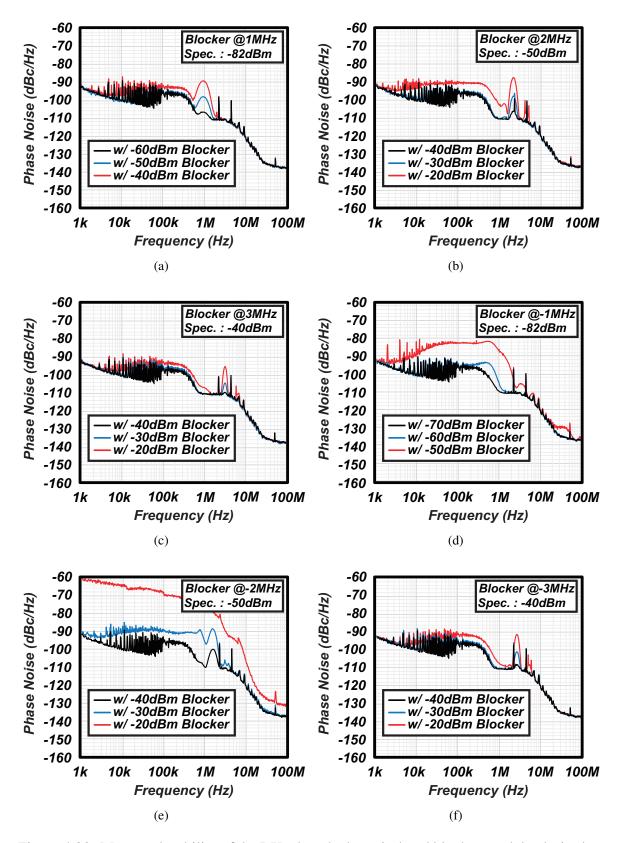

| 4.24 | Measurement result of the ADC SNDR                                                              | 97  |

| 4.25 | (a) Measurement result of the PGA output w/o phase and frequency syn-                           |     |

|      | chronization Loop (b) Measurement result of the PGA output w/ phase                             |     |

|      | and frequency synchronization Loop                                                              | 97  |

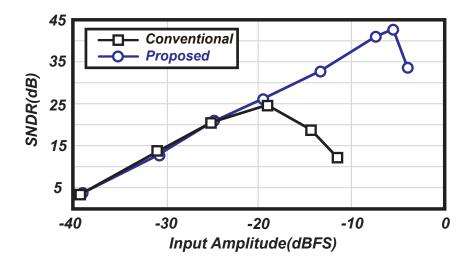

|      | Measured demodulator with CDR function                                                          | 98  |

| 4.27 | Measured BER with phase and frequency synchronization loop when the                             |     |

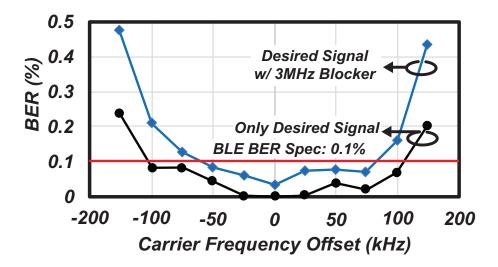

|      | carrier frequency offset is presented in the TX signal                                          | 99  |

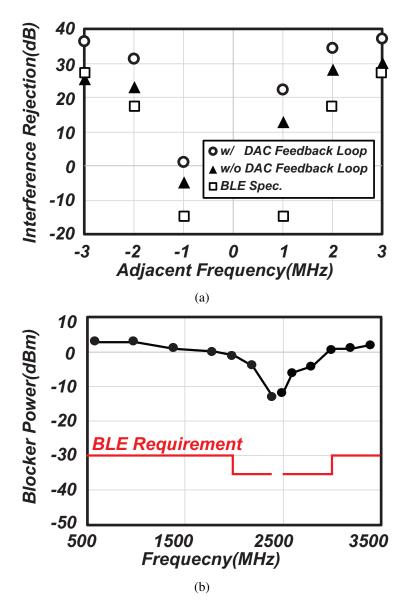

| 4.28 | (a) Measurement result of the RX ACR with and without DAC feedback                              |     |

|      | loop (b) Measurement result of the out-of-band blocker tolerance 1                              | 100 |

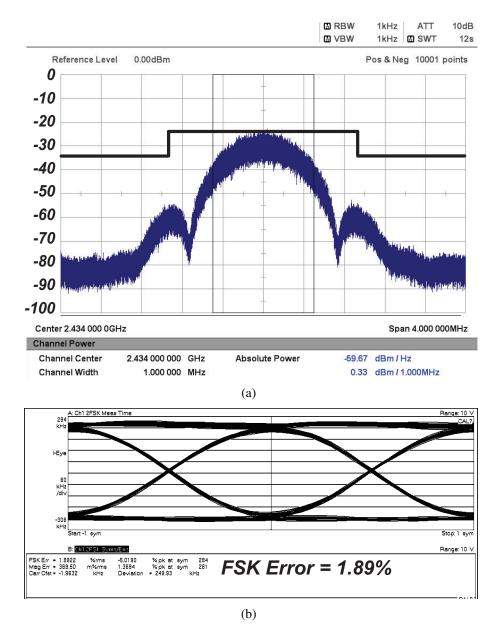

| 4.29 | (a) Measurement result of the TX spectrum mask (b) Measured eye dia-                            |     |

|      | gram of the single-point polar transmitter                                                      | 101 |

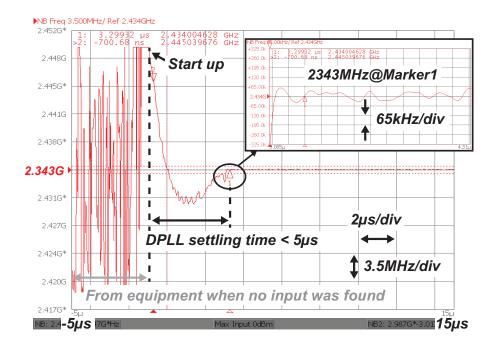

| 4.30 | Settling time of DPLL at 0-dBm PA output when DPLL and PA start up                              |     |

|      | simultaneously                                                                                  | 102 |

| LIST OF FIGURES | xiii |

|-----------------|------|

|                 |      |

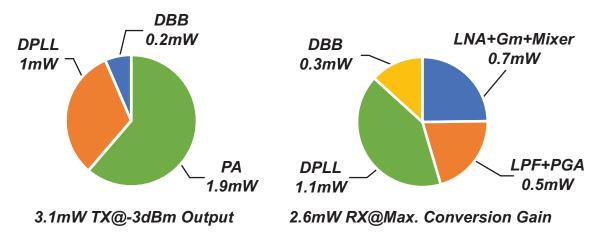

| 4.31 | Measured power consumptions of each building blocks                                 |

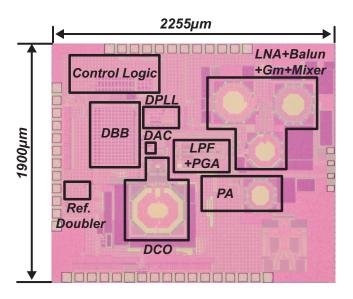

|------|-------------------------------------------------------------------------------------|

| 4.32 | Chip photo of BLE TRX                                                               |

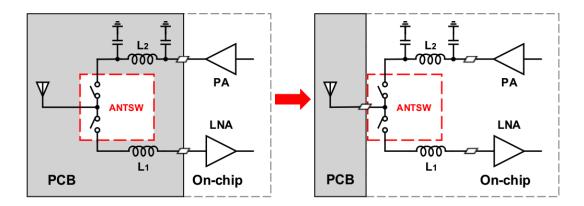

| 4.33 | The present TRX RF I/O solution                                                     |

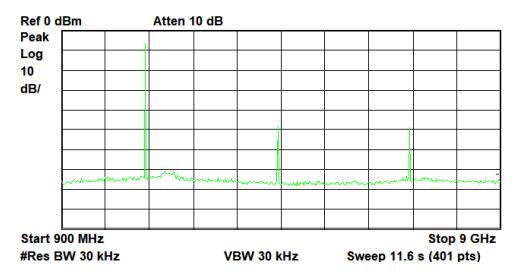

| 4.34 | Harmonics from the present BLE TX                                                   |

| 4.35 | RF-FE with integrated matching network and antenna switch 105                       |

|      |                                                                                     |

| 5.1  | Low-power DPLL-centric receiver architecture                                        |

| 5.2  | FOM comparison with the state-of-the-art fractional DPLLs under $5 \text{mW}$ . 109 |

| 5.3  | (a) Proposed closed-loop DPLL-based ADC with DC offset at DAC out-                  |

|      | put (b) Conversion diagrams                                                         |

# **List of Tables**

| 1.1 | Transmitter Characteristics                                 | 7   |

|-----|-------------------------------------------------------------|-----|

| 1.2 | Receiver Characteristics                                    | 8   |

| 3.1 | Comparison Table of The State-of-The-Art DTCs               | 48  |

| 3.2 | Comparison Table of The State-of-The-Art fractional-N DPLLs | 64  |

| 4.1 | Comparison Table of The State-of-The-Art BLE 4.0 TR/RX      | 103 |

| 4.2 | Major Differences from BLE 4.2                              | 104 |

| 5 1 | Comparison Table of The State-of-The-Art RLF 4.0 TR/RX      | 108 |

## **Chapter 1**

#### Introduction

# 1.1 Internet-of-Things and Its Available Wireless Standards

Internet of Things (IoT) covers huge industries and application scenarios. Fig. 1.1 shows several application cases. Machines such as vehicles can be connected over the air and "talk" to each other to ensure safe driving. Devices on or inside a human's body can help monitor both the mental or physical state from a person and share those data with a doctor or the family members. Devices for our daily life such as smartphones, cameras, TVs, lights will also be connected to cooperate, which multiple application scenarios can be defined to shrink the manual setting by humans greatly. For example, multiple types of sensors can be placed inside the house, ambient light sensors and proximity sensors will automatically turn on the light and change the level of the light by sensing if there are people inside the room and how is the environment light condition. Humidity sensors, temperature sensors, and air quality sensors will control the air conditioner and the air purifier to regulate the room temperature and clean the harmful particles inside the house. By those interconnected "smart" devices in the house, the house itself can become intelligent and more comfortable for people to live in. Finally, the city infrastructures will also form a huge network, for example, devices with beacon mode will form a very accurate navigation network that can navigate the people even in the indoor scenario. All those above mentioned wireless networks will greatly benefit from the high-speed wireless internet that enabled by the 5G cellular network. In the upcoming future, the small networks such as the wireless network in the house will be connected to a micro, pico or even femto gateway devices like the Wi-Fi router, and those micro, pico or femto gateway devices will finally be connected to the internet by the 5G base stations and eventually form a massive things' network. Tons of data can be processed locally or

Figure 1.1: The concept of the Internet of Things.

online. Artificial intelligence (AI) can access those data and help people to manage most of the things in our daily life, in our work *etc.*. A revolutionary era is approaching if IoT and other related technology are fully deployed.

After many years' researches and developments by industry companies and academic institutes, lots of wireless standards are carried out and developed year after year to realize the IoT era. Different standards are used for different cases in the complicate radio environment. Here we list some of the popular wireless standards for IoT applications:

**Bluetooth Classic:** A standard operates at 2.4GHz which is located in the globally unlicensed while being regulated industrial, scientific and medical (ISM) frequency band. It utilizes the frequency hopping technique to avoid being interfered. It specifies a data rate of up to 3Mbps with a maximum communication range of around 100m.

**Bluetooth Low-Energy:** A standard operates at 2.4GHz ISM-band and uses frequency hopping techniques. The latest standard of 5.0 version specifies a data rate of 125kbps, 1Mbps and 2Mbps and a minimum range of 200m outdoors and about 40 meters indoors. Other features include the beacon mode and ultra-low-energy consumption.

**IEEE 802.15.4:** A standard specifies a low-rate wireless personal area networks (LR-WPANs). It is the basis for ZigBee, WirelessHART, MiWi and ISA100.11a specifications.

**Zigbee:** A standard operates in the 2.4 GHz ISM-band with 250 kbps data rate. The maximum number of nodes in the Zigbee network is 1024. The communication range is approximately 200 meter.

**WirelessHart:** A standard provides a robust wireless protocol for the full range of process measurement, control, and asset management applications.

**DigiMesh:** A standard specifies a proprietary peer to peer networking topology for the wireless end-point connectivity.

**NFC:** It operates at a center frequency of 13.56 MHz using inductive coupled devices with a data rate up to 424kbps and a range of few centimeters.

**ANT:** It is used for wireless sensor networks operating at 2.4GHz ISM-band. It establishes rules for data representation, signaling, co-existence, error detection, and authentication.

**EnOcean:** It is an energy harvesting wireless technology. It works at 902MHz, 868MHz, or 315Mhz frequency band. The transmitting ranges are 30m for indoor and 300m for outdoor.

**Wi-Fi:** It operates at 2.4 GHz, 3.6 GHz and 4.9/5.0 GHz bands with a data rate from several Mbps to several Gbps. Common range is up to 100m and it can be extended.

**RFID:** It operates at 120-150 kHz (LF), 13.56 MHz (HF), 433 MHz (UHF), 865-868 MHz (Europe), 902-928 MHz (North America) UHF, 2450-5800 MHz (microwave), 3.1-10 GHz (microwave) frequency bands with a range from 10cm to 200m. Some usage examples include road tolls, building access *etc*.

**NB-IoT:** It is standardized by the 3GPP. It based on the present 3G/4G LTE networks with very narrow data bandwidth. It features at low rate and very long range.

#### 1.2 Bluetooth Low-Energy and its Applications

After decades of evolution from 1994, *Bluetooth*<sup>®</sup> technology becomes one of the most popular wireless standards in short and middle range communications. Together with Wi-Fi technology, it is widely adopted in almost all kinds of wireless communications. The most famous application scenario is its integration in every smart phone nowadays to replacing the conventional wire-line solutions such as the ear phones and keyboards *etc*. The Institute of Electrical and Electronics Engineer (IEEE) standardized the Bluetooth standard as IEEE 802.15.1. However it is no longer maintained by IEEE. Now a special interest group (SIG) oversees development of this standards as well as protects the trademarks. The manufacturer or the developer must satisfy Bluetooth SIG standards before releasing to the market.

The standards defines two modes for different purposes. The classic mode (Bluetooth

Classic) targets at a high data rate, and the low energy mode (Bluetooth Low-Energy/BLE) focus at ultra-low-power (ULP) operation. The BLE is more popular in terms of the IoT applications because of the extended battery life enabled by the supper low energy consumption. The moderate data rate can also meet most of the communication requirements. The core specification are already update to version 5.0 (BLE 5.0) [1] which added more new features for IoT applications than the previous version 4.2 (BLE 4.0) [2]. This thesis is based on BLE 4.0 because the work was started before BLE 5.0 has been released in the year of 2017. The physical layer specifications are shown in detail in [1, 2].

BLE devices support four different roles, which behave difference when different roles are selected:

- **Role 1**: It performs an advertiser which is connectible and can operate as a slave in the connection. For example, a thermometer sensor.

- **Role 2**: It performs a master device that scans for advertisers and can start and initiate the connections. It can establish many connections simultaneously. For example, the computer or the smart-phone.

- **Role 3**: It performs a broadcaster that is a non-connectible advertiser. Good examples are the tag for asset tracking or the tag for the pet ID.

- Role 4: It performs an observer scans for advertisements, while it couldn't initiate the connections by itself. For example, a display that receives the temperature data and displays it.

The first two roles are connectible and the last two roles are non-connectible. The variety of the roles present a good support for different low-range medium/low-data rate application scenarios. It is another reason that BLE standard becomes one of the most popular wireless technology for IoT applications.

#### 1.2.1 Beacon Mode of Bluetooth Low-Energy

In wireless technology, the beacon mode is the concept that a battery driven device keep broadcasting small pieces of information to the surrounded or passing-by devices. These small pieces of information may include: 1. the ambient data, such as temperature, air pressure, humidity *etc.*; 2. the micro-location data, such as asset tracking, retail *etc.*; 3. orientation data, such as acceleration, rotation, speed *etc.*. Usually, the transmitted data is a static one. However, it also may be the dynamic one, depending on the application. With the aforementioned BLE technology, the beacons can run for years without changing the battery. The BLE is ideal solution for beacon mode. Not only because of the low-power

operation but also the BLE eco-system is already deployed in most of the smart-phone and other BLE embedded devices. As such, the beacon mode will be one of a important technology for IoT and BLE will be a suitable standard to support this technology achieving better performance.

#### 1.2.2 Mesh Network of Bluetooth Low-Energy

As shown in Fig. 1.2, BLE supports a variety of wireless communications. It supports point-to-point communication, such as the audio transmitting and receiving, the video transmitting and receiving. It also supports broadcasting communication, such as beacon advertising. Recently, in the BLE 5.0, the Bluetooth SIG group added another feature to the present BLE standard, which is the availability of the mesh network. It will be the future of the communication topology for IoT applications. The mesh network is originated from the concept of massive network connection. It is a network topology in which a device (we name it a "node") transmits its data, and at the same time serves as a relay for other nodes. The routers are practiced to yield the most efficient data path for effective data communication. If a hardware failure occurs, many routers are available to continue the conversation which maximally ensures the connectivity and the data security.

#### 1.3 Challenges for BLE Transceiver Design

Fig. 1.3 shows an example of a BLE transient power profile from a commercial CC26XX SoC from TI. When the receiver is not active, the power is dominate by the leakage power/sleep power. When the desired signal is detected, the receiver is waken up by off-chip triggers and some pre-process procedures starts to run before transmitting and receiving the desired signal. After the pre-process operation, the RX and TX starts to work which receives and transmits data by a sequence decided by the application. The power consumption will be mainly dominated by the TX and RX active power if multiple transmitting and receiving steps are required. After finishing the receiving and transmitting steps, the TRX will do some post process and enter the sleep mode to save the power. Typical coin battery is compact for its size, however, the energy it contains is also limited by its size. For example, a SR44 alkaline coin battery contains an energy of 150mAh. Hence, the TX and RX active power should be minimized for the BLE applications.

Figure 1.2: Variety types of communications that BLE supports.

Figure 1.3: Power consumption of the breakdown of a Texas Instruments CC26XX BLE device during a connection event.

#### 1.3.1 Transmitter Design and its Challenges

Table 1.1 shows the specifications used to evaluate the BLE transmitter (TX). 40 channels with 2MHz spacing is assigned while the data rate is only 1Mbps with a 0.5 modulation

| Channels                           |                                       | K=0~39                  |  |

|------------------------------------|---------------------------------------|-------------------------|--|

|                                    |                                       | (2402MHz+K*2MHz)        |  |

| Modulation Sc                      | hama                                  | GFSK                    |  |

| Wiodulation 50                     | Modulation Scheme                     |                         |  |

| Eraguanay Day                      | ziation                               | 250kHz                  |  |

| Frequency Dev                      | /lation                               | (Minimum Value >185kHz) |  |

| Crosshala Data                     |                                       | 1Mbps                   |  |

| Symbole K                          | Symbole Rate                          |                         |  |

| Transmit Power                     |                                       | -20dBm to 10dBm         |  |

| In-band Spur Emission <sup>a</sup> | $ M^b-N^c =2MHz$                      | <-20dBm                 |  |

| in-band Sput Ellission             | M <sup>b</sup> -N <sup>c</sup>  ≥3MHz | <-30dBm                 |  |

| Harmonic Emission                  | 2nd Harmonic                          | <-41dBm                 |  |

| Trainfonc Emission                 | 3rd Harmonic                          | <-41dBm                 |  |

| Center Frequency Drift             | Max. Value                            | ±50kHz                  |  |

| Center Prequency Difft             | Rate                                  | 400Hz/μs                |  |

Table 1.1: Transmitter Characteristics

index. Most of the signal energy concentrates between -500kHz to +500kHz. This large channel spacings between each channel can greatly relax the near channel interference which relax the power consumption for the receiver (RX) design. A center frequency drift tolerance is 50kHz which maximumly relaxes the local oscillator (LO) specifications. Even a free running oscillator could be adopted in the design by this relaxed condition. However, in order to reduce the influence to other receiving devices such as Wi-Fi RX, the second harmonics should be greatly suppressed. A -41dBm of the 2nd harmonic of the transmitting frequency should be satisfied, which brings challenges when TX delivers a 10dBm signal. The harmonic suppression ratio should be over 51dBc to satisfy the FCC regulation.

#### 1.3.2 Receiver Design and its Challenges

Table 1.2 lists the most common requirements for the BLE RX design. A minimum sensitivity of -70dBm is required for the TX. However, most of the commercial applications required a less than -90dBm sensitivity. The improved sensitivity not only improves the receiving range but also help reduce the transmitting power level. The reduced power level from TX can greatly reduce its influence on other surrounded receivers. The max-

<sup>&</sup>lt;sup>a</sup> An adjacent channel power is specified for channels at least 2 MHz from the carrier. Power is integrated in 1MHz bandwidth.

<sup>&</sup>lt;sup>b</sup> Center frequency.

<sup>&</sup>lt;sup>c</sup> Adjacent channel frequency.

| Sensitivity                             |                  | <-70dBm     |

|-----------------------------------------|------------------|-------------|

| Max. Input I                            | Max. Input Power |             |

| PER <sup>a</sup> (BE                    | R)               | 30.8%(0.1%) |

|                                         | 0MHz             | -21dB       |

| Adjacent Channel Rejection <sup>b</sup> | 1MHz             | -15dB       |

|                                         | 2MHz             | 17dB        |

|                                         | ≥3MHz            | 27dB        |

|                                         | 30MHz-2000MHz    | -30dBm      |

| Blocker Power <sup>b</sup>              | 2000MHz-2400MHz  | -35dBm      |

| BIOCKEI FOWEI                           | 2500MHz-3000MHz  | -35dBm      |

|                                         | 3000MHz-12.75GHz | -30dBm      |

Table 1.2: Receiver Characteristics

<sup>&</sup>lt;sup>b</sup> The desired signal is used for the measurements.

Figure 1.4: The basic receiver architecture

imum input power tolerance is required as -10dBm which results a minimum dynamic range requirement of -70dBm-(-10dBm)=60dB for the entire receiver. The blocker performances are separated as two kinds: the in-band blocker tolerance/the adjacent channel rejection (ACR) and the out-band blocker tolerance. They are measured using a desired signal ( $S_{\rm desire}$ ) as the transmitting signal from TX. The blocker signals are specified as ( $S_{\rm blocker}$ ) with different offset frequency from  $S_{\rm desire}$ .  $S_{\rm desire}$  is specified as 3dB higher than the specified sensitivity level of -70dBm which is -67dBm.  $S_{\rm desire}$  and  $S_{\rm blocker}$  are both specified as 1Mbps GFSK signals with modulation index of 0.5 and BT of 0.5. The modulating data for  $S_{\rm desire}$  is PRBS9 code while PRBS15 is used for  $S_{\rm blocker}$ .

<sup>&</sup>lt;sup>a</sup> Packet error rate.

From this table, the design challenges can be explained when we roughly derive the electrical specifications for the RX design. The basic architecture of the modern RX is shown in Fig.1.4. A radio frequency (RF) front-end (FE) is followed after the antenna which amplify the desired signal  $S_{\rm desire}$  with minimum added noise while suppressing the interference signal  $S_{\rm blocker}$ . It also performs an frequency translator by using a LO that shift the center frequency of the  $S_{\rm desire}$  to a lower frequency in order to relax the requirements of further stages. An analog to digital converter (ADC) can be placed after the RF-FE to convert the analog signal into digital signal. The digital modem will do a post process to decode the analog baseband signal into 0 and 1 which can be recognized by digital computers to translate into all kinds of virtual information.

The RX sensitivity is mainly decided by the noise from the RF-FE and required signal to noise ratio ( $SNR_{\rm modem}$ ) from the digital modem to satisfy the specified bit error rate (BER). For a FSK baseband signal such as BLE, a 12dB can be an idea estimation of  $SNR_{\rm modem}$ . For a -95dBm sensitivity, the required noise figure of the RF-FE will be:

$$NF = S ensitivity - 10\log_{10}(kT \cdot B) - SNR_{\text{modem}} = 7dB$$

(1.1)

where B is the bandwidth of the baseband signal. This puts a stringent noise requirement on the amplifier design in RF-FE which will burn significant amount of current to suppress the noise from the antenna (kT noise). Another challenge comes from the large input power of -10dBm. Because the conversion gain of the input  $I_{RF}$  to the output  $V_{BB}$  cannot be absolute linear as shown in Fig.1.4, the large input signal will cause desensitization of the RX gain as well as produce the intermodulation signals such as 3rd-order intermodulation distortion (IMD3). The intercept point (IP) is used to evaluate this performance. The 3rd-order IP can be compute as:

$$IIP3 = -10dBm + SNR_{\text{modem}}/2 = -4dBm$$

(1.2)

The larger IIP3 is, the larger power budget will be required to maintain the linearity. Those noise and linearity requirements can be integrated into one specification of RX dynamic range. Here a dynamic range of -95dBm-(-10dBm)=85dBm is required for the RX. Assume the conversion gain of the RF-FE is  $G_{RF}$  and the SNDR of the ADC is SNR<sub>ADC</sub>. We can have the following two equations:

$$SNR_{ADC} + G_{RF} - NF - SNR_{modem} = 85dBm$$

$$\Rightarrow SNR_{ADC} + G_{RF} = 104dB$$

(1.3)

Such a high dynamic range will either require a high gain of RF-FE or a high resolution

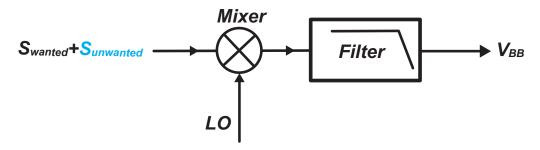

Figure 1.5: Wanted and unwanted signals down-converted by a mixer and LO.

of the ADC. If a high  $G_{RF}$  is designed, not only the increased gain itself requires more current but also the linearity is hard to maintain with limited power budget as shown in Eq. 1.2. If we enlarge the effective resolution of ADC, the power will also increase significantly.

Another challenge for RX is the blocker immunity especially the ACR. Basically, analog filters are embedded to filter out the additional energy from the blockers. If a linear RF-FE and an idea ADC is assumed, the suppression required for ACR at 3MHz offset will be at least 39dB which means a 3rd-order low-pass filter (LPF) is required for a 500kHz bandwidth. Notice that any non-idea effects from the RF-FE and ADC will greatly increase the required suppression from the LPF which increase the power consumption.

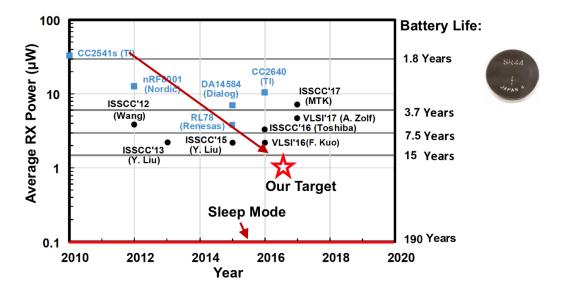

Last but not least is the nonideality from the LO. Fig.1.5 shows the frequency translation process inside the RF-FE. A mixer is acted as a multiplier that move the high frequency signals to a lower frequency by using a LO signal. As shown in Fig.1.6(a), if an ideal LO is used, the wanted signal  $S_{\text{wanted}}$  will be down-converted to a intermediate frequency ( $f_{\text{IF}}$ ) while the unwanted signal such as a blocker is down-converted to  $f_{\text{unwanted}} - f_{\text{LO}} + f_{\text{IF}}$ . However, the local oscillator such as a oscillator or a phase locked loop (PLL) will produce noise around the idea LO frequency, *i.e.*, phase noise. As shown in Fig.1.6(b), the unwanted signal will also be down-converted to  $f_{\text{IF}}$  and the component  $S_{\text{mx,noise}}$  cannot be distinguished after conversion. This process is well known as reciprocal mixing. Because of the nonideality from the LO, the phase noise level and the spur energy from the LO should be well constrained at blocker frequencies. For the ACR at 3MHz, the phase noise at 3MHz offset frequency is calculated as:

$$PN_{\text{ACR} \geqslant 3\text{MHz}} = S_{\text{desired}} - S_{\text{blocker}} - SNR_{\text{modem}} - 10\log_{10}(B) = -99\text{dBc/Hz}$$

(1.4)

The spurs from the LO, such as the fractional spur and the reference spur, will also cause reciprocal mixing which leads to potential degradation on the SNR of the desired

Figure 1.6: (a) Conventional data digitization process by the full-range TDC (b) Phase domain diagram.

signal. For the offset frequency more than 3MHz, the maximum spur level can be calculated as:

$$Spur_{ACR \ge 3MHz} = S_{desired} - S_{blocker} - SNR_{modem} = -39dBc$$

(1.5)

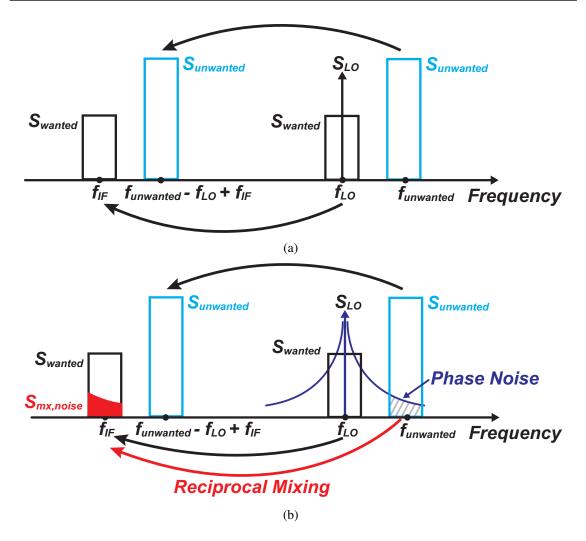

As a conclusion, the main challenge for the BLE RX is from the limited power budget when low sensitivity and high blocker tolerance are simultaneously required. Fig. 1.7 shows the battery life of the state-of-the-art RX using a coin battery (SR44). A duty-cycle of 600 $\mu$ s over 1s (0.06%) is assumed to enable and disable the RX. Due to the small duty cycle, the leakage power in sleep mode of the RX should be taken into consideration. From the data sheet of TI's most recent BLE SoC series (CC26XX), the leakage power can be assumed around 100nW in sleep mode. And the battery can support the receiver work for 190 years in the sleep mode, which can be negligible for RX operation. If we

Figure 1.7: Battery life of the state-of-the-art BLE RX and our target.

assume the the RX requires a zero start-up time, the RX active power will dominate the RX system power. An active power of under 2.5mW can support the RX system keep working for 19 years.

#### 1.4 Overview of the Thesis

The aim of this thesis is to investigate and achieve a fully integrated BLE transceiver using advanced CMOS technology toward the future IoT technology. The thesis is organized as follows:

Chapter 1 begins with an overview of the wireless standards for IoT applications and carries out the importance of the BLE standard. Chapter 1 also analyzed the design challenges for the BLE TRX design when considering the PHY specifications. The reciprocal mixing effect is explained in detail for the RX design, and the corresponded phase noise and spur performances of the DPLL are calculated and given.

Chapter 2 introduces some fundamentals and essential features of both the analog-type fractional-N PLL and the digital-type fractional-N PLL. The focus of Chapter 2 is on the digital-type PLL toward advanced CMOS technology. Different DPLL architectures are introduced to show the trade-offs between the power, jitter, locking time, etc. for each DPLL architecture. Then, various time-to-digital converter (TDC) and DTC architectures are introduced and reviewed for their power, jitter, and linearity trade-offs. Finally, the phase noise of the LC oscillator is introduced for understanding the noise to the phase

noise conversion mechanism.

Chapter 3 presents the proposed ULP fractional-N DPLL, which achieves sub-mW operation, a worst-case fractional spur of -56 dBc, and a jitter-power FOM of -246 dB. A 1st-order DSM-based fractional-division controller is discussed and analyzed for demonstrating its potential to support the sub-mW operation for a DPLL with a good jitter performance. A 10-b isolated constant-slope DTC is proposed to demonstrate the linearity and power efficiency improvements over the conventional DTC architectures. The gain-and-offset calibration of the time amplifier (TA) is introduced to help minimize the inband phase noise degradation by both TA gain error and the TA offset. Finally, the whole fractional-N DPLL design is carried out and measured with the proposed techniques. The comparison with the state-of-the-art fractional-N DPLL is summarized for demonstrating the merits of using the proposed techniques.

Chapter 4 introduces a BLE transceiver that utilized the proposed DPLL above as a central component. The embedded low-power wide-bandwidth fractional-N DPLL performs as 1) DPLL-based analog-to-digital converter (ADC) for the RX; 2) local oscillator (LO) for the RX; 3) phase and frequency synchronizer for the RX; 4) direct frequency modulator for the TX. The multi-function of the DPLL minimizes the power consumption of the TRX. The wide-bandwidth DPLL supports the single-path demodulation method for reducing the conventional I/Q branches to only I channel in RX. Hence, the number of the required analog baseband circuits is reduced by half, which helps reduce the RX power consumption significantly. Besides, the dynamic range of the DPLL-based ADC is greatly enhanced by 18 dB thanks to the proposed DAC feedback structure. It substantially improves the sensitivity and blocker performances. Finally, the entire BLE TRX is introduced and evaluated, which achieved the recorded low power consumption when compared with other state-of-the-art BLE TXs/RXs.

Chapter 5 is the conclusions for the thesis and the presented studies. Finally, future works are discussed for further developing the presented researches in this thesis.

### **Chapter 2**

# Fractional-N Digital PLLs for Wireless Communication

#### 2.1 Analog-Type Fractional-N PLLs

Due to the limited quality factor of the resonating circuits and unpredicted control gain, a free-running oscillator along can not used as a local oscillator frequency source nor the clock synthesizer. By using a negative feedback system and a high quality factor reference clock to control the free running oscillator, a frequency synthesizer/phase locked loop (PLL) can be realized. The analog PLL, comparing with its recent counterpart digital PLL(DPLL), still have better performance in terms of the phase noise performance. The Charge Pump PLL(CPPLL) as one of the most popular analog PLLs is widely researched and developed.

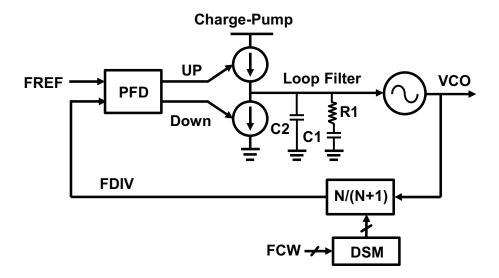

The topology of a CPPLL is shown in Fig. 2.1. The PFD(phase/frequency detector) will compare the phase and frequency error between reference and feedback clock and generates the frequency/phase error. The charge pump will converted the frequency/phase error to a loop filter and produce the correction signal to the VCO. The feedback signal will be divided by a frequency divider. If this divider operates at a integer value, it is called integer-N PLL. If a fractional divider is applied to the feedback path, it is called fractional-N PLL. The number of the pole at the origin in the open loop transfer function will decide which type of the control system is. If the PLL system has only one pole introduced by the oscillator, we call it type-I PLL. Type-I systems always show a good response speed comparing to higher type PLLs and very stable. However, it has a worse phase noise performance. The type-II PLL which is shown in Fig. 2.1 demonstrate an additional pole at origin introduced by the integrator capacitor C2. The static phase error will go to zero when the loop is locked, which exhibits a good phase noise performance.

Figure 2.1: Topology of CPPLL.

Figure 2.2: Phase-domain fractional-N DPLL.

#### 2.2 Types of Fractional-N DPLLs

Analog charge-pump PLL (CPPLL) has been the most preferred PLL architecture to implement fractional-N frequency synthesizing. CPPLL can realize the excellent jitter and spurious performance with small power consumption, *i.e.*, high FOM. However, an analog PLL loop filter requires a large area and is also very difficult to reconfigure. Further more, for advanced CMOS technology, digital circuits are more preferred to replace the analog counterparts such as filters, calibrations *etc*. To overcome these shortcomings, digital fractional-N PLL is investigated and studied which requires no large capacitors. Thanks to their intensive digital implementation, loop characteristics are much easier to reconfigure. Also, the digital PLL is much easier to shift from one process to another.

Fig. 2.2 shows the first proposal of the fractional-N DPLL. It uses a counter and a

Figure 2.3: Divider-based fractional-*N* ADPL.

time to digital converter (TDC) to count the phase values from the oscillator. A reference clock is used to perform a clean timer to read out the counted phases. The integer counter which works at oscillator frequency, will count every oscillator period. Its output can be represented as a integer phase. However, if only counter is implemented, there will always a residue phase information within one oscillator period cannot be extracted due to the limited resolution of the integer counter. Hence, a fractional counter with much finer resolution is required to cover one oscillator period to assist the integer counter operation. The fractional counter is also named as TDC. The integer phase and fractional phase of the oscillator within one reference period is quantized and synchronized by reference clock. Because a frequency control word (FCW) is more commonly used than the phase control word (PCW) in frequency synthesizer applications, the integer phase and fractional phase will be differentiate into the integer frequency and fractional frequency information by a digital differentiator. Then it compares with the desired FCW at PLL input. The error information is the frequency error and the phase error is produced after integration operation inside the digital loop filter (DLF). A digital controlled oscillator (DCO) is implemented which the oscillation frequency is controlled by digital codes. This architecture is well known for its pure phase domain operation and all the phase information from DCO can be derived by the counter and TDC.

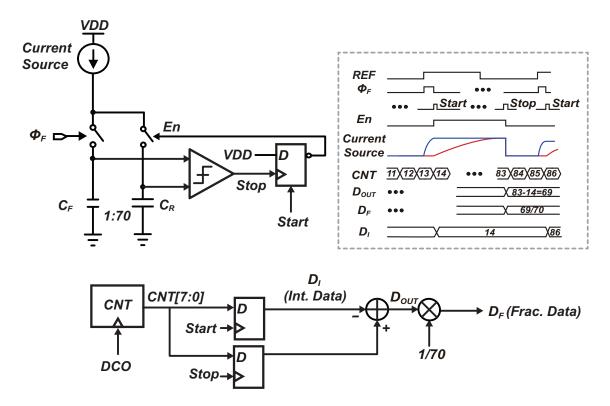

Another famous fractional-N DPLL architecture is shown in Fig. 2.3. This architecture is very similar to a CPPLL using the delta-sigma modulator (DSM) and a multi-modulus divider (MMDIV) at the feedback path. The MMDIV is a frequency divider as wel as a phase integrator. The FCW is input to the DSM oversampled by a clock at reference clock rate. The long bit width FCW will be modulated to a short bit width FCW which has a same length of the MMDIV control code width. The modulated output will dither the phase integration ratio of the MMDIV. In average, the MMDIV will produce an average phase integration ratio that should equal to the integration of FCW every refer-

Figure 2.4: DTC-based fractional-N DPLL implementation.

ence clock. If the phase from MMDIV is not equal to the reference phase, the TDC will produce a corresponded phase error. The DLF will filter the phase error and control the DCO accordingly. The TDC is similar as a phase frequency detector (PFD) and charge pump in CPPLL. The MMDIV also translate the frequency of DCO to a reference rate, hence the frequency error is also detected at TDC simultaneously. This architecture is known as the divider based DPLL.

There are several differences in designing these two architectures. The phase domain DPLL requires a absolute synchronized operation of the counter and the TDC to count the DCO phase within one reference period. And the TDC range should be exactly one DCO period. Any mismatch in the TDC range and DCO period will cause significant fractional spurs in fractional mode. As for the divider based DPLL, the TDC range should be over one DCO period at least if a 1st order DSM is applied. A higher DSM order will results in a much more wider TDC range. However, the TDC may not synchronize with any other circuits.

For phase domain DPLL, the TDC and counter are both working at DCO frequency. While for divider based architecture, the frequency is lower at TDC input to a rate of the reference frequency.

As mentioned above, for the divider based fractional-N DPLL, the TDC will require a quantization range of over at least one DCO period. As a phase calculator, the linearity is very important for achieving lower fractional spurs. This will cause large power consumptions for TDC design which is not preferred in low power applications such as BLE *etc*. Fundamentally, this large phase error is caused by the quantization error from the MMDIV due to the finite phase resolution of one DCO period. It performs an integer

integration operation. So, if we can minimize this error, the phase error at TDC input could be reduced. Since the MMDIV is an integer phase integrator, a fractional integrator with much higher resolution is required. A digital to time converter (DTC) is proposed to realize fractional time resolution while the digital integrator is used to integrate the fractional phase, as shown in Fig. 2.4. As a results, the DTC can reduce the quantization error from the MMDIV to several DTC resolution time hence a narrow-range TDC can be implemented. This greatly cut the TDC power consumption. At a extreme case, even 1bit TDC (BBPD) can be used for fractional operation. However, as discussed in ref. [3], a BBPD suffers from the very limited quantizing range and an ill defined gain. The limited quantizing range causes the slow convergence speed of the PLL by the well known cycle-slip effect and also causes slow settling speed of the DTC gain calibration (LMS). A multi-level TDC is desired for achieving faster converge speed and an well defined PD gain, which is more preferable for wireless applications [3].

# 2.3 Building Blocks of Fractional-N DPLL

## **2.3.1** Time-to-Digital Converter(TDC)

As one of the most important important building blocks in DPLL operation, time to digital converter (TDC) converts the phase information of the DCO into digital codes with sufficient accuracy, *i.e.*, the effective resolution of TDC. As for a data converter, the power consumption, the quantization noise, the linearity and the full scale of the TDC are important factors to take care and must be well optimized to satisfied the system requirement. In recent years, several different types of TDCs have been developed to achieve high resolution and good linearity, *i.e.*, the flash type, the charge-based type and the noise shaping type.

#### Flash Type TDC

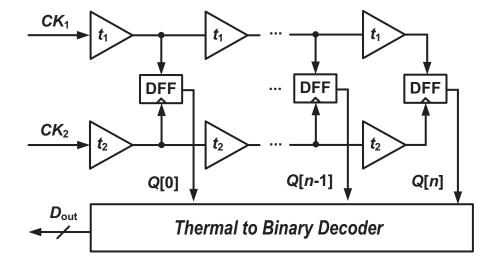

Flash type TDC is the most commonly seen TDC because of its simplicity in design and its resolution improvement from the advanced CMOS technology. Just like flash type ADC, analog interpolation is required to generate multiple references to compare with. The flash type ADC is using resistor string to interpolate a clean reference voltage and the signal is compared with each interpolated voltage reference using a voltage comparator. The voltage drop across the each of the resistor is the designed voltage resolution. Using the same mechanism, the flash type TDC uses a CMOS buffer chain to interpolate a clean reference clock. It is also called the "delay line based TDC" as shown in Fig. 2.5. The reference clock  $CK_1$  is interpolated by the buffers with a intrinsic delay of  $t_1$  to generate

Figure 2.5: Delay line based flash TDC.

multiple clock edges. Then,  $CK_2$  compares with each edge to derive the lead and lag relationship by using high precision D flipe-flop (DFF) logics. The thermal codes are converted into binary output by means of a decoder. It is easily notice that the buffer delay shrink with the technology evolution which improve its resolution. However, even with the 7nm technology, the maximum achievable resolution is around 5ps. For typical high performance fractional-N DPLL, sub-ps resolution is required for lower in-band phase noise. Furthermore, the buffer delay mismatch will greatly degrade the INL performance if a large phase quantizing range is desired.

In order to improve the resolution, vernier chain TDC is proposed as shown in Fig. 2.6. As compared with delay-line based TDC, another buffer chain is inserted at  $CK_2$  path. By doing so, the minimum quantization steps becomes  $t_1 - t_2$  which can be very small regardless to the technology. However, a large quantization range will cause a very long buffer chains at both paths. It degrades the linearity while consuming large power. Another technique to interpolate the time is to use a so-called "Local Passive Interpolation (LPI) TDC" [4] as shown in Fig. 2.7. A resistor chain is inserted between the input and the output of the delay cell to acquire more phases from one delay unit. The internal phases are more robust in PVT than the vernier-chain TDC. However, higher linearity requires smaller resistors which greatly increases power dissipation. Other methods to increase the flash type TDC resolution are reported in [3, 5, 6] by using time amplifier (TA). TA amplifies the input time difference proportional to its gain which effectively increases the TDC time resolution. However, the TA suffers from gain and offset variation across PVT which makes it less practical.

Figure 2.6: Vernier-chain TDC.

Figure 2.7: Linear passive interpolated TDC.

## **Charge-based Type TDC**

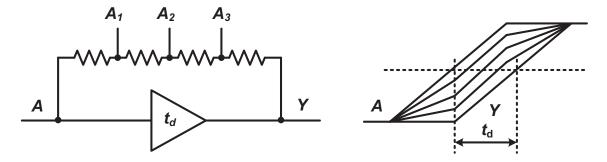

The charge based TDC is another choice to realize high performance TDC [7, 8]. One of the simplest way is to convert the charge information into the digital quantity using a real world ADC [8] as shown in Fig. 2.8. PFD and charge pumps are used to derive the input phase difference and convert the phase error into charge information. The SAR ADC followed can quantize the charge information on its capacitor into digital codes. The conversion gain is decided by the charge pump gain, and its resolution is decided by the charge pump current and the ADC resolution. The merits of this architecture is that the charge pump shares integrating capacitor with the capacitor-DAC (CDAC) inside the SAR ADC, and its resolution can be lower to sub-ps with sufficient amount of quantization range. However, the two individual charge pumps required for the ADC for differential signals suffer from mismatches. Furthermore, the up-down current mismatches are also critical factor that will degrades the linearity performance.

Figure 2.8: Charge domain TDC using SAR ADC.

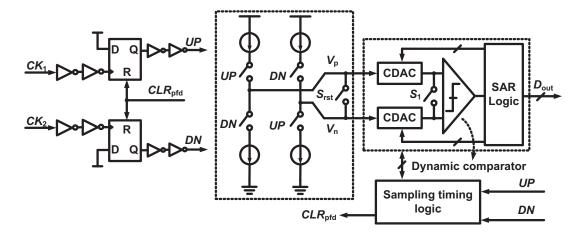

Single Slope TDC (SS-TDC) is proposed to realize high resolution, good linearity with lower power consumption [7] as shown in Fig. 2.9. Instead of using two charge pumps, a single current source are used to generate a slope  $V_F$  that proportional to the phase error  $\Phi_F$ , and the "amplifier" slope  $V_{RAMP}$  by using N:1 ratio capacitors  $C_R$  and  $C_F$ . When the current source starts charging  $C_R$ , a start signal is generated and a counter value running at  $f_{CNT}$  is recorded as CNT(N). When  $V_{RAMP}$  reaches the coltage level of  $V_F$ , a stop signal is generated by a comparator. The counter value of CNT(N+1) is recorded. Hence, the time difference  $\Delta T_{ERR}$  can be compute using the following equation:

$$\Delta T_{\text{ERR}} = \left(CNT(N+1) - CNT(N)\right) \cdot \frac{1}{f_{\text{CNT}}} \cdot \frac{1}{N}$$

(2.1)

This method shares the current source in two conversion steps which cancels the nonlinearity from the charging process. It achieves a high linearity with good power efficiency. However, the resolution is depends on how fast the counter runs, this potentially limits the maximum achievable resolution from a high reference clock.

## **Noise-Shaping TDC**

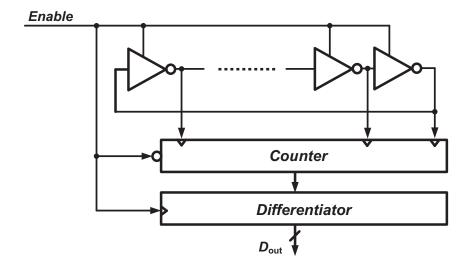

As widely known, noise shaping technique can improve the effective resolution by shaping the noise out of the spectrum of interest. Just like noise shaping ADC that shapes the low frequency quantization noise power to the high frequencies, the noise shaping TDC can shape the jitter power to the higher frequencies. The most famous architecture of noise shaping TDC was proposed in [9] known as the gate-ring oscillator (GRO) TDC. As shown in Fig. 2.10, when *Enable* signal is high, the counter works to count the phases of the oscillator. The counted data is sampled at the falling edge of *Enable* and then reset

Figure 2.9: Single-slope TDC.

the counter. The phase information from *Enable* is reserved using the gating inverters even the counter is reset. Consequently, the next counting can start from the previous stored residue phase which results a continues phase counting over a time period. The followed differentiator after counter will shape the quantization noise from the oscillator and counter in a first order manner. However, the charge sharing issue and the current leakage from the *Enable* path will greatly affect the TDC linearity. Furthermore, the GRO TDC also suffers a deadzone issue when *Enable* pulse is very small.

## **2.3.2** Digital-to-Time Converter(DTC)

As discussed above, to reduce the dynamic range of the TDC, digital to time converter (DTC) used to assist the operation of the TDC with narrower dynamic range. It improves the TDC resolution and linearity while achieving high energy efficiency on phase quantization process. As like TDC, the power consumption, linearity, resolution and noise are also important for DTC design.

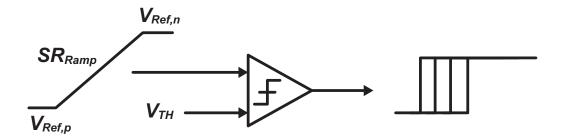

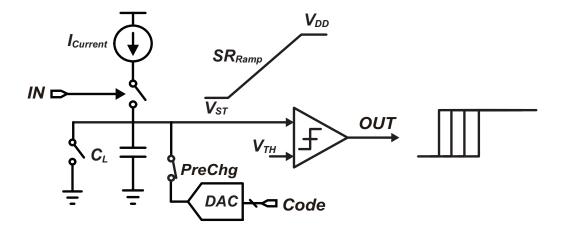

In general, DTC is a circuit that generates delays instead of quantizing phase errors. It can be designed in a much more efficient way than the TDC. To get a delayed rising edge, a slope with a slew rate of  $SR_{Ramp}$  and a comparator with a threshold of  $V_{TH}$  are required

Figure 2.10: GRO TDC.

Figure 2.11: Concept of DTC.

as shown in Fig. 2.11. The delay can be written as:

$$t_{\text{delay}} = \frac{V_{\text{TH}} - V_{\text{Ref,p}}}{SR_{\text{Ramp}}} \tag{2.2}$$

From Eq. (2.2), the delay can be varied by changing either the comparator  $V_{\rm TH}$ , the starting voltage of the slope  $V_{\rm Ref,p}$  or the slew rate of the slope  $SR_{\rm Ramp}$ . Each of which has different design trade-offs and we will discuss it later.

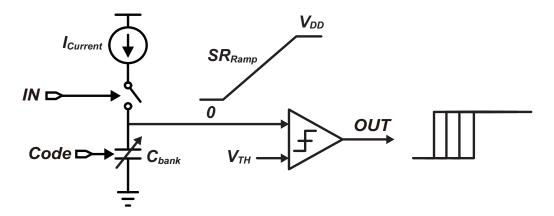

## Variable Slew Rate (Variable-Slope) DTC

As for the most commonly seen DTC in [10] shown in Fig. 2.12, it utilized a so called variable slope method to acquire different delays. A current source is used to generate the ramp signal triggered by input. A digital controlled capacitor bank is used to vary the

Figure 2.12: Concept of DTC.

slew rate of:

$$SR_{\text{Ramp}} = \frac{I_{\text{current}}}{C_{\text{bank}}} \tag{2.3}$$

We can write the achievable delay range  $(DR_{DTC})$  as:

$$DR_{\rm DTC} = V_{\rm TH} / \frac{I_{\rm Current}}{C_{\rm bank}} = V_{\rm TH} \cdot \frac{C_{\rm bank}}{I_{\rm Current}}$$

(2.4)

If we assume the current is constant during charging and discharging the  $C_{\text{bank}}$ , we can write the DTC power consumption as:

$$P_{\rm DTC} = V_{\rm DD} \cdot I_{\rm Current} \cdot f \cdot V_{\rm DD} / \frac{I_{\rm Current}}{C_{\rm bank}} = V_{\rm DD}^2 \cdot C_{\rm bank} \cdot f$$

(2.5)

f is the operation frequency of the DTC. From the above equaltion, double the delay range while keeping a same power consumption,  $C_{\text{bank}}$  cannot be changed as shown in Eq. (2.5). Hence,  $I_{\text{NMOS}}$  should be halved as shown in Eq. (2.4). The variance of the timing jitter of the DTC can be analyzed like in [11]. We can write the jitter variance equation of the DTC as:

$$\sigma_{\text{DTC}}^{2} = \frac{4kT\gamma_{\text{Current}}DR_{\text{DTC}}}{I_{\text{Current}}(VDD - V_{\text{TH}})} + \frac{kTC_{\text{bank}}}{I_{\text{Current}}^{2}}$$

$$= \frac{kTC_{\text{bank}}}{I_{\text{Current}}^{2}} \cdot \left(1 + \frac{4\gamma_{\text{Current}}}{VDD/V_{\text{TH}} - 1}\right)$$

(2.6)

where k is the Boltzmann constant, T is the temperature. Now we found if we reduced the current by half, the jitter will double. This is the well know delay range and jitter trade-off for delay elements. To reduce the jitter from DTC, the current and load capacitor bank should increase simultaneously while leaving there ratio the same.

Figure 2.13: Constant slope DTC vs variable slope DTC.

## Variable Starting Voltage (Constant-Slope) DTC

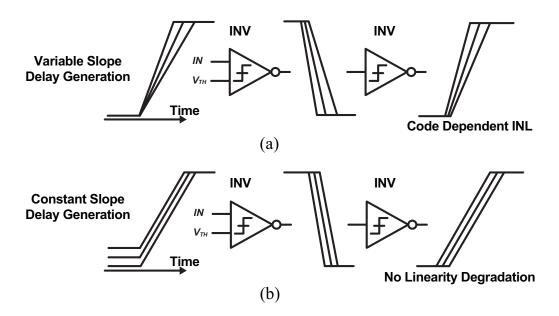

The variable slope architecture shows a simplicity in design while bringing a major problem. As shown in Fig. 2.13(a), a comparator outputs reversed edge from its input at the threshold voltage. Internally, the comparator is a open-loop amplifier who has a very high gain around its reference voltage. Any small voltage difference between the IN and  $V_{\rm TH}$  will be amplified and the output will be saturated. It the gain is infinite, no matter what the input slew rate is, the output will instantaneously drops to zero at the first input, and the second stage will produce its corresponded rising edge. However, practically, the gain can not be infinite. The finite gain will produce a finite slew rate at the output of the first stage if the input slew rate varies. As a results, there is a dependency of the variable delay and the input slew rate. This is a code dependent quantity which is very difficult to remove. It is the major nonlinear source for the variable slope DTC.

However, as shown in Fig. 2.13(b), if we vary the starting voltage while using the same ramp for every comparison, the nonlinearity due to the comparator imperfection can be fundamentally removed. This is the so called constant-slope DTC. As shown from Fig. 2.11, the starting voltages could be changes as well to generate code dependent delays. This methods achieves excellent linearity comparing with conventional variable delay DTCs [12].

Figure 2.14: Constant slope DTC.

Figure 2.15: Continues time comparator with a variable  $V_{\text{TH}}$  control.

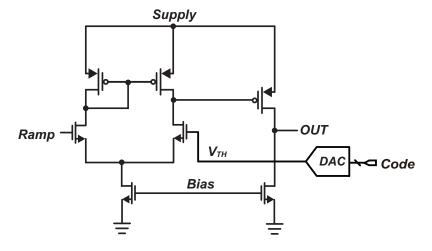

## Variable Threshold (Ramp-Division) DTC

From Eq. (2.2), the last thing we can do is to vary the threshold of the comparator. The slope still has a constant slew rate during the comparison which mitigates the finite gain induced nonlinearity. Fig. 2.15 shows a continues time comparator design, one of the comparator input is connected to a DAC which generated code dependent voltage. The  $V_{\text{TH}}$  decides the threshold of the comparator. Another side is connected to the constant ramp. When the ramp reaches the  $V_{\text{TH}}$ , a rising edge will be produced. However, practically, the common-mode voltage of the comparator will also vary according to the variable

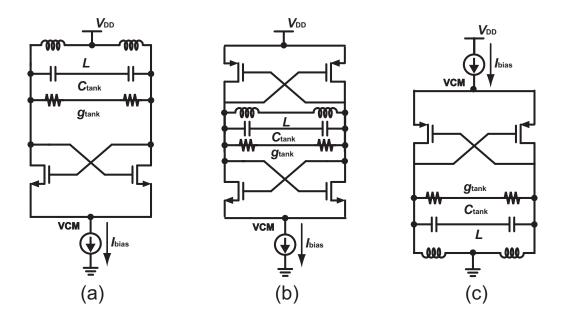

Figure 2.16: Three types of LC-VCO topology: (a) NMOS type LC-VCO; (b) CMOS type LC-VCO; (c) PMOS type LC-VCO.

$V_{\rm TH}$ . The common mode voltage will greatly affect the intrinsic delay of the comparator. This intrinsic delay could vary more than several ps which greatly degrade the linearity. It is even worse than the finite gain effect from the comparator.

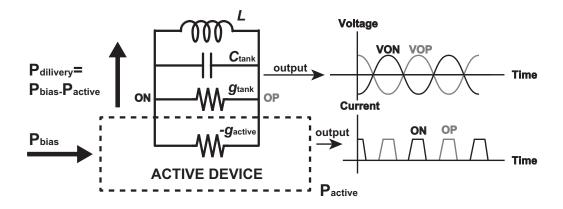

## 2.3.3 LC-Oscillator and Oscillator Phase Noise