# T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

## 論文 / 著書情報 Article / Book Information

| 論題(和文)           | ゲート付き4 端子法によるMoS2 FET の電気特性評価                                                                         |

|------------------|-------------------------------------------------------------------------------------------------------|

| Title(English)   | Gated Four-Probe Method for Evaluation of Electrical Characteristics in MoS2 Field-Effect Transistors |

| 著者(和文)           | 大場智昭, 川那子高暢, 小田俊理                                                                                     |

| Authors(English) | T. Oba, T. Kawanago, S. Oda                                                                           |

| 出典               | <br>  第79回応用物理学会秋季学術講演会 講演予稿集<br>                                                                     |

| 講演番号             | 19a-311-6                                                                                             |

| 発行日<br>          | 2018, 9                                                                                               |

### ゲート付き4端子法によるMoS2FETの電気特性評価

# Gated Four-Probe Method for Evaluation of Electrical Characteristics in MoS<sub>2</sub> Field-Effect Transistors

### 東工大未来研 工学院電気電子系 〇大場智昭 、川那子高暢、小田俊理

Tokyo Tech. QNERC and Dept of EE °T. Oba, T. Kawanago, S. Oda

E-mail: oba.t.ae@m.titech.ac.jp

#### 【はじめに】

二硫化モリブデン(MoS<sub>2</sub>)は天然の鉱物として存在し、バンドギャップが 1.2~1.8 eV の値を示す層状構造の無機単結晶半導体である。また膜厚を 1 分子層単位で調節できる、ダングリングボンドがないなどの層状構造特有の特徴をもつため、電界効果トランジスタ(FET)のチャネル材料として有望視されている。本研究ではバックゲート構造のMoS<sub>2</sub> FET を作製し、source と drain 電極の間に電圧測定端子を新たに形成することでチャネル内の電圧差を測定した。測定したチャネル電圧差とDrain-Source 電流から、MoS<sub>2</sub> FET のコンタクト抵抗やキャリア移動度を評価した。

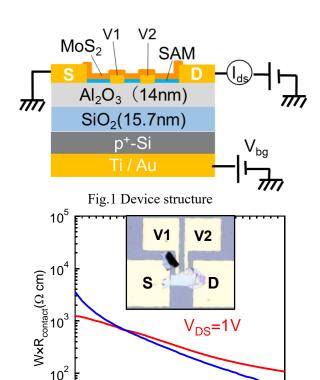

【実験方法】SPM 及び 1%HF で洗浄した p<sup>+</sup>-Si 基 板上に SiO<sub>2</sub> を作製し、その上に Al<sub>2</sub>O<sub>3</sub> を原子層堆 積法(ALD)によって形成した。次に、 Ti(10nm)/Au(40nm)の source/drain コンタクト及び 電圧測定端子を作製した。Ti は Au と Al<sub>2</sub>O<sub>3</sub> との 密着層として用いた。基板裏面には、真空蒸着に より Ti(30nm)/Au(20nm)を堆積し、バックゲート を作製した。その後、酸素プラズマを照射し、 Al<sub>2</sub>O<sub>3</sub>表面にヒドロキシ基を形成し SAM を溶か した 2-プロパノールに浸漬することで SAM/Al<sub>2</sub>O<sub>3</sub>構造を作製した。ゲート絶縁膜作製後、 MoS2を剥離法によって基板上に転写した。PDMS とマイクロマニピュレータを用いる事で、MoS2 をパターニングした基板上に転写した[1]。最後 に、窒素雰囲気中、150℃、30分間の熱処理を行 った。図1に、作製したデバイスの構造を示す。 【実験結果】Si 基板を用いた MOS キャパシタの 容量-電圧特性から SiO<sub>2</sub> の膜厚は 15.7 nm、Al<sub>2</sub>O<sub>3</sub> の膜厚は 14 nm であり、SAM/Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> 全体の 容量値は  $0.13 \mu F/cm^2$  であった。図 2 に、ゲート 付き4端子法によって測定したMoS2FETのコン タクト抵抗を示す。コンタクト抵抗は、 $10^2 \sim 10^3 \Omega$ cm と低い値を示した。同様にゲート付き 4 端子 法によって測定したチャネル移動度は、26 cm²/Vsであった。詳細は当日報告する。

Fig.2 Contact Resistance of MoS<sub>2</sub> FET with SAM-based gate dielectrics and Microscope image of fabricated FET

Gate Voltage(V)

$V_{DS} = 0.05 V$

#### 【参考文献】

10<sup>1</sup>

[1] A. C. Gomez et al., 2D Mater. 1, 011002 (2014). [謝辞]

-2

本研究に関して、ご協力頂いた東京工業大学の河 野行雄准教授に感謝致します。

本研究は、JST-CREST(JPMJCR16F4)、科研費若手(B)(17K14662)および矢崎科学技術振興記念財団の支援により実施された。

デバイス作製は東京工業大学の角嶋邦之准教授、 若林整教授、筒井一生教授にご協力いただいた。