# T2R2 東京工業大学リサーチリポジトリ Tokyo Tech Research Repository

### 論文 / 著書情報 Article / Book Information

| 題目(和文)            |                                                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | Study on Phase Locked Loop using Injection-Locked Ring Oscillator                                                                                                                           |

| 者者(和文)            | <br>  韓政勲<br>                                                                                                                                                                               |

| Author(English)   | Jeonghoon HAN                                                                                                                                                                               |

| 出典(和文)            | 学位:博士(学術),<br>学位授与機関:東京工業大学,<br>報告番号:甲第10896号,<br>授与年月日:2018年3月26日,<br>学位の種別:課程博士,<br>審査員:松澤 昭,高田 潤一,益 一哉,岡田 健一,山下 幸彦                                                                       |

| Citation(English) | Degree:Doctor (Academic),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第10896号,<br>Conferred date:2018/3/26,<br>Degree Type:Course doctor,<br>Examiner:,,,, |

|                   | 博士論文                                                                                                                                                                                        |

| Type(English)     | Doctoral Thesis                                                                                                                                                                             |

## Study on Phase Locked Loop using Injection-Locked Ring Oscillator

#### Jeonghoon Han

A Dissertation in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

Department of International Development of Engineering Graduate School of Science and Engineering Tokyo Institute of Technology

February 2018

To My Loving Parents

## Acknowledgment

This thesis would not have been possible without all those people who have guided, supported, and encouraged me during my PhD studies.

Firstly, I owe my deepest gratitude to my supervisor, Professor Akira Matsuzawa, for giving me the opportunity to work with talented people of the lab, his valuable guidance, immense knowledge, motivation, enthusiasm, and patience. His immense knowledge, wisdom of life, and generous support have helped me to complete my dissertation and manage my life in Japan.

I would like to express my deep sense of gratitude to my vice supervisor, Professor Junich Takada, for his continuous support and guidance.

I greatly appreciate to Associate Professor Kenichi Okada for his valuable supervision, precious attention and support throughout my research.

I am deeply grate to Professor Kazuya Masu and Associate Professor Yukihiro Yamashita for constructive comments and advices.

I wish to thank Assistant Professor Masaya Miyahara for generous support, discussion and suggestions.

I also appreciate Ms. Yoshino Kasuga, Ms Makiko Tsunashima, and Mr. Hironori Sakaguchi for their support and helps.

I would like to extend my gratitude to all members of Matsuzawa and Okada Lab for their warm friendship, especially to Dr. Win Chaivipas, Dr. Musa Ahmed, Dr. Daehwa Paik, Dr, Hyunui Lee, Mr. Mitsutoshi Sugawara, Mr. Kenji Mori, Mr. Ninh Hong Phuc, Mr. Yusuke Asada, and Mr. Seungjong Lee for their encouragements and constructive discussions.

I wish to thank all members of COSMOS-kai in Oota-ku, especially Mr. Kuwahara. They have treated me like one of their own family.

I would like also to take this opportunity to express gratitude to Professor

Dong Myong Kim and Professor Dong Wook Kang of Kookmin University in Korea, for sincere and valuable guidance and encouragement during my undergraduate days.

Finally, I wish to thank my parents, brothers, and sisters. My life has been built based on their love and supports.

### Abstract

This thesis presents a study on a phase-locked loop (PLL) with an injection-locked ring oscillator. The proposed injection-locked PLL separates the injection-locked ring oscillator from the phase-tracking loop of the PLL such that can provide stable lock-state maintenance and the tolerance to temperature and supply voltage variation. The ideal lock range is also derived under direct injection method in an injection-locked ring oscillator to clarify stable lock state. The measurement results show that the proposed injection-locked PLL has the tolerance to a voltage variation of 11.2% in supply voltage of 1.2 V. In-band noises of the proposed PLL at offset frequencies of 10kHz and 100kHz are -108.2dBc/Hz and -114.6dBc/Hz, respectively.

Moreover, the metastable range detection method is introduced to achieve a balance of frequency coverage of the PLL. Also, the compensation technique to voltage and temperature variation in PLLs with hybrid control is introduced to enhance the tolerance to the variations

## Contents

| $\mathbf{A}_{0}$ | cknov | wledgn            | nent                          | iii          |

|------------------|-------|-------------------|-------------------------------|--------------|

| $\mathbf{A}$     | bstra | ct                |                               | $\mathbf{v}$ |

| C                | onter | its               |                               | vii          |

| Li               | st of | Figure            | es                            | xi           |

| Li               | st of | Tables            | s x                           | vii          |

| 1                | Intr  | $\mathbf{coduct}$ | ion                           | 1            |

|                  | 1.1   | Proces            | ss Scaling                    | 2            |

|                  | 1.2   | Analo             | g and Digital Circuits        | 4            |

|                  | 1.3   | Motiv             | ation and Thesis Organization | 8            |

|                  |       | 1.3.1             | Motivation                    | 8            |

|                  |       | 1.3.2             | Thesis Organization           | 9            |

| <b>2</b>         | Pha   | se-Loc            | cked Loops                    | 11           |

|                  | 2.1   | Jitter            | and Phase Noise               | 11           |

|                  | 2.2   | Oscilla           | ators                         | 15           |

|                  |       | 2.2.1             | LC Oscillators                | 16           |

|                  |       | 2.2.2             | Ring Oscillators              | 18           |

|                  |       | 2.2.3             | Injection-Locked Oscillators  | 26           |

|                  | 2.3   | Phase             | -Locked Loops                 | 29           |

|                  |       | 2.3.1             | Phase Detector                | 30           |

|                  |       | 2.3.2             | Charge Pump                   | 35           |

|   |      | 2.3.3    | Loop Filter                                                | 37  |

|---|------|----------|------------------------------------------------------------|-----|

|   |      | 2.3.4    | Voltage Controlled Oscillator                              | 39  |

|   |      | 2.3.5    | Loop Transfer Functions                                    | 40  |

|   | 2.4  | Summ     | nary                                                       | 47  |

| 3 | Inje | ection-l | Locked Ring Oscillator as a Frequency Multiplier           | 49  |

|   | 3.1  | Conve    | entional Lock Range of Injection-locked Oscillator         | 49  |

|   | 3.2  | Ideal    | Lock Range                                                 | 50  |

|   | 3.3  | Asym     | metric Lock Range of an Injection-Locked Ring Oscillator . | 55  |

|   | 3.4  | Summ     | nary                                                       | 61  |

| 4 | Inje | ection-l | Locked Charge Pump Phase-Locked Loop with a Replic         | ca  |

|   | Rin  | g Osci   | llator                                                     | 63  |

|   | 4.1  | Conve    | entional Phase Locked Loop                                 | 63  |

|   | 4.2  | Design   | n of Injection-Locked Oscillator                           | 69  |

|   |      | 4.2.1    | Process Variation                                          | 73  |

|   |      | 4.2.2    | Power Supply Voltage Variation                             | 77  |

|   |      | 4.2.3    | Temperature Variation                                      | 78  |

|   | 4.3  | Imple    | mentation of the Proposed Injection-Locked CPPLL           | 81  |

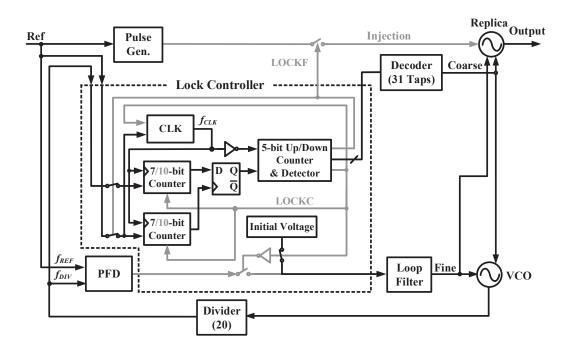

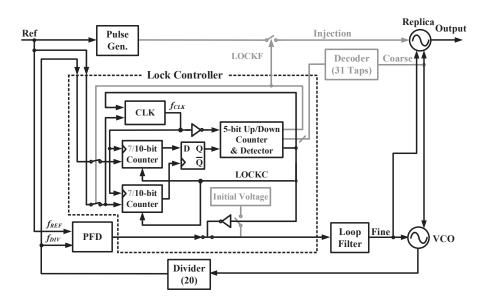

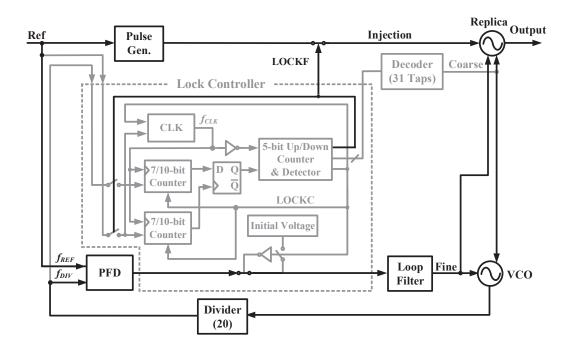

|   |      | 4.3.1    | Design of Lock Controller                                  | 82  |

|   |      | 4.3.2    | Configuration and Operation of the Proposed Injection-     |     |

|   |      |          | Locked CPPLL                                               | 94  |

|   | 4.4  | Perfor   | mance Comparison                                           | 98  |

|   | 4.5  | Summ     | nary                                                       | 102 |

| 5 | Enh  | ancen    | nent of Tolerance to Voltage-Temperature Variation         | 103 |

|   | 5.1  | Meta-    | Stable Detection                                           | 104 |

|   | 5.2  | Enhar    | ncement of Fine Tuning Range                               | 108 |

|   |      | 5.2.1    | Basic Concept of Enhancement of Fine Tuning Range          | 109 |

|   |      | 5.2.2    | Analysis of Tolerance Enhancement                          | 111 |

|   |      | 5.2.3    | Circuit Configuration and Operation                        | 115 |

|   |      | 5.2.4    | Simulation Results                                         | 119 |

|   | 5.3  | Summ     | nary                                                       | 122 |

| 6            | Con   | clusions and Future Work                               | 125 |

|--------------|-------|--------------------------------------------------------|-----|

|              | 6.1   | Conclusions                                            | 125 |

|              | 6.2   | Future Work                                            | 126 |

| Bi           | bliog | raphy                                                  | 127 |

| $\mathbf{A}$ | List  | of Published Papers                                    | 139 |

|              | A.1   | Journal Papers                                         | 139 |

|              | A.2   | International Conferences and Workshops without review | 139 |

|              | A.3   | Domestic Conferences and Workshops                     | 140 |

|              | A.4   | Co-Authors                                             | 140 |

|              |       | A.4.1 International Conferences and Workshops          | 140 |

# List of Figures

| 1.1  | ITRS load map for gate length                                            | 3  |

|------|--------------------------------------------------------------------------|----|

| 1.2  | Chip area in a system-on-chip (SoC)                                      | 4  |

| 1.3  | Comparison between current consumptions of LC and ring oscil-            |    |

|      | lators                                                                   | 5  |

| 1.4  | Comparison between occupied chip areas of LC and ring oscillators.       | 6  |

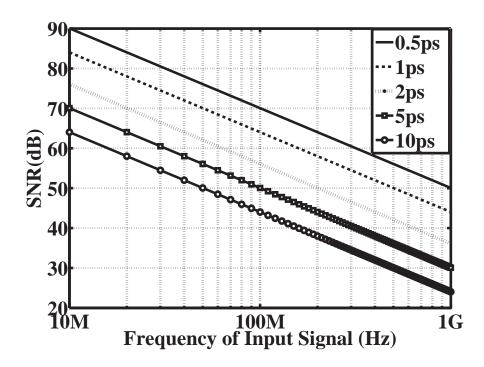

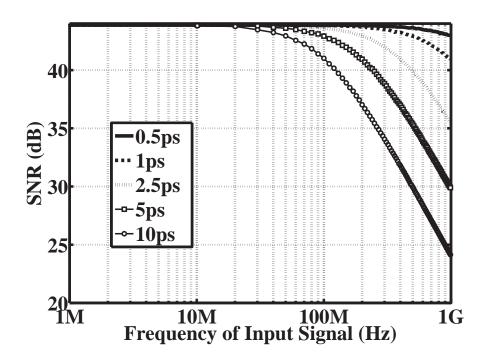

| 1.5  | Signal-to-noise ratio (SNR) of an ADC due to the clock jitter. $$ .      | 7  |

| 1.6  | SNR due to the clock jitter in a 7-bit 1Gsps ADC                         | 8  |

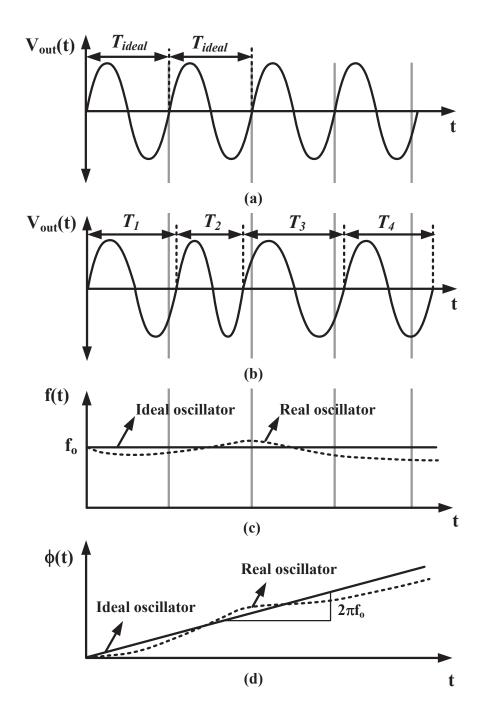

| 2.1  | Free running outputs of (a) an ideal oscillator and (b) a real oscil-    |    |

|      | lator, and (c) the output frequencies and (d) phases of the oscillators. | 12 |

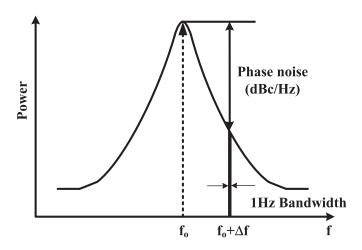

| 2.2  | Definition of phase noise                                                | 14 |

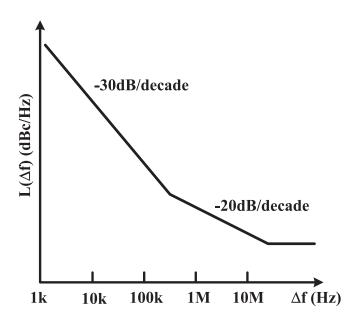

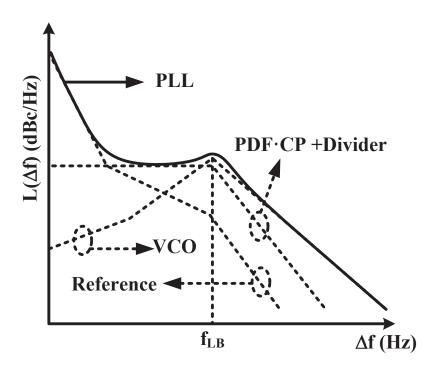

| 2.3  | Phase noise of an oscillator                                             | 15 |

| 2.4  | (a) Ideal LC resonant tank (b) resonant tank with parasitic resis-       |    |

|      | tance                                                                    | 16 |

| 2.5  | (a) Resonant tank with a parallel parasitic resistance (b) resonant      |    |

|      | tank with a negative resistance                                          | 17 |

| 2.6  | Complementary LC oscillator                                              | 18 |

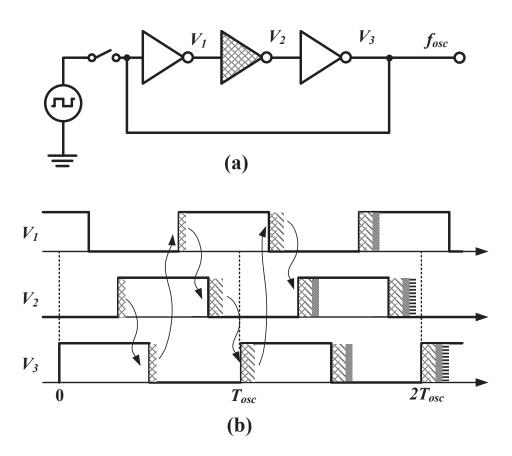

| 2.7  | Inverter-based ring oscillator                                           | 19 |

| 2.8  | (a) Delay stage of the inverter-based ring oscillator, and a simple      |    |

|      | circuit model to estimate (b) rising and (c) falling delays              | 20 |

| 2.9  | Linear model of the ring oscillator                                      | 21 |

| 2.10 | (a) Delay line with only one noisy stage and (b) waveforms of the        |    |

|      | delay line                                                               | 22 |

| 2.11 | (a) Ring oscillator with only one noisy stage and (b) waveforms of       |    |

|      | the ring oscillator                                                      | 24 |

| 2.12 | 4-stage differential ring oscillator                                | 25 |

|------|---------------------------------------------------------------------|----|

| 2.13 | Concept of an injection-locked oscillator                           | 26 |

| 2.14 | Waveforms in an injection-locked oscillator                         | 27 |

| 2.15 | Waveforms in an injection-locked oscillator                         | 28 |

| 2.16 | Phase noise in the injection-locked ring oscillators as a frequency |    |

|      | multiplier                                                          | 29 |

| 2.17 | Block diagram of a charge-pump PLL                                  | 30 |

| 2.18 | (a) Exclusive-OR phase detector (b) input an output signals of the  |    |

|      | exclusive-OR gate                                                   | 31 |

| 2.19 | The gain of the exclusive-OR gate                                   | 32 |

| 2.20 | Tristate phase-frequency detector                                   | 33 |

| 2.21 | Input an output signals of the tristate phase-frequency detector    | 33 |

| 2.22 | Gain of the tristate phase-frequency detector                       | 34 |

| 2.23 | Charge pump                                                         | 35 |

| 2.24 | Input and output signals of the charge pump                         | 36 |

| 2.25 | Active proportional-integral loop filter                            | 37 |

| 2.26 | Passive 1st order loop filter                                       | 38 |

| 2.27 | Passive 2nd order loop filter                                       | 38 |

| 2.28 | Passive 3rd order loop filter                                       | 39 |

| 2.29 | Transfer function of the voltage-controlled oscillator              | 40 |

| 2.30 | Linear model of the phase-locked loop                               | 41 |

| 2.31 | (a) Forward-loop response and (b) its phase of the 2nd order phase  |    |

|      | locked loop.                                                        | 42 |

| 2.32 | Closed loop gain of the 2nd order PLL                               | 44 |

| 2.33 | Linear noise model of the PLL                                       | 44 |

| 2.34 | Noise transfer functions of the 2nd order PLL                       | 45 |

| 2.35 | Total phase noise of the PLL                                        | 46 |

| 3.1  | Conventional injection-locked oscillator model                      | 50 |

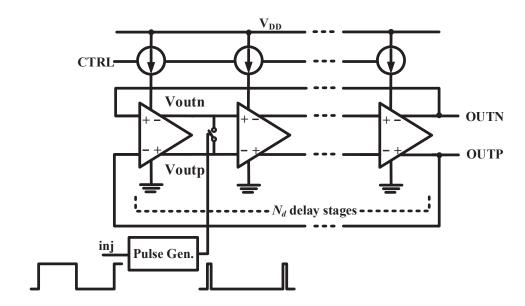

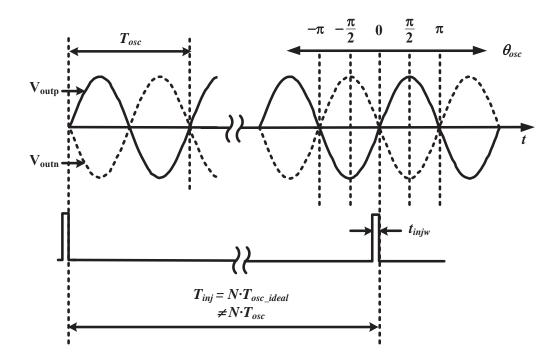

| 3.2  | injection-locked ring oscillator with $N_d$ delay stages            | 51 |

| 3.3  | Relation between the free running and the injection pulse           | 52 |

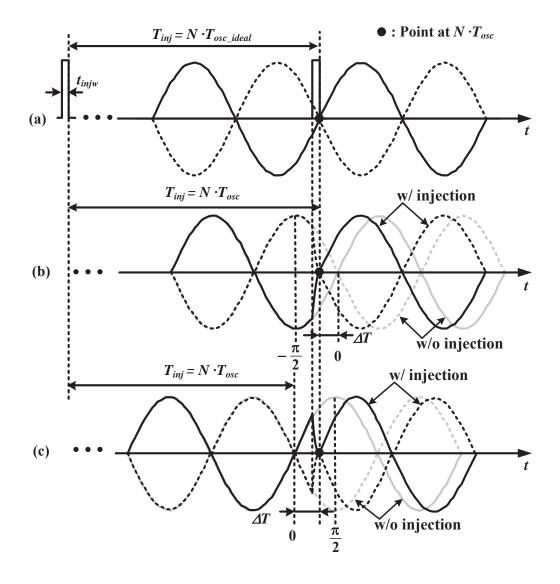

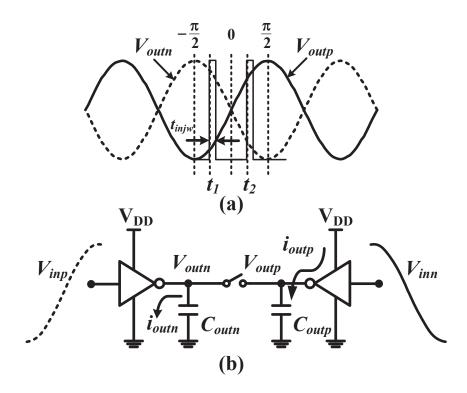

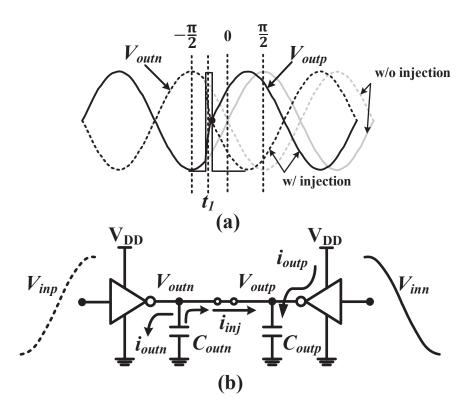

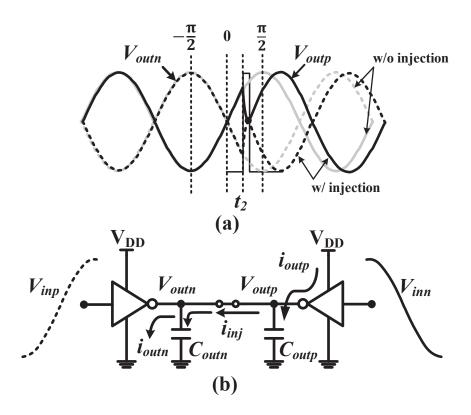

| 3.4  | (a) Noiseless oscillator output and injection pulse (b) differential              |    |

|------|-----------------------------------------------------------------------------------|----|

|      | outputs of the oscillator before and after injection when the pulse               |    |

|      | signal is injected at $-\pi/2 < \phi_{osc} < 0$ of the phase of the oscillator    |    |

|      | (c) differential outputs of the oscillator before and after injection             |    |

|      | when the pulse signal is injected at $0 < \phi_{osc} < \pi/2$ of the phase of     |    |

|      | the oscillator                                                                    | 53 |

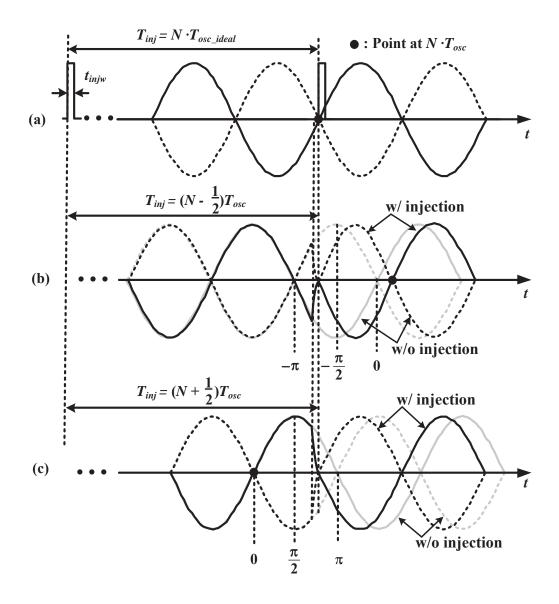

| 3.5  | (a) Noiseless oscillator output and injection pulse (b) differential              |    |

|      | outputs of the oscillator before and after injection when the pulse               |    |

|      | signal is injected at $-\pi < \phi_{osc} < -\pi/2$ of the phase of the oscillator |    |

|      | (c) differential outputs of the oscillator before and after injection             |    |

|      | when the pulse signal is injected at $\pi/2 < \phi_{osc} < \pi$ of the phase      |    |

|      | of the oscillator                                                                 | 55 |

| 3.6  | General current flow in a ring oscillator                                         | 56 |

| 3.7  | Current flow when an injection signal is inputted at $-\pi/2 < \phi_{osc} < 0$ .  | 58 |

| 3.8  | Current flow when an injection signal is inputted at $0 < \phi_{osc} < \pi/2$ .   | 59 |

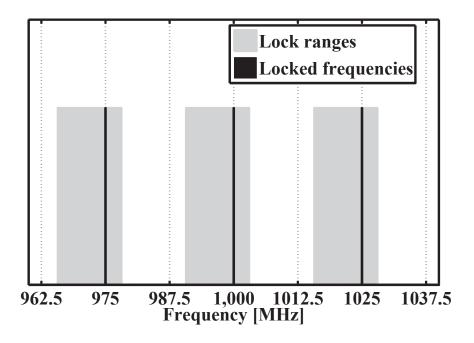

| 3.9  | Simulation results on asymmetric lock ranges and locked frequencies. $$           | 60 |

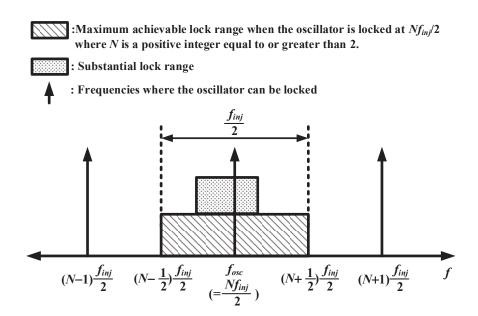

| 3.10 | Ideal lock range of the injection-locked ring oscillator                          | 61 |

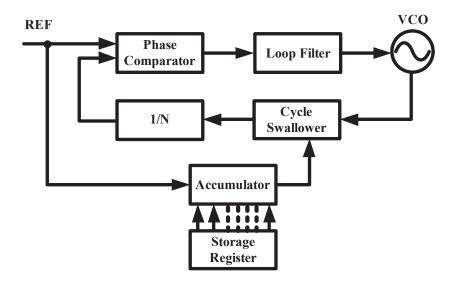

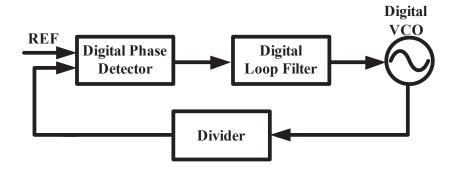

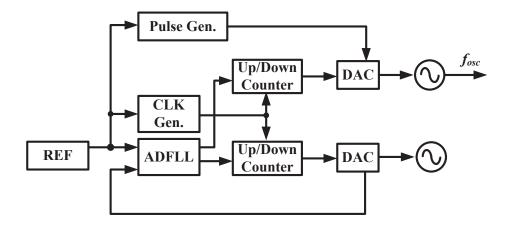

| 4.1  | Fractional-N phase-locked loop                                                    | 64 |

| 4.2  | All digital phase-locked loop                                                     | 65 |

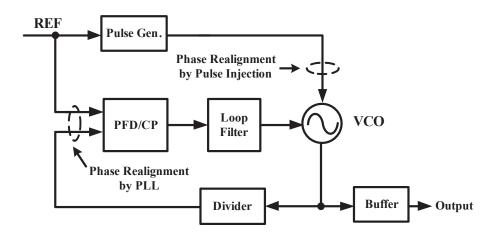

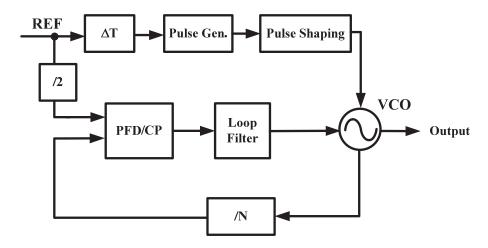

| 4.3  | Phase confliction due to pulse injection in a conventional PLL                    | 66 |

| 4.4  | Injection-locked PLL with a pulse timing control                                  | 66 |

| 4.5  | Injection-locked PLL with self-aligned injection window                           | 67 |

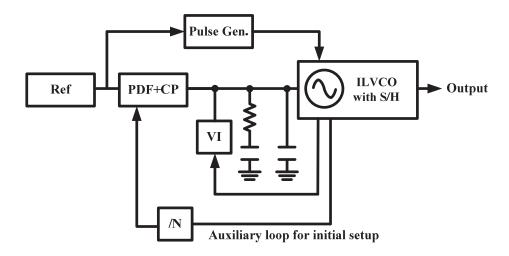

| 4.6  | Phase realignment in a conventional PLL                                           | 68 |

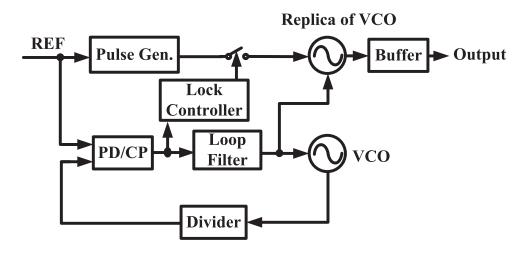

| 4.7  | Proposed injection-locked CPPLL with a replica of the ring oscil-                 |    |

|      | lator                                                                             | 68 |

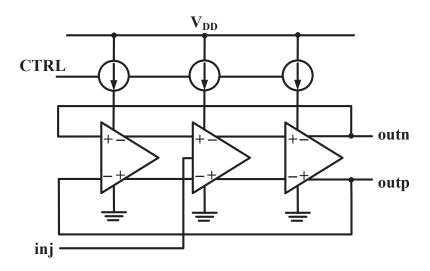

| 4.8  | Block diagram of 3-stage injection-locked ring oscillator                         | 69 |

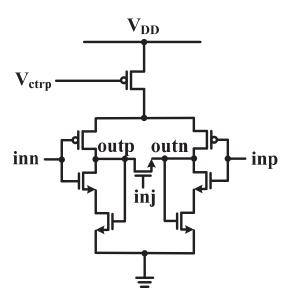

| 4.9  | Delay stage of the injection-locked ring oscillator with one current              |    |

|      | source                                                                            | 70 |

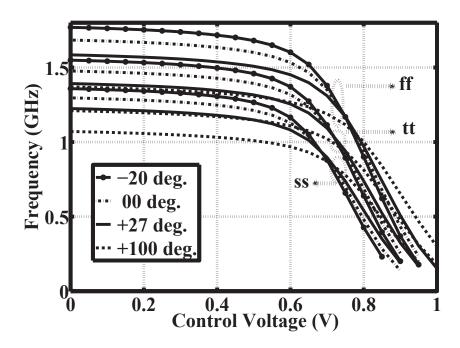

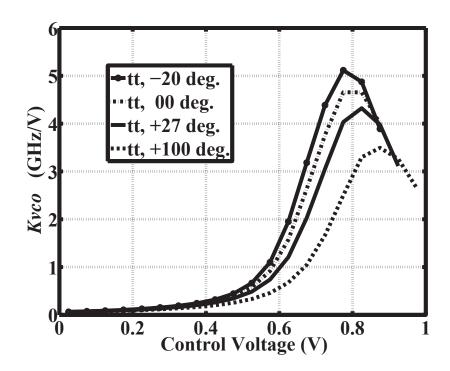

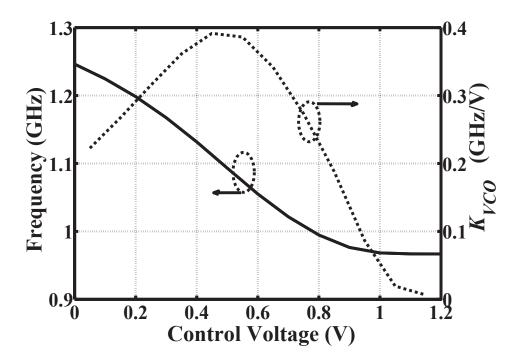

| 4.10 | Tuning ranges of the 3-stage injection-locked ring oscillator. $$                 | 70 |

| 4.11 | Oscillator gain, $K_{VCO}$ , of the 3-stage injection-locked ring oscillator.     | 71 |

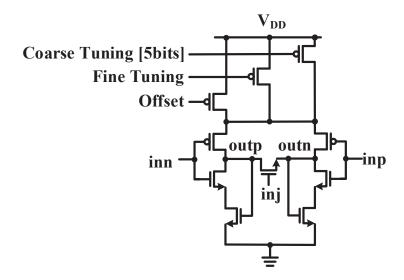

| 4.12 | Delay stage of the injection-locked ring oscillator with multiple                 |    |

|      | current sources                                                                   | 71 |

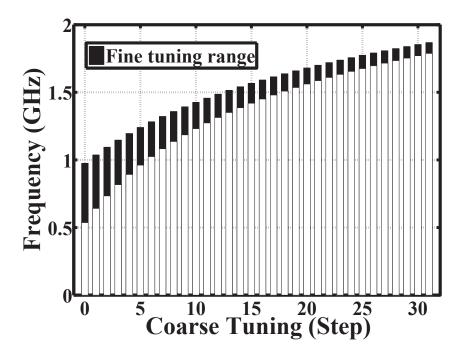

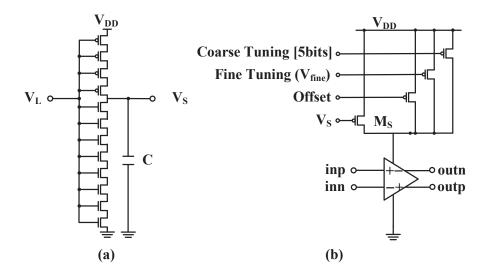

| 4.13 | Coarse tuning and fine tuning ranges of the injection-locked ring                                          |          |

|------|------------------------------------------------------------------------------------------------------------|----------|

|      | oscillator                                                                                                 | 73       |

| 4.14 | Oscillation frequency and oscillator gain over the fine tuning voltage. $$                                 | 74       |

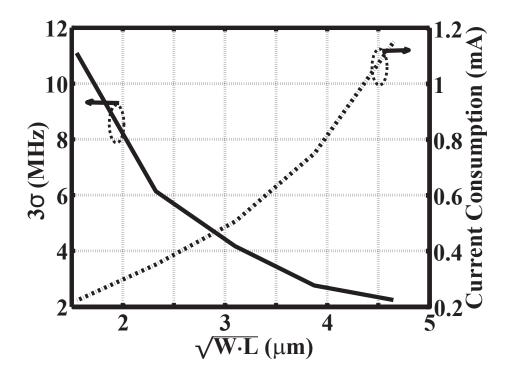

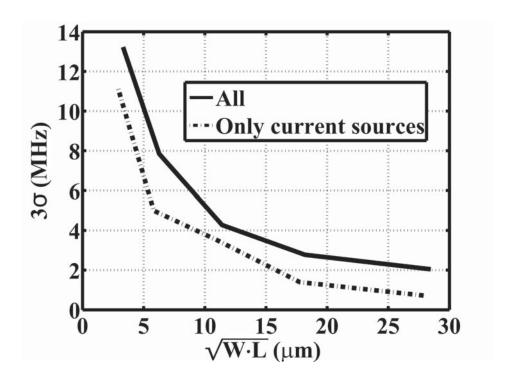

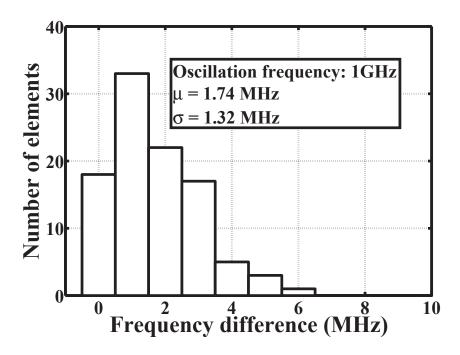

| 4.15 | Monte Carlo simulation results on the frequency variations and                                             |          |

|      | current consumptions with respect to the delay sizes of the oscillator.                                    | 75       |

| 4.16 | Monte Carlo simulation results on the frequency variation with                                             |          |

|      | respect to sizes of the current sources and all components of the                                          |          |

|      | oscillator                                                                                                 | 76       |

| 4.17 | Lock ranges of the injection-locked oscillator with respect to sizes                                       |          |

|      | of switches                                                                                                | 77       |

| 4.18 | Monte Carlo simulation results on the frequency difference be-                                             |          |

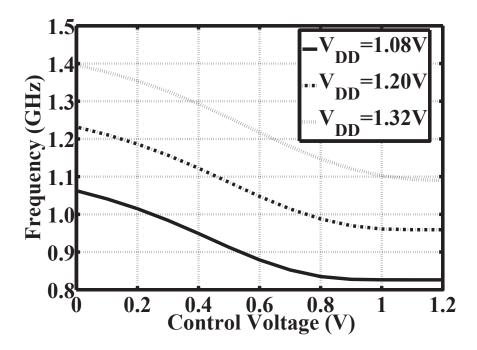

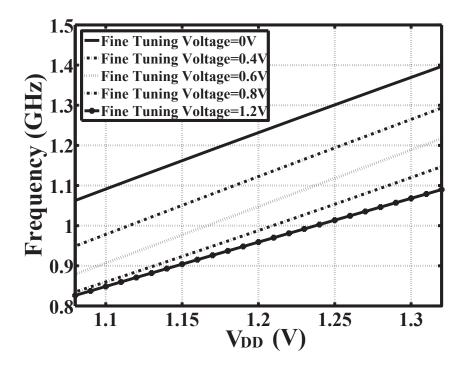

|      | tween the oscillator and its replica due to process variation. $\ . \ .$                                   | 78       |

| 4.19 | Free-running frequencies with respect to supply voltage $(V_{DD})$                                         |          |

|      | variation                                                                                                  | 79       |

| 4.20 | Free-running frequencies with respect to supply voltage $(V_{DD})$                                         |          |

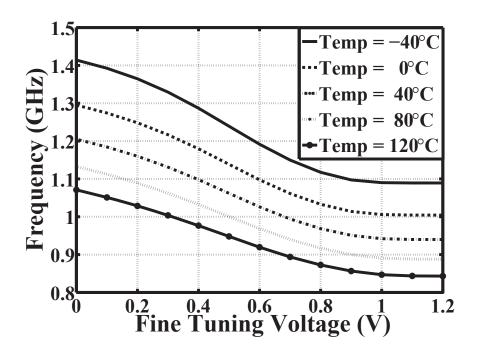

|      | variation                                                                                                  | 80       |

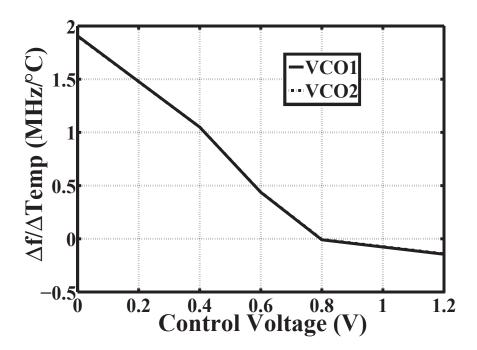

| 4.21 | Oscillation frequency over temperature variation                                                           | 81       |

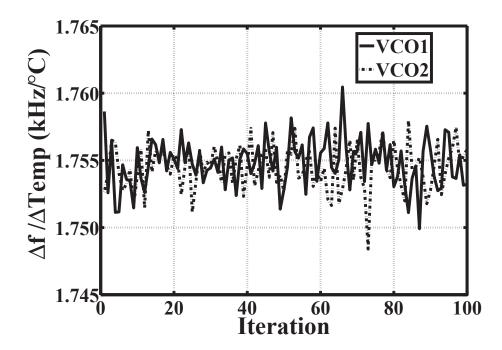

| 4.22 | Frequency-to-temperature ratio of two oscillators in Monte Carlo                                           |          |

|      | simulation                                                                                                 | 82       |

| 4.23 | Difference between average frequency-to-temperature ratio in two                                           |          |

|      | ring oscillators (Monte Carlo simulations)                                                                 | 83       |

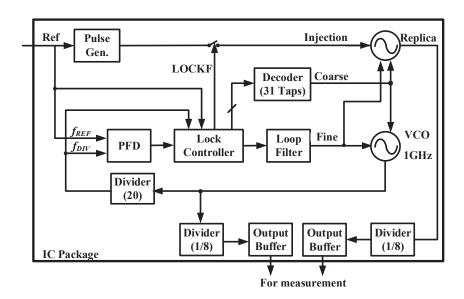

| 4.24 | Proposed injection-locked CPPLL with a replica of the ring oscil-                                          |          |

|      | lator                                                                                                      | 84       |

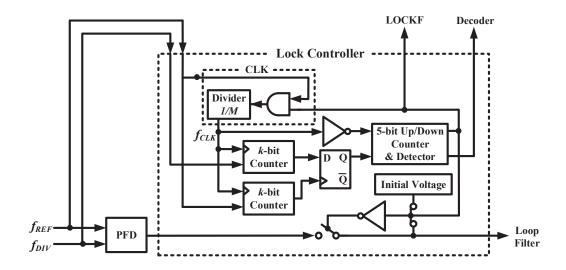

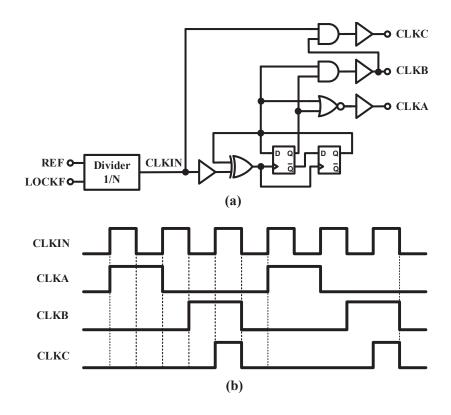

| 4.25 | Block diagram of a lock controller for the coarse tuning                                                   | 84       |

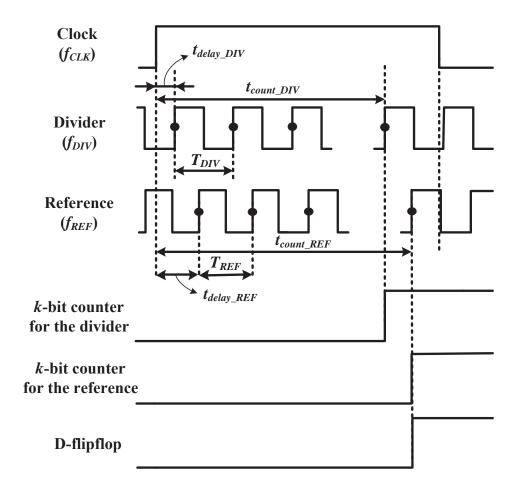

| 4.26 | Timing chart of the signals for coarse tuning                                                              | 86       |

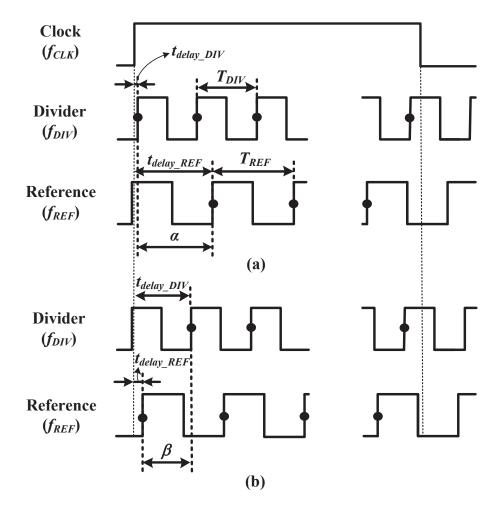

| 4.27 | Delay differences (a) when $t_{delay\_REF} \ge t_{delay\_DIV}$ and (b) $t_{delay\_REF} \le t_{delay\_DIV}$ | <u> </u> |

|      | $t_{delay\_DIV}$                                                                                           | 88       |

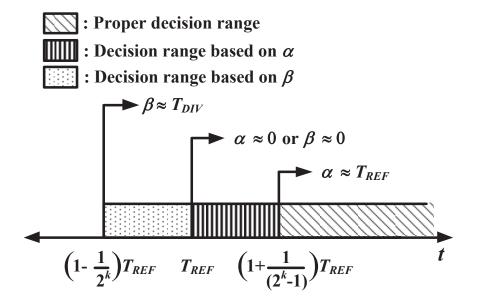

| 4.28 | Decision range in which the period of the reference is decided to                                          |          |

|      | be larger than one of the divider                                                                          | 90       |

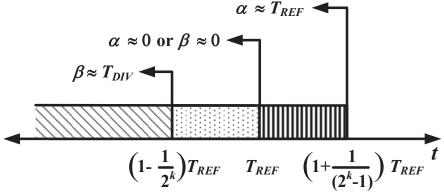

| 4.29 | Decision range in which the period of the reference is decided to                                          |          |

|      | be less than one of the divider                                                                            | 92       |

| 4.30 | Operation of the proposed injection-locked CPPLL for coarse tuning.                                        | 94       |

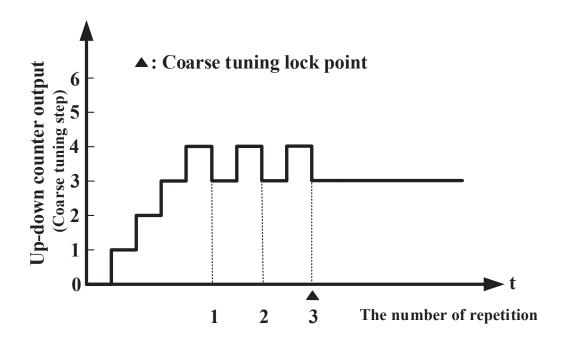

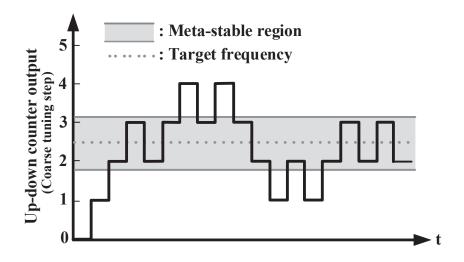

| 4.31 | The output of the up-down counter for coarse tuning                                                        | 95       |

| 4.32 | Operation of the proposed injection-locked CPPLL for fine tuning.                  | 96  |

|------|------------------------------------------------------------------------------------|-----|

| 4.33 | Normal operation of the proposed injection-locked CPPLL                            | 97  |

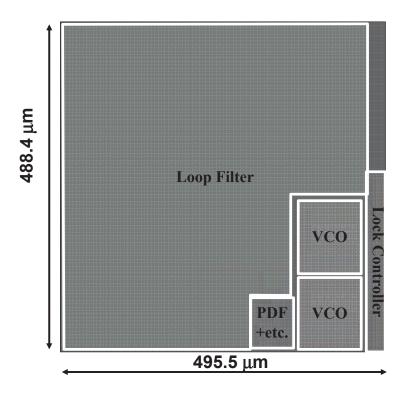

| 4.34 | Layout of the proposed injection-locked CPPLL                                      | 98  |

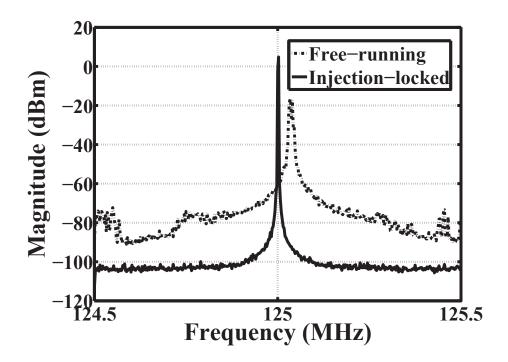

| 4.35 | Measured spectra of the free-running and injection-locked oscilla-                 |     |

|      | tors with (a) resolution bandwidth of 1kHz (b) resolution band-                    |     |

|      | width of 10Hz                                                                      | 99  |

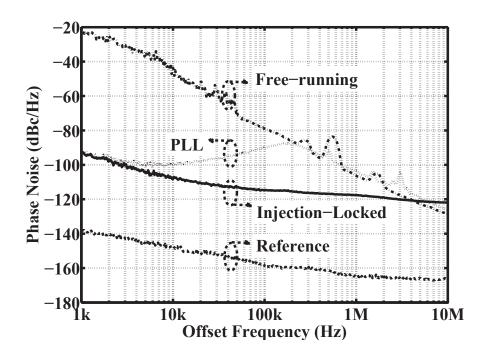

| 4.36 | Measurement phase noises (note that all data except the reference                  |     |

|      | was converted to the phase noise seen at 1GHz)                                     | 101 |

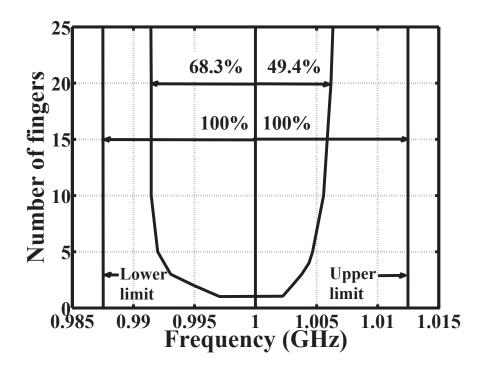

| 5.1  | Wide meta-stable region                                                            | 104 |

| 5.2  | Narrow meta-stable region                                                          | 105 |

| 5.3  | Medium meta-stable region                                                          | 106 |

| 5.4  | Simulation results of the meta-stable detection                                    | 107 |

| 5.5  | Injection-locked PLL with a VT variation compensator                               | 109 |

| 5.6  | Basic concept to turn on or off a current source slowly                            | 110 |

| 5.7  | Liner noise model of the PLL with the noise in the oscillator                      | 111 |

| 5.8  | Calculation results of $\Delta f_{OSC}$                                            | 114 |

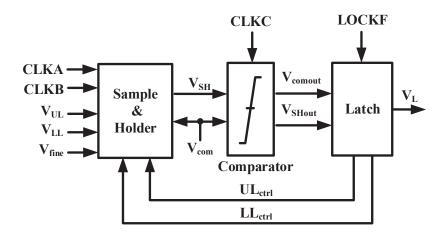

| 5.9  | Block diagram of a VT variation compensator                                        | 115 |

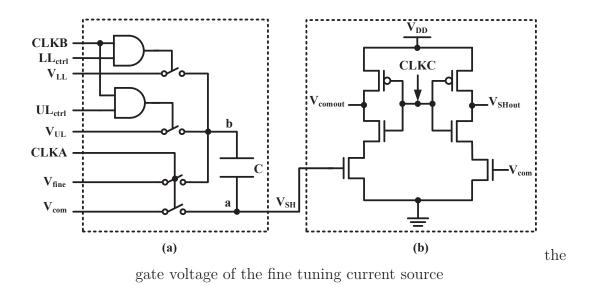

| 5.10 | (a) RC switch and (b) Modified delay stage of the ring oscillator.                 | 116 |

| 5.11 | Clock generator and its waveforms for the limit-voltage detector. $\boldsymbol{.}$ | 117 |

| 5.12 | Limit-voltage detector                                                             | 117 |

| 5.13 | (a) Sample-and-holder and (b) comparator                                           | 118 |

| 5.14 | Comparison between the calculation and the simulation results of                   |     |

|      | $\Delta f_{OSC}$ when the proposed VT variation compensator is used                | 120 |

| 5.15 | Simulation results in the case of without the RC switch. $\ \ldots \ \ldots$       | 121 |

| 5.16 | Simulation results in the case of with the RC switch                               | 122 |

## List of Tables

| 1.1 | Scaling results for circuit performance                              | 2   |

|-----|----------------------------------------------------------------------|-----|

| 4.1 | Metastable range based on the number, $k$ , of bits of the counters. | 93  |

| 4.2 | Performance comparison                                               | 100 |

## Chapter 1

### Introduction

Semiconductor technology has greatly been progressed over the last few decades. It may not be exaggeration that semiconductor technology has also accelerated the development and improvement of other technology and improved many aspects of our lives. Semiconductors allow various electronic devices to be implemented in an integrated chip and to be operated with low power consumption and high speed. These days, the most popular semiconductors would be complementary metal-oxide-semiconductor (CMOS), which is widely used for various systems since it is cheap, small, stable, and less-power hungry.

CMOS is very suitable for digital processing owing to very low static power consumption and also used in analog circuits, such as analog-to-digital converters (ADCs), digital-to-analog converters (DACs), and RF baseband circuits. Moreover, mixed circuits with both analog and digital systems can be implemented by CMOS in the same wafer [1]. Development of CMOS technology has allowed high speed high resolution analog-to-digital converters (ADCs), high performance baseband circuits, high speed digital signal processors, and so on.

In CMOS integrated circuits, most of systems require periodic signals, called system clocks, generally to synchronize internal components or to sample data. The quality of the system clocks critically affects the performance of many systems. For example, noisy clock generators can increase bite error rate of communication systems and reduce signal-to-noise ratio (SNR) in ADCs [2].

The clock generators in most of integrated circuits are implemented by the frequency synthesizers, such as phase-locked loops employing a crystal oscillator as a reference, for high performance and stability [3] [4]. With the development of the CMOS technology, the clock generators have also been required to reduce power consumption and cost while maintain the quality of their performances.

This chapter summarizes the process scaling, also called semiconductor scaling, guiding the CMOS technology development. And it reviews challenges in mixed signal circuits. The motivation of this thesis is also introduced.

#### 1.1 Process Scaling

In 1965, Gordon Moore predicted that the number of components on the IC would be roughly double each year, based on the late 1950's and the early 1960's technologies [5]. He also insisted that the increase of the components results in a cost reduction for components. It was not for the long term but for the next 10 years. However, the trend of the increase of components has been continued for the last few decades [6] - [13]. The increase of components has been mainly achieved by the device scaling. In 1974, the scaling method of the circuit was proposed by Dennard as shown in Table 1.1 [17]. Even though the limit and the future of scaling have been discussed for long time [6]- [16], Iwai expected that the scaling would be continued until the gate length of around 5nm, which is supposed to be the physical limit [13].

Table 1.1: Scaling results for circuit performance

| Device or circuit parameter     | Scaling factor |

|---------------------------------|----------------|

| Device dimension $t_{ox}, L, W$ | $1/\kappa$     |

| Doping concentration $Na$       | $\kappa$       |

| Voltage $V$                     | $1/\kappa$     |

| Current I                       | $1/\kappa$     |

| Capacitance $\epsilon A/t$      | $1/\kappa$     |

| Delay time/circuit $VC/I$       | $1/\kappa$     |

| Power dissipation/circuit $VI$  | $1/\kappa^2$   |

| Power density $VI/A$            | 1              |

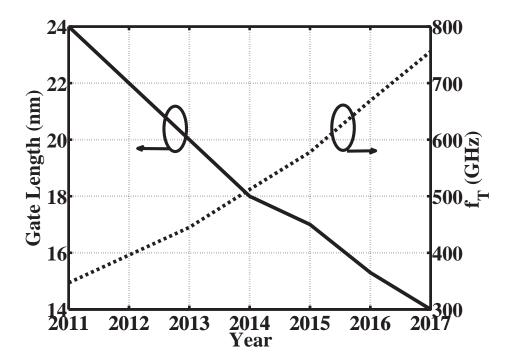

Figure 1.1 shows load map for gate length and cut-off frequency,  $f_T$ , based on the scaling of CMOS processes in ITRS 2011 [21]. CMOS scaling provides

Figure 1.1: ITRS load map for gate length.

digital circuits with a few benefits [8] [18]. When gate length is reduced, gate capacitance,  $C_{GS}$ , is also reduced and its cut-off frequency is increased since it is inversely proportionally to gate capacitance [22].

$$f_T = \frac{gm}{2\pi C_{GS}} \tag{1.1}$$

It allows faster circuits. And chip area decreases such that the cost of the circuit can be reduced and power consumption too.

$$P_{digital} = CV_{DD}^2 f (1.2)$$

Power consumption,  $P_{digital}$ , in digital circuits is also reduced since the power supply voltage,  $V_{DD}$ , has been reduced as well as the reduction of the gate length, even though the rate of the voltage supply reduction is not as large as the rate of the gate length reduction [6].

### 1.2 Analog and Digital Circuits

One of advantages of CMOS process can implement analog and digital circuits in one wafer. In these days, many kinds of communication systems have been implemented together with digital circuits in CMOS process.

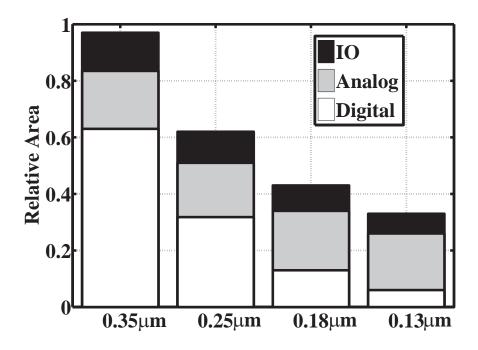

Figure 1.2: Chip area in a system-on-chip (SoC).

As well as digital circuits, the device scaling provides analog circuits with some benefits, such as the reduction of the minimum noise figure of a MOSFET and the improvements of the quality factor of MIM (Metal-Insulator-Metal) capacitor [18]. However, analog circuits do not have benefits from the process scaling as much as digital circuits. The intrinsic gain is reduced and the gap between pre- and post-layout simulation results is widen as the devices are scaled down [19] [20]. Area sharing ratio of analog circuits in a chip becomes larger. Figure 1.2 shows chip area when the mixed signal system-on-chip (SoC) is fabricated in the CMOS process [23]. As the process scaling proceeds, the whole area becomes small but the chip sharing ratio of analog circuits increases since the passive circuits, such

as inductors and capacitors, are hardly scaled down with the process scaling. Especially, inductors require large area.

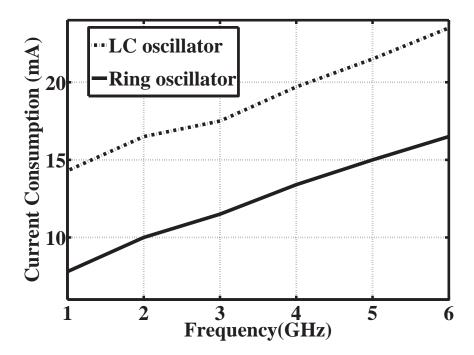

Figure 1.3: Comparison between current consumptions of LC and ring oscillators.

In the view of chip area, performance, and power consumption, there is very big difference between analog circuits with or without inductors. Let us give an example of design of a clock generator. When the clock generators are designed for the system, one of two major types of oscillators is generally selected. One is LC oscillators and the other is ring oscillators. LC oscillators are composed of LC resonant circuit and have low noise characteristic than other oscillators. Ring oscillators have poor noise characteristics such that they are seldom used for the systems requiring high purity oscillation frequency. However, ring oscillators have several advantages compared to LC oscillators. They have wide tuning range, low power consumption, and small occupied area. Figure 1.3 shows comparison of power consumption between the ring oscillator and the LC oscillator fabricated in 90nm CMOS process [24]. Both increase current consumption as the oscillation frequency increases. However, the LC oscillator consume the current about 2.5

times larger than that of the ring oscillator. Power consumption becomes more important in mobile systems using battery.

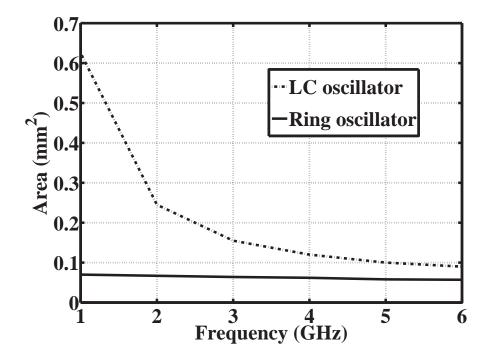

Figure 1.4: Comparison between occupied chip areas of LC and ring oscillators.

Figure 1.4 shows comparison of occupied area between the two oscillators. As the oscillation frequency increases, the occupied area of the LC oscillator decreases while the area of the ring oscillator looks almost same. Since the oscillation frequency of the LC oscillator is inversely proportional to the inductance, the area of the LC oscillator becomes small as the oscillation frequency increases. It is thus considered that LC oscillators will be preferred as high frequency clock generator in fine CMOS process without any restriction of power consumption. In the case of the relatively low oscillation frequency, for example, around 1GHz, it is not easy to select one between ring and LC oscillators. Considering the power consumption, chip area, and tuning range, the ring oscillator is suitable. But the phase noises of the ring oscillators is hard to reach the LC oscillators theoretically [25]. On the other hand, the LC oscillator has better phase noise characteristics but requires large area and has a limited tuning range.

Figure 1.5: Signal-to-noise ratio (SNR) of an ADC due to the clock jitter.

Relatively low frequency clock generators with low phase noise is generally required for analog-to-digital converters (ADCs) and digital-to-analog converters (DACs). Figure 1.5 shows signal-to-noise ratio (SNR) of an ADC due to the clock jitter [26]. When the clock has any timing disturbance during sampling operation of an ADC, it generates error in the sampled data and directly effects performance of the ADC.

Figure 1.6 shows SNR due to the clock jitter in a 7-bit 1Gsps ADC [2]. When the frequency of the input signal is low, the clock jitter seldom affects performance of the ADC. However, when the frequency of the input signal goes higher, the SNR of the ADC goes down rapidly. For input signal with one-half the sampling frequency, the clock jitter should be below 2ps. Thus, the clock jitter is very important factor for the performance of the ADCs and DAC.

Figure 1.6: SNR due to the clock jitter in a 7-bit 1Gsps ADC.

### 1.3 Motivation and Thesis Organization

#### 1.3.1 Motivation

The scaling of CMOS technology allows faster circuits, small chip areas, and low power consumption for many systems. However, not every system requires a high frequency clock as high as the frequencies required in RF circuits. When LC oscillators are implemented as a clock generator with a frequency around 1GHz in a fine CMOS process, very large area and power consumption are accompanied. On the other hand, ring oscillators can not provide good noise characteristics as low as the LC oscillator.

This thesis focuses on the relatively low frequency oscillators with low noise characteristic and small occupied area. Recently, injection-locked oscillators as frequency multipliers are rising again [27] - [32]. Injection-locked oscillators generally have been used to be not frequency multipliers but frequency dividers [33] - [36]. There are two kinds of injection-locked oscillators. One is based on ring

oscillators and the other is LC oscillators. The injection-locked LC oscillators require large area as same as LC oscillators but injection-locked ring oscillators do not. When they are locked, the phase noise of the injection-locked oscillators tend to follow the low phase noise of the reference. However, there are a few challenge in using the injection-locked ring oscillators as a frequency multiplier. First of all, it is difficult to achieve high multiplication ratio. The second is that the lock range is still ambiguous. The third is that it is very weak to the voltage-temperature variations.

Thus, this thesis discusses about a maximum lock range of an injection-locked ring oscillator and an injection-locked charge-pump phase-locked loop to maintain the stable lock state.

#### 1.3.2 Thesis Organization

In chapter 2, fundamentals of oscillators and the phase locked loop are described and the trade-offs in selecting oscillators for the phase-locked loop is discussed. In chapter 3, an ideal lock range of an injection-locked oscillator used as a frequency multiplier is derived. In chapter 4, it is introduced that an injection-locked ring oscillator is embedded in the charge pump phase-locked loop. Chapter 5 describes lock detection technique in a lock controller and how to enhance the tolerance to voltage-temperature variations in the injection-locked phase-locked loop. In chapter 6, a summary of this thesis is presented with the future works.

## Chapter 2

## Phase-Locked Loops

In submicron processes, design of frequency synthesizer in relatively low frequency, for example around 1GHz, looks facile since much more higher frequency synthesizers can be implemented. However, considering some required specifications for the frequency synthesizers, such as power consumption, occupied chip area, and low phase noises, it is difficult and tricky for the designer to handle trade-offs among them. When it is implemented in more fine processes, it becomes more tricky. PLLs are widely used in many systems which requires clock generator since they can provide stable high frequency signal. This chapter describes the noise in the clock generators and clarifies the trade-offs in design of the PLLs after basic concepts of their components are presented.

#### 2.1 Jitter and Phase Noise

All electric systems suffer undesired noises. An ideal clock generator outputs a certain signal waveform with a fixed period or frequency. However, real clock generators provide output signals of which periods or frequencies fluctuate around fixed ones as shown in Fig. 2.1. The clock generator can be an oscillator or a system including the oscillator, such as phase-locked loop. The clock generators with excessive noise will increase the bit error rate in communication systems or malfunction in digital systems. First of all, in order to avoid such undesired conditions, stability of the oscillators must be considered. Stability of the oscillators

Figure 2.1: Free running outputs of (a) an ideal oscillator and (b) a real oscillator, and (c) the output frequencies and (d) phases of the oscillators.

for systems are generally quantified by two means. One is observed in the time domain and the other is in the frequency domain.

The instability of the clock in time domain is called timing jitter. Jitter is specified by statistical terms since it has a random characteristic. Two kinds of timing jitters are widely used. One is a period-jitter and the other is a cycle-to-cycle jitter. A period jitter,  $\Delta T_p$ , as shown in Eq. 2.1 is a change of the period from an ideal period and generally used to calculate timing margin in digital systems [37].

$$\Delta T_p = T_k - T_{ideal} \tag{2.1}$$

Its RMS (root-mean-square),  $\sigma_p$ , is expressed as following:

$$\sigma_p^2 = \lim_{N \to \infty} \frac{1}{N} \sum_{k=1}^N (\Delta T_p)^2 \tag{2.2}$$

Cycle-to-cycle jitter,  $\Delta T_{c2c}$ , is a deviation in the period between two adjacent periods as shown in Eq. 2.3 [38].

$$\Delta T_{c2c} = T_{k+1} - T_k \tag{2.3}$$

The RMS of the cycle-to-cycle error,  $\sigma_{c2c}$ , is

$$\sigma_{c2c}^2 = \lim_{N \to \infty} \frac{1}{N} \sum_{k=1}^{N} (\Delta T_{c2c})^2$$

(2.4)

Figure 2.1 shows the characteristics of a noiseless and a noisy oscillators with sinusoidal waveforms. The ideal oscillator outputs  $Asin(2\pi f_o t)$  but a noisy oscillator does  $Asin(2\pi f_o t + \phi_n)$ .  $\phi_n$  is a noise component called jitter. The change of the transition of the oscillators in the time domain results in fluctuation of the oscillation frequency in the frequency domain as shown in Fig. 2.1(c). Thus, its spectrum looks skirt around the ideal oscillation frequency as shown in Fig. 2.2.  $\phi_n$  is also a noise component to modulate the phase of the oscillator in the frequency domain. Thus, phase noise is used to evaluate the stability of the oscillator in the frequency domain. Phase noise,  $L(\Delta f)$ , is defined as the ratio of the noise power in a 1 Hz bandwidth at a certain frequency offset,  $\Delta f$ , to the signal

Figure 2.2: Definition of phase noise.

power at a carrier frequency,  $f_o$ .

$$L(\Delta f) = 10 log \{ \frac{\text{noise power in a 1 Hz bandwidth at frequency offset}}{\text{power at a carrier frequency}} \} [\text{dBc/Hz}]$$

(2.5)

Phase noise is a very important factor to evaluate the purity of the oscillators or frequency synthesizers since phase locked loop is generally designed in the frequency domain. Figure 2.3 shows the characteristic of the phase noise in the oscillators. In the low offset frequency, the phase noise is inversely proportional to the frequency. Especially, the phase noise with a 30dB/decade slope is associated with the flicker noise which is the dominant noise source at low frequencies in silicon MOSFETs. The flicker noise is expressed by the fluctuation of the channel free carriers due to the random capture emission or the fluctuations in the surface potential. It is mainly dominated in NMOS by carrier-density fluctuation and in PMOS by mobility fluctuation [53]. Thus, it can be roughly modeled as two dominant approaches [52]. The first approach provides a power spectral density  $S_{nf}(f)$ , of the equivalent input noise voltage appearing in series with the gate.

$$S_{nf}(f) = \frac{K}{C_{ox}^{\prime 2}WL} \frac{1}{f} \tag{2.6}$$

Figure 2.3: Phase noise of an oscillator.

where K is process-dependent coefficient,  $C'_{ox}$  oxide capacitance per unit area, and W and L the channel width and length. This equation is suitable for NMOSs since flicker noise of the n-channel devices have independence on the gate bias voltage. Another approach is for PMOSs providing a power spectral density for the equivalent input noise voltage, which depends on the gate bias voltage.

$$S_{nf}(f) = \frac{K(V_{GS})}{C_{ox}'WL} \frac{1}{f}$$

$$(2.7)$$

where K is bias-dependent coefficient. In oscillators, the flicker noise is upconverted to the oscillation frequency and is dominant in  $1/f^3$ , region of phase noise [54].

#### 2.2 Oscillators

In electronic systems, two kinds of oscillators are widely used. One is LC oscillators and the other is ring oscillators. In this section, their characteristics are investigated. Furthermore, injection-locked oscillators are also described. The

injection-locked oscillators are generally used as frequency dividers. A few papers presented that the injection-locked oscillators are used as frequency multipliers.

#### 2.2.1 LC Oscillators

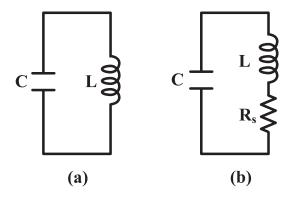

Figure 2.4: (a) Ideal LC resonant tank (b) resonant tank with parasitic resistance.

LC oscillators are a type of the most widely used oscillators in CMOS technology since they have low phase noise characteristic than other oscillators. The LC oscillator is composed of resonant component of inductor and capacitor as shown in Fig. 2.4 [39]. Its resonant frequency depends on inductance and capacitance. Resonant tank has an infinite impedance at the resonant frequency such that the oscillator outputs a periodic signal. The resonant frequency is obtained as following:

$$f = \frac{1}{2\pi\sqrt{LC}}\tag{2.8}$$

Since a real inductor has series parasitic resistance as shown in Fig. 2.4 (b), the real resonant tank composed of only an inductor and a capacitor outputs not a periodic signal but a decaying signal. The series parasitic resistance can be replaced with the parallel parasitic resistance as shown in Fig. 2.5 (a) [40]. The parallel parasitic resistance,  $R_p$ , can be expressed by the series parasitic resistance,  $R_s$ , and the quality factor, Q, of the inductor.

Figure 2.5: (a) Resonant tank with a parallel parasitic resistance (b) resonant tank with a negative resistance.

$$R_p = (Q^2 + 1)R_s$$

where  $Q = \frac{R_p}{X_p}$  (2.9)

where  $X_p$  is a shunt reactance. When negative resistance is connected to the resonant tank in parallel as shown in Fig. 2.5 (b), the resonant tank will recover infinite impedance at the resonant frequency. The negative resistance can be implemented by cross coupled transistors and its value is determined by the transconductance.

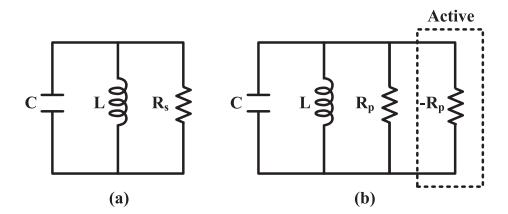

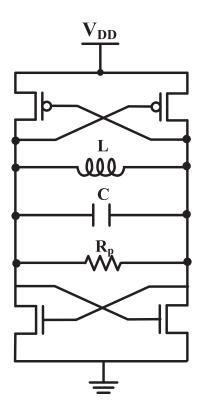

Widely used LC oscillator has cross coupled negative resistance as shown in Fig. 2.6 [41]. It is possible to be implemented only with NMOS or PMOS cross coupled negative resistance. The phase noise spectrum,  $L(\Delta\omega)$ , of the LC oscillator can be expressed as following [42]:

$$L(\Delta\omega) = 10log\left[\frac{2FkT}{P_{sig}}\left\{1 + \left(\frac{\omega_o}{2Q\Delta\omega}\right)^2\right\}\left(1 + \frac{\omega_{1/f^3}}{|\Delta\omega|}\right)\right]$$

(2.10)

where F is fitting factor to account for excess noise in all regions. The phase noise of the LC oscillators mainly depends on the quality factor, Q, of the LC tank and the signal power,  $P_{siq}$ .

Figure 2.6: Complementary LC oscillator.

## 2.2.2 Ring Oscillators

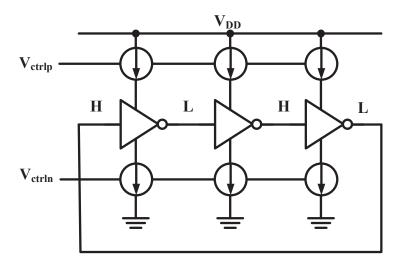

A different type of most widely used oscillators is a ring oscillator since it has less occupied area, wide tuning range, and low power consumption. Figure 2.7 shows a 3-stage inverter-based ring oscillator. Its oscillation frequencies are generally controlled by the current sources, which can be only one between top or bottom ones. Inverter-based ring oscillators are composed of odd-stage inverters. An inverter basically outputs the reversed voltage of its input voltage. As shown in Fig. 2.7, the input of the first stage is high but the output of the third stage is low. When the input of the first stage is connected to the output of third stage, the inverter chain becomes unstable and then oscillates. That is, an unstable state results in a stable oscillation.

The ring oscillator has a very simple structure. However, it is not easy to achieve an accurate oscillation frequency estimation since it has not any resonant

Figure 2.7: Inverter-based ring oscillator.

components unlike LC oscillators. Oscillation of ring oscillators is substantially based on amplification of MOSFETs and RC delays. Since MOSFETs are inherently nonlinear active devices, analyses of them are not facile. However, they can be linearly analyzed under the restricted condition called small signal analysis, which the gate bias is fixed and the input and output signals are very small enough to be linearized. However, ring oscillators have large input and output signals, generally from ground to the supply voltage, called full swing. The small signal analysis is not useful for analysis of the ring oscillator. Moreover, they change in time. In other words, ring oscillators are a nonlinear and time variant system. Thus, accurate analysis of them is quite tricky.

The oscillation frequency estimation of the ring oscillator is mainly performed by two approaches. The first approach is to use charging and discharging mechanism of a capacitor. A simple circuit model of the inverter is shown in Fig. 2.8 [43]. The load capacitor,  $C_L$ , is parasitic capacitor at the output of the inverter stage. An additional capacitance can be also loaded at the output node. The current,  $I_{ctrl}$ , is controlled by the control voltages,  $V_{ctrlp}$  and  $V_{ctrln}$ , which are gate bias voltages of the NMOS or PMOS used to be current sources. When the capacitor is charged as shown in Fig. 2.8 (b), the current,  $I_{ctrlp}$ , is as following:

Figure 2.8: (a) Delay stage of the inverter-based ring oscillator, and a simple circuit model to estimate (b) rising and (c) falling delays.

$$I_{ctrlp} = \frac{\mu_p C_{oxp}}{2} \frac{W_p}{L_p} (V_{ctrlp} - V_{thp})^2$$

(2.11)

where  $V_{thp}$  is a threshold voltage of the PMOS,  $\mu_p$  is a mobility of a carrier,  $C_{oxp}$  is an oxide capacitance, and  $W_p$  and  $L_p$  are the channel width and length, respectively. Thus, the rising time,  $t_r$ , is  $C_L V_{DD}/I_{ctrlp}$  and can be rewritten as following:

$$t_r = C_L V_{DD} \frac{2L_p}{W_p \mu_p C_{oxp}} \frac{1}{(V_{DD} - V_{thp})^2}$$

(2.12)

When the capacitor is discharged as shown in Fig. 2.8(c), the falling time,  $t_f$ , can be also obtained by the same method. Thus, the oscillation frequency.  $f_{OSC}$ , of a N-stage ring oscillator can be estimated as following:

$$f_{OSC} = \frac{1}{N(t_r + t_f)} \tag{2.13}$$

Figure 2.9: Linear model of the ring oscillator.

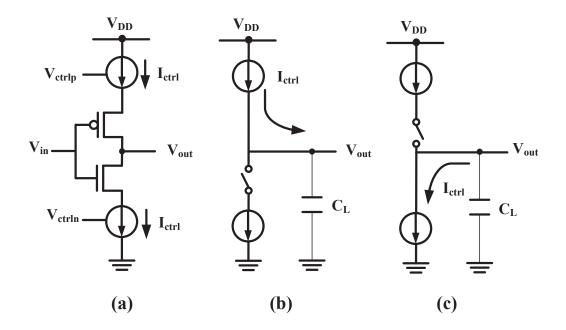

The other approach for the oscillation frequency estimation is to linearize a delay cell with Gm cell and RC load in the case of a 3-stage differential ring oscillator [44]. Figure 2.9 shows a linear model of the ring oscillator. The oscillation frequency of a 3-stage ring oscillator is as following:

$$f_{OSC} = \frac{\sqrt{3}}{2\pi RC} \tag{2.14}$$

The oscillation frequency can be also estimated by considering currents in the delay stage and time-varying characteristics of parasitics and the gate resistance [45], or by analyzing a ring oscillator as a nonlinear feedback system [46].

Phase noises of the inverter-based ring oscillator were introduced in [25]. They were modeled by producing a voltage ramp at its output in response to a correctly positioned step input. The phase noises,  $L_{ring,1/f}(f)$  and  $L_{ring,white}(f)$ , due to flicker and white noises, are respectively

$$L_{ring,1/f}(f) = \frac{C'_{ox}}{8MI} \left(\frac{\mu_N K_{fN}}{L_N^2} + \frac{\mu_P K_{fP}}{L_P^2}\right) \frac{f_o^2}{f^3}$$

(2.15)

$$L_{ring,white}(f) = \frac{2kT}{I} (\frac{1}{V_{DD} - V_t} (\gamma_N + \gamma_P) + \frac{1}{V_{DD}}) (\frac{f_{OSC}}{f})^2$$

(2.16)

where I is a pull-up current charging an inverter's load C to  $V_{DD}$ ,  $\mu_N$  and  $\mu_N$  are carrier mobilities of NMOS and PMOS respectively,  $K_{fN}$  is the empirical coefficient,  $K_{fP}$  is a bias-dependent quality,  $f_o$  is oscillation frequency,  $V_t$  is the

threshold voltage, and  $\gamma_N$  and  $\gamma_P$  are noise factors of NMOS and PMOS, respectively. These equations show that the low phase noise can be obtained by the longest channel length and the larger current consumption.

Figure 2.10: (a) Delay line with only one noisy stage and (b) waveforms of the delay line.

Another phase noise model can be derived from phase noise of a delay line multiplying a shaping function [47]. Figure 2.10 shows three-stage delay line with

only one noisy inverter and node voltages at each output. Under a certain input frequency, the output voltage of the latter stage has more large noise since it suffers all uncorrelated noises of the previous stages. Homayoun obtained the two-sided phase noise,  $S_{\Phi,DL}$ , of the delay line from uncorrelated jitters on the rising and falling edges and derived the phase noise. Homayoun's approach is to obtain the phase noise of the delay line with only one noisy stage and the overall phase noise of the delay line by multiplying the phase noise of the one noisy stage with the number of delay stages. The two-sided phase noise,  $S_{\Phi,white,DL}$ , due to white noise and the two-sided phase noise,  $S_{\Phi,1/f,DL}$ , due to 1/f noise in N-delay line are respectively

$$S_{\Phi,white,DL} = \frac{\pi^2}{2I_D^2} [S_I(f)|_{NMOS} + S_I(f)|_{PMOS}] + \frac{2kT\pi^2}{I_D V_{DD}}$$

(2.17)

$$S_{\Phi,1/f,DL} = \frac{\pi^2}{4NI_D^2} \left[ S_{1/f}(f)|_{NMOS} + S_{1/f}(f)|_{PMOS} \right]$$

(2.18)

where  $S_I(f)$  is the thermal noise current,  $S_{1/f}(f)$  is the flicker noise current, k is the Boltzmann constant, T is the absolute temperature,  $I_D$  is the drain current of the on-transistor, and  $V_{DD}$  is the supply voltage.

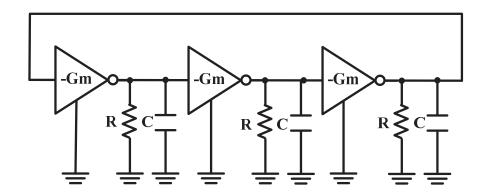

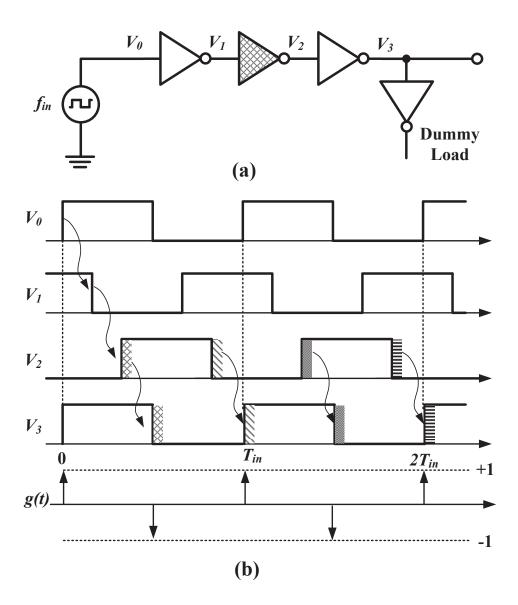

Homayoun's model for the phase noise of the ring oscillator also assumed that the only second stage inverter has noise. And it investigated the effect on the output of the stage as shown in Fig. 2.11. Contrary to the delay stage, the ring oscillator accumulates the previous jitters as shown in Fig. 2.11 (b). The output waveform was thus obtained by convoluting the noise sources with g(t)and adding it to an ideal wave. The phase noise,  $S_{\Phi,ring}$ , of the ring oscillator shown in Fig. 2.11 (a) was obtained by multiplying the phase noise of the delay line with the shaping function, G(f).

$$S_{\Phi,ring}(\Delta f) = S_{\Phi,DL}(\Delta f)|G(f)|^2 \qquad (2.19)$$

$$= \left( S_{\Phi,white,DL} + S_{\Phi,1/f,DL} \right) \left( \frac{f_{osc}}{\pi \Delta f} \right)^2 \tag{2.20}$$

Figure 2.11: (a) Ring oscillator with only one noisy stage and (b) waveforms of the ring oscillator.

This equation can be rewritten as follows

$$S_{\Phi,ring}(\Delta f) = \frac{f_{osc}^2}{\Delta f^2} \left\{ \frac{1}{2I_D^2} \left[ S_I(\Delta f)|_{NMOS} + S_I(\Delta f)|_{PMOS} \right] + \frac{2kT}{I_D V_{DD}} \right\} + \frac{f_{osc}^2}{4NI_D^2 \Delta f^2} \frac{1}{2I_D^2} \left[ S_{1/f}(\Delta f)|_{NMOS} + S_{1/f}(\Delta f)|_{PMOS} \right]$$

(2.21)

Equation 2.21 shows that the phase noise due to white noise in the ring oscillator is inversely proportional to the drain current of the on-transistor and the supply voltage. And the phase noise due to flicker noise is inversely proportional to the number of the delay stages and the drain current of the on-transistor. The number of the delay stages is inversely proportional to the oscillation frequency. When the oscillation frequency is predetermined and the current consumption is fixed, the phase noise due to flicker noise mainly depends on the flicker noise current, which relies on area of the MOSs and the process characteristics. Thus, Homayoun's model also shows that the phase noise of the ring oscillator mainly depends on the current consumption under the same supply voltage and oscillation frequency. It gives the same design insight as Abidi's model.

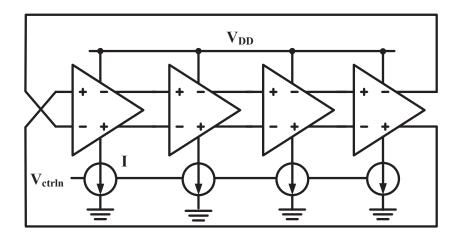

Figure 2.12: 4-stage differential ring oscillator.

Another popular topology in ring oscillators is a differential type as shown in Figure 2.12. While the inverter-based ring oscillators must have odd stages, the differential ring oscillators can have odd or even stages. The oscillation frequency in differential ring oscillators can be also estimated by the above methods.

Ring oscillators can be implemented with small chip area and low power consumption, but they have generally poor phase noise since they do not have any resonant components unlike LC oscillators. The phase noises,  $L_{1/f}(f)$  and  $L_{white}(f)$ , due to flicker and white noises in a differential ring oscillator were introduced in [25].

$$L_{1/f}(f) = A \frac{K_f}{WLC'_{ox}f} \left(\frac{1}{V_{efft}^2}\right) \frac{f_o^2}{f^3}$$

(2.22)

$$L_{white}(f) = \frac{2kT}{Iln2} \left\{ \gamma \left( \frac{3/4}{V_{effd}} + \frac{1}{V_{efft}} \right) + \frac{1}{V_{op}} \right\} \left( \frac{f_{OSC}}{f} \right)^2$$

(2.23)

where  $K_f$  is the empirical coefficient, I is the tail current,  $V_{effd}$  is the effective gate voltage on the differential pair,  $V_{efft}$  is the effective gate voltage in the tail current source, and  $V_{op}$  is a differential peak output voltage swing, Comparison between the phase noises of the ring and LC oscillator in [25] shows that the ring oscillator takes takes 450 times large current compared with that of the LC oscillator in order to achieve the same phase noise. That is why LC oscillators are mostly used in applications requiring low phase noise.

#### 2.2.3 Injection-Locked Oscillators

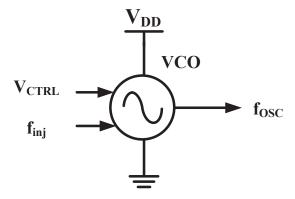

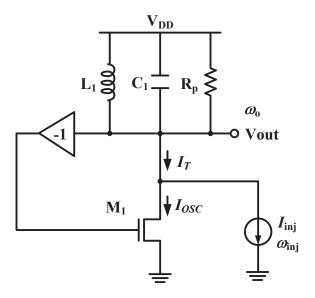

Figure 2.13: Concept of an injection-locked oscillator.

Basic concept of an injection-locked ring oscillator is shown in Fig. 2.13. The injection-locked oscillator is composed of a voltage-controlled oscillator and an external signal source. Let's consider that the oscillator outputs a signal with a frequency,  $f_{OSC}$ , which is controlled by a voltage,  $V_{CTRL}$ . Then, when the external signal with a frequency,  $f_{inj}$  is inputted to the oscillator and the oscillator is locked by the external signal, the output of the oscillator is realigned every period of the injection signal. The injection signal can be sinusoidal or pulse shaped signals.

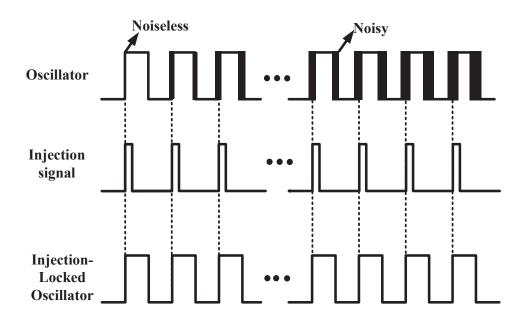

Figure 2.14 shows waveforms in an injection-locked oscillator when the injection signal and the oscillator have the same frequency. In noisy oscillator, the

Figure 2.14: Waveforms in an injection-locked oscillator.

output waveform fluctuates from an ideal waveform. When time goes by, the deviation from the ideal waveform may increase due to noises. However, if the injection signal has lower phase noise than the oscillator, the waveform of the oscillator will realign at the injection signal every injection period and the phase noise of the oscillator approaches the one of the injection signal. The injection oscillators are generally used as a frequency divider, called the injection-locked frequency divider, and especially preferred for high frequencies, which the digital dividers can not cover [48]- [50].

The phase noise of the injection-locked frequency divider is mainly determined by the phase noise of the injection signal.

$$L_{ILFD} \approx L_{inj} - 20log(N) \tag{2.24}$$

where  $L_{ILFD}$  is the phase noise of the injection-locked frequency divider,  $L_{inj}$  is the phase noise of the injection signal, and N is the division ratio. The injection-locked frequency dividers can be based on LC or ring oscillators. LC-based injection-locked oscillators have better noise performance the ring-based

but suffer narrower locking range and unwanted harmonics.

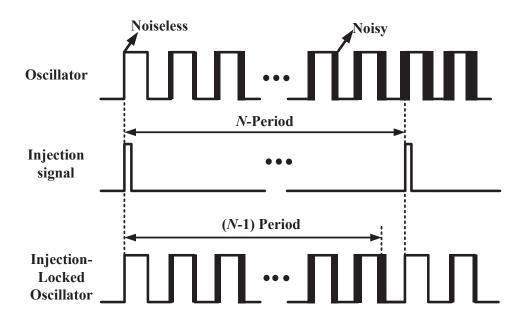

Figure 2.15: Waveforms in an injection-locked oscillator.

The injection-locked oscillators can be also used as frequency multipliers. Figure 2.15 shows waveforms in an injection-locked oscillator when the frequency of the injection signal is higher than the oscillator. When the ratio between two frequencies is small, the phase noise of the oscillator is closer to the phase noise of the injection signal and the lock state is more stable. However, when the ratio becomes larger, it is getting hard for the oscillator to be locked by the injection signal since the deviation from the ideal waveform may increased due to the noises generated by the oscillator itself during non-injected periods.

When the oscillator is locked by the injection signal, the phase noise of the oscillator tends to follow the phase noise of the injection signal. When the frequency of the injection signal is N-times higher than the oscillator, the phase noise,  $L_{OSC}$  of the oscillator as following:

$$L_{OSC} \approx L_{inj} + 20log(N) + \alpha \tag{2.25}$$

where  $\alpha$  is noise of the oscillator during (N-1) periods. When the frequency

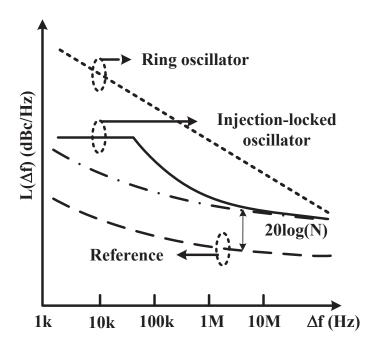

Figure 2.16: Phase noise in the injection-locked ring oscillators as a frequency multiplier.

of the injection signal is N-times lower than the oscillator, the phase noise,  $L_{OSC}$  of the oscillator becomes as shown in Fig. 2.16. At the low offset frequency, the phase noise of the oscillator is a little bit higher than  $L_{inj} + 20log(N)$  and at the high offset frequency, the phase noise of the oscillator becomes  $L_{inj} + 20log(N)$ . In CMOS technology, it is substantially difficult to secure the stable lock state due to quite narrow lock range, process variations, and poor modeling [51].

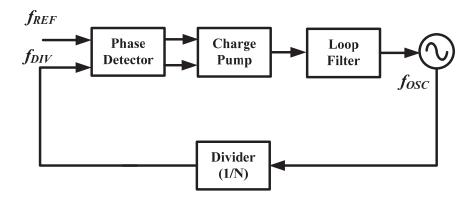

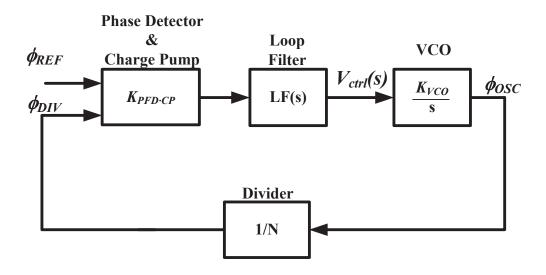

# 2.3 Phase-Locked Loops

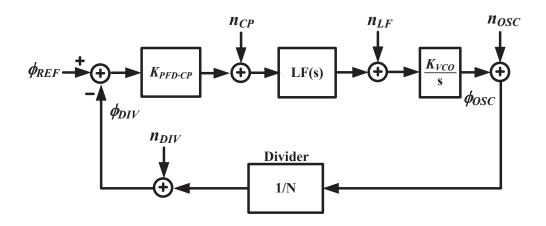

In many CMOS VLSI systems, the clock generators do not consist of only oscillators since the generated signal can have quite poor and unstable performance. Thus, the clock generators are generally composed of a system including the oscillators, such as PLLs. Simple block diagram of charge-pump PLLs is shown in Fig. 2.17. Charge pump PLLs are most widely used for clock generators since they have good stability and reasonable phase noise characteristics.

Figure 2.17: Block diagram of a charge-pump PLL.

The charge-pump PLLs are composed of a voltage-controlled oscillator, a frequency divider, phase-frequency detector, a charge-pump, and a loop filter. The voltage-controlled oscillator is controlled by a voltage, which is proportional to the frequency of its output signal. The frequency divider divides the frequency of its input signal to output the frequency-divided signal. Then the output of the divider has the same frequency to the reference. The crystal oscillators are frequently used as the reference since they have low phase noise and high stability. The phase-frequency detector detects the frequency or phase difference between two input signals, the reference signal and the output of divider, and outputs the indicating signal whether the phase of the output of the divider leads or lags the phase of the reference. The charge-pump converts the pulse width of its input signals to current. This current is a high frequency signal and then is filtered in the loop filter. The loop filter is actually a low pass filter and is a very important component to secure the stability of the feedback loop. The output of the loop filter is inputted to the oscillator and the frequency of the oscillator is thus controlled by the phase difference with the reference.

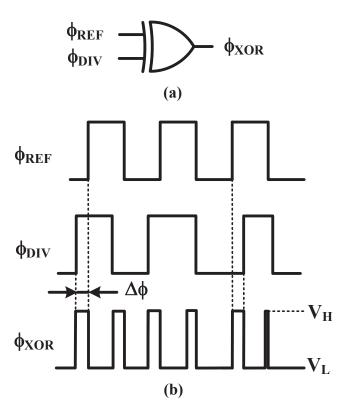

#### 2.3.1 Phase Detector

A simple phase detector can be implemented by an exclusive-OR gate as shown in Fig. 2.18. It outputs high when the two inputs are different with each other.

Figure 2.18: (a) Exclusive-OR phase detector (b) input an output signals of the exclusive-OR gate.

Thus, its average output has the same value when the phase difference. The transfer function of the phase detector is called the gain of the phase detector and defined as following:

$$K_{PD} = \frac{V_{mean}}{\Delta \Phi} [V/rad] \tag{2.26}$$

where  $V_{mean}$  is the mean of the output voltage and  $\Delta\Phi$  is the phase difference. The phase detector of the exclusive-OR has the following phase gain:

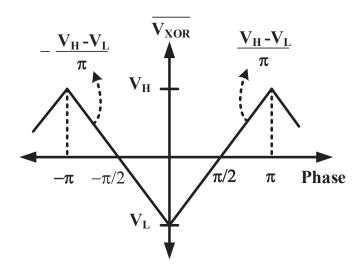

Figure 2.19: The gain of the exclusive-OR gate.

$$K_{PD} = \frac{V_H - V_L}{\pi} \text{ for } -\pi < \Delta \phi < 0$$

$$= -\frac{V_H - V_L}{\pi} \text{ for } 0 < \Delta \phi < \pi$$

(2.27)

$$= -\frac{V_H - V_L}{\pi} \text{ for } 0 < \Delta \phi < \pi$$

(2.28)

The stable lock happens at the phase difference of  $-\pi/2$  or  $\pi/2$ . Thus, only the range of  $\pi$  is usable. The gain with the same sign in positive and negative phase differences may lose the lock.

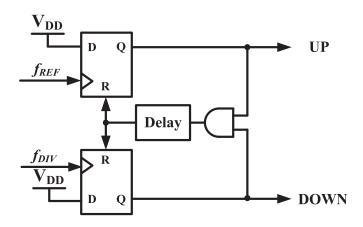

These kinds of problem can be solved by a tristate phase-frequency detector. It is composed of two D-flipflop and an AND gate as shown in Fig. 2.20. It outputs two kinds of signals, UP and DOWN. When the reference leads the output of the divider, the phase frequency detector outputs UP first and then when the output of the divider is high, the down signal is outputted and the phase-frequency detector is reset. The phase-frequency detector has three states, that is, up, down, and zero. Zero state is not substantially zero. As shown in Fig. 2.21, the phase-frequency detector outputs up and down at the same time when the two inputs are the same phase. The pulse width,  $PW_{min}$ , in this case

Figure 2.20: Tristate phase-frequency detector.

Figure 2.21: Input an output signals of the tristate phase-frequency detector.

is determined by delay of the AND gate, D-flipflop, and delay block. Without the delay stage, the phase-frequency detector outputs a very narrow pulse when two inputs has almost zero phase difference. it can not properly operate the next stage of the charge pump and results in dead zone. The deadzone will increase phase noise. The problem can be solved by inserting the delay stage. The delay stage increases minimum pulse width to properly operate the next stage.

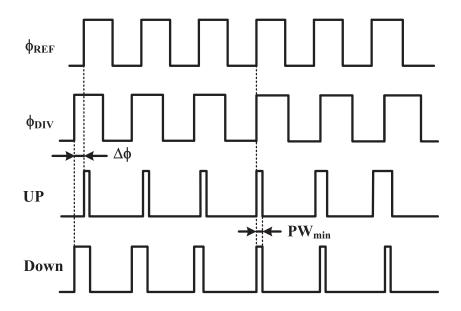

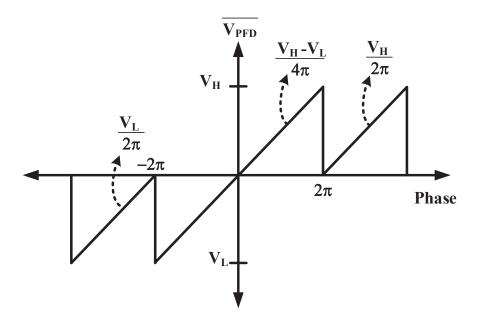

Figure 2.22: Gain of the tristate phase-frequency detector.

The transfer function of the phase-frequency detector is shown in Fig. 2.22. Its linear phase detection range is  $4\pi$ , which is four times wider than that of the exclusive-OR.

$$K_{PFD} = \frac{V_H - V_L}{4\pi} \text{ for } -2\pi < \Delta\phi < 2\pi$$

(2.29)

=  $\frac{1}{2\pi} \text{ when } V_H = 1 \text{ and } V_L = -1$

$$=\frac{1}{2\pi} \text{ when } V_H = 1 \text{ and } V_L = -1$$

(2.30)

The gains with different signs in positive and negative phase differences allow frequency detection and stable lock happens zero phase difference.

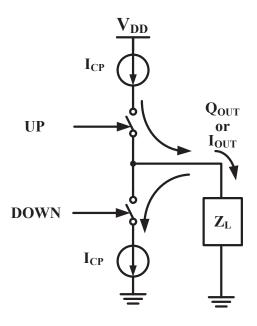

Figure 2.23: Charge pump.

## 2.3.2 Charge Pump

The charge pump is a kind of a converter converting digital error pulse to analog current. Figure 2.23 shows a simple block diagram of the charge pump. The UP and DOWN signals switch on or off the current source, respectively. When UP is high, the current,  $I_{CP}$  flows in the load and when DOWN is high, the current flow out of the load. Thus, the transfer function of the charge pump is  $I_{CP}[A/V]$ . This simple concept does not provide relation between the phase error and the output of the charge pump. When both the phase-frequency detector and the charge pump is considered at the same time, the relation between them can be provided and the combine gain of them also obtained.

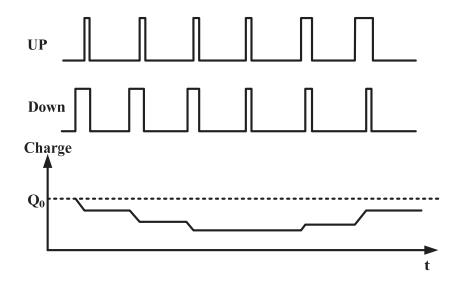

The charge pump convert the output of the phase-frequency detector to charge, which is proportional to the pulse width of the output. When the current source outputs constant current,  $I_{CP}$ , the UP and DOWN switch on or off the current source for the pulse width,  $PW_{UP}$  and  $PW_{DOWN}$ . Thus, charge,  $Q_{CP}$ , flows in or out of the load,  $Z_L$ . Figure 2.24 shows the input and output signals

Figure 2.24: Input and output signals of the charge pump.

of the charge pump.  $Q_0$  is an initial charge in the capacitor. Thus, the output charge,  $Q_{OUT}$ , due to the phase difference,  $\Delta \phi$ , is as following:

$$Q_{OUT} = \frac{I_{CP}\Delta\phi}{2\pi f_{REF}}[C] \tag{2.31}$$

The output charge can be average by the period and converted to the average output current,  $I_{OUTmean}$ .

$$\frac{Q_{OUT}}{T_{REF}} = \frac{I_{CP}\Delta\phi}{2\pi f_{REF}} \cdot T_{REF} \left[ \frac{C}{s} \right]$$

(2.32)

This equation can be written as following:

$$I_{OUTmean} = \frac{I_{CP}\Delta\phi}{2\pi}[A] \tag{2.33}$$

Thus, the combine gain,  $K_{PDF\cdot CP}$  with the phase-frequency detector in Eq. 2.30 and the charge pump is obtained as following [55]:

$$K_{PDF\cdot CP} = \frac{I_{OUTmean}}{\Delta \phi} = \frac{I_{CP}}{2\pi} \left[ \frac{A}{rad} \right]$$

(2.34)

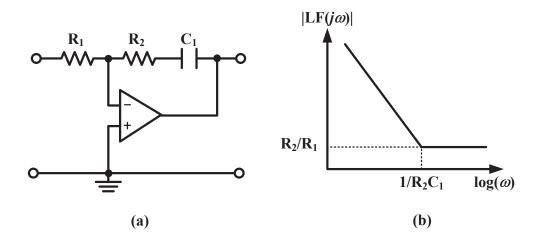

#### 2.3.3 Loop Filter

Figure 2.25: Active proportional-integral loop filter.

The loop filter integrates the output current of the charge pump and outputs the averaged voltage. The main purpose of the loop filter is to establish the dynamics of the feedback loop and to secure a suitable control of the oscillator [56]. The loop filter can be implemented by active or passive elements, which are called active loop filters and passive filter, respectively. Figure 2.25 shows an active proportional-Integral (PI) loop filter. Its transfer function is as following:

$$|LF_{PI}(s)| = \frac{sC_1R_2 + 1}{sC_1R_1} \tag{2.35}$$

The active PI loop filter has a pole at 0 Hz and a zero at  $1/(C_1R_2)$ Hz. Thus, it has a large open loop gain at low frequency. While higher order active filters can filter out of the noise, they has still a few of drawback. The linearity and open loop gain of the active filter limits the frequency gain of the loop. And the noise of the active filter can increase the phase noise of the PLL.

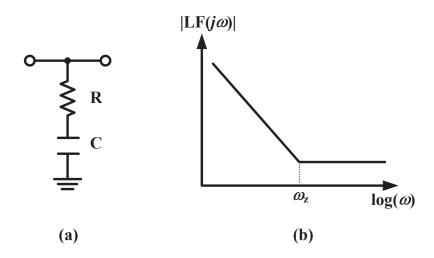

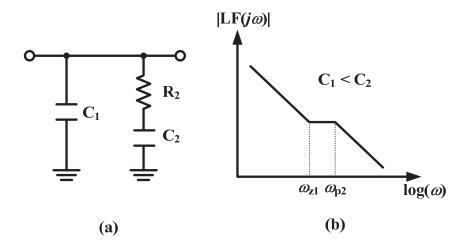

The most simple passive loop filter is shown in Fig. 2.26. Its transfer function is as following:

$$|LF_{P1st}(s)| = R + \frac{1}{sC}$$

(2.36)

Figure 2.26: Passive 1st order loop filter.

Figure 2.27: Passive 2nd order loop filter.

The passive 1st-order loop filter can track the signal more quickly than higherorder loop filter. But this has critical drawback which the control voltage experiences discrete steps due to abrupt changes in the charge pump current. This ripple can be mitigated by adding an additive capacitor to the 1-st-order loop filter. Then, the loop filter becomes 2nd-order shown in Fig 2.27. It has the following transfer function:

$$|LF_{P2nd}(s)| = \frac{sC_2R_2 + 1}{s^2C_1C_2R_2 + s(C_1 + C_2)}$$

(2.37)

If k is larger than unity and  $C_2$  is k times larger than  $C_1$ , then the transfer function can be rewritten as following:

$$|LF_{P2nd}(s)| = \frac{skC_1R_2 + 1}{s(k+1)C_1\{skC_1R_2/(k+1) + 1\}}$$

(2.38)

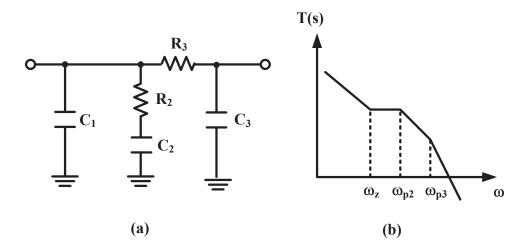

Figure 2.28: Passive 3rd order loop filter.

In order to further suppress reference spurs and high frequency noise, another pole can be added in the loop filter as shown in Fig. 2.28. Higher-order loop filters can be also implemented. However, they are seldom used in practice since it is hard to obtain the phase margin for stability. The 2nd and 3rd order loop filters are mostly preferred.

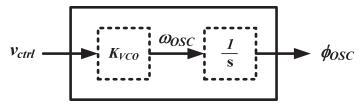

# 2.3.4 Voltage Controlled Oscillator

The output of a voltage controlled oscillator such as LC and ring oscillators has an inherent frequency sensitivity over control voltage. It is called an oscillator gain,  $K_{VCO}$ , defined as following:

#### Voltage-controlled oscillator

Figure 2.29: Transfer function of the voltage-controlled oscillator.

$$K_{VCO} = \frac{\omega_2 - \omega_1}{v_{ctrl2} - v_{ctrl1}} \left[ \frac{radHz}{V} \right]$$

(2.39)

Thus, the angular frequency,  $\omega_{OSC}(t)$ , is

$$\omega_{OSC}(t) = K_{VCO}v_{ctrl}(t) \tag{2.40}$$

Thus output phase of the oscillator,  $\phi_{OSC}(t)$ , is

$$\phi_{OSC}(t) = K_{VCO} \int v_{ctrl}(t)dt \qquad (2.41)$$

In the phase-locked loop, the transfer function of the oscillator is obtained by taking the Laplace transform to the phase of the oscillator output.

$$\frac{\Phi_{OSC}(s)}{V_{ctrl}(s)} = \frac{K_{VCO}}{s} \tag{2.42}$$

Thus, an ideal voltage-controlled oscillator is an integrator.

### 2.3.5 Loop Transfer Functions

The linear model of the phase-locked loop can be expressed as shown in Fig. 2.30. The loop characteristics of the phase-locked loop can be considered by the linear model. The forward-loop transfer function, T(s), is as following:

$$T(s) = \frac{\phi_{OSC}}{\phi_{REF}} = \frac{K_{PDF \cdot CP} \cdot LF(s) \cdot K_{VCO}}{s}$$

(2.43)

Figure 2.30: Linear model of the phase-locked loop.

The order of the phase locked loop is defined by the number of poles in the open loop transfer function. When the passive 1st order loop filter is adapted, the phase-locked loop is the 2nd order. Its forward transfer function becomes as following:

$$T(s) = \frac{I_{CP}}{2\pi} \cdot \frac{K_{VCO}}{s} \frac{(sCR+1)}{sC}$$

(2.44)

The open-loop transfer function has two poles at 0 rad/sec and one zero at  $\omega_{z1} = 1/(CR)$ . The crossover frequency,  $\omega_c$ , of the forward loop transfer function is obtained by the following equation.

$$|T(j\omega)| = \frac{I_{CP}}{2\pi} \cdot \frac{K_{VCO}\sqrt{\omega_c^2 C^2 R^2 + 1}}{\omega_c^2 C^2} = 1$$

(2.45)

Assume that  $\omega_c^2 C^2 R^2 >> 1$ , then the crossover frequency,  $\omega_c$ , is

$$\omega_c = \frac{I_{CP} K_{VCO} R}{2\pi C} \tag{2.46}$$

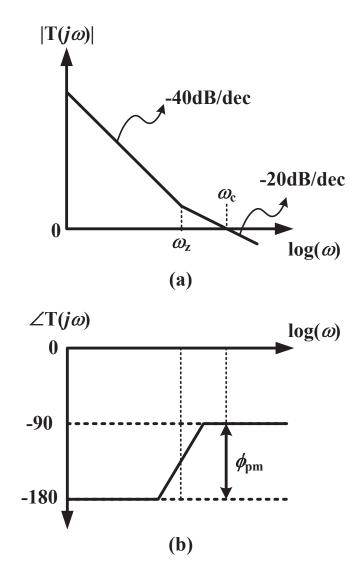

Figure 2.31 shows the open-loop response of the 2nd order phase locked loop. Its closed-loop transfer function, is expressed as following:

Figure 2.31: (a) Forward-loop response and (b) its phase of the 2nd order phase locked loop.

$$H(s) = \frac{\phi_{OSC}}{\phi_{REF}} = \frac{K_{PDF\cdot CP} \cdot LF(s) \cdot K_{VCO}/s}{1 + K_{PDF\cdot CP} \cdot LF(s) \cdot K_{VCO}/(N \cdot s)}$$

$$= \frac{N(sCR + 1)}{2\pi CNs^2/(I_{CP}K_{VCO}) + sCR + 1}$$

(2.47)

And its denominator can be expressed by the 2nd-order equation.

$$2\pi CNs^2/(I_{CP}K_{VCO}) + sCR + 1 = K(s^2 + 2\xi\omega_n s + \omega_n^2)$$

(2.48)

Thus, the natural frequency,  $\omega_n$ , the damping factor,  $\xi$ , and the constant, K, are extracted from the denominator.

$$\omega_n = \sqrt{\frac{I_{CP}K_{VCO}}{2\pi CN}} \tag{2.49}$$

$$\xi = \frac{R}{2} \sqrt{\frac{I_{CP} K_{VCO} C}{2\pi N}} \tag{2.50}$$

$$K = \omega_n^2 \tag{2.51}$$

Thus, the crossover frequency of the forward loop transfer function can be rewritten in terms with the natural frequency.

$$\omega_c = \frac{N}{R}\omega_n^2 \tag{2.52}$$

When the zero of the closed loop transfer function is  $\omega_z = 1/RC = \omega_z/(2\xi)$ , the closed loop transfer function can be expressed as following:

$$H(s) = \frac{N(s2\xi/\omega_n + 1)}{\omega_n^2(s^2 + 2\xi\omega_n s + \omega_n^2)}$$

(2.53)

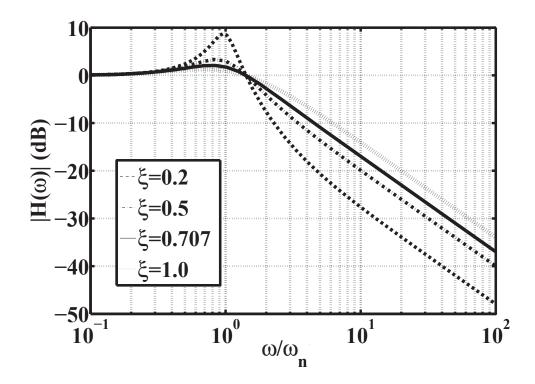

The closed loop gain of the 2nd order PLL is shown in Fig. 2.32. The overshoot in the frequency response results in the overshoot in the step response in the time domain. Thus, the damping factor is generally selected to be  $1/\sqrt{2}$ . The most important function of the PLL is noise filtering. The open-loop transfer function, G(s), is

$$G(s) = NT(s) = \omega_n^2 \frac{(s2\xi/\omega_n + 1)}{s^2}$$

(2.54)

Figure 2.33 shows the linear noise model of the PLL. Transfer function from each noise source to output phase can be obtained by the open loop transfer function. For example, transfer function,  $N_{OSC}(s)$ , of the noise source from the

Figure 2.32: Closed loop gain of the 2nd order PLL.

Figure 2.33: Linear noise model of the PLL.

oscillator is 1/(1+G(s)). Thus, the noise transfer functions from each noise source are as following:

Figure 2.34: Noise transfer functions of the 2nd order PLL.

$$N_{OSC}(s) = \frac{\Phi_{OSC}(s)}{n_{OSC}(s)} = \frac{s^2}{s^2 + 2\xi\omega_n s + 1}$$

(2.55)

$$N_{DIV}(s) = \frac{\Phi_{OSC}(s)}{n_{DIV}(s)} = \frac{-N(s2\xi/\omega_n + 1)}{\omega_n^2(s^2 + 2\xi\omega_n s + \omega_n^2)}$$

(2.56)

$$N_{LF}(s) = \frac{\Phi_{OSC}(s)}{n_{LF}(S)} = \frac{sK_{VCO}}{s^2 + 2\xi\omega_n s + 1}$$

(2.57)

$$N_{PDFCP}(s) = \frac{\Phi_{OSC}(s)}{n_{PDFCP}(s)} = \frac{N(s2\xi/\omega_n + 1)}{K_{PDFCP}\omega_n^2(s^2 + 2\xi\omega_n s + \omega_n^2)}$$

(2.58)

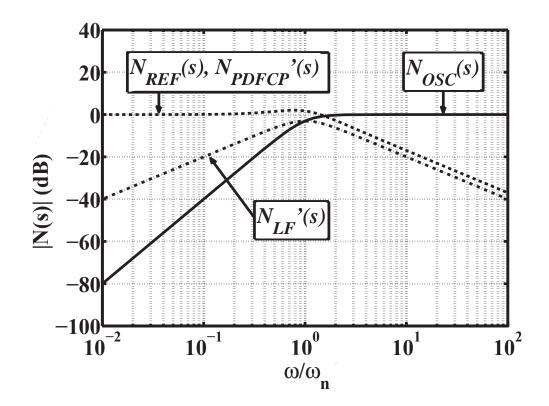

The noise transfer functions of the 2nd order PLL are shown in Fig. 2.34.  $N'_{LF}(s)$  and  $N'_{PDFCP}(s)$  are transfer functions normalized by gains of  $N_{LF}(s)$  and  $N_{PDFCP}(s)$ , respectively. The noise transfer functions of the noises generated at

the reference, the phase frequency detector and charge pump have characteristic of a low pass filter. And the noise transfer function of the noises generated at the loop filter has characteristic of a bandpass filter. Especially, noise transfer function of the noise generated at the oscillator has high pass filter and then noises with high power around the oscillation frequency can be filtered out. Thus, large loop bandwidth can block much larger noises from the oscillator but increases inband noise from the reference, the phase frequency detector, and the charge pump. The loop bandwidth,  $f_{LB}$ , is generally selected by balancing the noises such that the output noise can be minimized.

Figure 2.35: Total phase noise of the PLL.

Figure 2.35 shows the total phase noise of the PLL. The output noise mainly depends on the noises of the oscillator and the reference. For lower phase noise, LC oscillators are preferred but are accompanied with large power consumption and chip area, and narrow tuning range. For wide tuning range and low power consumption, ring oscillators are preferred but also accompanied with poor phase

noise and large chip area for loop filter due to high frequency sensitivity of the ring oscillator. For the PLL around 1GHz, the PLL with the ring oscillator has smaller area since area of the LC oscillator itself requires large area about  $500 \times 500 \mu \text{m}^2$  [58], but the phase noise is inferior than the PLL with a LC oscillator.

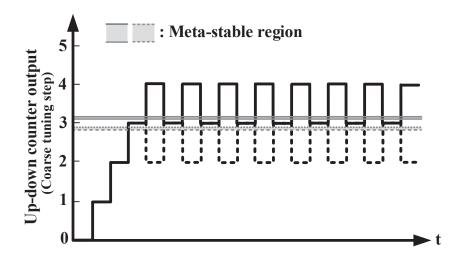

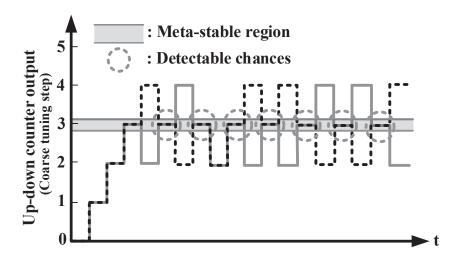

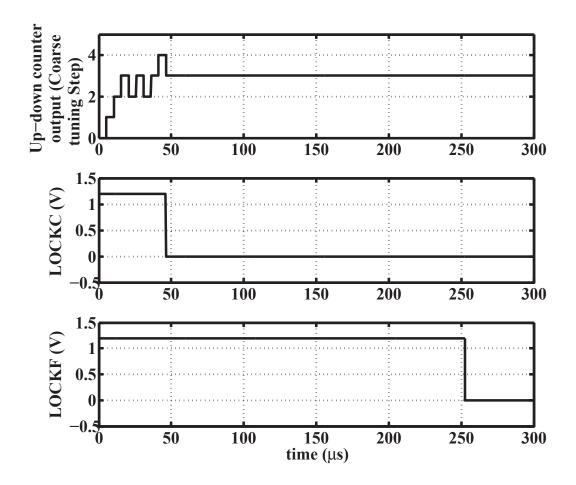

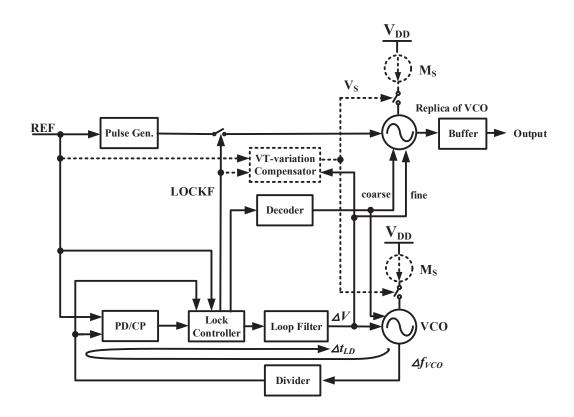

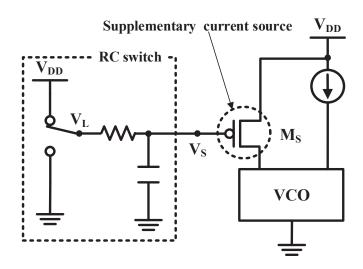

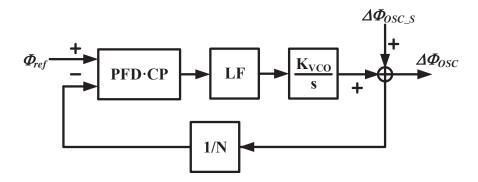

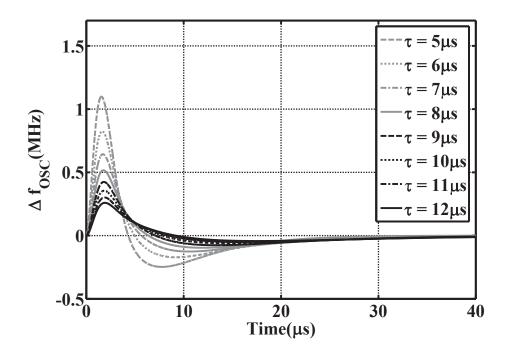

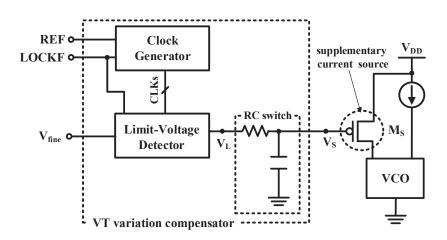

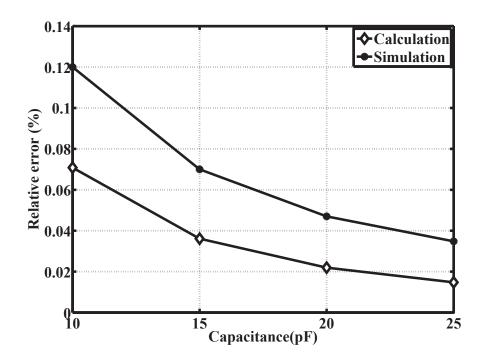

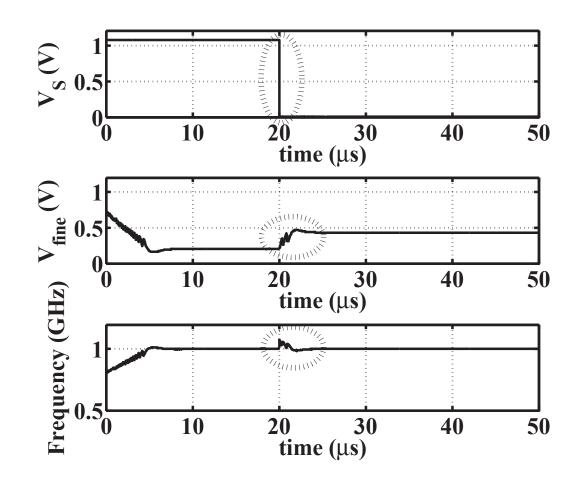

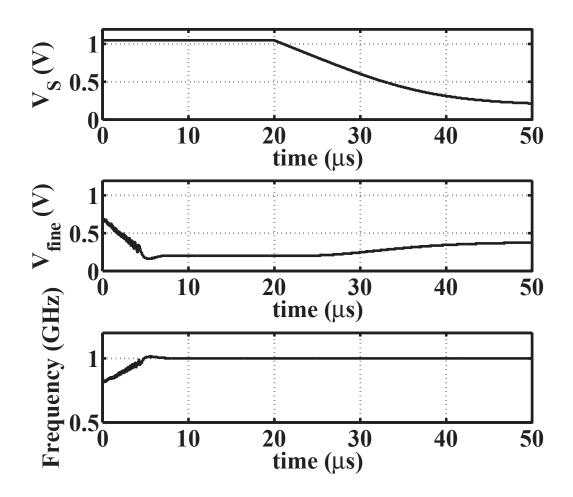

# 2.4 Summary