## T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

## 論文 / 著書情報 Article / Book Information

| 題目(和文)            | SiC MOSFET用の希土類ゲート絶縁膜に関する研究                                                                                                                                                                    |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Title(English)    | A Study on Rare Earth Gate Dielectrics for SiC MOSFET                                                                                                                                          |  |  |

| 著者(和文)            | 宋禛漢                                                                                                                                                                                            |  |  |

| Author(English)   | Jinhan Song                                                                                                                                                                                    |  |  |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第11929号,<br>授与年月日:2021年3月26日,<br>学位の種別:課程博士,<br>審査員:角嶋 邦之,筒井 一生,若林 整,渡辺 正裕,飯野 裕明,岩井 洋,喜多<br>浩之                                                           |  |  |

| Citation(English) | ion(English)  Degree:Doctor (Engineering), Conferring organization: Tokyo Institute of Technology, Report number:甲第11929号, Conferred date:2021/3/26, Degree Type:Course doctor, Examiner:,,,,, |  |  |

| 学位種別(和文)          | 博士論文<br>                                                                                                                                                                                       |  |  |

| Type(English)     | Doctoral Thesis                                                                                                                                                                                |  |  |

## **Doctoral thesis**

# A Study on Rare Earth Gate Dielectrics for SiC MOSFET

Supervisor

Assoc. Prof. Kuniyuki Kakushima

Department of Electrical and Electronic Engineering,

School of Engineering,

Tokyo Institute of Technology, Japan

March 2021

Jinhan Song

## **Abstract**

Silicon carbide (SiC) is a promising candidate for high efficiency power device application. However, SiC metal-oxide-semiconductor field-effect transistor (MOSFET) using thermally grown silicon dioxide (SiO<sub>2</sub>) as gate dielectrics suffer from degraded mobility as well as the reliability issues in threshold voltage ( $V_{th}$ ). Various process technologies have been proposed to recover the degraded mobility so far. However, the negative shift in the  $V_{th}$  was enhanced by these processes. Insertion of rare earth oxide gate dielectrics has been reported to achieve both high mobility as well as high  $V_{th}$  at the same time. As the basic mechanism is not fully understood, further research on rare earth oxide gate dielectrics for SiC power devices is mandatory.

As the thermally grown interface structure seems to be origin of the degradation in mobility and the negative shift in the  $V_{th}$ , complete inhibition of the surface SiC oxidation or different surface SiC oxidizing process might be used to solve the problem. Therefore, in this study, as rare earth materials, yttrium-silicate (Y-silicate) and cerium oxide (CeO<sub>x</sub>) dielectrics for SiC metal-oxide-semiconductor (MOS) capacitors and MOS field-effect transistors (MOSFET) have been investigated based on physical and electrical analyses. Coating with Y-silicate is known to protect the SiC surface from oxidation, thus preserving the initial surface after gate stack formation. On the other hand, CeO<sub>x</sub> is known to oxidize the surface by means of radical oxygen species, expecting different type of interface structure.

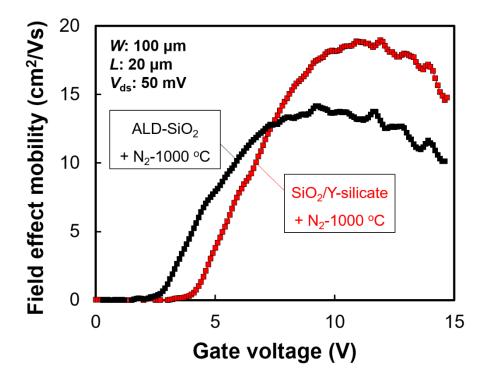

A thermal stability of the Y-silicate interface layer with a thickness of 0.6 nm has been confirmed at  $1000^{\circ}$ C annealing. A lower interface state density ( $D_{it}$ ) is lower, and a higher peak mobility of  $19 \text{ cm}^2/\text{Vs}$  with a high  $V_{th}$  of 4.2 V has been obtained compared to a

deposited-SiO<sub>2</sub> with the same process. Although limited improvements were obtained, initial surface treatment might further enhance the properties.

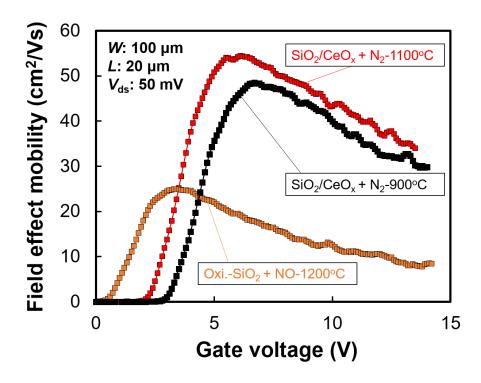

On the other hand,  $CeO_x$  interface layer has showed its thermal stability up to  $1100^{\circ}C$  process temperature. A high peak mobility of 54 cm<sup>2</sup>/Vs with a  $V_{th}$  of 2.3 V has been obtained with the  $CeO_x$  interface layer, both higher than high-temperature NO-processed MOSFETs. Although there exists hysteresis in the gate voltage swing, the interface formation by means of  $CeO_x$  layer might be the key to forming the interface structure.

By stacking the rare earth gate dielectrics, namely  $CeO_x/Y$ -silicate or Y-silicate/ $CeO_x$ , a slight degraded mobility compared to  $CeO_x$  interface layer was obtained. However, the  $V_{th}$  showed a higher value, keeping the role of both gate dielectrics.

In conclusion, the effect of rare earth oxide interface layers for gate dielectric on SiC to the mobility and the  $V_{th}$  has been experimentally investigated. Suppression of the surface SiC oxidation by Y-silicate layer leads to the suppression of the negative shift in  $V_{th}$  with slight mobility recovery. CeO<sub>x</sub> interface layer improves the mobility over 50 cm<sup>2</sup>/Vs with suppression of negative  $V_{th}$  shift. The obtained results give insights and guideline to the interface formation structure for SiC MOSFET processes.

## Contents

| Chapter 1 Introduction                                        |    |  |

|---------------------------------------------------------------|----|--|

| 1.1 Introduction of SiC semiconductors and device application |    |  |

| 1.2 Issues in SiC devices                                     | 7  |  |

| 1.2.1 Electron mobility degradation                           | 7  |  |

| 1.2.2 Negative threshold voltage shift                        | 11 |  |

| 1.3 Material selection for interface layer                    | 15 |  |

| 1.3.1 Inhibition of surface oxidation                         | 15 |  |

| 1.3.2 Surface oxidation by radical oxygen atoms               | 16 |  |

| 1.4 Purpose of this study                                     | 17 |  |

| Reference                                                     | 18 |  |

|                                                               |    |  |

| Chapter 2 Fabrication and characterization methods            | 23 |  |

| 2.1 Experiment procedure                                      | 23 |  |

| 2.1.1 Surface cleaning                                        | 23 |  |

| 2.1.2 Atomic layer deposition (ALD)                           | 23 |  |

| 2.1.3 Post-deposition annealing (PDA)                         | 24 |  |

| 2.1.4 RF magnetron sputtering                                 | 25 |  |

| 2.1.5 Photolithography                                        | 26 |  |

| 2.1.6 Reactive ion etching (RIE)                              | 27 |  |

| 2.1.7 Post-metallization annealing (PMA)                      | 28 |  |

| 2.2 Device fabrication                                        | 29 |  |

| 2.2.1 Fabrication procedure for <i>n</i> -MOS capacitors      | 29 |  |

| 2.2.2 Fabrication procedure for <i>n</i> -MOSFETs             | 31 |  |

| 2.3 Characterization method                                                                                      |    |  |  |  |

|------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| 2.3.1 Capacitance-Voltage (C-V) measurement                                                                      | 32 |  |  |  |

| 2.3.2 Interface state density ( $D_{it}$ ) by conductance method                                                 | 33 |  |  |  |

| 2.3.3 Pulse measurement for $I_d$ - $V_g$ characteristics                                                        | 35 |  |  |  |

| 2.3.4 Effective channel length extraction                                                                        | 36 |  |  |  |

| 2.3.5 Field effect mobility extraction                                                                           | 37 |  |  |  |

| 2.3.6 X-ray photoelectron spectroscopy (XPS)                                                                     | 38 |  |  |  |

| 2.3.7 Transmission electron microscope (TEM)                                                                     | 39 |  |  |  |

| Reference                                                                                                        | 41 |  |  |  |

| Chapter 3 Atomic layer deposition by Ar multiple boost injection                                                 | 43 |  |  |  |

| 3.1 Deposition with low vapor pressure precursors: Y <sub>2</sub> O <sub>3</sub> and CeO <sub>x</sub> film cases | 44 |  |  |  |

| 3.2 A proposal of Ar-boosted multi-shot process                                                                  | 47 |  |  |  |

| 3.3 Film coverage by the number of multi-shot                                                                    | 50 |  |  |  |

| 3.3.1 Boost time dependency of growth rate                                                                       | 50 |  |  |  |

| 3.3.2 Effect of precursor multi-shot for growth rate                                                             | 52 |  |  |  |

| 3.4 Demonstration of Y-silicate deposition                                                                       | 57 |  |  |  |

| 3.5 Summary of chapter 3                                                                                         |    |  |  |  |

| Reference                                                                                                        | 61 |  |  |  |

| Chapter 4 SiC MOS devices with an Y-silicate interface layer                                                     | 65 |  |  |  |

| 4.1 XPS analysis for Y-silicate film on SiC substrate                                                            | 66 |  |  |  |

| 4.2 Thickness of Y-silicate layer on electrical property                                                         |    |  |  |  |

| 4.3 Process temperature of Y-silicate interface layer                                                            |    |  |  |  |

| 4.4 Interface property with a flat Y-silicate interface layer                    |     |  |  |

|----------------------------------------------------------------------------------|-----|--|--|

| 4.5 Mobility of MOS transistors with a flat Y-silicate interface layer           |     |  |  |

| 4.6 Summary of chapter 4                                                         | 75  |  |  |

|                                                                                  |     |  |  |

|                                                                                  |     |  |  |

| Chapter 5 Mobility recovery by a CeO <sub>x</sub> layer insertion                | 77  |  |  |

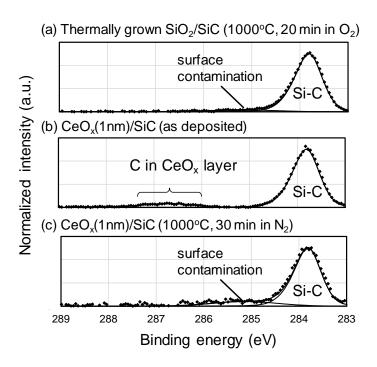

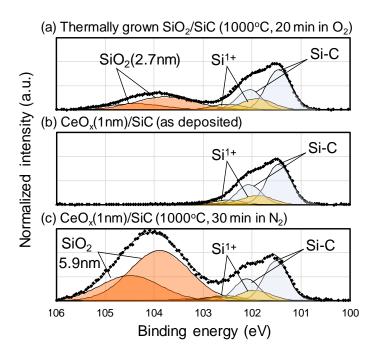

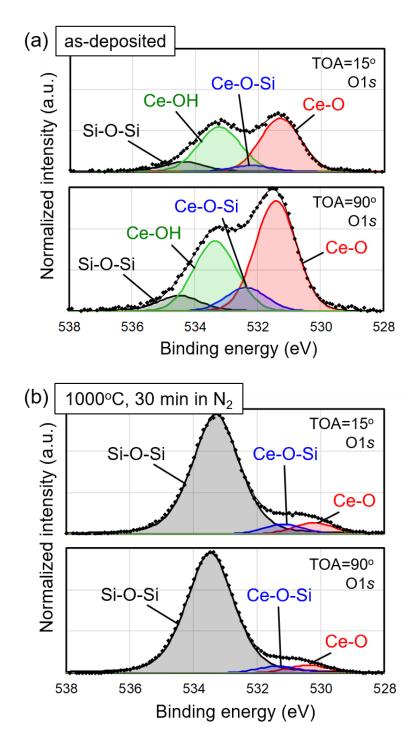

| 5.1 XPS analysis for CeO <sub>x</sub> films on SiC substrates                    | 78  |  |  |

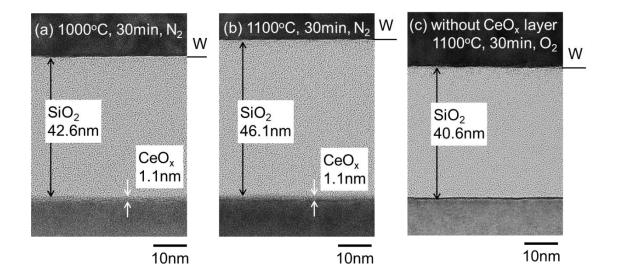

| 5.2 Cross sectional TEM images of SiO <sub>2</sub> /CeO <sub>x</sub> dielectrics | 81  |  |  |

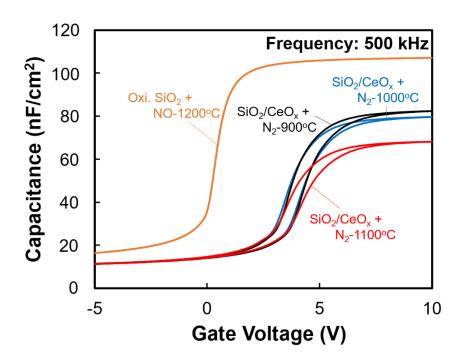

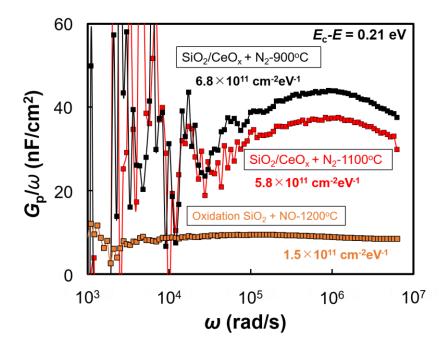

| 5.3 Interface properties of CeO <sub>x</sub> interface layers on SiC substrates  | 83  |  |  |

| 5.4 Electron mobility recovery with CeO <sub>x</sub> interface layers            | 85  |  |  |

| 5.5 Summary of chapter 5                                                         | 87  |  |  |

| Reference                                                                        | 88  |  |  |

|                                                                                  |     |  |  |

| Chapter 6 CeO <sub>x</sub> and Y-silicate gate dielectric stack                  | 90  |  |  |

| 6.1 Interface properties of stacked oxides                                       | 91  |  |  |

| 6.1.1 CeO <sub>x</sub> /Y-silicate stacked interface layer                       | 91  |  |  |

| 6.1.2 Y-silicate/CeO <sub>x</sub> stacked interface layer                        | 93  |  |  |

| 6.2 MOSFET characteristics with stacked interface layer                          | 95  |  |  |

| 6.3 Summary of chapter 6                                                         | 97  |  |  |

|                                                                                  |     |  |  |

| Chapter 7 Summary and conclusions                                                | 99  |  |  |

| Reference                                                                        | 103 |  |  |

| Publications and presentations                                                   | 104 |  |  |

## **Chapter 1 Introduction**

- 1.1 Introduction of SiC semiconductors and device application

- 1.2 Issues in SiC devices

- 1.2.1 Electron mobility degradation

- 1.2.2 Negative threshold voltage shift

- 1.3 Material selection for interface layer

- 1.3.1 Inhibition of surface oxidation

- 1.3.2 Surface oxidation by radical oxygen atoms

- 1.4 Purpose of this study

Reference

## 1 Introduction

## 1.1 Introduction of SiC semiconductors and device application

SiC is a thermally and chemically stable material. SiC has no liquid state and sublimates at temperatures above 2000 degrees due to its high thermal stability. [1-1] In addition, SiC is the second hardest material after diamond due to its strong Si-C bonding. With these properties, SiC has been utilized in environment of high temperature and corrosion as a ceramic material. [1-2, 1-3]

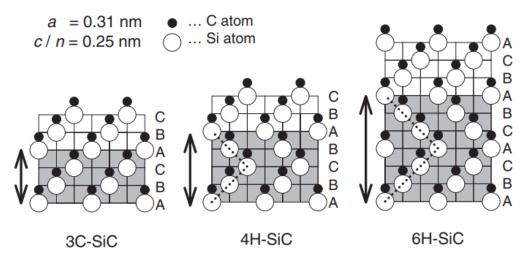

Recently, SiC has also been focused as a semiconductor material. SiC is classified the IV-IV group element semiconductor, which shows polytypism in crystal growth. [1-4] This polytypism can be expressed by close-packed structure of atom. Typical crystal structures of SiC formed in crystal growth are shown in Fig. 1.1.1. 3C, 4H and 6H are Ramsdell notation, each number means that number of stacked atomic unit layers. C and H are initials of cubic and hexagonal, respectively. Moreover, each polytype has different electrical characteristics.

Fig 1.1.1 Arrangements of Si and C atoms for 3C-, 4H-, and 6H-SiC. A, B, and C are occupation sites of hexagonal close-packed structures. [1-5]

| Material                                                      | Si   | 3C-SiC | 4H-SiC | 6H-SiC |

|---------------------------------------------------------------|------|--------|--------|--------|

| E <sub>g</sub> (eV)<br>Bandgap                                | 1.1  | 2.2    | 3.2    | 3.0    |

| E <sub>BD</sub> (10 <sup>6</sup> V/cm)<br>Breakdown field     | 0.3  | 1.5    | 3.0    | 3.0    |

| μ(cm²/Vs)<br>mobility                                         | 1450 | 1000   | 900    | 500    |

| v <sub>sat</sub> (10 <sup>6</sup> cm/s)<br>Saturated velocity | 10   | 27     | 22     | 19     |

| κ(W/cm <sup>2</sup> K) Thermal conductivity                   | 1.5  | 5.0    | 5.0    | 5.0    |

Fig 1.1.1 Comparison of physical properties between Si and SiC. [1-6]

The physical properties of SiC are shown in Table 1.1.1. From the table, 4H-SiC has superior bandgap, breakdown field and bulk mobility than other polytypes. These properties of 4H-SiC are suitable for application in power devices. In comparison with Si, bandgap and breakdown field of 4H-SiC are 3 and 10 times higher, respectively. By using SiC instead of conventional Si, it is expected to be able to fabricate a semiconductor that operates stably in a high temperature and high voltage environment.

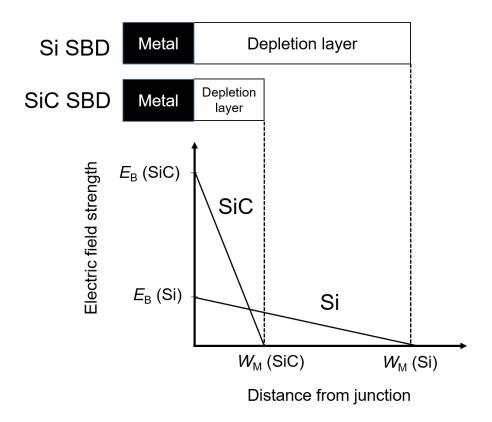

Particularly, SiC can realize high performance of devices with its high breakdown field. It has been reported that SiC Schottky barrier diodes (SBD) and metal-oxide-semiconductor field-effect transistors (MOSFET) show low on-resistance and significant power loss reduction. [1-7] Fig. 1.1.2 shows the electric field distribution in depleted layer of Si and SiC Schottky barrier diodes when back bias is applied. The maximum electric field ( $E_B$ ) at junction interface is dielectric breakdown field strength. At this time, the depletion layer width is also maximized. Breakdown voltage is obtained by the area of each triangle. 4H-SiC can reduce a depletion layer width to 1/10 and increase doping

Fig 1.1.2 Electric field distribution in depleted layer of Si and SiC Schottky barrier diodes.

concentration in this region to 100 times. According to this, resistance of drift layer is significantly decreased to 1/300~1/500. On-resistance is dominant in resistance of drift layer, thus large reduction of on-resistance can be realized by SiC.

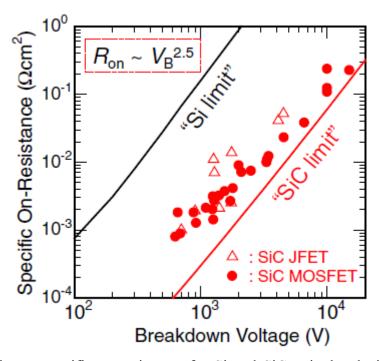

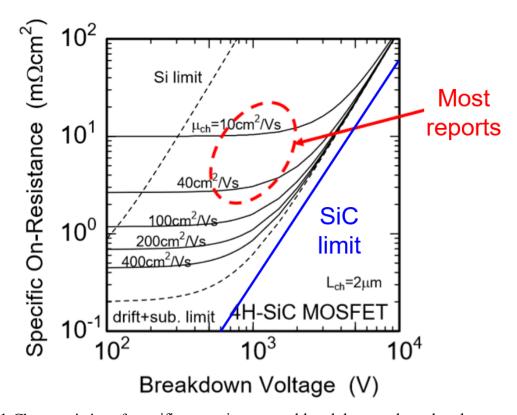

Fig. 1.1.3 shows the relation between on-resistance and breakdown voltage for Si and SiC. In case of same breakdown voltage, low on-resistance is realized by SiC introduction to devices. On the contrary, in case of same on-resistance, SiC devices can be operated in higher voltage than those of Si. Above mentioned advantages of SiC have been clearly demonstrated with numerous reports. With this superior property, SiC devices are expected to be widely spread to increase power efficiency of industry beyond the limit of Si.

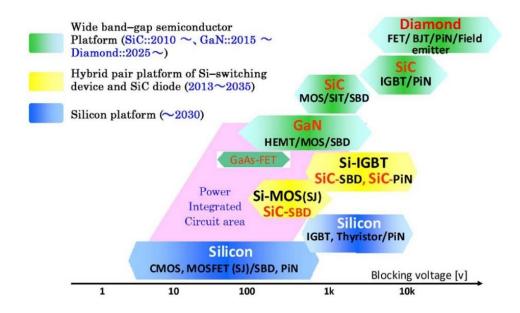

Fig 1.1.4 shows the roadmap of semiconductor application in power devices. For conventional Si power devices, SBD and PiN diode have been used under 200 V and over 200 V blocking voltage, respectively. For switching devices, Si MOSFET can be used up to 600 V blocking voltage. Although Si insulated gate bipolar transistor (IGBT) can realize a higher blocking voltage than Si MOSFET by its bipolar operation, which has suffered from switching loss issue. [1-8] However, unipolar SiC power devices allow application over 5 kV blocking voltage. Additionally, ultra-high voltage application over 5 kV~10 kV is predicted with SiC IGBT/PiN. While performance of Si power devices is reaching its limit, industrial demands are increasing. To realize a society of high energy efficiency, SiC might be the key material of power devices

Fig 1.1.3 Minimum specific on-resistance for Si and SiC unipolar devices versus the blocking voltage. [1-9]

Fig 1.1.4 Application field and trend of semiconductor in power devices. [1-10]

## 1.2 Issues in SiC devices

## 1.2.1 Electron mobility degradation

A unique advantage of SiC over other wide bandgap semiconductor is a growth of SiO<sub>2</sub> by thermal oxidation, which is advantageous for device fabrication using traditional Si process. However, thermally grown SiO<sub>2</sub> dielectrics cause degradation of electron mobility in SiC MOSFET. Most of reported the channel electron mobility of SiC MOSFETs using thermally grown SiO<sub>2</sub> still at the level of 10~40 cm<sup>2</sup>/Vs as shown in Fig. 1.2.1.1. This low inversion channel mobility inevitably leads to much higher on resistance of SiC power devices. [1-11, 1-12] The mobility of 10~40 cm<sup>2</sup>/Vs is insufficient to reach SiC limit, therefore, over 100 cm<sup>2</sup>/Vs is required for 1.2 kV blocking voltage

Fig 1.2.1.1 Characteristics of specific on-resistance and breakdown voltage by electron mobility variation.

application. Breakdown voltage of 1.2 kV is mainly applied to rated voltage over 500 V, which is major region of industry such as electric vehicles, motor control or heating. [1-9] Thus, the mobility issue of SiC is critical for application of power devices.

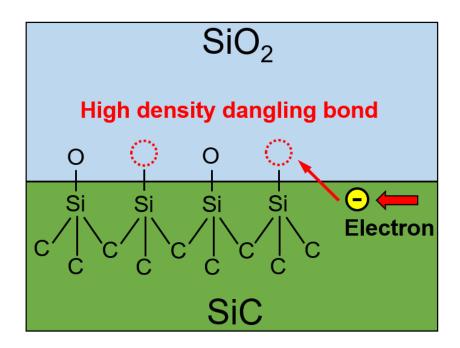

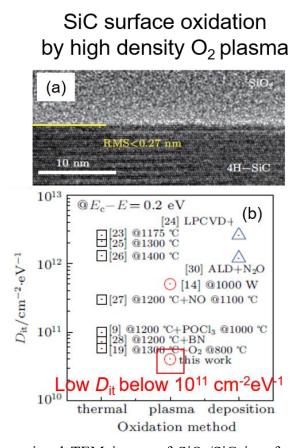

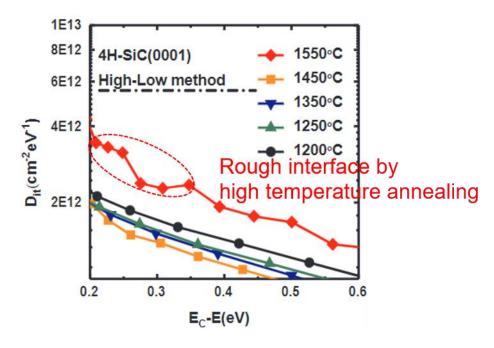

For mobility issue, high interface state density (D<sub>it</sub>) at SiO<sub>2</sub>/SiC interface has been reported as one of the causes. [1-13] Especially, carbon-related defects have been considered as one of the causes for high D<sub>it</sub>. During thermal oxidation of SiC, most of the excess carbon is transformed into CO molecules and diffused from interface. However, some of the carbon atoms can remain at interface and form carbon clusters or graphitic regions. [1-14~16] In addition, oxygen defects have also been considered for high D<sub>it</sub> issues. The high  $D_{it}$  near the SiC conduction band edge is caused by oxide defects located close to the interface, which defects affect mobility degradation. [1-17, 1-18] This kind of defect may result from the oxygen vacancy, or from the dangling bond originates from the lattice mismatch of SiO<sub>2</sub> with SiC. Many reports have shown that there is a strong relationship between  $D_{it}$  and electron mobility for SiC MOS-devices. [1-19~22] From these reports, an inverse proportional relationship between  $D_{it}$  and electron mobility can be summarized for increasing of mobility with reduction of  $D_{\rm it}$ . To achieve high electron mobility, reduction of  $D_{\rm it}$  below  $10^{11}$  cm<sup>-2</sup>Vs<sup>-1</sup> is necessary.  $D_{\rm it}$  of  $10^{10} \sim 10^{11}$  cm<sup>-2</sup>Vs<sup>-1</sup> is comparable to SiO<sub>2</sub>/Si interface level, which may be the key factor for increasing mobility of SiC devices.

Electron mobility degradation by high  $D_{it}$  is mainly related to coulomb scattering phenomenon. Fig. 1.2.1.2 shows the schematic illustration of mobility degradation in SiC devices. When high density dangling bond is formed at SiO<sub>2</sub>/SiC interface, some of electrons in current are trapped there. The trapped electrons cause coulomb scattering by repulsive force against other electrons. This phenomenon interrupts current flow and

degrades electron mobility. Furthermore, that occurs more frequently with higher  $D_{it}$ . For low  $D_{it}$  and high electron mobility, various interface engineering techniques have been introduced.

Fig 1.2.1.2 Schematic illustration of electron mobility degradation at SiO<sub>2</sub>/SiC interface.

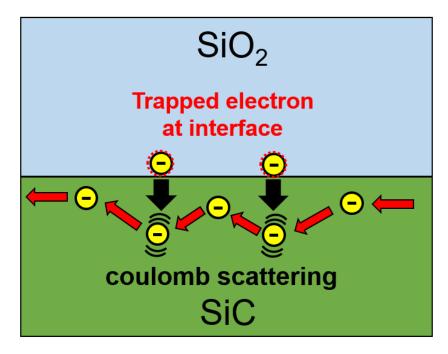

First, interface nitrogen atom passivation by nitric oxide (NO) or nitrous oxide (N<sub>2</sub>O) has been commonly performed, which improves the peak mobility up to  $40 \text{ cm}^2/\text{Vs}$  with  $D_{\text{it}}$  reduction. [1-23~25] By N passivation to SiO<sub>2</sub>/SiC interface, dangling bond of Si or C atoms are terminated and carbon residues are also removed by oxygen decomposed from NO or N<sub>2</sub>O. Schematic mechanism is shown in Fig. 1.2.1.3.

Fig 1.2.1.3 SiO<sub>2</sub>/SiC interface before and after N passivation. [1-26]

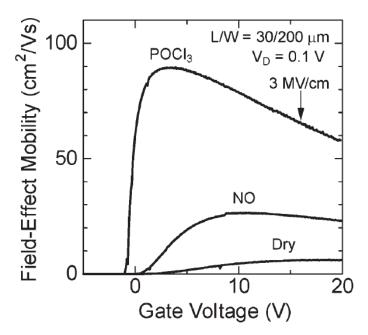

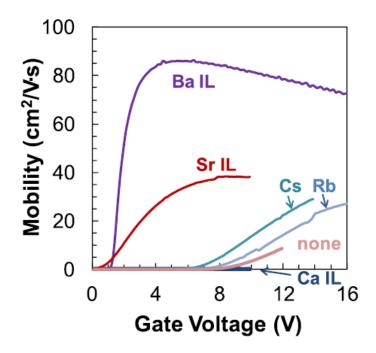

Besides, various foreign atom incorporations have also been investigated to further improve the mobility. P atoms incorporation by POCl<sub>3</sub> annealing into the SiO<sub>2</sub> layer is reported to achieve a high peak mobility of 89 cm<sup>2</sup>/Vs. [1-27~29] Although P atoms are not passivated at interface but almost distributed in SiO<sub>2</sub> layer, which reduces  $D_{it}$  more than NO annealing. For this  $D_{it}$  reduction, interface strain reduction has been expected as a reason. On the other hand, Ba atoms induced oxidation process recovers the peak mobility up to 85 cm<sup>2</sup>/Vs by increase of mobile free carriers. [1-30, 1-31] These results

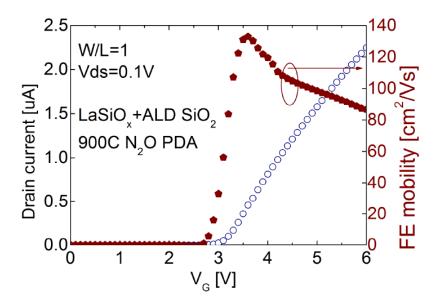

also show low  $D_{it}$  values, which is achieved by different mechanism from conventional oxidation process. In addition, a high peak mobility of 134 cm<sup>2</sup>/Vs was reported with an La-silicate interface layer accompanied by the nitrogen passivation process. [1-32~34] For interface engineering, gate dielectrics other than SiO<sub>2</sub> also have potential.

## 1.2.2 Negative threshold voltage shift

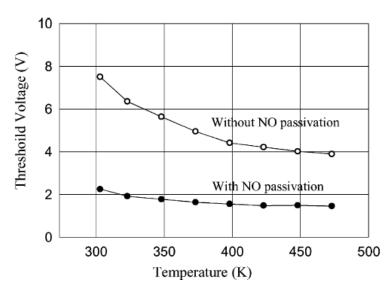

Although the reduction in the  $D_{it}$  can improve the mobility, a negative threshold voltage  $(V_{th})$  shift has been observed after positive bias. The negative  $V_{th}$  shift after NO annealing is shown in Fig. 1.2.2.1. Decreasing  $V_{th}$  corresponds to the reduction of negative effective charge in the oxide or at the interface for both passivated and un-passivated devices. In addition, more severe shifts have been observed. The examples of P and Ba incorporated MOSFETs are shown in Fig. 1.2.2.2 and 1.2.2.3, respectively. It seems to be related with reduction of interface trap and negative fixed charge, however, a  $V_{th}$  close to 0 V is cannot be explained with only that.

Fig. 1.2.2.1 Temperature dependence of threshold voltage with and without NO passivation. [1-35]

Fig. 1.2.2.2 Field-effect mobility of 4H-SiC MOSFETs fabricated on the Si face by dry oxidation, NO annealing, and the POCl<sub>3</sub> annealing at 1000°C. [1-36]

Fig. 1.2.2.3 Field-effect mobility from  $I_{\rm d}$ - $V_{\rm g}$  transfer characteristics for MOSFETs processed with Rb, Cs, Ca, Sr, or Ba interface layers, compared to an un-passivated thermal oxide (labeled "none"). [1-37]

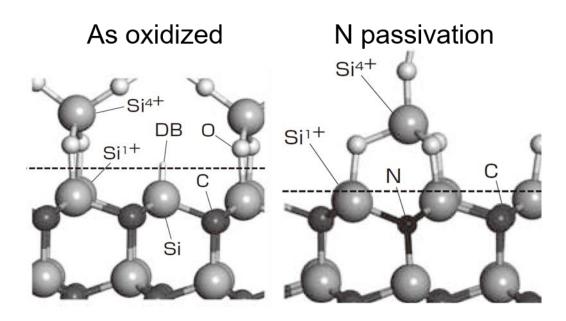

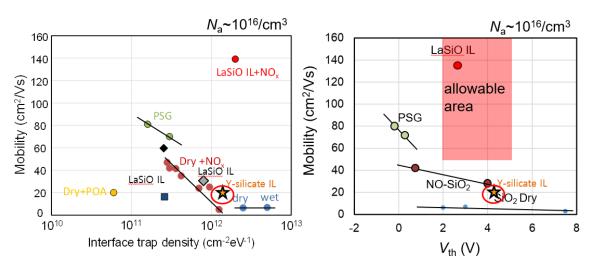

On the other hand, lanthanum silicate (La-silicate) interface layer shows a high mobility of 134 cm<sup>2</sup>/Vs with a relatively high  $V_{\rm th}$  of 3 V. [1-32] Fig 1.2.2.4 shows the  $I_{\rm d}$ - $V_{\rm g}$  characteristics with La-silicate interface layer. Although the  $D_{\rm it}$  at the interface between the La-silicate interface layer and the SiC surface is not low enough (over  $10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup>), rare earth silicate interface layer seems to a promising interface layer for recovering the mobility while keeping the high  $V_{\rm th}$ .

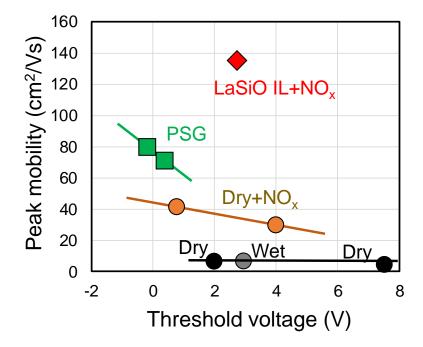

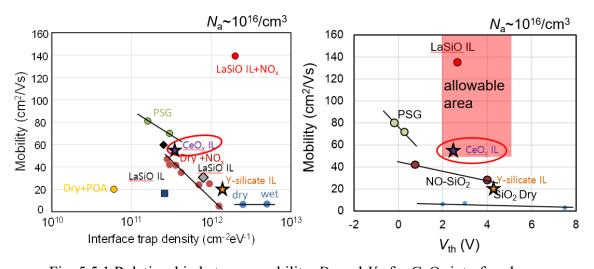

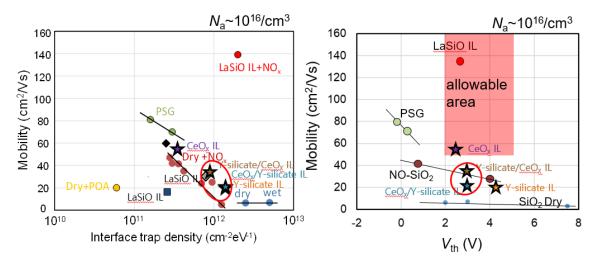

The relationship between peak mobility and  $V_{th}$  of reported MOSFET is shown in Fig. 1.2.2.5. After dry oxidation without interface treatment, the peak mobility stays at poor value of lower than  $10 \text{ cm}^2/\text{Vs}$ . NO<sub>x</sub> gas annealing is added after dry oxidation, the peak mobility is increased to  $28 \text{ cm}^2/\text{Vs}$ . However, the mobility increase accompanies the sacrifice of  $V_{th}$ . The  $V_{th}$  decreases with the increase of annealing time. Similarly, interface treatment by PSG also leads to a high mobility of  $80 \text{ cm}^2/\text{Vs}$ ,  $V_{th}$  shifts to negative direction. However, a high peak mobility of  $134 \text{ cm}^2/\text{Vs}$  is achieved by La-silicate interface layer without significant  $V_{th}$  decrease. As mentioned above, the La-silicate interface layer showed the high  $D_{it}$  over  $10^{12} \text{ cm}^{-2} \text{eV}^{-1}$ . Nevertheless, the superior electric properties of rare earth silicate interface layer are attractive for SiC devices.

Fig. 1.2.2.4  $I_d$ - $V_g$  characteristics of LaSiO<sub>x</sub>/30 nm SiO<sub>2</sub> MOSFET after 900 °C N<sub>2</sub>O PDA. [1-32]

Fig. 1.2.2.5 Reported peak electron mobility with  $V_{\rm th}$  of SiC MOSFETs. Each reported data is PSG [1-29], LaSiO [1-32], Dry/Wet [1-38] and NO<sub>x</sub> [1-23], respectively. The channel doping is of the order of  $10^{16}$ /cm<sup>3</sup>.

## 1.3 Material selection for interface layer

#### 1.3.1 Inhibition of surface oxidation

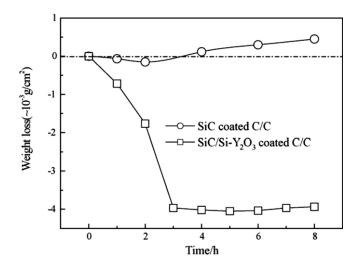

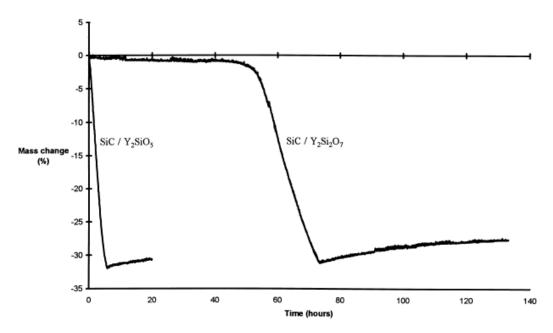

Commonly, rare earth silicate or aluminosilicate glasses have been utilized to promote liquid-phase SiC-based ceramics due to low reactivity to the SiC compounds. Also, among rare earth silicates, yttrium silicate (Y-silicate) has been used as an anti-oxidation coating to SiC compounds because of its equivalent thermal expansion coefficient to the SiC. Fig 1.3.1.1 shows the isothermal oxidation curves of SiC-C/C and SiC/Si-Y<sub>2</sub>O<sub>3</sub> coated C/C at 1773 K. Y-silicate coating is effective for anti-oxidation, which leads to reduction of weight loss of SiC. Similary, the anti-oxidation effect of Y<sub>2</sub>Si<sub>2</sub>O<sub>7</sub> is also clearly known by mass change as shown in Fig. 1.3.1.2.

To investigate an anti-oxidation effect for SiC MOS devices, a Y-silicate layer inhibiting the SiC surface oxidation will be deposited as a gate dielectric on SiC substrates, and electrical characteristics will be also evaluated.

Fig. 1.3.1.1 Isothermal oxidation curves of SiC–C/C and SiC/Si–Y<sub>2</sub>O<sub>3</sub> coated C/C at 1773 K. [1-39]

1.3.1.2 Isothermal oxidation behaviour of C/SiC with coatings based on Y-silicate at 1600 °C. [1-40]

Fig.

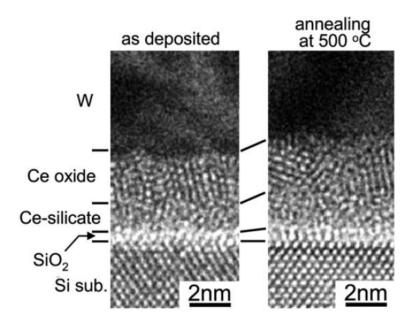

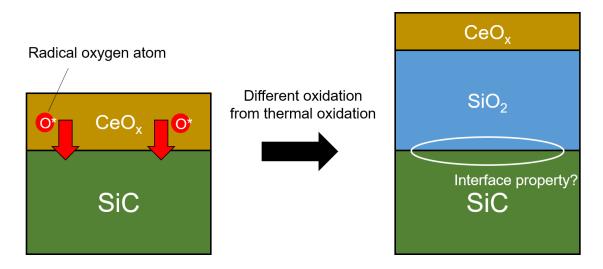

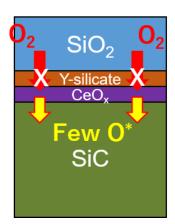

## 1.3.2 Surface oxidation by radical oxygen atoms

Among rare earth oxides, CeO<sub>x</sub> is known to promote oxidation of adjacent materials by producing radical oxygen atoms. For instance, an interface SiO<sub>2</sub> layer is formed after annealing the CeO<sub>x</sub>/Si structure. The interface layer formation is triggered by the supply of oxygen atoms to change the valence number of Ce atoms during the reaction. Although 4H-SiC surface is less reactive to oxygen atoms than Si surface, one can still expect the formation of the interface SiO<sub>2</sub> layer. Since the reaction is based on oxygen radicals, the interface structure might be different from those created by thermally grown SiO<sub>2</sub>. Therefore, in this thesis, the effect of CeO<sub>x</sub> layer on SiC substrates will be investigated.

Fig. 1.3.2.1 Cross sectional TEM of W/CeO<sub>x</sub>/Si before and after 500°C annealing. [1-41]

## 1.4 Purpose of this study

As the thermally grown interface structure seems to be origin of the degradation in mobility and the negative shift in the  $V_{th}$ , complete inhibition of the surface SiC oxidation or different surface SiC oxidizing process might be used to solve the problem. As coating with Y-silicate is known to protect the SiC surface from oxidation, the initial surface can be preserved during the gate stack formation. On the other hand,  $CeO_x$  is known to oxidize the surface by means of radical oxygen species, expecting different type of interface structure. The purpose of this thesis is to elucidate the effect of Y-silicate and  $CeO_x$  gate dielectrics for SiC MOS capacitors and MOSFET.

#### Reference

- [1-1] R. W. Olesinki and G. J. Abbaschian, Bull. Alloy Phase Diagrams 5, 486, 527 (1984).

- [1-2] E. Passalacqua, S. Freni and F. Barone, Mater. Lett., 34, pp. 257-262 (1998).

- [1-3] J. She, J. Yang, N. Kondo, T. Ohji, S. Kanzaki and Z. Deng, J. Am. Ceram. Soc., 85, pp. 2852-2854 (2002).

- [1-4] A. R. Verma and K. Krishna, Polymorphism and Polytypism in Crystals, Wiley, New York (1966).

- [1-5] H. Matsunami, Jpn. J. Appl. Phys., 43, pp. 6835-6847 (2004).

- [1-6] M. Hiroyuki, N. oodani, T. Kimoto, and K. Taka "Technology of semiconductor SiC and its application", pp. 9-20 (2001).

- [1-7] M. Bhatnagar and B.J. Baliga, IEEE Trans. Elec. Dev., 40, pp. 645-655 (1993).

- [1-8] G. Wang, F. Wang, G. Magai, Y. Lei, A. Huang and M. Das, IEEE ECCE, pp. 3230-3234 (2013).

- [1-9] T. Kimoto, Jpn. J. Appl. Phys., 54, 040103 (2015).

- [1-10] M. Ohashi, IEEE Trans. Electron Devices, 60, pp. 528-534 (2013).

- [1-11] J. Spitz, M. R. Melloch, Jr. J. A. Cooper, and M. A. Capano, IEEE Elec. Dev. Lett., 19, pp. 100-102 (1998).

- [1-12] V. R. Vathulya and M. H. White, Solid-State Electron., 44, pp. 309-315 (2000).

- [1-13] J. R. Williams, G.Y. Chung, C. C. Tin, K. McDonald, D. Farmer, R.K. Chanana,

- R. A. Weller, S. T. Pantelides, O.W. Holland, M. K. Das, and L. C. Feldman, Mater. Sci. For., 389-393, pp.967-972 (2002).

- [1-14] V. V. Afanas'ev, M. Bassler, G. Pensl, and M. Schulz, Phys. Stat. Sol. (a), 162, pp.321-337 (1997).

- [1-15] K. McDonald, R. A. Weller, S. T. Pantelides, L. C. Feldman, G. Y. Chung, C. C. Tin, and J. R. Williams, J. Appl. Phys., 93, pp.2719-2722 (2003).

- [1-16] J. M. Knaup, P. Deák, and Th. Frauenheim, Phys. Rev. B, 72, 115323 (2005).

- [1-17] V. V. Afanas'ev and A. Stesmans, Phys. Rev. Lett., 78, pp.2437-2440 (1997).

- [1-18] V. V. Afanas'ev, A. Stesmans, M. Bassler, G. Pensl, and M. J. Schulz, Appl. Phys. Lett., 76, pp.336-337 (2000).

- [1-19] John Rozen, Ayayi C. Ahyi, Xingguang Zhu, John R. Williams, and Leonard C. Feldman, IEEE Trans. Elec. Dev., 58, pp.3808-3811 (2011).

- [1-20] S. Yoshida, S. Nishino, H. Harima and T. Kimoto, Mater. Sci. For., 389-393, pp. 985-988, (2002).

- [1-21] H. Yoshioka, J. Senzaki, A. Shimozato, Y. Tanaka, and H. Okumura, Appl. Phys. Lett., 104, 083516 (2014).

- [1-22] A.Pérez-Tomása, P.Godignona, N.Mestresb and J.Millána, Micro. Eng., 83, pp. 440–445 (2006).

- [1-23] G. Y. Chung, C. C. Tin, J. R. Williams, K. McDonald, R. K. Chanana, R. A. Weller,S. T. Pantelides, L. C. Feldman, O.W. Holland, M. K. Das and J. W. Palmour, IEEE Elec.

- Dev. Lett. 22, pp. 176-178 (2001).

- [1-24] G. Y. Chung, C. C. Tin, J. R. Williams, K. McDonald, M. Di Ventra, S. T. Pantelides,

- [1-25] P. Jamet, S. Dimitrijev and P. Tanner, J. Appl. Phys., 90, pp. 5058-5063 (2001).

L. C. Feldman and R. A. Weller, Appl. Phys. Lett., 76, pp. 1713-1715 (2000).

- [1-26] Fuji electric, technical report, 89, 21 (2016).

- [1-27] D. Okamoto, H. Yano, K. Hirata, T. Hatayama and T. Fuyuki, IEEE Elec. Dev. Lett., 31, pp. 710-712 (2010).

- [1-28] H. Yano, T. Araoka, T. Hatayama and T. Fuyuki, Mater. Sci. For., 740-742, pp. 727-

- 732 (2013).

- [1-29] Y. K. Sharma, A. C. Ahyi, T. Isaacs-Smith, A. Modic, M. Park, Y. Xu, E. L. Garfunkel, S. Dhar, L. C. Feldman and J. R. Williams, IEEE Elec. Dev. Lett., 34, pp. 175-177 (2013).

- [1-30] E. Fujita, M. Sometani, T. Hatakeyama, S. Harada, H. Yano, T. Hosoi, T. Shimura and H. Watanabe, AIP Adv., 8, 085305 (2018).

- [1-31] D. J. Lichtenwalner, L. Cheng, S. Dhar, A. Agarwal and J. W. Palmour, Appl. Phys. Lett., 105, 182107 (2014).

- [1-32] X. Yang, B. Lee and V. Misra, Mater. Sci. For., 778-780, pp. 557-561 (2014).

- [1-33] X. Yang, B. Lee and V. Misra, IEEE Elec. Dev. Lett., 39, pp. 244-247 (2018).

- [1-34] M. Kang, K. Lawless, B. Lee and V. Misra, Mater. Sci. For., 924, pp. 482-485 (2018).

- [1-35] G.Y. Chung, J.R. Williams, C.C. Tin, K. McDonald, D. Farmer, R.K. Chanana, S.T. Pantelides, O.W. Holland, L.C. Feldman, Appl. Surf. Sci., 184, pp. 399-403 (2001).

- [1-36] D. Okamoto, H. Yano, K. Hirata, T. Hatayama and T. Fuyuki, IEEE Elec. Dev. Lett., 31, pp. 710-712 (2010).

- [1-37] D. J. Lichtenwalner, L. Cheng, S. Dhar, A. Agarwal and J. W. Palmour, Appl. Phys. Lett., 105, 182107 (2014).

- [1-38] S. Harada, R. Kosugi, J. Senzaki, W. Cho, K. Fukuda, K. Arai, and S. Suzuki, J. Appl. Phys., 91, pp.1568-1571 (2002).

- [1-39] J. Huang, H. Li, X. Zeng, F. Deng, X. Xiong and K. Li, Ceram. Int., 33, pp. 887-890 (2007).

- [1-40] J. D. Webster, M. E. Westwood, F. H. Hayes, R. J. Day, R. Taylor, A. Duran, M. Aparicio, K. Rebstock, W. D. Vogel, J. Europ. Ceram. Soc., 18, pp. 2345-2350 (1998).

[1-41] M. Mamatrishat, M. Kouda, K. Kakushima, H. Nohira, P. Ahmet, Y. Kataoka, A. Nishiyama, K. Tsutsui, N. Sugii, K. Natori, T. Hattori and H. Iwai, Vacuum, 86, pp. 1513-1516 (2012).

## Chapter 2 Fabrication and characterization methods

## 2.1 Experiment procedure

- 2.1.1 Surface cleaning

- 2.1.2 Atomic layer deposition (ALD)

- 2.1.3 Post-deposition annealing (PDA)

- 2.1.4 RF magnetron sputtering

- 2.1.5 Photolithography

- 2.1.6 Reactive ion etching (RIE)

- 2.1.7 Post-metallization annealing (PMA)

#### 2.2 Device fabrication

- 2.2.1 Fabrication procedure for *n*-MOS capacitors

- 2.2.2 Fabrication procedure for *n*-MOSFETs

#### 2.3 Characterization method

- 2.3.1 Capacitance-Voltage (C-V) measurement

- 2.3.2 Interface state density  $(D_{it})$  by conductance method

- 2.3.3 Pulse measurement for  $I_d$ - $V_g$  characteristics

- 2.3.4 Effective channel length extraction

- 2.3.5 Field effect mobility extraction

- 2.3.6 X-ray photoelectron spectroscopy (XPS)

- 2.3.7 Transmission electron microscope (TEM)

#### Reference

## 2 Fabrication and characterization method

## 2.1 Experiment procedure

## 2.1.1 Surface cleaning

A substrate before pretreatment basically has inorganic pollution such as metal and nature oxide film, organic pollution and so on. Sulfuric acid-Hydrogen Peroxide Mixture (SPM) treatment, using piranha solution which is a mixture of sulfuric acid (H<sub>2</sub>SO4) and hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>), is effective for removing organic residue on substrate surface. It will also hydroxylate the substrate surface, making the substrate highly hydrophilic. Hydrofluoric acid (HF) treatment is another pretreatment process for removing inorganic pollutions on substrate. Due to the strong acid property, a hydrofluoric acid can remove most metal residues and oxides on substrate. HF treatment are often performed after SPM treatment. In this study, the solution radio of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> was set to 3:1 and fresh solution heating up to 180°C was used. Samples were treated in H<sub>2</sub>SO<sub>4</sub>/H<sub>2</sub>O<sub>2</sub> solution for 10 min to remove organic pollutions. After SPM treatment, samples were set into 20% HF for 2 min to remove residue particle and metal contamination.

## 2.1.2 Atomic layer deposition (ALD)

In this study, all gate dielectrics are deposited by ALD process. ALD is a film deposition method by precise film thickness control. A type of precursor is different depending on the target film, and the film grows on the substrate by oxidizing it. The precursor molecules react with surface of substrate, but reaction between precursor molecules is limited by self-limiting characteristic. Consequently, the maximum film thickness deposited on the surface after a single exposure to is determined by the nature of the precursor-surface interaction. [2-1] Using this characteristic, target film thickness

can be achieved by cyclic pulse process.

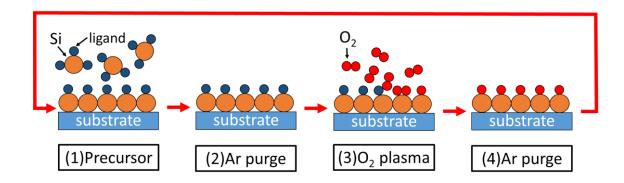

Figure 2.1.2.1 illustrated the example of basic cycling process for deposition of ALD-SiO<sub>2</sub>, Firstly, precursor is injected to the reaction chamber and coating the material. After then, any excess is removed by Ar purge. O<sub>2</sub> plasma is radiated and reacts with precursor to create another layer on the surface. After reaction between the precursor and O<sub>2</sub> plasma, excess O<sub>2</sub> is removed by Ar purge again and this process is repeated until target thickness is deposited.  $Y_2O_3$  and  $CeO_x$  layer are also deposited by same principle with SiO<sub>2</sub>.

Fig 2.1.2.1 schematic illustration of atomic layer deposition process.

## 2.1.3 Post-deposition annealing (PDA)

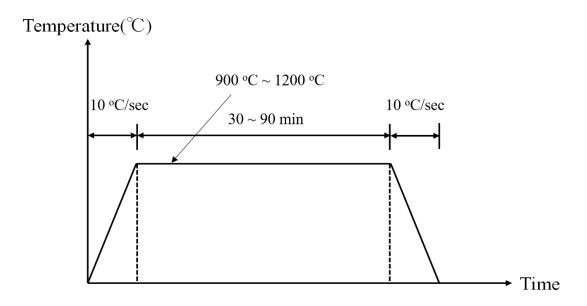

Deposited gate dielectrics are annealed with a lamp annealer. That process is called post-deposition annealing (PDA) for improvement of dielectric property. The samples are heated by light focusing from source. Also, oxidation of SiC substrates for standard samples is also performed in this annealer. A SiC susceptor in the annealer can endure in high temperature, thus high temperature annealing over 1000°C is available. The temperature curve in annealing process is shown in Fig 2.1.3.1. In this study, ranges of PDA temperature and time are from 900°C to 1200°C and from 30 min to 90 min, respectively.

Fig 2.1.3.1 Temperature curve in PDA process.

## 2.1.4 RF magnetron sputtering

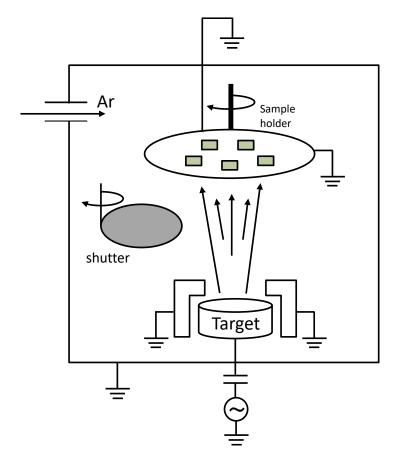

Deposition of gate and source/drain (S/D) electrodes are conducted by radio frequency (RF) magnetron sputtering. The illustration of RF magnetron sputtering is shown in Fig 2.1.4.1. Ar gas flow into the chamber, and a high electric field is applied between substrate and target. Ionized Ar atoms hit the target, and then target atoms are emitted. Emitted target atoms fly through the vacuum chamber and deposited on the substrate. W gate and Ni S/D electrodes were deposited with RF power of 150 W in Ar ambient. In case of TiN deposition, N<sub>2</sub> gas was also added to chamber for nitridation of target. Deposition rate of nitride is low for collision of Ar and N<sub>2</sub> atoms, thus a RF power was set to 300 W.

Fig 2.1.4.1 Schematic illustration of RF magnetron sputtering

## 2.1.5 Photolithography

To patterning the samples, photolithograph process is utilized. First, positive photoresist was coated on the samples by spin coating. Rotation per minute (RPM) was set to 3000 per minute. Then the samples were heated to 115°C to drive off excess moisture in the photoresist, which is so called pre-baking process. Next, the coated samples were aligned and exposed with photomask and ultraviolet (UV). After that, exposed area was developed by dipping in developer. Finally, the samples were treated by post-baking process to solidify the remaining photoresist for the following plasma etching. The processes of photolithography are illustrated in Fig. 2.1.5.1.

Fig 2.1.5.1 Schematic illustration of the photolithography process. [2-2]

## 2.1.6 Reactive ion etching (RIE)

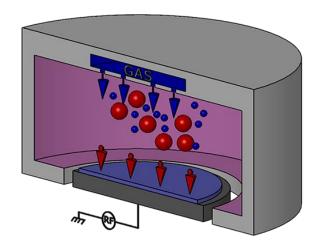

RIE is plasma etching technology for realizing nano or micro-patterning. Figure 2.1.6.1 is schematic illustration of RIE process. In this study, this process is used for isolation of sputtered W and TiN films for gate electrodes. Plasma is generated by applying RF power, after then, etching gas ions move to substrate by applying DC power. The etching gas ions conflict with material of substrate, which is removed by sputtering and chemical reaction. For device reliability, isolation of gate electrodes was performed by slightly over etching than standard condition.

Figure 2.1.6.1 Schematic illustration of RIE process. [2-3]

## 2.1.7 Post-metallization annealing (PMA)

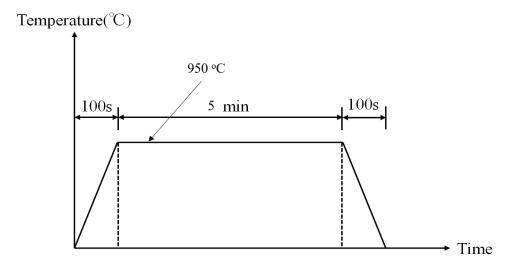

Post-metallization annealing (PMA) is a thermal treatment conducted by rapid thermal annealing (RTA). After formation of gate and S/D electrodes, the samples were annealed to improve contact property. The temperature curve in annealing process is shown in Fig 2.1.7.1. A rapid heating rates was obtained by high intensity lamps. In this study, annealing temperature of 950°C was used with forming gas (F.G).

Fig 2.1.7.1 Temperature curve in PMA process.

#### 2.2 Device fabrication

### 2.2.1 Fabrication procedure for *n*-MOS capacitors

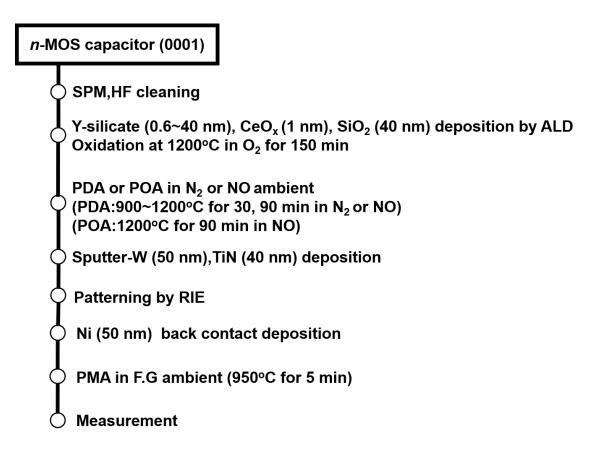

4H-SiC MOS capacitors were fabricated on a Si-face (0001) n-type ( $N_D$ =5×10<sup>15</sup> cm<sup>-3</sup>) 4° off-axis epitaxial layer. The samples were chemically cleaned by H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> mixture (SPM) solutions, followed by chemical oxide removal by HF (20%) dipping for 1 min. Gate dielectric layers of Y-silicate (0.6~40 nm), CeO<sub>x</sub>, (1 nm) and SiO<sub>2</sub> (40 nm) were deposited by atomic layer deposition (ALD) process at a substrate temperature of 200°C using oxygen remote plasma and precursors; Y(iPrCp)3, Ce(iEtCp)3, and  $SiH[N(CH_3)_2]_3$ , respectively. To secure the deposition coverage of the  $Y_2O_3$  and the  $CeO_x$ layers, a multi-shot deposition process was utilized. [2-4] A detail of Y-silicate layer deposition will be introduced in chapter 3.4. The samples were then post-deposition annealed (PDA) in either N<sub>2</sub> or NO ambient at various temperatures from 900°C to 1200°C for 30 min and 90 min. A standard sample with thermal oxidation formed by 1200°C (~34 nm), followed by post oxidation annealing (POA) in NO:N<sub>2</sub>=20%:80% gas at 1200°C, was fabricated. 50-nm-thick W gate electrodes were deposited by RF sputtering with a 40-nm-thick TiN capping layer to protect the surface against oxidation. The metal layers were patterned by reactive ion etching (RIE) with Cl<sub>2</sub> and Ar chemistries. Finally, 50-nm-thick Ni contact layers were deposited on the backside of the samples by RF sputtering. The capacitors were then post-metallization annealed (PMA) at 950°C in F.G (N<sub>2</sub>: H<sub>2</sub>=97 %:3 %) ambient for 5 min. The fabrication flow of MOS capacitors is shown in Fig. 2.2.1.1.

Fig 2.2.1.1 Fabrication flow of SiC MOS capacitors.

### 2.2.2 Fabrication procedure for *n*-MOSFETs

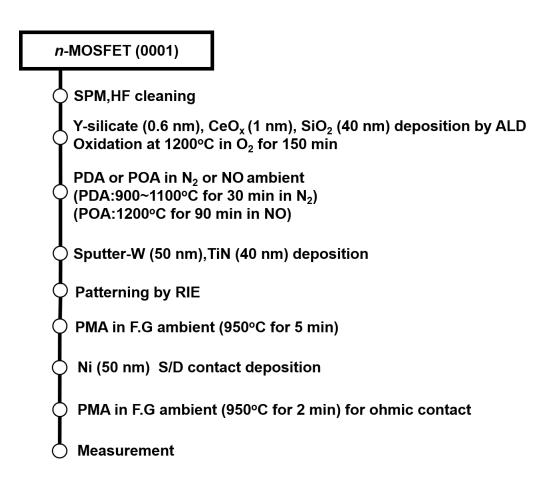

Planar 4H-SiC MOSFETs were fabricated on a Si-face (0001) p-type ( $N_A$ =2×10<sup>15</sup> cm<sup>-3</sup>) 4° off-axis epitaxial layer. The same structure of gate dielectrics with the capacitors were deposited by ALD. PDA was performed at from 900°C to 1100°C for 30 min, and POA condition is same to capacitors. TiN/W layers were deposited for gate electrodes. After gate patterning, PMA was performed at 950°C for 5 min in F.G ambient for removal of carbon residue in dielectrics by oxygen diffusion from W. Ni was used for S/D contact, and it was annealed at 950°C for 2 min to obtain ohmic property. The fabrication flow of MOSFETs is shown in Fig. 2.2.2.1.

Fig 2.2.2.1 Fabrication flow of SiC MOSFETs.

### 2.3 Characterization method

### 2.3.1 Capacitance-Voltage (*C-V*) measurement

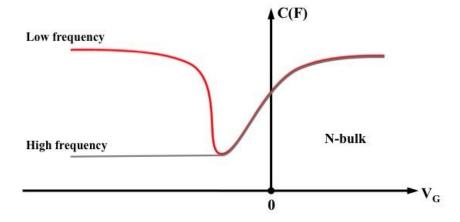

Capacitance-Voltage (*C-V*) characteristic measurements were performed with frequency of 500 kHz by precision LCR (E4980A, Agilent). The measurement of capacitance was conducted by contact with gate electrode and back electrode of capacitors. The range of measurement voltage was set from -5 V to 10 V for all capacitors. Also, measurement frequency was set to 500 kHz. From measured *C-V* characteristics, various information of devices can be extracted such as interface property, doping concentration and so on. Fig. 2.3.1.1 shows the schematic *C-V* curves.

Fig 2.3.1.1 Schematic *C-V* curves in low and high frequency.

### 2.3.2 Interface state density $(D_{it})$ by conductance method

The conductance method is one of the methods to determine interface state density ( $D_{it}$ ). Interface trap capture and emission of carriers can be evaluated by  $D_{it}$ .

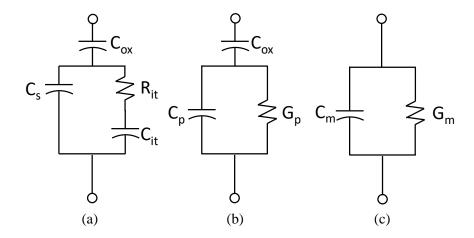

The simplified equivalent circuit of MOS-capacitor applied with the conductance method is shown in Fig. 2.3.2.1 (a). where  $C_{ox}$  is the oxide capacitance,  $C_S$  is the semiconductor capacitance. Also, where  $C_{it}$  and  $R_{it}$  are the interface trap capacitance and the interface trap resistance, respectively. The circuit can be simplified to the circuit in Fig. 2.3.2.1 (b), where  $C_P$  and  $G_P$  are given by [2-5]:

$$C_{p} = C_{s} + \frac{C_{it}}{1 + (\omega \tau_{it})^{2}}$$

(2.1)

$$\frac{G_p}{\omega} = \frac{q\omega \tau_{it} D_{it}}{1 + (\omega \tau_{it})^2} \tag{2.2}$$

Here,  $D_{it}$  is determined by maximum  $G_p/\omega$ , which relationship is expressed by [2-5]:

$$D_{it} = \frac{2.5}{q} \left(\frac{G_p}{\omega}\right)_{\text{max}} \tag{2.3}$$

Measured capacitance and conductance consist of the parallel combination as shown in Fig. 2.3.2.1 (c).  $G_p/\omega$  can be converted into an equation based on the measured parameters, which is expressed by [2-5]:

$$\frac{G_p}{\omega} = \frac{\omega G_m C_{ox}^2}{G_{yy}^2 + \omega^2 (C_{ox} - C_{yy})^2}$$

(2.4)

From this equation,  $G_p/\omega$  can be obtained by measurement, and  $D_{it}$  is also can be calculated.

Fig. 2.3.2.1 Equivalent circuits for conductance measurements; (a) MOS-Capacitor with interface trap time constant  $\tau_{it} = R_{it}C_{it}$ , (b) simplified circuit of (a), (c) measured circuit, [2-5].

## 2.3.3 Pulse measurement for $I_{\rm d}$ - $V_{\rm g}$ characteristics

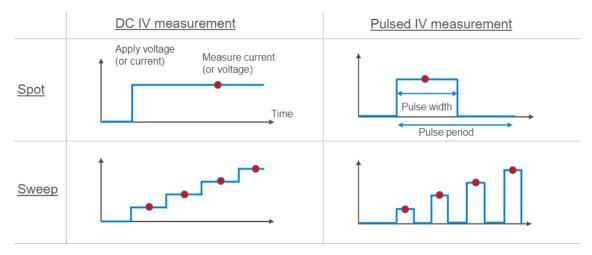

In this study, pulse measurement is performed to the drain current ( $I_d$ ) on gate voltage ( $V_g$ ) characteristics,  $I_d$ - $V_g$ , for MOSFETs instead of DC measurement. This is to minimize the effect carrier trapping to generate the hysteresis in the sweeping measurement and to extract the real mobility obtained by the fabricated interface. Fig. 2.3.3.1 shows the fundamental characteristics of DC and pulse measurements.

Fig. 2.3.2.1 Fundamental characteristics of DC and pulse measurements.

### 2.3.4 Effective channel length extraction

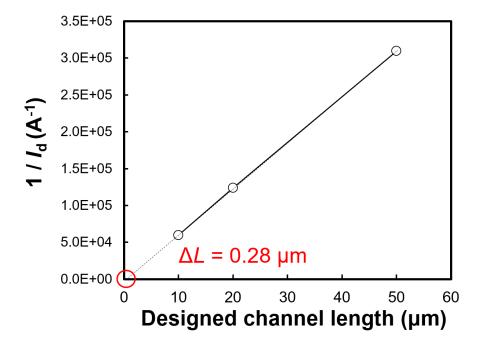

A Gate channel length is an important parameter for analysis of MOS capacitor and MOSFET properties. However, that can fluctuate in patterning process from designed length. Therefore, an effective channel length is need to be extracted for accurate evaluation. By Terada method, measured entire channel resistance is expressed by [2-6]

$$R = R_o + (\rho/W)(L_m + \Delta L) \tag{2.5}$$

Where  $R_o$  is extrinsic resistance,  $\rho$  is channel sheet resistance, W is channel width,  $L_m$  is designed channel length and  $\Delta L$  is the difference between  $L_{eff}$  of effective channel length and  $L_m$ .

Terada plot for effective channel length is shown in Fig. 2.3.4.1. This measurement was performed in SiC MOSFET with thermally grown SiO<sub>2</sub> dielectric.  $\Delta L$  was estimated to be 0.28  $\mu$ m.

Fig. 2.3.4.1 Terada plot at designed channel length of 10, 20 and 50 μm.

### 2.3.5 Field effect mobility extraction

When the transistor is operated in the linear region, where  $V_{ds}$  is small and  $I_d$  increase proportional with  $V_{ds}$ . The field-effect mobility is determined from the transconductance, defined by:

$$g_m = \frac{\partial I_d}{\partial V_{gs}} (V_{ds} = constant)$$

(2.6)

Where  $I_d$  is the drain current,  $V_{gs}$  is the bias voltage between gate and source of MOSFET, and  $V_{ds}$  is the bias voltage between drain and source. The drift component of the drain current with  $Q_n = C_{ox}(V_{gs} - V_{th})$  is:

$$I_{d} = \frac{W}{L} \mu_{FE} C_{ox} (V_{gs} - V_{th}) V_{ds}$$

(2.7)

When the field-effect mobility is determined, the transconductance can be given as:

$$g_m = \frac{W}{L} \mu_{FE} C_{ox} V_{ds} \tag{2.8}$$

Where W and L are the width and length of the channel,  $C_{ox}$  is the capacitance of gate insulator. When this equation is solved for the mobility, it is known as the field-effect mobility:

$$\mu_{FE} = \frac{Lg_m}{WC_{ox}V_{ds}} \tag{2.9}$$

In this study, the  $V_{ds}$  was control to be 50 mV when measuring the field-effect mobility.

### 2.3.6 X-ray photoelectron spectroscopy (XPS)

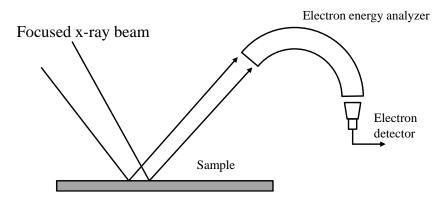

X-ray photoelectron spectroscopy (XPS) is one of the most widely used methods for surface analysis of specimen. When a specimen is irradiated with a soft X-ray corresponding to energy of tens to thousands of eV, electrons are emitted from the core level or valence level. At this time, the emitted electrons are called photoelectron. In order that photoelectrons to be emitted, kinetic energy more than binding energy and work function is required. Since the measured binding energy is the intrinsic energy of the element, the element of the specimen can be analyzed. In addition, the binding energy changes according to the chemical bonding state, information on the chemical bonding state can be obtained. The schematic illustration of XPS measurement is shown in Fig. 2.3.6.1. In this study, XPS measurement was utilized for analysis of Y<sub>2</sub>O<sub>3</sub> and CeO<sub>x</sub> composition after thermal process.

Fig 2.3.6.1 Schematic illustration of XPS measurement.

### 2.3.7 Transmission electron microscope (TEM)

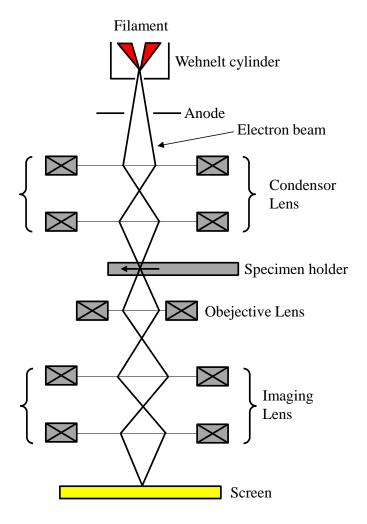

Transmission electron microscopy (TEM) is a famous method for obtain high resolution image by transmit electron beam through ultra-thin specimen. Fig 2.3.7.1 shows the schematic illustration of TEM. TEM is largely composed of 4 parts, these are electron gun, condenser lens, objective lens and detector. When a potential difference is made from filament to anode, an acceleration voltage is generated, which is generally 60 to 300 kV. The generated electron beam is focused and manipulated by condenser lens, which allows desired size and location for the specimen. The electron beam passed through the specimen is converted into an image through the objective lens and imaging lens. At this time, contrast is formed by difference in scattering electrons. In this study, we observed cross section of MOS devices to confirm formation of Y-silicate or CeO<sub>x</sub> gate dielectric by TEM.

Fig 2.3.7.1 Schematic illustration of TEM device structure.

### Reference

- [2-1] Puurunen, Riikka L., "Surface chemistry of atomic layer deposition: A case study for the trimethylaluminum/water process". *J. Appl. Phys.*, 97 pp. 12, (2005)

- [2-2] Lithography Nanopatterning Tutorial, <a href="https://www.sigmaaldrich.com/technical-documents/articles/materials-science/lithography-nanopatterning/tutorial.html">https://www.sigmaaldrich.com/technical-documents/articles/materials-science/lithography-nanopatterning/tutorial.html</a>, SigmaAldrich.

- [2-3] Reactive Ion Etching, <a href="https://www.corial.com/en/technologies/reactive-ion-etching-rie/">https://www.corial.com/en/technologies/reactive-ion-etching-rie/</a>, CORIAL Company.

- [2-4] J. Song, Y. Lin, T. Hoshii, H. Wakabayashi, K. Tsutsui and K. Kakushima, Jpn. J. Appl. Phys., 59, SMMB01 (2020).

- [2-5] Dieter K. Schroder, "Semiconductor material and device characterization", pp. 358-361 (2006).

- [2-6] K. Terada and H. Muta, Jpn. J. Appl. Phys., 18, pp. 953-959 (1979).

# Chapter 3 Atomic layer deposition by Ar multiple boost injection

- 3.1 Deposition with low vapor pressure precursors:  $Y_2O_3$  and  $CeO_x$  film cases

- 3.2 A proposal of Ar-boosted multi-shot process

- 3.3 Film coverage by the number of multi-shot

- 3.3.1 Boost time dependency of growth rate

- 3.3.2 Effect of precursor multi-shot for growth rate

- 3.4 Demonstration of Y-silicate deposition

- 3.5 Summary of chapter 3

Reference

### 3 Atomic layer deposition by Ar multiple boost injection

With low on-resistance advantage, trench type MOSFET is becoming the mainstream of SiC MOS-structure. However, a strong crystallographic orientation dependent oxidation on 3D-gate structure may result in the formation of an uneven SiO<sub>2</sub> layer, which may pose reliability issues. [3-1] On this point, gate dielectrics formed by conformal deposition processes seem to be prominent ways for replacing the thermally grown SiO<sub>2</sub> ones. ALD has been indicated to be a feasible method to form conformal SiO<sub>2</sub> layer on semiconductor surfaces. [3-2] Also, as the ALD process can be performed at low process temperature, the risk of forming carbon deficiency in the sub-surface SiC channel can be reduced. [3-3] However, several materials of precursor have low vapor pressures, it aggravates film coverages on substrates by low growth per cycle. The film coverage is particularly important for interface property, thus it needs to be improved for reliability of devices.

In this chapter, effect of Ar-boosted precursor multi-shot to film coverage for Y<sub>2</sub>O<sub>3</sub> and CeO<sub>x</sub> will be introduced. Additionally, properties of Y<sub>2</sub>O<sub>3</sub> and Y-silicate films deposited by multi-shot process will be also presented.

# 3.1 Deposition with low vapor pressure precursors: $Y_2O_3$ and $CeO_x$ film cases

Y<sub>2</sub>O<sub>3</sub> thin films have wide applications owing to its material properties; a relatively wide bandgap of 5.5 eV, a high relative permittivity of  $\approx$ 15, and a high refractive index of 1.8. Also, the Gibbs free energy of Y<sub>2</sub>O<sub>3</sub> is negatively largest among rare earth oxides, suggesting a stable film property against oxygen vacancy formation. [3-4] Y<sub>2</sub>O<sub>3</sub> thin films can be deposited by various physical vapor depositions (PVD) [3-5,3-6] or chemical vapor depositions (CVD) [3-7,3-8]. With the advent of recent ALD to deposit conformal and pinhole-free thin films, many works have been reported to form Y<sub>2</sub>O<sub>3</sub> films by the ALD method. With this method, a wide range of applications using ALD-Y<sub>2</sub>O<sub>3</sub> has been reported so far, including gate dielectrics for semiconductors (GaAs, graphene and so on) [3-9~15], yttria-stabilized zirconia (YSZ) for fuel cell [3-16~18]. Common precursors used for Y<sub>2</sub>O<sub>3</sub> thin film deposition are cyclopentane (Cp) based molecules; bisisopropylcyclpentadienyl-diisopropylacetamidinate yttrium (Y(<sup>i</sup>PrCp)<sub>2</sub>(N-<sup>i</sup>Pr-amd)) [3-20~221, tris-methylcyclopentadienyl yttirium  $(Y(MeCp)_3)$ [3-15],trisethylcyclopentadienyl yttrium (Y('EtCp)<sub>3</sub>) [3-19,3-23], tris-isopropylcyclopentadienyl yttrium Y(iPrCp)<sub>3</sub> [3-11,3-24]. For oxidant, either H<sub>2</sub>O, ozone or O<sub>2</sub> remote plasma is used to remove the ligands of the precursors and to oxidize the chemisorbed surface Y atoms. CeO<sub>x</sub> has a moderate bandgap of 3.0~3.6 eV and high permittivity of 23~52. CeO<sub>x</sub> is known to control the oxygen partial pressure of the adjacent oxide layer by changing the valence number between 3 and 4, and has been applied to control the  $V_{\rm th}$  of Si MOS devices [3-25,3-26]. In addition, several CeO<sub>x</sub> thin films have also been deposited by ALD with Cp-based precursors.

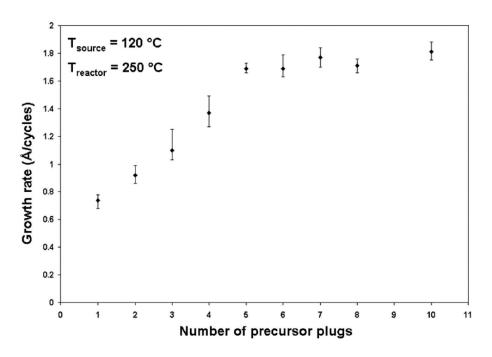

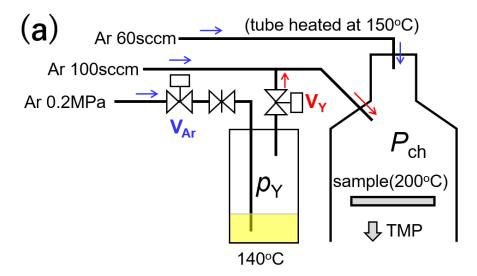

As Cp-based precursors generally exhibit low vapor pressure, several techniques have been utilized to efficiently deliver the gas into the chamber [3-11~15, 3-19]. One way is the exposure mode, where all the inlet and outlet valves of the chamber are close to confine the precursor in the chamber, allowing the surface reaction within the time of the encapsulation. Another way is to bubble the liquid precursors with an inert carrier gas, allowing efficient precursor carrier into the chamber. The usage efficiency of the precursor of the former method is high, but the time for deposition can be long, which is one of the drawbacks of ALD. On the other hand, the sequence of the latter method is simple and one can easily obtain Y<sub>2</sub>O<sub>3</sub> and CeO<sub>x</sub> thin films. The growth per cycle (GPC) of Y<sub>2</sub>O<sub>3</sub> and CeO<sub>x</sub> thin films is reported to be around 0.1 nm/cycle irrespective of any combination of the precursor and the oxidant or deposition method, which is far less than one monolayer of Y<sub>2</sub>O<sub>3</sub> and CeO<sub>x</sub> molecules. Fig. 3.1.1 and 3.1.2 show the general GPC of the Y<sub>2</sub>O<sub>3</sub> and CeO<sub>x</sub> thin films.

Fig. 3.1.1 GPC of Y<sub>2</sub>O<sub>3</sub> films with Y(EtCp)<sub>3</sub> precursor by H<sub>2</sub>O. [3-19]

Fig. 3.1.1 GPC of  $CeO_x$  films with  $Ce(iPrCp)_3$  precursor by  $O_2$  plasma. The temperature of substrate is 250 °C. [3-27]

### 3.2 A proposal of Ar-boosted multi-shot process

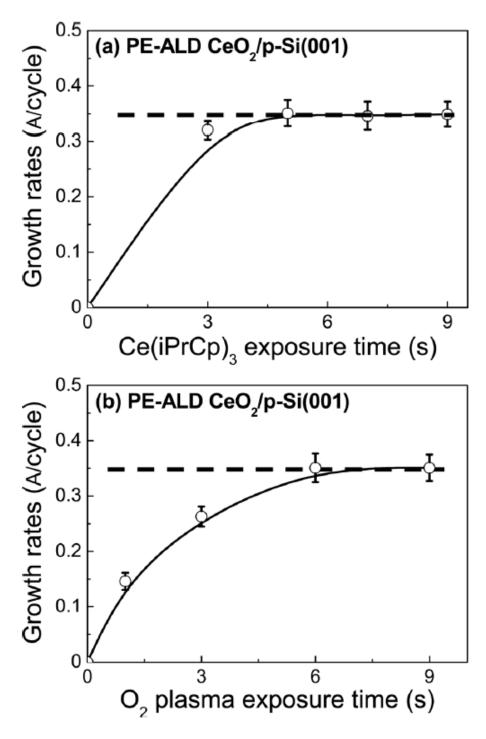

The low GPC values of the Y<sub>2</sub>O<sub>3</sub> and CeO<sub>x</sub> films were presented above section. The efficiency of the precursor usage might be low if the condition of injection is not optimized. Therefore, we will report a high GPC by using multiple boost injection method. The precursors and the oxidant are Y(<sup>1</sup>PrCp)<sub>3</sub>, Ce(<sup>1</sup>PrCp)<sub>3</sub> and remote oxygen plasma, respectively. Fig. 3.2.1 (a) shows the schematic structure of the ALD system used in this study. Three Ar lines, one is to purge the surface of the sample which is directly connected to the chamber, and another is for precursor delivery, and the other one is the boost line, connected to the precursor cylinder for bubbling, is used for the multiple boost injection. All the gas lines were heated to 150 °C to avoid any condensation of the precursor during the cycle process. The reactor chamber temperature was maintained at 200 °C which is lower than the decomposition temperature of the precursor. The mass flow rates for Ar purge and precursor delivery lines were 60 and 100 sccm, respectively. During the process, Ar gas through both purge and precursor delivery is supplied, and with the control of conductance of the turbo molecular pump (TMP), the chamber pressure is set to 77 Pa. With this high chamber pressure, one can expect a conformal deposition of the films into trench structures with a high aspect ratio. The cylinder of the precursor was kept at 140 °C. At this temperature, the vapor pressure of the precursor is less than 20 Pa and this value is lower than the chamber pressure, so one cannot expect any precursor delivery with this setup. The inner pressure of the cylinder can be pressurized slowly by controlling the Ar boost valve (V<sub>Ar</sub>) in the boost line through a needle valve which is set just after V<sub>Ar</sub>. After pressurizing the cylinder higher than the chamber pressure, the V<sub>Ar</sub> is closed, and then the injection valve  $(V_Y)$  can introduce the precursors effectively into the chamber. A simple model based on equation (3-1) suggests a high precursor delivery efficiency of

almost 100 % if the cylinder is pressurized to 0.2 MPa.

$$\eta = 1 - \frac{P_{ch}}{P_V + P_{Ar}} \tag{3.1}$$

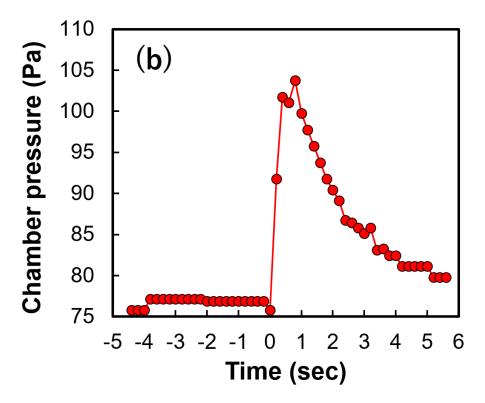

Fig. 3.2.2 (b) shows a typical chamber pressure after injection of the precursor by  $V_Y$  for 1 sec. One can see the injection of mixed gas from the cylinder even for a high base pressure (77 Pa) of the chamber. The decay of the pressure was less than 10 s. By repeating the  $V_{Ar}$  and  $V_Y$  sequence several times before remote oxygen plasma treatment, we can deliver the precursor into the chamber by multiple injections.

For sample preparation, the cleaned Si substrates were set into the chamber for 30 min to reach the temperature of  $200^{\circ}$ C before deposition. The Ar boost gas was injected into the cylinder first before the precursor is injected into the chamber. With our setup, the cylinder pressure was 0.17 and 0.2 MPa for the  $V_{Ar}$  opening time of 1 and 20 s, respectively. After closing  $V_{Ar}$  the mixed gas in the pressurized cylinder was released into the chamber by opening the  $V_Y$ . The injection time of the precursor, the opening time of  $V_Y$  was fixed to 5 s per cycle. The chemisorbed precursor on the surface of the substrates was oxidized by  $O_2$  remote plasma. The  $O_2$  plasma was radiated for 20 s per each cycle with an RF power of 300 W.

$p_{Y}$ : vapor pressure of the precursor  $P_{ch}$ : chamber pressure

Fig. 3.2.1 (a) Schematic structure of ALD system assisted by Ar boost. (b) The chamber pressure after the Y(<sup>i</sup>PrCp)<sub>3</sub> precursor injection with 0.5 second-boost.

### 3.3 Film coverage by the number of multi-shot

### 3.3.1 Boost time dependency of growth rate

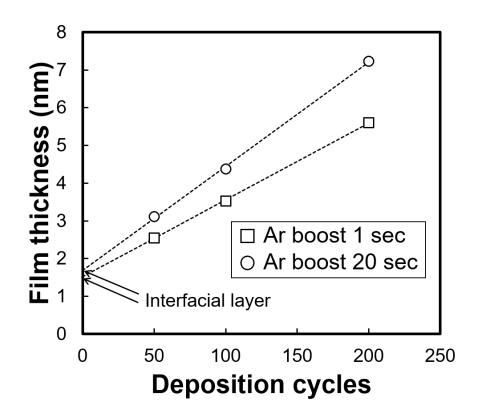

Firstly, for the Y<sub>2</sub>O<sub>3</sub> films, the film thicknesses on different cycles, 50 to 200 cycles, with V<sub>Ar</sub> opening time of 1 s (a cylinder pressure of 0.17 MPa) or 20 s (a cylinder pressure of 0.2 MPa) are shown in Fig. 3.3.1.1. A linear trend in the thickness on the number of cycles is obtained for both conditions. The GPC of the former condition is calculated to be 0.02 nm/cycle from the slope in the thickness-cycle relationship. This GPC value is a typical value for most ALD processes. Under this condition, a precursor dose of 2.1×10<sup>15</sup> cm<sup>-2</sup> can be calculated from the cylinder volume of 100 mL and vapor pressure of 22 Pa deposited on a 6-inch Si wafer. The reactive sticking coefficient of the precursor to the wafer can be calculated as 10<sup>-1</sup>, which is quite high to those for Al<sub>2</sub>O<sub>3</sub> ALD with trimethylaluminum precursor (TMA) of 10<sup>-3</sup>. On the other hand, for the latter case, a GPC of 0.027 nm/cycle was obtained. We can see a small increase in the GPC with higher cylinder pressure. As the pressure of the cylinder is high enough, a  $\eta=1$  can be achieved for both cases. Therefore, the difference in the GPC between the two cases is the difference in the Ar partial pressure. We anticipate that the Ar bombardment to remove the physically adsorbed molecules at the surface may reduce the steric hindrance, resulting to enhance the chemical adsorption and leading to higher coverage. Nevertheless, as the pressure of the Ar gas line connected to the ALD equipment is set to 0.23 MPa, one cannot expect much higher GPC by simply increasing the cylinder pressure.

Fig. 3.3.1.1  $Y_2O_3$  film thickness on cycles for 1 s and 20 s of boost time. The GPC is 0.027 nm/cycle for a boost time of 20 s.

### 3.3.2 Effect of precursor multi-shot for growth rate

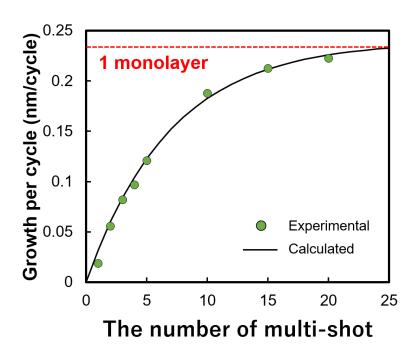

By repeating the set of cylinder pressurization and mixed gas injection into the chamber before oxygen plasma irradiation, a higher dose of the precursor can be exposed to the surface of the substrate. Fig. 3.3.2.1 shows the GPC of the formed Y<sub>2</sub>O<sub>3</sub> films under different numbers of shots. The Y<sub>2</sub>O<sub>3</sub> film thickness increases with the number of shots and shows a saturation to a GPC at 0.22 nm/cycle. The trend of the coverage with the number of shots can be modeled based on the equation,

$$\frac{dQ}{dt} = r_a - r_d = k_a p(1 - Q) - k_d Q, (3.2)$$

where Q is the surface chemisorption coverage and t is the number of multi-shot.  $r_a$  and  $r_d$  are the adsorption and desorption rate, respectively.  $k_a$  and  $k_d$  are the rate constant of adsorption and desorption, respectively and p is the partial pressure of the precursor. Once the coverage is saturated, dQ/dt = 0, we obtain a condition of Langmuir isotherm, showing an equilibrium chemisorption coverage,  $Q^{eq}$ , and equation 2 can be reduced to the following equation [3-28,3-29],

$$Q^{eq} = \frac{k_a p}{k_a p + k_d} = \frac{1}{1 + (Kp)^{-1}} \quad , \tag{3.3}$$

where K is equal to  $k_a/k_d$ . Using equation (2) and (3), the following differential equation is obtained.

$$Q = Q^{eq} (1 - e^{-(k_a p + k_d)t})$$

(3.4)

$Q^{eq}$  of 0.23 nm can be calculated from the monolayer thickness of Y<sub>2</sub>O<sub>3</sub> (a=2.65 Å, cubic) [3-30,3-31]. From numerical fit to the data, a  $k_ap$  and a  $k_d$  of 0.13 and 0.014, respectively, show a good agreement to the obtained GPC for each number of shots. From this relationship, a GPC 0.23 nm/cycle, a monolayer deposition per cycle, can be expected with a larger number of multi-shots.

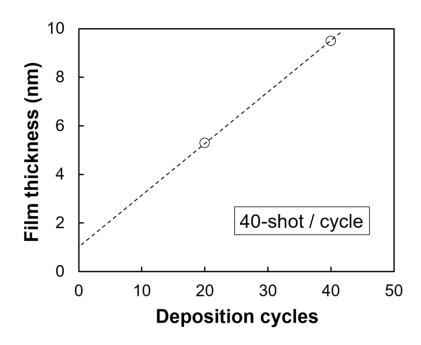

With the same multi-shot condition, the CeOx films were also deposited at precursor temperature of 130 °C. The CeO<sub>x</sub> film thickness by 40-shot per cycle is shown in Fig. 3.3.2.2. The high GPC of 0.21 nm/cycle is obtained as with the Y<sub>2</sub>O<sub>3</sub> films. From this result, multi-shot process is effective for both Y<sub>2</sub>O<sub>3</sub> and CeO<sub>x</sub> films.

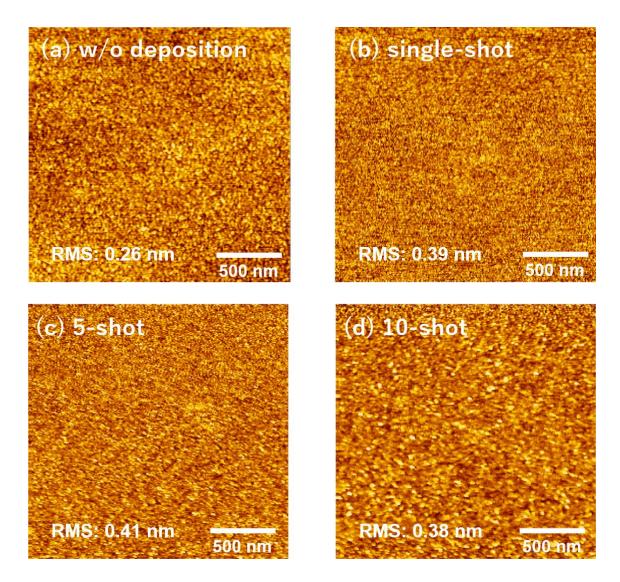

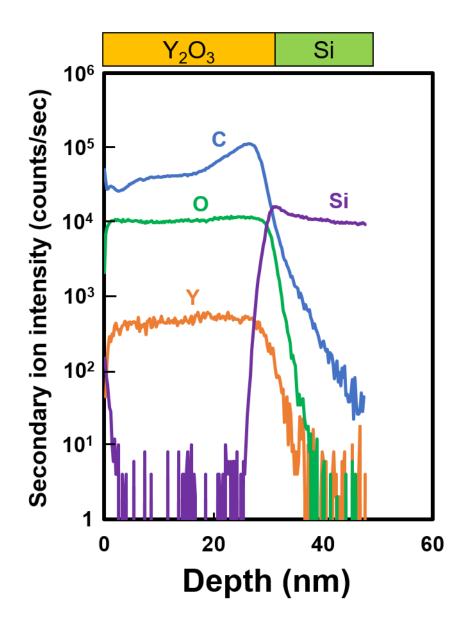

Fig. 3.3.2.3 (a) shows the AFM image of the initial surface of the Si substrate before deposition, where a root-mean-square roughness ( $R_a$ ) is 0.26 nm. Fig. 3.3.2.3 (b)~(d) show the AFM surface images of 5-nm-thick Y<sub>2</sub>O<sub>3</sub> films deposited by single-shot, 5-shot and 10-shot, respectively. The  $R_a$  are obtained as (b) 0.39 nm, (c) 0.41 nm and (d) 0.38 nm. The roughness of the Y<sub>2</sub>O<sub>3</sub> films hardly changes by the number of shots. Therefore, one can shorten the processing time by removing unnecessary oxygen plasma exposure. Fig. 3.3.2.4 shows the SIMS profiles of the Y<sub>2</sub>O<sub>3</sub> film formed by the 10-shot process. A uniform carbon atom distribution was observed throughout the film. An optimized process to reduce the carbon atoms in the film may be needed by changing the oxygen plasma condition; power or oxygen gas flow rate, and so on.

Fig. 3.3.2.1 GPC on the number of multi-shot at an Ar boost of 1 s. The calculated thickness of one monolayer is around 0.23 nm.

Fig. 3.3.2.2  $CeO_x$  film thickness by 40-shot per cycle at an Ar boost of 1 s. GPC is 0.21 nm/cycle.

Fig. 3.3.2.3 AFM images of surface for (a) the initial Si substrate, (b)  $Y_2O_3$  deposited by single-shot, (c)  $Y_2O_3$  deposited by multi-shot (5-shot) and (d)  $Y_2O_3$  deposited by multi-shot (10-shot). The  $Y_2O_3$  thicknesses of (b)~(d) are 5 nm.

Fig. 3.3.2.4 SIMS profiles of the  $Y_2O_3$  film formed by 10-shot (~32 nm).

### 3.4 Demonstration of Y-silicate deposition

Rare earth silicates maintain its amorphous structure under the typical semiconductor process temperature range [3-32], which is advantageous for suppression in the leakage current as well as variability [3-33]. The formation of rare earth silicates is commonly conducted by interface reaction between rare earth oxides and a Si substrate under the thermal process [3-34]. However, the interface reaction can aggravate performance in SiC devices which are sensitive to interface property. One of the ways to inhibit the consumption of SiC substrates is to supply Si atoms into the deposited film, forming silicate without any reaction to the substrates.

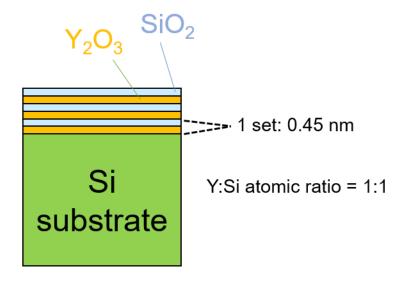

Yttrium silicate (Y-silicate) films, a typical rare-earth silicate [3-35], are formed by cyclic deposition of Y<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> in this section. The formation of stable Y-silicate films can extend a range of application for SiC gate dielectrics. Fig. 3.4.1 shows the schematic structure of Y<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> multi-stacked film. The cycles were determined to have the Y/Si atomic ratio of the stacked-layer to be 1:1 by multi-shot process, and the calculated

Fig. 3.4.1 Schematic structures of Y<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> multi-stacked films.

minimum thickness of the stacked-layer for the target atomic ratio of 1:1 was 0.45 nm. Moreover, the SiO<sub>2</sub> film was deposited with a tris-dimethylamino-silane (TDMAS) precursor. The temperature of chamber reactor was 200°C.

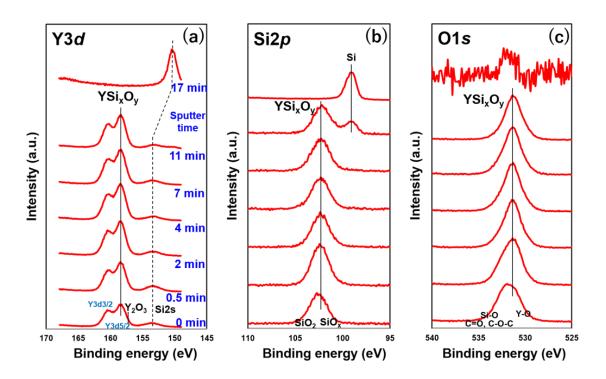

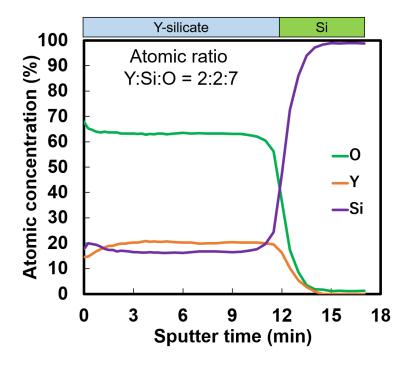

The stacked-layer with a thickness of 35 nm without annealing process was analyzed by x-ray photoelectron spectroscopy (XPS). Fig. 3.4.2 (a), (b) and (c) show the spectra of Y3d, Si2p and O1s core levels of the stacked-layer with different sputtering times. The peaks of Y3 $d_{3/2}$  and Y3 $d_{5/2}$  spectra, located at 160.2 eV and 158.2 eV, respectively, are shifted by 1.4 eV from reference positions of 158.8 eV and 156.8 eV of pure Y<sub>2</sub>O<sub>3</sub> [3-36]. The shift in the binding energy indicates that most of the Y atoms are in the form of silicate. The Si2p peak at 102.2 eV is separated from 103.3 eV (SiO<sub>2</sub>), indicating that the formation of SiO<sub>2</sub> is not apparent. Moreover, the O1s peak at 531.2 eV is also obviously different from the reference peaks of Y<sub>2</sub>O<sub>3</sub> (529.5 eV) and SiO<sub>2</sub> (533.0 eV), suggesting that the stacked layer is readily transformed in the form of Y-silicate during ALD process. This fact is in contrast to the Hf-silicate formation by ALD, where annealing process is required to mediate the Hf-O-Si bonding. The bandgap of the stacked-layer was estimated to be 6.4 eV from O1s loss spectrum, which is attractive for various insulator applications. Fig. 3.4.3 shows the XPS depth profile of the stacked-layer obtained by Ar bombardment. The atomic ratio of Y, Si and O remained constant throughout the film at almost 2:2:7 until the Si substrate appeared. From the results, it is confirmed that a uniform Y-silicate layer with a composition of Y<sub>2</sub>Si<sub>2</sub>O<sub>7</sub> can be obtained by the multi-stacking of Y<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> ALD process.

Fig. 3.4.2 XPS spectra of the  $Y_2O_3/SiO_2$  multi-stacked layer ( $\sim 35$  nm, As depo.) for (a)  $Y_3d$ , (b) Si2p, and (c) O1s regions. The main spectra indicate a Y-O-Si bond.

Fig. 3.4.3 XPS depth profile of the Y<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> multi-stacked layer (~ 35 nm, As depo).

### 3.5 Summary of chapter 3

We investigated the ALD of Y<sub>2</sub>O<sub>3</sub> and CeO<sub>x</sub> films by Ar boost technology. A GPC of 0.02 nm/cycle, a typical value for the Y<sub>2</sub>O<sub>3</sub> ALD, was obtained by the Ar boost. By repeating the Ar boost precursor injection into the chamber, the GPC was found to increase with the number of shots and showed a saturation to 1 monolayer of Y<sub>2</sub>O<sub>3</sub> film. The GPC over the number of shots was well-explained by the adsorption and desorption mode. With 20 multiple shots, the high GPC of 0.22 nm/cycle was achieved. Similarly, the high GPC of 0.21 nm/cycle was obtained in the CeOx films with 40 multiple shots. The films by multiple boot injection did not show any degradation in the surface roughness. Multiple boost injection method has an advantage for effective utilization of the low-vapor pressure precursors for high chamber pressure environment. Finally, Low temperature formation of Y-silicate layer has been confirmed by cyclic deposition of stacked-layer of Y<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> ALD layers.

#### Reference

- [3-1] K. Kakushima, T. Koyanagi, K. Tachi, J. Song, P. Ahmet, K. Tsutsui, N. Sugii, T. Hattori and H. Iwai, J. ECS Trans., 61(2), pp. 135-142 (2014).

- [3-2] R. K. Puurunen, J. Appl. Phys., 97, 121301 (2005).

- [3-3] K. C. Chang, N. T. Nuhfer, and L. M. Porter, Appl. Phys., Lett., 77, pp. 2186-2188 (2000).

- [3-4] J. P. Gaviría, A.E. Bohé, Thermo. Acta. 509, 100 (2010).

- [3-5] J. J. Araiza, M. Cardenas, C. Falcony, V. M. Mendez-Garcia, M. Lopez, G. Contreras-Puente, J. Vac. Sci. Technol. A16, 3305 (1998).

- [3-6] R. H. Horng, D. S. Wuu, J. W. Yu, C. Y. Kung, Thin Solid Films 289, 234 (1998).

- [3-7] W. J. Varhu, M. Massimo, J. M. Carrulli, V. Baranauskas, E. Adams, E. Broitman, Vac. Sci. Technol. A11, 1870 (1993).

- [3-8] R. N. Sharma, A. C. Rastogi, Appl. Phys. Lett. 76, 4215 (1994).

- [3-9] S. Seppälä, J. Niinistö, T. Blanquart, M. Kaipio, K. Mizohata, J. Räisänen, C. Lansalot-Matras, W. Noh, M. Ritala, and M. Leskela, Chem. Mater. 28, 5440 (2016).

- [3-10] E. Ballee, A. Ringuede, M. Cassir, M. Putkonen, L. Niinisto, Chem. Mater. 21, 4614 (2009).

- [3-11] R. Xu, S. K. Selvaraj, N. Azimi, C. G. Takoudis, ECS Trans. 50, 107 (2012).

- [3-12] I.-K. Oh, K. Kim, Z. Lee, K. Y. Ko, C.-W. Lee, S. J. Lee, J. M. Myung, C. Lansalot-Matras, W. Noh, C. Dussarrat, H. Kim, H.-B.-R. Lee, Chem. Mater. 27, 148 (2015).

- [3-13] H. Jung, W.-H. Kim, B.-E. Park, W. J. Woo, I.-K. Oh, S. J. Lee, Y. C. Kim, J.-M.

- Myoung, S. Gatineau, C. Dussarrat, H. Kim, ACS Appl. Mater. Interf. 10, 2143 (2018).

- [3-14] S.Y. Wu, K.H. Chen, Y.H. Lin, C.K. Cheng, C.H. Hsu, J. Kwo, M. Hong, Micro. Eng. 147, 310 (2015).

- [3-15] J. Niinisto, M. Putkonen, L. Niinisto, Chem. Mater. 16, 2953 (2004).

- [3-16] B.-E. Park, I.-K. Oh, C. Mahata, C. W. Lee, D. Thompson, H. -B. –R. Lee, W. J. Maeng, H. Kim, Alloys and Comp. 722, 307 (2017).

- [3-17] J. H. Shim, C.-C. Chao, H. Huang, F. B. Prinz, Chem. Mater. 19, 3850 (2007).

- [3-18] K. Bae, K. S. Son, J. W. Kim, S. W. Park, J. An, F. B. Prinz, J. H. Shim, Hydro. Energy 39, 2621 (2014).

- [3-19] P. Majumder, G. Jursich, A. Kueltzo, C. Takoudis, Journal of the ECS. 155, G152 (2008).

- [3-20] J.-S. Lee, W.-H. Kim, I.-K. Oh, M.-K. Kim, G. Lee, C.-W. Lee, J. Park, C. Lansalot-Matras, W. Noh, H. Kim, Appl. Surf. Sci. 297, 16 (2014).

- [3-21] I.-S. Park, Y. C. Jung, S. Seong, J. Ahn, J. Kang, W. Noh, C. Lansalot-Matras, Mater. Chem. 2, 9240 (2014).

- [3-22] J. H. Kang, Y. C. Jung, S. S., T. Lee, J. Ahn, W. Noh, I. S. Park, Mater. Sci. Semi. Proc. 63, 279 (2017).

- [3-23] L. Lecordier, ECS Trans. 69 (7), 109 (2015).

- [3-24] R. Sparks, G. Jursich, A. Zdunek, J. I. Rossero, C. G. Takoudis, J. Underg. Research 7, 32 (2014).

- [3-25] M. Mamatrishat, M. Kouda, K. Kakushima, H. Nohira, P. Ahmet, Y. Kataoka, A. Nishiyama, K. Tsutsui, N. Sugii, K. Natori, T. Hattori, H. Iwai, Vacuum, 86, pp. 1513-1516 (2012).

- [3-26] N. Umezawa, Appl. Phys. Lett., 96, 162906 (2010).

- [3-27] W. Kim, M. Kim, W. J. Maeng, J. Gatineau, V. Pallem, C. Dussarrat, A. Noori, D. Thompson, S. Chu and H. Kim, J. Elec. Soc., 158, pp. G169-G172 (2011).

- [3-28] S. Azizian, S. Eris, Lee D. Wilson, Chem. Phys. 513, 99 (2018).

- [3-29] R. L. Puurunen, J. Appl. Phys. 97, 121301 (2005).

- [3-30] R.J. Gaboriaud, F. Paumier, B. Lacroix, Thin Solid Films 601, 84 (2016).

- [3-31] L. J. Alvarez, M. A. S. Miguel, J. A. Odriozola, Phys. Rev. B. 59, 17, 303 (1999).

- [3-32] J. S. Jur, D. J. Lichtenwalner, A. I. Kingon, Appl. Phys. Lett. 90, 102908 (2007).

- [3-33] A. Bayeral, M. Lanza, M. Porti, F. Campabadal, M. Nafria, X. Aymerich, G. Benstetter, Microelectron. Eng. 88, 1334 (2011).

- [3-34] K. Kakushima, K. Tachi, M. Adachi, K. Okamoto, S. Sato, J. Song, T. Kawanago, P. Ahmet, K. Tsutsui, N. Sugii, T. Hattori, H. Iwai, Solid-State Electron. 54, 715 (2010).

- [3-35] D. Niu, W. Ashcraft, Appl. Phys. Lett. 81, 676 (2002).

- [3-36] J. J. Chambers, G. N. Parsons, J. Appl. Phys. 90, 918 (2001).

# Chapter 4 SiC MOS devices with an Y-silicate interface layer

- 4.1 XPS analysis for Y-silicate film on SiC substrate

- 4.2 Thickness of Y-silicate layer on electrical property

- 4.3 Process temperature of Y-silicate interface layer

- 4.4 Interface property with a flat Y-silicate interface layer

- 4.5 Mobility of MOS transistors with a flat Y-silicate interface layer

- 4.6 Summary of chapter 4

Reference

### 4 SiC MOS devices with an Y-silicate interface layer

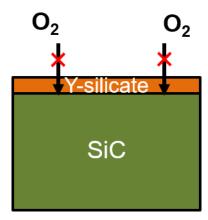

The antioxidation property of Y-silicate to SiC was described in chapter 1.3.1. This property is also suitable for SiC MOS which is sensitive to interface oxidation. The schematic illustration is shown in Fig. 4.1.

In this chapter, we present the electrical characteristics of 4H-SiC MOS devices with the Y-silicate interface layer.

Fig. 4.1 Schematic illustration of oxidation inhibition by Y-silicate layer.

### 4.1 XPS analysis for Y-silicate film on SiC substrate

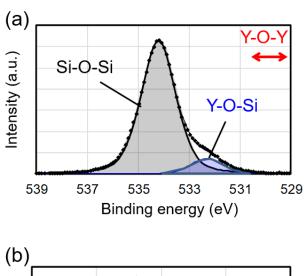

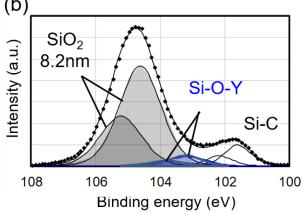

Fig. 4.1.1 shows O1s and Si2p spectra of the Y<sub>2</sub>O<sub>3</sub> (3 nm)/SiC sample after annealing at 1000°C for 30 min in N<sub>2</sub>. The take-off angle is 90°. In O1s spectra as shown in Fig. 4.1.1 (a), Y-O-Y bonding does not appear. Y<sub>2</sub>O<sub>3</sub> is all transformed into Y-silicate in annealing. On the other hand, Si-O-Si bondings are revealed in both O1s and Si2p spectra, a thick SiO<sub>2</sub> of 8.2 nm is formed at the interface. This SiO<sub>2</sub> layer may be due to oxygen radicals of Y<sub>2</sub>O<sub>3</sub> layer, therefore, a Y-silicate layer is needed to be formed by SiO<sub>2</sub>/Y<sub>2</sub>O<sub>3</sub> stacked film in ALD process before annealing.

Fig. 4.1.1 (a) O1s and (b) Si2p spectra of Y<sub>2</sub>O<sub>3</sub> (3 nm)/SiC after annealing at 1000°C for 30 min in N<sub>2</sub>.

### 4.2 Thickness of Y-silicate layer on electrical property

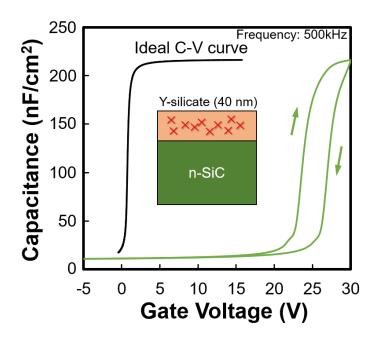

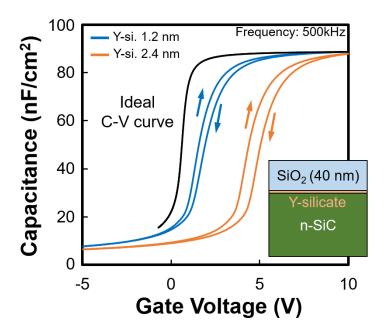

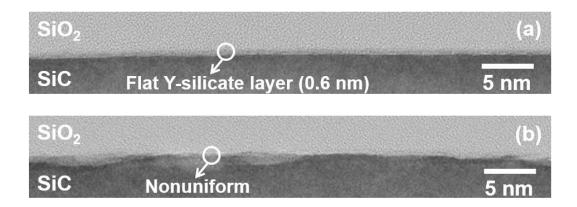

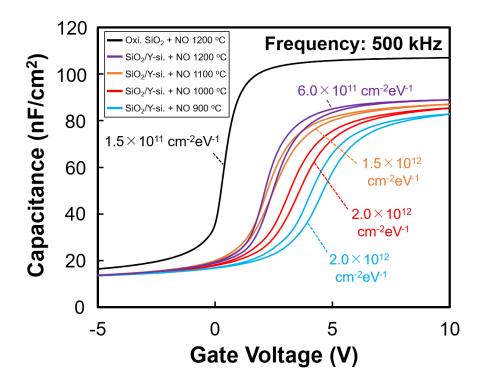

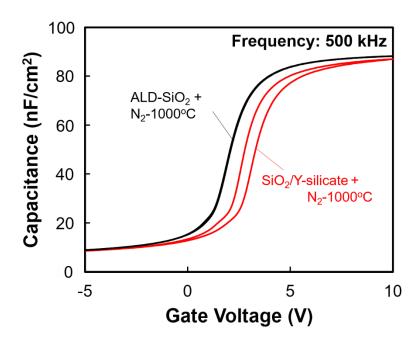

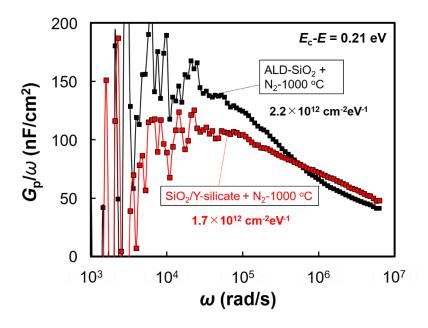

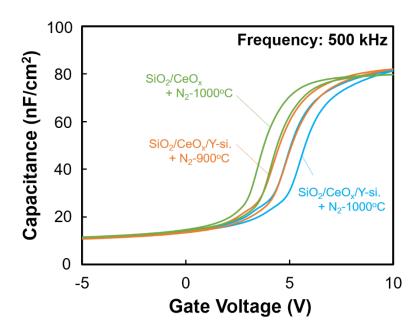

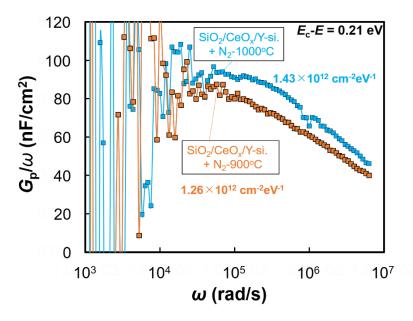

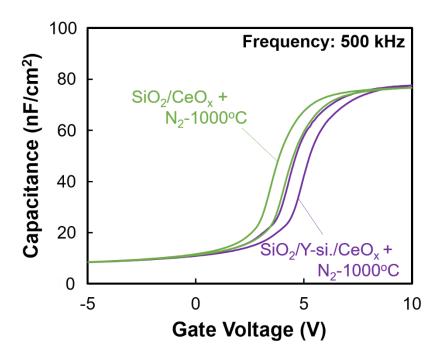

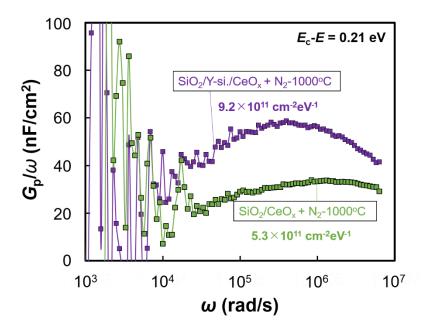

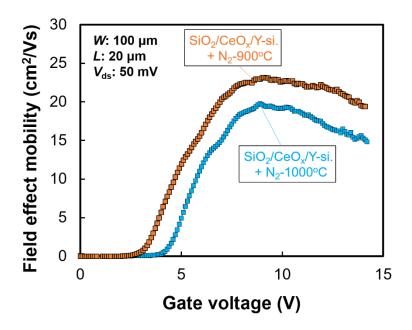

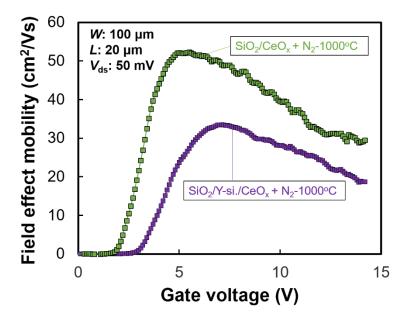

For investigation of pure Y-silicate dielectric property, a 40 nm-thick Y-silicate dielectric layer was deposited on a SiC substrate substitute for SiO<sub>2</sub> dielectric. The Y-silicate layer was formed by cyclic deposition of SiO<sub>2</sub>/Y<sub>2</sub>O<sub>3</sub> stacked layer, thus a Y<sub>2</sub>Si<sub>2</sub>O<sub>7</sub> layer was already formed in ALD process. Fig 4.2.1 shows the C-V characteristic of the MOS capacitor with 40 nm-thick Y-silicate layer. PDA was performed at 1200°C for 90 min with NO gas. Compared with ideal C-V curve, the V<sub>fb</sub> is significantly shifted to positive direction, and the hysteresis voltage (V<sub>hys</sub>) is also large. This electrical degradation may be caused by large oxide traps or negative fixed charges in the Y-silicate layer.