# T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

## 論文 / 著書情報 Article / Book Information

| 題目(和文)            | SiC-MOSFETを使用した大容量双方向絶縁形DC-DCコンバータの損失<br>低減に関する研究                                                                                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | Study of Power-Loss Reduction in High-Power Bidirectional Isolated DC-DC Converters Using SiC-MOSFETs                                                                                           |

| 著者(和文)            | 羽根田崚                                                                                                                                                                                            |

| Author(English)   | Ryo Haneda                                                                                                                                                                                      |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第12081号,<br>授与年月日:2021年9月24日,<br>学位の種別:課程博士,<br>審査員:藤田 英明,千葉 明,萩原 誠,竹内 希,清田 恭平,和田 圭二                                                                      |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第12081号,<br>Conferred date:2021/9/24,<br>Degree Type:Course doctor,<br>Examiner:,,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                            |

| Type(English)     | Doctoral Thesis                                                                                                                                                                                 |

## 東京工業大学工学院電気電子系

# << 博 士 論 文 >>

# SiC-MOSFET を使用した 大容量双方向絶縁形 DC-DC コンバータの 損失低減に関する研究

令和3年9月

指導教員 藤田 英明 教授

提 出 者

コース 電気電子コース

氏名 羽根田 崚

# 目次

| 第1章   | 序論    |                                    | 1  |

|-------|-------|------------------------------------|----|

| 1.1   | 本研究   | その背景                               | 1  |

|       | 1.1.1 | 双方向絶縁形 DC-DC コンバータ(DAB コンバータ)の名称と効 |    |

|       |       | 率評価の意義                             | 1  |

|       | 1.1.2 | パワー半導体素子と磁気デバイスの低損失化の技術動向          | 3  |

|       | 1.1.3 | 電力損失分離の必要性と課題                      | 5  |

|       | 1.1.4 | DAB コンバータの技術課題と解決策                 | 7  |

| 1.2   | 本研究   | での目的と成果                            | 8  |

|       | 1.2.1 | 本研究の目的                             | 8  |

|       | 1.2.2 | 本研究の成果                             | 9  |

| 1.3   | 本論文   | 大の構成                               | 10 |

| 第 2 章 | DAB : | コンバータの技術動向                         | 13 |

| 2.1   | DAB   | コンバータの回路方式                         | 13 |

|       | 2.1.1 | 単相 DAB コンバータ                       | 13 |

|       | 2.1.2 | 三相 DAB コンバータ                       | 14 |

|       | 2.1.3 | 直列共振 DAB コンバータ                     | 17 |

|       | 2.1.4 | DAB コンバータの回路方式の比較                  | 18 |

| 2.2   | DAB   | コンバータの電力変換効率の動向                    | 19 |

| 2.3   | DAB   | コンバータの損失低減に向けた課題                   | 22 |

|       | 2.3.1 | ZVS の動作原理とターンオン損失の発生原理             | 22 |

|       | 2.3.2 | <b>ZVS</b> 時のターンオフ損失の発生原理          | 25 |

| 2.4   | ZVS   | 時のスイッチング損失の測定                      | 27 |

|       | 2.4.1 | 全損失・変換効率の測定誤差                      | 29 |

ii 目次

|     | 2.4.2 | 電流検出遅れによるターンオフ損失の測定誤差                       | 30 |

|-----|-------|---------------------------------------------|----|

|     | 2.4.3 | ターンオフ損失と測定可能なエネルギーの関係                       | 30 |

| 2.5 | 軽負荷   | 「時や昇降圧動作時の低損失化                              | 32 |

|     | 2.5.1 | レグ間位相シフト                                    | 32 |

|     | 2.5.2 | 間欠運転                                        | 33 |

| 2.6 | 本章の   | )まとめ                                        | 34 |

| 第3章 | スイッ   | チング損失の分離                                    | 37 |

| 3.1 | 実験シ   | ·ステム                                        | 37 |

|     | 3.1.1 | システム構成                                      | 37 |

|     | 3.1.2 | 全損失と変換効率の定義                                 | 40 |

|     | 3.1.3 | 変換効率                                        | 40 |

| 3.2 | 実験結   | 課                                           | 40 |

|     | 3.2.1 | $v_L, v_{\mathrm{tr}}, i_{\mathrm{m}}$ の測定法 | 40 |

|     | 3.2.2 | 実験波形                                        | 41 |

| 3.3 | 損失分   | 離                                           | 42 |

|     | 3.3.1 | 概要                                          | 43 |

|     | 3.3.2 | Step 1: 配線抵抗損失                              | 44 |

|     | 3.3.3 | Step 2: 変圧器鉄損                               | 44 |

|     | 3.3.4 | Step 3: インダクタ鉄損                             | 45 |

|     | 3.3.5 | Step 4: 抵抗損失とスイッチング損失の分離                    | 48 |

|     | 3.3.6 | Step 5: 導通損失, 銅損, 未知損失の算出                   | 48 |

|     | 3.3.7 | 結果と考察                                       | 50 |

| 3.4 | スイッ   | チング損失の測定誤差                                  | 51 |

|     | 3.4.1 | 電流・電圧の瞬時値積による直接測定                           | 51 |

|     | 3.4.2 | 提案する全損失からの損失分離                              | 51 |

| 3.5 | スイッ   | チング損失の分離                                    | 52 |

|     | 3.5.1 | Bridge 1, 2 のスイッチング電流の比較                    | 52 |

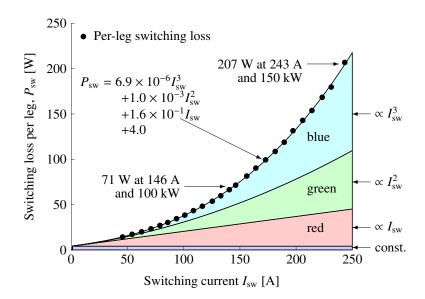

|     | 3.5.2 | スイッチング損失とスイッチング電流の関係                        | 53 |

|     | 3.5.3 | スイッチング損失と直流電圧の関係                            | 55 |

| 3.6 | 温度に   | よる損失測定と比較                                   | 58 |

|     | 3.6.1 | 温度による SiC モジュールの損失測定                        | 58 |

目次

|                    | 3.6.2 分離結果と温度による測定値の比較                        | 61  |

|--------------------|-----------------------------------------------|-----|

| 3.7                | 本章のまとめ                                        | 64  |

| 第4章                | 軽負荷時の損失低減                                     | 67  |

|                    |                                               | _   |

| 4.1                | 効率測定用のテストベンチ                                  | 67  |

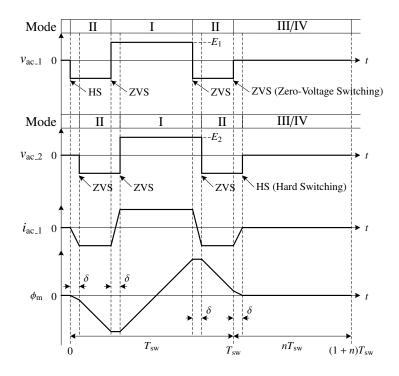

| 4.2                | 連続運転の動作原理・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 69  |

| 4.3                | 実現可能な間欠運転の4種類の制御法                             | 70  |

| 4.4                | 電流不連続モード (DCM) 間欠運転                           | 72  |

| 4.5                | 電流連続モード (CCM) 間欠運転                            | 73  |

|                    | 4.5.1 DCM, CCM 間欠運転と研究業績との対応関係                | 73  |

|                    | 4.5.2 CCM 間欠運転の動作原理                           | 74  |

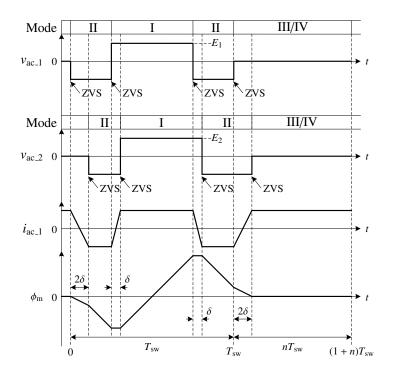

| 4.6                | スイッチング損失の推定                                   | 75  |

| 4.7                | 最適なスイッチング周波数の選定                               | 76  |

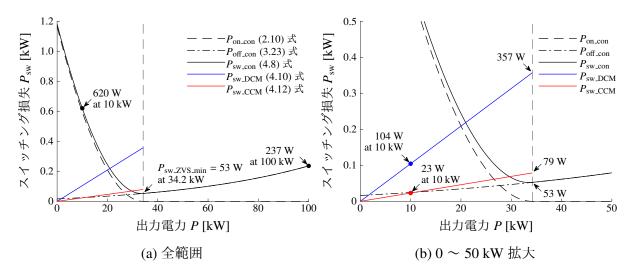

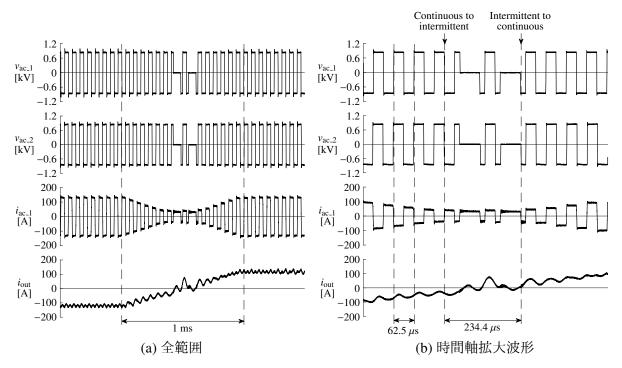

| 4.8                | 実験波形と変換効率.................................... | 78  |

|                    | 4.8.1 実験波形                                    | 78  |

|                    | 4.8.2 全損失と変換効率                                | 81  |

| 4.9                | 間欠運転による広範囲な出力領域の高効率化                          | 83  |

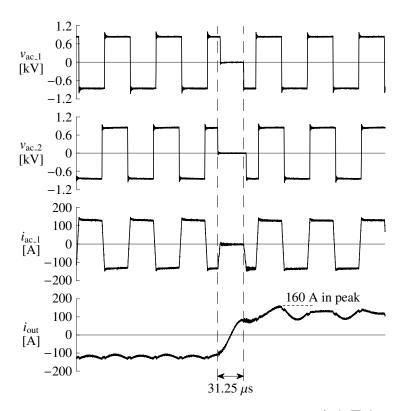

| 4.10               | 過渡特性                                          | 84  |

| 4.11               | 間欠運転時の電圧リプル                                   | 87  |

|                    | 4.11.1 実験検討                                   | 87  |

|                    | 4.11.2 理論検討                                   | 87  |

| 4.12               | 間欠運転時の騒音                                      | 88  |

| 4.13               | 変換効率の動向と将来予測                                  | 89  |

| 4.14               | 本章のまとめ                                        | 92  |

| 第5章                | 昇降圧動作時の損失低減                                   | 95  |

| カラ <u>キ</u><br>5.1 | 一般的な位相シフト制御の動作原理                              | 9:  |

| 3.1                |                                               |     |

|                    | 5.1.1 ブリッジ間の位相シフト制御 (Method I)                | 96  |

|                    | 5.1.2 高圧側ブリッジのレグ間位相シフト制御 (Method II)          | 9'  |

| 5.2                | 昇降圧動作時の効率測定用のテストベンチ                           | 99  |

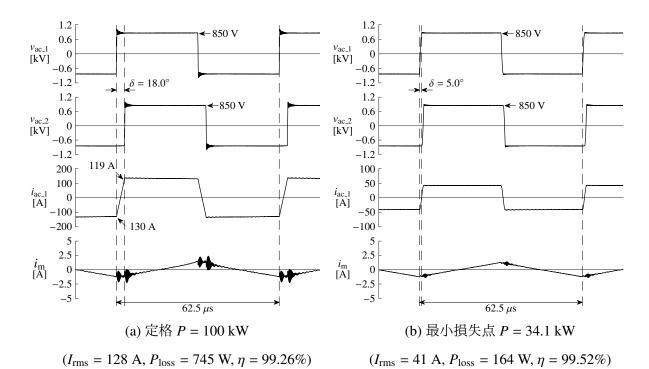

| 5.3                | 実験波形                                          | 100 |

| 5.4                | 損失分離の手順                                       | 102 |

|                                         | 目次     |

|-----------------------------------------|--------|

| インダクタ鉄損          損失分離結果          本章のまとめ | 104    |

| 結論                                      | 107    |

| 本研究の成果                                  | 107    |

| 本研究の技術的意義                               | 109    |

| 今後の展望                                   | 109    |

| 武                                       | 111    |

| 責                                       | 125    |

|                                         | 127    |

|                                         | 損失分離結果 |

# 表目次

| 1.1 | スイッチング損失の測定・推定法の比較                                                            | 6   |

|-----|-------------------------------------------------------------------------------|-----|

| 2.1 | 図 2.1 の 3 種類の DAB コンバータの回路方式による比較                                             | 18  |

| 3.1 | 図 3.1 の 750-V 100-kW 16-kHz DAB コンバータの実験定数                                    | 38  |

| 3.2 | 図 3.1 の 750-V 100-kW 16-kHz DAB コンバータの冷却システム                                  | 39  |

| 3.3 | 1.2-kV 400-A SiC-MOSFET/SBD 4-in-1 モジュールの電気的特性(三菱電                            |     |

|     | 機,FMF400BX-24A) [97]                                                          | 39  |

| 3.4 | 図 3.4 のインダクタ鉄損(1 個当たり)の推定値の比較                                                 | 47  |

| 3.5 | $E_1$ = $E_2$ = 650 V, 750 V, 850 V, $f_{ m sw}$ = 16 kHz での分離したレグ当たりのス       |     |

|     | イッチング損失の比較                                                                    | 55  |

| 3.6 | 図 3.14 の $E_1 = E_2 = 650$ V, 750 V, 850 V, $f_{sw} = 16$ kHz でのスイッチング        |     |

|     | 電流 $I_{\text{sw}} = 150~\text{A}$ で等しい場合の実験値の比較                               | 56  |

| 3.7 | $E_1 = E_2 = 750$ V, $100$ kW, $16$ kHz, $I_{\rm rms} = 147$ A での温度から測定した SiC |     |

|     | モジュールの損失                                                                      | 62  |

| 3.8 | 図 3.23 の $E_1 = E_2 = 750$ V, $100$ kW, $16$ kHz でのサージ振動に起因する損失               | 64  |

| 4.1 | 図 4.1 の 850-V 100-kW 16-kHz DAB コンバータの実験定数                                    | 68  |

| 4.2 | $E_1 = E_2 = 850 \text{ V}, P = 100 \text{ kW}$ でのスイッチング周波数変化時の変換効率           |     |

|     | の比較                                                                           | 76  |

| 4.3 | 100-kW DAB コンバータの変換効率の比較と将来予測                                                 | 89  |

| 5.1 | 図 5.4 の 100-kW 16-kHz DAB コンバータの実験定数                                          | 100 |

| 5.2 | ブリッジ間の位相シフト制御適用時と高圧側ブリッジ (Method I) のレグ                                       |     |

|     | 間位相シフト制御 (Method II) 適用時の $E_1$ = 750 V, $E_2$ = 850 V, 100 kW,               |     |

|     | 16 kHz での実験値比較                                                                | 105 |

# 図目次

| 1.1  | DAB コンバータの基本回路(変圧器巻数比 1:1)                                       | 2  |

|------|------------------------------------------------------------------|----|

| 1.2  | DAB コンバータの直流-直流変換効率 99.3%の意義                                     | 2  |

| 1.3  | 重量 26 kg の珪素鋼板を使用した単相 100-V 3-kVA 50-Hz 変圧器(左側)                  |    |

|      | と重量 11 kg のファインメットを使用した単相 750-V 100-kVA 16-kHz 変                 |    |

|      | 圧器(右側)の外観                                                        | 4  |

| 1.4  | 2 種類の全損失の測定法                                                     | 6  |

| 1.5  | DAB コンバータの昇圧動作時 ( $E_1 < E_2$ ) の入出力のブリッジ変換器の損                   |    |

|      | 失の関係(変圧器巻数比 1:1)                                                 | 7  |

| 2.1  | 3 種類の代表的な DAB コンバータの回路方式(変圧器巻数比 1:1)                             | 14 |

| 2.2  | 図 2.3 に関する単相 DAB コンバータ                                           | 15 |

| 2.3  | 図 2.2 の単相 DAB コンバータの $E_1 = E_2$ での理論波形の一例                       | 15 |

| 2.4  | 図 2.5 に関する三相 DAB コンバータ                                           | 16 |

| 2.5  | 図 2.4 の三相 DAB コンバータの $E_1 = E_2$ での理論波形の一例                       | 16 |

| 2.6  | 図 2.7 に関する直列共振 DAB コンバータ                                         | 17 |

| 2.7  | 図 2.6 の直列共振 DAB コンバータの $E_1 = E_2$ での理論波形の一例                     | 17 |

| 2.8  | 大容量(10 kW 以上)DAB コンバータの定格時の直流-直流電力変換効率                           |    |

|      | の動向                                                              | 20 |

| 2.9  | 図 2.2 の出力電力変動時と負荷電圧変動時の理論波形                                      | 22 |

| 2.10 | 図 2.2 の DAB コンバータの Bridge 1 のデッドタイム期間前後の動作モード                    | 23 |

| 2.11 | 図 2.10 の MOSFET $Q_2$ , $Q_3$ のドレイン-ソース間電圧の理論波形                  | 24 |

| 2.12 | 図 2.2 の Bridge 1 の Q <sub>1</sub> , Q <sub>4</sub> ターンオフ前後の動作モード | 26 |

| 2.13 | 図 2.12 の $Q_1$ ターンオフ時の理論波形                                       | 27 |

| 2.14 | 2 種類の電力変換効率の測定法                                                  | 29 |

| 2.15 | 図 2.12 で電流検出遅れが発生した場合の理論波形                                                               | 31 |

|------|------------------------------------------------------------------------------------------|----|

| 2.16 | 図 2.15 の電流検出遅れに対する ZVS 時のターンオフ損失の測定誤差                                                    | 31 |

| 2.17 | 図 $2.2$ の $E_1 < E_2$ での入出力の両方のブリッジのレグ間位相シフト制御適                                          |    |

|      | 用時の理論波形                                                                                  | 32 |

| 2.18 | 間欠運転の制御概念                                                                                | 33 |

| 3.1  | $E_1 = E_2 = E$ での 750-V 100-kW 16-kHz DAB コンバータのテストベンチ                                  | 38 |

| 3.2  | 図 3.1 のテストベンチと測定機器の外観                                                                    | 39 |

| 3.3  | 図 $3.1$ の $v_L, v_{tr}$ の測定環境                                                            | 41 |

| 3.4  | 図 3.1 の $E_1 = E_2 = 750 \mathrm{V}$ でのターンオフ時の電流を等しく設定した場合                               |    |

|      | の実験波形                                                                                    | 42 |

| 3.5  | $E_1=E_2$ での損失分離手順 $\dots$                                                               | 43 |

| 3.6  | 正弦波でのインダクタ・変圧器の誘導起電力,励磁電流の理論波形                                                           | 44 |

| 3.7  | センダストインダクタのインピーダンス,位相の周波数特性                                                              | 46 |

| 3.8  | $E_1 = E_2 = 750$ V, $P = 100$ kW, $f_{\rm sw} = 16$ kHz での損失分離結果                        | 49 |

| 3.9  | $E_1=E_2=750$ V, $f_{\mathrm{sw}}=16$ kHz での出力電力に対する全損失と損失分離結果                           | 50 |

| 3.10 | $E_1 = E_2 = 750 \text{ V}, f_{\text{sw}} = 16 \text{ kHz}$ での出力電力に対する Bridge 1, 2 のスイッ  |    |

|      | チング電流                                                                                    | 52 |

| 3.11 | 図 3.1 の $E_1 = E_2 = 750$ V, $f_{sw} = 16$ kHz での位相シフト期間の時間軸拡大                           |    |

|      | 波形                                                                                       | 53 |

| 3.12 | $E_1=E_2=750~ m V$ , $f_{ m sw}=16~ m kHz$ でのスイッチング電流に対する分離したレ                           |    |

|      | グ当たりのスイッチング損失                                                                            | 54 |

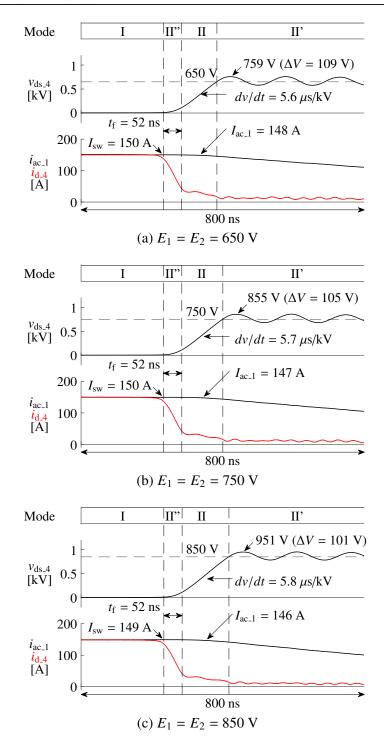

| 3.13 | 図 3.1 の MOSFET $Q_4$ のドレイン-ソース間電圧 $v_{ds\_4}$ とドレイン電流 $i_{d\_4}$ .                       | 56 |

| 3.14 | $I_{\rm sw}$ = 150 A, $f_{\rm sw}$ = 16 kHz での Bridge 1 の MOSFET Q <sub>4</sub> ターンオフ時のド |    |

|      | レイン-ソース間電圧とドレイン電流の実験波形                                                                   | 57 |

| 3.15 | 図 3.14 の Mode II の等価回路                                                                   | 58 |

| 3.16 | 図 3.1 のテストベンチの SiC モジュール,ヒートシンク,冷却ファン,                                                   |    |

|      | サーミスタの配置                                                                                 | 59 |

| 3.17 | SiC モジュールの温度-損失特性の測定回路                                                                   | 59 |

| 3.18 | 図 3.17 で測定した SiC モジュールの温度-損失特性                                                           | 59 |

| 3.19 | 図 3.17 で測定した SiC モジュールのオン抵抗と導通損失の温度依存性 .                                                 | 60 |

図目次 ix

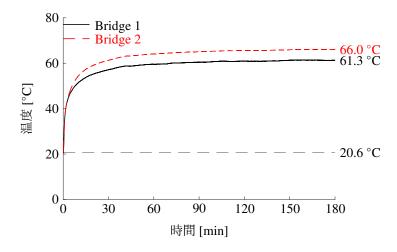

| 3.20 | $E_1 = E_2 = 750 \text{ V}, 100 \text{ kW}, 16 \text{ kHz}$ での $3$ 時間の連続運転試験時の SiC モ                                                   |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------|----|

|      | ジュールの温度                                                                                                                                | 60 |

| 3.21 | 図 3.8 の $E_1 = E_2 = 750$ V, $100$ kW, $16$ kHz での周波数に比例する損失の内訳                                                                        | 62 |

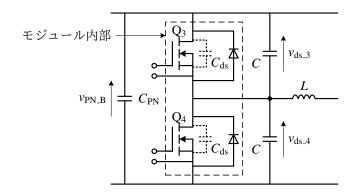

| 3.22 | 図 3.1 の $Q_4$ のドレイン-ソース間電圧 $v_{ds.4}$ と Leg B の PN 間電圧 $v_{PN.B}$ .                                                                    | 63 |

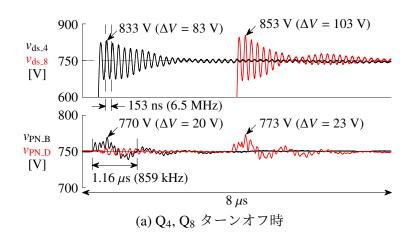

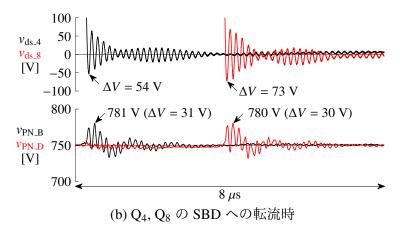

| 3.23 | 図 3.1 の $E_1 = E_2 = 750$ V, $16$ kHz, $100$ kW での $Q_4$ , $Q_8$ スイッチング時の                                                              |    |

|      | ドレイン-ソース間電圧と PN 間電圧の実験波形                                                                                                               | 63 |

| 4.1  | $E_1 = E_2 = E$ での 850-V 100-kW 16-kHz DAB コンバータのテストベンチ                                                                                | 68 |

| 4.2  | 双方向絶縁形 DC-DC コンバータの基本回路構成                                                                                                              | 69 |

| 4.3  | Bridge 1 の 4 つのスイッチングモード                                                                                                               | 69 |

| 4.4  | 理論的に実現可能な4種類の間欠運転の制御法                                                                                                                  | 71 |

| 4.5  | DCM 間欠運転の 1 間欠周期の理論波形 ( $E_1 = E_2 = E$ )                                                                                              | 72 |

| 4.6  | CCM 間欠運転の 1 間欠周期の理論波形 $(E_1 = E_2 = E)$                                                                                                | 73 |

| 4.7  | 図 4.1 の $E_1 = E_2 = 850$ V, $f_{sw} = 16$ kHz での出力電力に対するスイッチン                                                                         |    |

|      | グ損失の推定値                                                                                                                                | 75 |

| 4.8  | 連続運転時の $E_1$ = $E_2$ = 850 V, $f_{\rm sw}$ = 16 kHz での実験波形                                                                             | 77 |

| 4.9  | 図 4.8 の MOSFET ターンオン時の時間軸拡大波形                                                                                                          | 78 |

| 4.10 | DCM 間欠運転時の $E_1=E_2=850$ V, $f_{\rm sw}=16$ kHz, $P=10$ kW での実験波                                                                       |    |

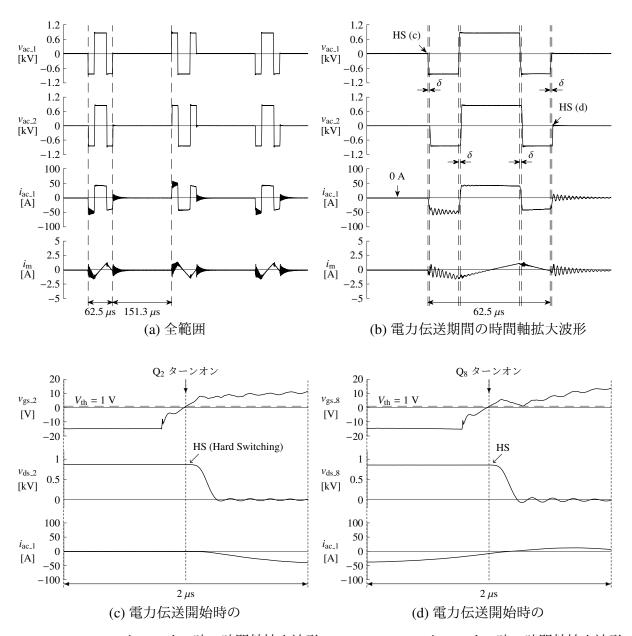

|      | 形 $(I_{\rm rms}=23~{\rm A},P_{\rm con}=34.1~{\rm kW},\delta=5.0^{\circ},n=2.48,P_{\rm loss}=164~{\rm W},\eta=98.39\%)$                 | 79 |

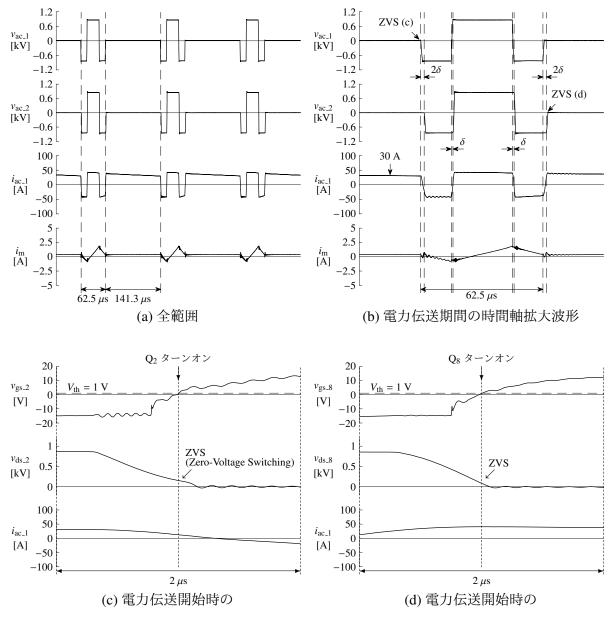

| 4.11 | CCM 間欠運転時の $E_1=E_2=850$ V, $f_{\rm sw}=16$ kHz, $P=10$ kW での実験波                                                                       |    |

|      | 形 $(I_{\rm rms} = 36~{\rm A}, P_{\rm con} = 34.1~{\rm kW}, \delta = 5.0^{\circ}, n = 2.26, P_{\rm loss} = 85~{\rm W}, \eta = 99.16\%)$ | 80 |

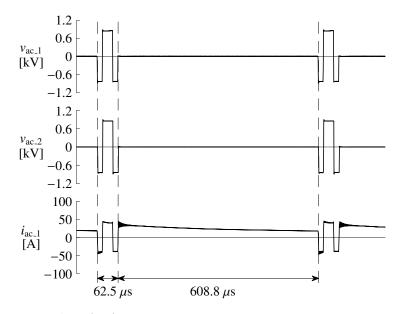

| 4.12 | CCM 間欠運転時の $E_1=E_2=850$ V, $f_{\rm sw}=16$ kHz, $P=3$ kW での実験波                                                                        |    |

|      | $\mathbb{H}$ $(I_{\rm rms}=1~{\rm A},P_{\rm con}=34.1~{\rm kW},\delta=5.0^\circ,n=9.74,P_{\rm loss}=42~{\rm W},\eta=98.62\%)$          | 81 |

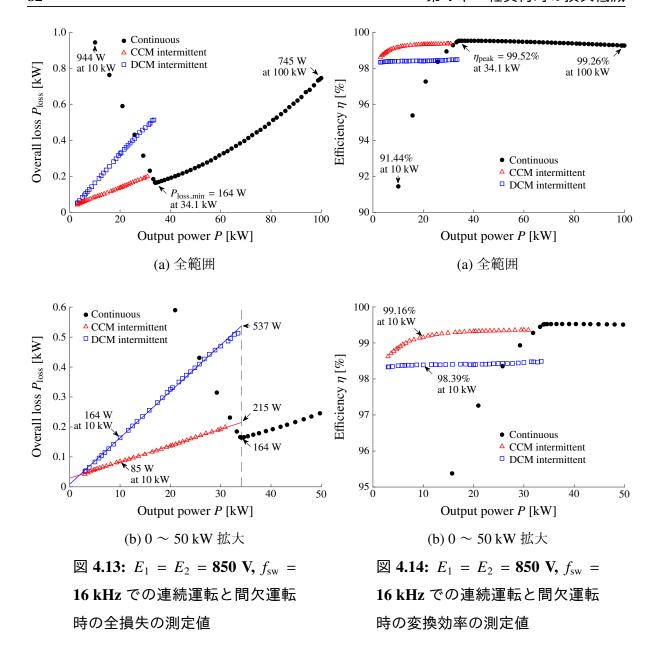

| 4.13 | $E_1 = E_2 = 850$ V, $f_{\rm sw} = 16$ kHz での連続運転と間欠運転時の全損失の測定値                                                                        | 82 |

| 4.14 | $E_1 = E_2 = 850$ V, $f_{\rm sw} = 16$ kHz での連続運転と間欠運転時の変換効率の測                                                                         |    |

|      | 定値                                                                                                                                     | 82 |

| 4.15 | ドレインソース間合成容量 $C_{ m all}$ と直流電圧 $E$ による軽負荷時と定格時の                                                                                       |    |

|      | 損失の変化                                                                                                                                  | 84 |

| 4.16 | $E_1$ = $E_2$ = 850 V, $f_{ m sw}$ = 16 kHz での 1 ms の出力電力 $-100$ kW $\sim 100$ kW                                                      |    |

|      | 反転動作時の過渡特性の実験波形                                                                                                                        | 84 |

| 4.17 | $E_1 = E_2 = 850 \mathrm{V}, f_\mathrm{sw} = 16 \mathrm{kHz}$ での $31.25 \mu\mathrm{s}$ の出力電力 $-100 \mathrm{kW} \sim 100 \mathrm{kW}$   |    |

|      | 反転動作時の過渡特性の実験波形                                                                                                                        | 85 |

| 4.18 | CCM 間欠運転時の直流キャパシタの電圧リプル測定用のテストベンチ                                                                                               |     |

|------|---------------------------------------------------------------------------------------------------------------------------------|-----|

|      | $(L_{\text{dc}\_1} = 40 \mu\text{H}, L_{\text{dc}\_2} = 8 \mu\text{H})  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots$ | 86  |

| 4.19 | CCM 間欠運転時の $E_1$ = $E_2$ = 850 V, $f_{\rm sw}$ = 16 kHz, $P$ = 10 kW での電圧リ                                                      |     |

|      | プルの実験波形 ( $P_{\text{con}} = 34.1 \text{ kW}, \delta = 5.0^{\circ}, n = 2.26$ )                                                  | 86  |

| 4.20 | 間欠運転時の等価周波数                                                                                                                     | 88  |

| 4.21 | 100-kW DAB コンバータの定格 100 kW での損失分離結果の比較                                                                                          | 90  |

| 4.22 | 変換効率 99.5%以上の達成による技術的価値                                                                                                         | 91  |

| 5.1  | 図 5.2, 5.3 に関する DAB コンバータの基本回路                                                                                                  | 96  |

| 5.2  | $E_1 < E_2$ でのブリッジ間の位相シフト制御適用時の理論波形 $\dots$                                                                                     | 97  |

| 5.3  | $E_1 < E_2$ での高圧側ブリッジのレグ間位相シフト制御適用時の理論波形 .                                                                                      | 98  |

| 5.4  | 昇降圧動作時の効率測定が可能な 100-kW 16-kHz DAB コンバータのテス                                                                                      |     |

|      | トベンチ                                                                                                                            | 99  |

| 5.5  | 図 5.4 の DAB 1, 2 にブリッジ間の位相シフト制御を適用した場合の $E_1$ =                                                                                 |     |

|      | 750 V, $E_2$ = 850 V, $P_1$ = 100 kW での実験波形                                                                                     | 101 |

| 5.6  | 図 5.5 の位相シフト期間の時間軸拡大波形                                                                                                          | 102 |

| 5.7  | 図 5.4 の DAB 1 に高圧側ブリッジのレグ間位相シフト制御を, DAB 2 に                                                                                     |     |

|      | ブリッジ間の位相シフト制御を適用した場合の $E_1$ = 750 V, $E_2$ = 850 V,                                                                             |     |

|      | $P_1$ = 100 kW での DAB 1 の実験波形 ( $I_{\rm rms}$ = 146 A, $\delta_1$ = 9.1°, $\phi_1$ = 20.1°,                                     |     |

|      | $P_{\mathrm{loss}}$ = 1056 W, $\eta$ = 98.96%, DAB 2 の波形は図 5.5(b) と同様)                                                          | 103 |

| 5.8  | $E_1 \neq E_2$ での損失分離手順                                                                                                         | 104 |

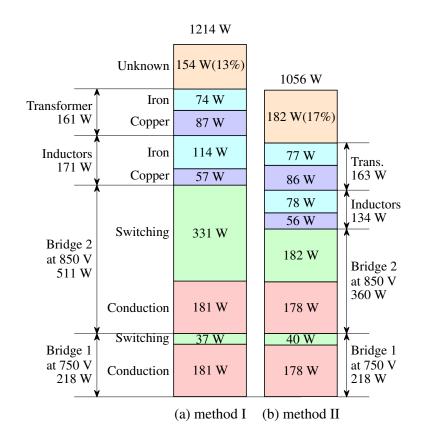

| 5.9  | 図 5.5 のブリッジ間の位相シフト制御 (Method I) 適用時と図 5.7 の高圧                                                                                   |     |

|      | 側ブリッジのレグ間位相シフト制御 (Method II) 適用時の DAB 1 の $E_1$ =                                                                               |     |

|      | 750 V E <sub>2</sub> = 850 V 100 kW 16 kHz での損失分離結果                                                                             | 104 |

# 第1章

## 序論

### 1.1 本研究の背景

脱炭素社会を目指す国際的な協定である「パリ協定」が、2020年から本格的に運用されている。これに対して我が国は、「2050年までに80%の温室効果ガスの排出削減を目指す」という目標を掲げている[1]。これを実現するための重要な取り組みとして、太陽光・風力などの再生可能エネルギーの主力電源化、電気自動車・航空機・船舶などの電動化の普及が挙げられ、このためにはパワーエレクトロニクス(パワエレ)技術が必要不可欠である。これは、パワー半導体素子のスイッチング動作を活用することにより、電力機器の省エネルギー化や小型・軽量化を可能にする実用的な技術である[2]。パワエレ機器では、特にパワー半導体素子と磁気デバイスが重要な役割を担う。

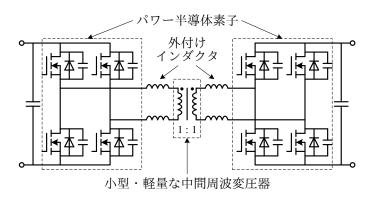

# **1.1.1** 双方向絶縁形 **DC-DC** コンバータ(**DAB** コンバータ)の名称と効率評価の意義

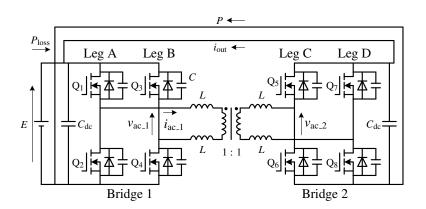

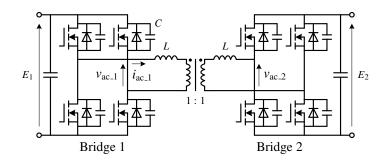

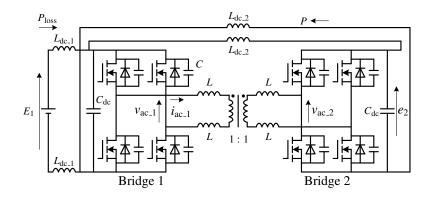

パワー半導体素子や磁気デバイスの低損失化に伴って、電気自動車のバッテリー充放電システム、太陽光・風力発電システムなどに応用される直流-直流電力変換器である双方向絶縁形 DC-DC コンバータが注目されている。図 1.1 に電気的絶縁と電圧整合を目的とした小型・軽量の中間周波変圧器(巻数比 1:1)を使用した双方向絶縁形 DC-DC コンバータの基本回路構成を示す。この回路はその機能から双方向絶縁形 DC-DC コンバータの基本回路構成を示す。この回路はその機能から双方向絶縁形 DC-DC コンバータ、回路構成からは Dual-Active-Bridge (DAB) コンバータとも呼ばれている。本論文では、略して DAB コンバータと呼ぶ。2 台の単相ブリッジ変換器を中間周波変圧器と外付けインダクタを介して接続する左右対称の回路構成に特長がある。ブリッジ間に位相差を設けることで、スイッチング損失を低減可能な零電圧スイッチング (ZVS:

2 第1章 序論

図 1.1: DAB コンバータの基本回路(変圧器巻数比 1:1)

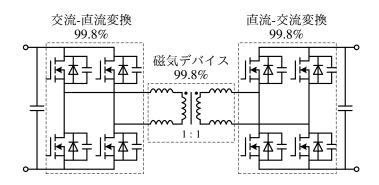

図 1.2: DAB コンバータの直流-直流変換効率 99.3%の意義

Zero-Voltage Switching) を容易に行えるため、大電力用途に適している [3-10]。

10 kW 以上の大容量 DAB コンバータの効率評価を実施している研究機関は本学(東工大),ヨーロッパの RWTH Aachen University,ETH Zurich,アメリカの The University of Texas at Austin,オランダの Delft University,Eindhoven University の 6 大学のみである。本論文では,SiC-MOSFET モジュールとファインメット変圧器を使用した 850-V 100-kW 16-kHz 非共振形・単相 DAB コンバータのテストベンチにより,定格 100 kW で変換効率 99.3%を達成し,筆者が調査した限り,現時点での世界最高効率である。DAB コンバータの直流・直流電力変換効率 99.3%ということは,図 1.2 に示すように直流-交流変換,磁気デバイス,交流-直流変換の 3 つのステージに分けて考えると,各段では 99.8%もの超高効率動作の実現を意味する。大容量 100 kW テストベンチを使用して詳細な効率評価を行った例は筆者が知る限り他になく,さらなる高効率化を目指して大容量 DAB コンバータの効率評価を行うことは学術的・技術的に意義がある。

1.1 本研究の背景 3

#### 1.1.2 パワー半導体素子と磁気デバイスの低損失化の技術動向

パワエレ機器の主要部品であるパワー半導体素子とインダクタや変圧器などの磁気デバイスの低損失化に関する最新の技術動向を述べる。

■パワー半導体素子 従来は大電力用のパワー半導体素子として Si (Silicon) を材料とした IGBT (Insulated Gate Bipolar Transistor) が主流であったが、近年では低損失なワイドバンドギャップ半導体である SiC (Silicon Carbide) を材料とした MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor) の導入が増えてきている [11,12]。以下に日本での代表的な SiC-MOSFET モジュールの導入例を要約する。

- 1. 2012 年: 三菱電機は東京メトロ銀座線の鉄道車両用主回路システムに Si-IGBT と SiC-SBD (Shottky Barrier Diode) のハイブリッド SiC モジュールを適用し、消費電力量 38.6%低減を実証した [13]。

- 2. 2015 年: 三菱電機は小田急電鉄車両の鉄道車両用主回路システムに SiC-MOSFET と SiC-SBD のフル SiC モジュールを適用し、全体として約 40%の省エネ効果を 実証した [14]。

さらに、国家プロジェクトとしても SiC デバイスの実用化に取り組んできた [15]。

MOSFET は IGBT が原理的に有するテール電流が存在しないため、スイッチング損失の低減が可能であり、高周波動作に適している。SiC は Si に比べて、絶縁破壊電界強度が約 10 倍であるため、高耐圧化が容易である。また、MOSFET のチャネル長を短くできることから、オン抵抗低減により導通損失の低減が可能となる。IGBT は原理的にビルトイン電圧を有するが、MOSFET はオン抵抗により導通損失が決定するため、広範囲な出力領域で低損失化が可能である。これらのことから SiC と MOSFET の組み合わせにより、高耐圧で低損失な半導体素子が実現可能である。SiC-MOSFET モジュールは、現在 1.2~3.3 kV 耐圧までの製品が市販されており、さらに 6.5 kV 耐圧のモジュールの開発が進んでいる [16]。近年では、従来のプレーナゲート構造 SiC-MOSFET に代わるトレンチゲート構造 SiC-MOSFET の開発が進められている。トレンチゲート構造はウエハの溝にゲート電極を埋め込んだ構造であり、従来のプレーナゲート構造に比べて、面積を小さくできるため、オン抵抗をさらに 50%削減できることと [17]、ドレイン-ゲート間の帰還容量が減少することにより、スイッチング損失が 50%削減できることが報告されている [18]。これらの報告例と、SiC-MOSFET は Si-IGBT に比べて発展途上であることから、将来的に損失が半分以下になることは現実的である。

4 第1章 序論

図 1.3: 重量 26 kg の珪素鋼板を使用した単相 100-V 3-kVA 50-Hz 変圧器(左側)と重量 11 kg のファインメットを使用した単相 750-V 100-kVA 16-kHz 変圧器(右側)の外観

- ■磁気デバイス パワエレ機器に欠かせない要素としてインダクタや変圧器などの磁気 デバイスがある。インダクタはエネルギー蓄積要素として、変圧器は電気的絶縁と電圧整合の手段として機能する。インダクタは鉄心にギャップを設け、磁気抵抗を大きくすることで、エネルギーの蓄積を可能にする。一方、変圧器は鉄心のギャップは不要で、磁気抵抗を可能な限り小さくすることで、一次側から二次側にエネルギーを伝えやすくする。これらの素子はスイッチング周波数を数十~数百 kHz まで引き上げることにより最大磁束密度を低減できるため、小型・軽量化を図ることができる [19]。高周波用途のインダクタ鉄心構造として従来は Mn-Zn フェライトなどの積層鉄心が主流であったが、Fe-Si-Al 合金(Magnetics、商品名「センダスト」)[20] や Fe 基金属ガラス合金(アルプスアルパイン、商品名「リカロイ」)[21] などの圧粉鉄心が注目されている。以下に圧粉鉄心の代表的な特長を要約する。

- 1. 積層鉄心に比べて原理上うず電流損が小さいため、高周波では低損失なインダクタが実現できる。

- 2. 多数の粉末間の空間がギャップとして機能する。

- 3. 粉末を押し固めるため、種々の形状に対応可能である。

リカロイはセンダストに変わる最新の磁性材料であり、鉄心の直流抵抗が高いことから、 うず電流損がほとんど発生せず、さらなる低損失化が期待できる [22]。

一方、中間周波変圧器の磁性材料に着目すると、商用周波用途として珪素鋼板、高周

1.1 本研究の背景 5

波用途として Mn-Zn フェライトなどが使用されてきたが,近年ではナノ結晶軟磁性材料(日立金属,商品名「ファインメット」)が注目されている。ファインメットの飽和磁束密度はフェライトに比べて約 4 倍大きく,数十 kHz では低鉄損であるため,大容量変圧器の小型・軽量化に適している [23]。図 1.3 に体積と重量の比較のために変圧比が 1:1の2つの変圧器の外観を示す。左側は珪素鋼板を使用した単相 100-V 3-kVA 50-Hz 変圧器であり,重量は 26 kg である。右側は最新の厚さ 14  $\mu$ m のファインメット (FT-3TL)を使用した単相 750-V 100-kVA 16-kHz ノーカットコア変圧器であり,重量は 11 kg である。容量が約 33 倍になっているにもかかわらず,重量は 58%もの削減を実現している。さらに,厚さ 14  $\mu$ m のリボン状の形状がノーカットコア構造を可能にし,カットコア構造に比べて,大幅な損失低減が実現できる [24]。ファインメットは磁化のしやすさを表す透磁率が高い磁性材料であるため,インダクタには適していない。

本論文では、パワエレ機器の低損失化の観点からパワー半導体素子として SiC-MOSFET モジュールを、インダクタのコア磁性材料としてセンダスト、リカロイを、変圧器のコア磁性材料としてファインメットを使用する。

#### 1.1.3 電力損失分離の必要性と課題

電力変換器のさらなる高効率化の可能性を示すためには、支配的な損失要素を明確化する必要がある。特に DAB コンバータの場合には軽負荷時や昇降圧動作時に増大するスイッチング損失を定量的に評価することが必要不可欠である。表 1.1 にスイッチング損失の測定・推定法の比較を示す。スイッチング損失の測定・推定法は以下の 4 種類に大別できる。

- 1. MOSFET のデータシートからの推定: 一般にダブルパルス試験によるハードス イッチング動作時の結果であり, 低損失なスイッチング動作である零電圧スイッ チング時には適用できない。

- 2. 実機のドレイン・ソース間電圧とドレイン電流の瞬時値積による直接測定: スイッチングが高速な SiC-MOSFET の場合,特にプローブの検出遅れの補正が厄介であり [25,26],測定精度は約50%で実用的ではない。

- 3. 温度による間接測定 [26–30]: 測定精度は 10 ~ 20%で, 直接測定と比べて高精度な測定が可能であるが, 測定時間が長いことや温度測定の基準を固定するために恒温槽などの特別な測定環境が必要である。

| 手法                                                                     | 精度          | 課題           |  |  |  |

|------------------------------------------------------------------------|-------------|--------------|--|--|--|

| データシートからの推定                                                            | 記載なし        | ZVS では適用不可   |  |  |  |

| 電流・電圧の瞬時値積による直接測定                                                      | 約 50%*      | ドレイン電流の測定精度  |  |  |  |

| 温度による間接測定 [26–30]                                                      | 約 10 ~ 20%  | 測定時間が長い      |  |  |  |

| 価反による同弦側に [20-30]                                                      | #J 10 - 20% | 特別な測定環境が必要   |  |  |  |

| 高精度に測定した全損失からの損失分離 [31]                                                | 約 20%**     | インダクタ鉄損の測定精度 |  |  |  |

| * 5 4 10 10 10 14 7 14 5 17 1 7 10 10 11 11 11 11 11 11 11 11 11 11 11 |             |              |  |  |  |

表 1.1: スイッチング損失の測定・推定法の比較

<sup>\*\*</sup> インダクタ鉄損の測定誤差が ±10%の場合

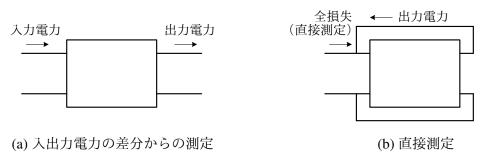

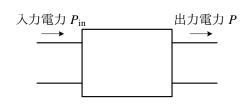

図 1.4: 2 種類の全損失の測定法

4. 高精度に測定した全損失からの損失分離 [31]: 温度による間接測定と同程度の測定精度 20%を有し、短時間かつ特別な測定環境なしで測定可能であるため、簡便かつ実用的な手法である。しかし、昇降圧動作時への適用については未検討であった。

図 1.4 に 2 種類の全損失の測定法を示す。図 1.4(a) は入出力電力を個別に測定し、それらの差分から全損失を測定する手法である。全損失の測定誤差は入出力電力の測定精度の差分と入力電力に対する全損失の割合に依存するため、現在入手可能な高精度なパワーアナライザ(電力測定誤差: 0.2% [32])を使用しても、変換効率が 99.3%の場合、全損失の測定誤差は 57%となり、実用的ではない。図 1.4(b) は入出力の端子を直接接続した構成で、「全損失を直接高精度に測定可能」な点に特長がある [33]。全損失の測定誤差はパワーアナライザの電力測定精度 0.2%となり、高効率な変換効率の評価に適した測定法である。手法 4.は、図 1.4(b) を使用し、「全損失が高精度に測定可能」である特長を活用することで簡便かつ実用的なスイッチング損失の分離を可能にする。

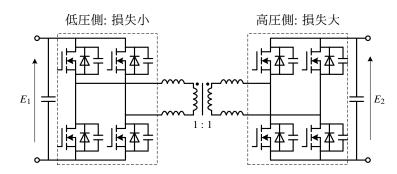

図 1.5 に中間変圧器の巻数比が 1:1 の DAB コンバータの昇圧動作時の入出力のブリッジ変換器の損失の関係を示す。昇降圧動作時には入出力のブリッジ変換器の損失が異なるため, [31] で提案された損失分離法ではブリッジ変換器ごとの損失を分離するこ

<sup>\*</sup>電流検出遅れ補正精度が立下り時間に対して10%の場合

1.1 本研究の背景

7

図 1.5: DAB コンバータの昇圧動作時  $(E_1 < E_2)$  の入出力のブリッジ変換器の損失の関係(変圧器巻数比 1:1)

とができない。本論文では、[31]をベースとして、「実用的な昇降圧動作の範囲では、零電圧スイッチング時のスイッチング損失がターンオフ時の電流にのみ依存し、入出力電圧にはほぼ無関係」であることを理論と実験で確認し、昇降圧動作時にも適用可能なスイッチング損失の評価法を提案する。

#### **1.1.4 DAB** コンバータの技術課題と解決策

DAB コンバータには以下の 2 点の技術課題が以前から指摘されている。

- 1. 軽負荷時の損失増大: 日本での太陽光発電の設備利用率は 15.9% [34], 風力発電の場合, 陸上で 20%, 洋上で 30% [35] である。これらの応用を想定した場合, DAB コンバータは軽負荷動作が要求され,電力損失は定格動作時に比べて増大することが知られている [36,37]。これはスイッチング損失を低減可能な零電圧スイッチングが不完全あるいは不能となることで, MOSFET のターンオン損失が増大するためである。

- 2. 昇降圧動作時の損失増大: 高圧 DC グリッド間の接続 [38], モータドライブ [9,39], Solid-State Transformer (SST) [40–42] などの応用として,複数の DAB コンバータをカスケード接続した高圧マルチレベル変換器として使用される場合には,各 DAB コンバータの入出力電圧が一致する。このような動作条件では,変換効率が最大となる。一方,バッテリー充放電システムなどの応用では DAB コンバータは昇降圧動作が要求され,その場合の電力変換効率は入出電圧が等しい場合に比べて低下することが知られている [43–46]。これは高圧側の MOSFET のターンオフ時のスイッチング電流が上昇し,ターンオフ損失が増大するためである。

軽負荷時や昇降圧動作時の低損失化を実現するために大きく以下の2つの手法が報告 されている。

- 1. レグ間の位相シフト [5,43,47–63]: DAB コンバータのブリッジ間の位相シフトに加えて、レグ間の位相シフトを適用した制御法であり、インバータの制御法として古くから知られる one-pulse PWM を適用することと同義である。しかし、制御変数と制御パターンが増大するため、制御アルゴリズムが複雑である。

- 2. 間欠運転 [64-74]: 電力伝送休止期間を設け、伝送電力を平均的に調整しようとする制御概念であり、制御アルゴリズムが単純で、軽負荷時でもスイッチング損失を低減可能な点に特長がある。この制御概念は通信分野で古くから使用されているデータ転送方式である「バーストモード」と同義である。英語で"burst"は「破裂する、爆発する」という意味であり、通信分野では一度に複数のパルス状のデータを「一括」で転送するという概念として使用されている [75,76]。本論文で提案する手法は電力を送る動作と休む動作が1周期ごとに交互に行われることから、より適切な用語として「間欠運転」 (intermittent operation) を使用する。しかし、従来の電流不連続モード間欠運転では、電力伝送の開始時と終了時のスイッチング損失が低減できる可能性が残されていた [70,74,77]。

### 1.2 本研究の目的と成果

#### 1.2.1 本研究の目的

本論文は、SiC-MOSFET を使用した大容量双方向絶縁形 DC-DC コンバータ(DAB コンバータ)を対象として、零電圧スイッチング時の SiC-MOSFET のスイッチング損失を定量的に評価する簡便かつ実用的な手法を提案し、軽負荷時や昇降圧動作時に増大するスイッチング損失を低減する制御法を提案する。

電圧・電流の瞬時値積からスイッチング損失を測定する方法では、SiC-MOSFET のスイッチングが高速であるため、電流検出遅延の影響を取り除くことが困難であり、実用的な測定精度を得ることは期待できない。これに対して、[31] で提案された高精度に測定した全損失からの損失分離が実用的であるが、昇降圧動作時では入出力のブリッジ変換器の損失が異なるため、適用できない。本論文では、「零電圧スイッチング時のスイッチング損失がターンオフ時の電流にのみ依存し、入出力電圧とはほぼ無関係」であることを理論と実験で確認し、昇降圧動作時にも適用可能なターンオフ時の電流からの

スイッチング損失の評価法を提案する[78]。

軽負荷時の低損失化を実現する制御法として制御アルゴリズムが単純な間欠運転が有力であるが、電力伝送の開始時と終了時のスイッチング損失が低減できる可能性が残されていた [70,74,77]。本論文では、提案法で評価したスイッチング損失を用いて従来の間欠運転の損失増大を定量的に明らかにし、電力伝送休止期間中に電流を意図的に還流させることにより、スイッチング損失を大幅に低減可能な電流連続モード間欠運転を提案する [79]。

昇降圧動作時の低損失化を実現する制御法としてレグ間位相シフト制御が検討されているが、制御アルゴリズムが複雑であった [49]。本論文では、提案法で評価したスイッチング損失に基づいて、昇降圧動作時の定格出力領域の損失低減に焦点を絞って制約条件を設けることで、制御アルゴリズムが単純な高圧側ブリッジへのレグ間位相シフト制御を提案する [78]。

#### 1.2.2 本研究の成果

本研究の成果を以下に要約する。

- 1. 昇降圧動作時にも適用可能な零電圧スイッチング時の SiC-MOSFET のスイッチング損失の評価法を提案した。これは温度による間接測定と同程度の測定精度を有し、ターンオフ時の電流を測定するだけでよいため、簡便かつ実用的な手法である。

- 2. 軽負荷時の低損失化が可能な制御法として電流連続モード間欠運転を提案した。 定格の 10 ~ 100%の広範囲な出力領域で変換効率 99.16%以上の高効率動作を実現した。

- 3. 昇降圧動作時の低損失化が可能な制御法として高圧側のブリッジのレグ間位相シフトを提案した。入力電圧 750 V, 出力電圧 850 V の昇圧動作時において定格 100 kW での変換効率は 98.96%に到達し、従来制御の 98.80%に比べて 0.16%の向上を達成した。

大容量 100 kW テストベンチを使用して軽負荷時・昇降圧動作時を含む詳細な効率評価を行った例は筆者が知る限り他になく、学術的・技術的に意義がある。

10 第1章 序論

### 1.3 本論文の構成

本論文は、全6章で構成されており、以下に概要を示す。

#### 第1章序論

本章では、本研究の背景と目的を明らかにし、研究方法の概略を示す。

#### 第2章 DAB コンバータの技術動向

本章では、大容量 DAB コンバータの回路方式を比較し、対象とする回路方式を決定する。次に、他の研究機関が発表した、10 kW 以上の大容量 DAB コンバータの変換効率評価に関する文献調査を行い、本研究の学術的・技術的な意義を示す。最後に、DABコンバータのさらなる変換効率向上のための課題と解決策を整理し、本論文の位置付けを明確にする。

#### 第3章 スイッチング損失の分離

本章では、昇降圧動作時にも適用可能な零電圧スイッチング時のスイッチング損失の分離法を検討する。これは [31] をベースとしており、電圧・電流の瞬時値積による直接測定が困難な SiC-MOSFET のスイッチング損失をターンオフ時の電流から簡便かつ実用的に分離可能である点に特長がある。1.2-kV 400-A SiC-MOSFET/SBD 4-in-1 モジュールを用いた 100-kW 16-kHz DAB コンバータのテストベンチを設計・製作し、損失分離を行う。分離したスイッチング損失の測定誤差について検討し、温度による間接測定と同程度であることを示す。「実用的な昇降圧動作の範囲では、零電圧スイッチング時のスイッチング損失が入出力電圧とはほぼ無関係」であることを理論と実験により議論し、提案法が昇降圧動作時にも適用できることを実証する。

#### 第4章 軽負荷時の損失低減

本章では、軽負荷時の高効率化を実現するための制御法として制御アルゴリズムが単純な間欠運転を検討する。従来の電流不連続モード間欠運転では電力伝送の開始時と終

1.3 本論文の構成 11

了時のみスイッチング損失を低減可能な零電圧スイッチングが不可となるため、さらなる低損失化の可能性が残されていることを明らかにする。提案する電流連続モード間欠運転は電力伝送休止期間中に電流を意図的に還流させることにより、軽負荷時であってもすべてのスイッチングで零電圧スイッチングが実現できるため、変換効率の大幅な向上が期待できる。設計・製作した 1.2-kV 400-A SiC-MOSFET/SBD 4-in-1 モジュールを用いた 850-V 100-kW 16-kHz DAB コンバータのテストベンチに提案法を適用し、有効性を実証する。最後に、3 章で得た損失分離結果を使用して変換効率の将来予測を行い、本論文の技術的意義を示す。

#### 第5章 昇降圧動作時の損失低減

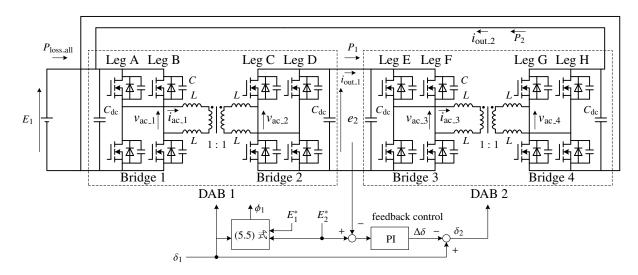

本章では、昇降圧動作時の低損失化が可能な制御法として高圧側のブリッジのレグ間位相シフトを提案する。これは定格出力領域の損失低減に焦点を絞って制約条件を設けることで、制御アルゴリズムを単純化できる点に特長がある。昇降圧動作時の効率測定が可能な2台の同一定格の100-kW16-kHzDABコンバータ(中間変圧器の巻数比1:1)を縦続接続したテストベンチを設計・製作し、3章で分離したスイッチング損失が入出力電圧とはほぼ無関係である実証結果を応用して、昇圧動作時の損失分離を行い、提案法適用時の損失低減効果を実証する。

#### 第6章 結論

本章では、第3~5章で得られた研究成果をまとめ、今後の展望について明らかに する。

## 第2章

## DAB コンバータの技術動向

本章では、大容量 DAB コンバータの回路方式を比較し、対象とする回路方式を決定する。次に、他の研究機関が発表した、10 kW 以上の大容量 DAB コンバータの変換効率評価に関する文献調査を行い、本研究の学術的・技術的な意義を示す。最後に、DABコンバータのさらなる変換効率向上のための課題と解決策を整理し、本論文の位置付けを明確にする。

### 2.1 DAB コンバータの回路方式

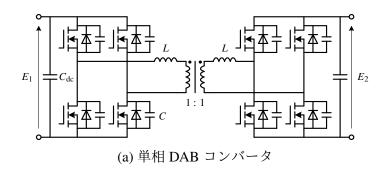

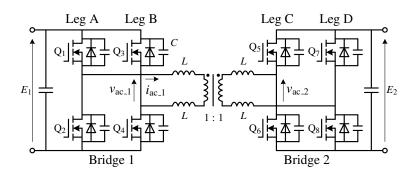

図 2.1 に示すように DAB コンバータの回路方式は大きく 3 つに分類される。以下では、各回路方式の動作原理について簡単に説明し、特長と課題を比較する。

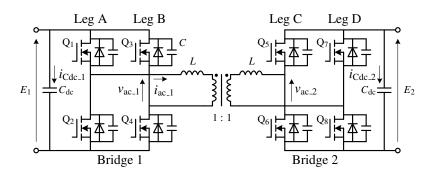

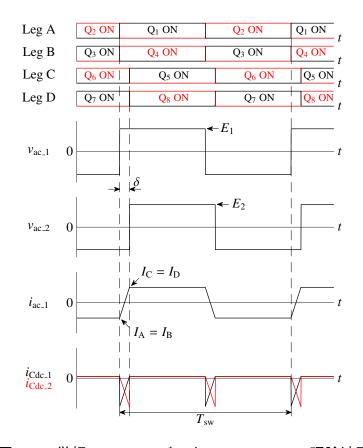

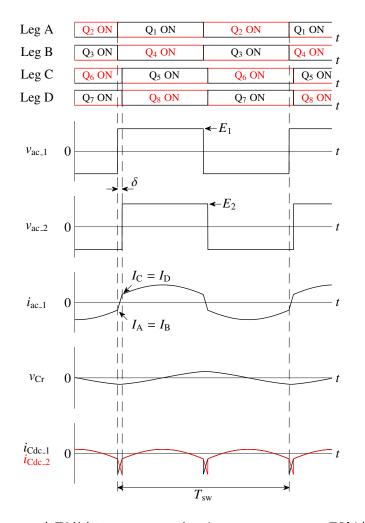

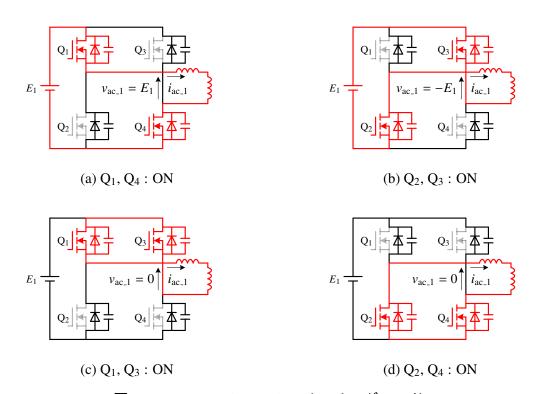

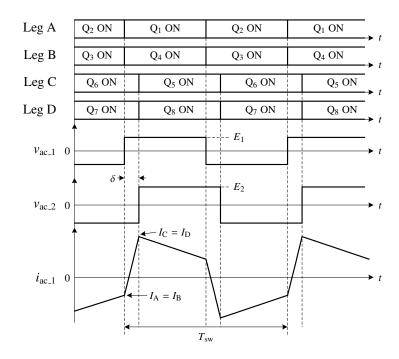

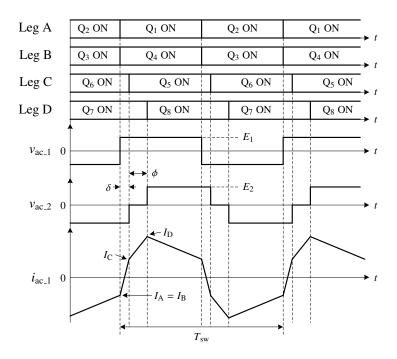

#### 2.1.1 単相 DAB コンバータ

図 2.2 に単相 DAB コンバータの回路,図 2.3 に  $E_1 = E_2$  での理論波形を示す。Bridge 1,2 はそれぞれ 180° 通電の方形波電圧  $v_{\rm ac.1}$ ,  $v_{\rm ac.2}$  を出力し,これらの位相差を調整することで,出力電力を制御する。単相 DAB コンバータの出力電力 P は, $v_{\rm ac.1}$  と  $v_{\rm ac.2}$  の位相差  $\delta$  により次式で表される [3]。

$$P = \frac{E_1 E_2}{2\pi f_{\text{sw}} L_{\text{all}}} \delta \left( 1 - \frac{\delta}{\pi} \right) \tag{2.1}$$

$$L_{\text{all}} = 2L \tag{2.2}$$

ここで、 $L_{\text{all}}$  は一次側に等価換算した外付けインダクタのインダクタンスと、変圧器の漏れインダクタンスを含む合計のインダクタンスである。 $I_{\text{A}}$ ,  $I_{\text{B}}$ ,  $I_{\text{C}}$ ,  $I_{\text{D}}$  はそれぞれ Leg A,

図 2.1: 3 種類の代表的な DAB コンバータの回路方式 (変圧器巻数比 1:1)

B, C, D の MOSFET がターンオフする時の瞬時電流であり、本論文ではスイッチング電流と定義する。Bridge 1 の Leg A と Leg B,Bridge 2 の Leg C と Leg D がそれぞれ同時にスイッチングするため, $I_A=I_B$ , $I_C=I_D$  となる。 $E_1=E_2$  の場合,すべてのスイッチング電流は等しくなり, $I_A=I_B=I_C=I_D$  が成立するため,すべての MOSFET のスイッチング損失は等しくなる。

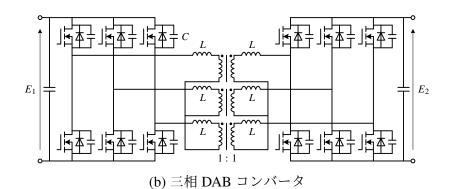

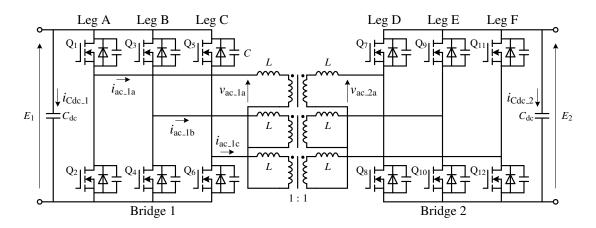

#### 2.1.2 三相 DAB コンバータ

図 2.4 に三相 DAB コンバータの回路,図 2.5 に  $E_1 = E_2$  での理論波形を示す。三相インバータの各レグの上下の MOSFET は 180° ごとにオンオフを繰り返し,各レグ間の位

図 2.2: 図 2.3 に関する単相 DAB コンバータ

図 2.3: 図 2.2 の単相 DAB コンバータの  $E_1 = E_2$  での理論波形の一例

相差は  $120^\circ$  に固定する。直流キャパシタに流れる電流は三相の交流電流のリプルが打ち消し合うことで,図 2.2 に比べて電流リプル実効値を低減可能である。三相 DAB コンバータの出力電力 P は,Bridge 1 と Bridge 2 の位相差  $\delta$  により次式で表される [3]。

$$P = \frac{3E_1E_2}{2\pi f_{\text{sw}}L_{\text{all}}} \delta\left(\frac{2}{3} - \frac{\delta}{2\pi}\right) \tag{2.3}$$

ただし、上式は  $\delta < \pi/6$  の条件でのみ成立する。 $E_1 = E_2$  の場合、 $I_A = I_C = I_D = I_E$ 、 $I_B = I_F$  が成立する。 $I_A = I_C = I_D = I_E < I_B = I_F$  であるため、Leg B, F のスイッチング損

図 2.4: 図 2.5 に関する三相 DAB コンバータ

図 2.5: 図 2.4 の三相 DAB コンバータの  $E_1 = E_2$  での理論波形の一例

失が Leg A, C, D, E より大きくなる。

図 2.6: 図 2.7 に関する直列共振 DAB コンバータ

図 2.7: 図 2.6 の直列共振 DAB コンバータの  $E_1 = E_2$  での理論波形の一例

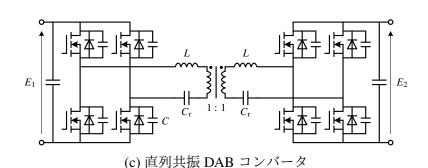

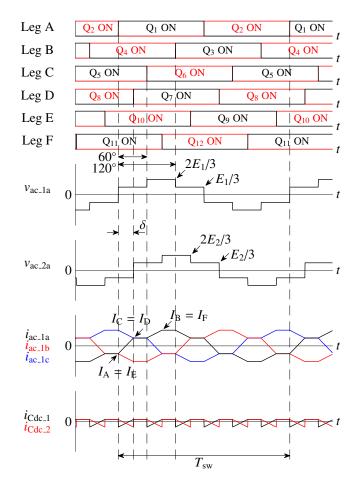

### 2.1.3 直列共振 DAB コンバータ

図 2.6 に直列共振 DAB コンバータの回路,図 2.7 に  $E_1 = E_2$  での理論波形を示す。交流側のインダクタ L と共振キャパシタ  $C_r$  の直列共振により,図 2.2 に比べてスイッチング電流を低減可能な点に特長がある。MOSFET のスイッチングパターンは図 2.2 と同様

| 回路方式         | 単相(図 2.1(a)) | 三相(図 2.1(b))                | 直列共振(図 2.1(c)) |

|--------------|--------------|-----------------------------|----------------|

| 直列共振キャパシタ    | 不要           | 不要                          | 必須(大型・重量)      |

| 変圧器          | 単相変圧器 1 個    | 三相三脚変圧器 1 個<br>または単相変圧器 3 個 | 単相変圧器 1 個      |

| 変圧器直流偏磁      | 発生しやすい       | 発生しやすい                      | 発生しにくい         |

| 異常振動         | 発生しにくい       | 発生しにくい                      | 発生しやすい         |

| 直流キャパシタ電流リプル | 大            | 小                           | 中              |

| 部品点数         | 少            | 多                           | 中              |

| 制御自由度        | 高            | 低                           | 中              |

| 応用先          | 大容量          | 大容量                         | 比較的小容量         |

表 2.1: 図 2.1 の 3 種類の DAB コンバータの回路方式による比較

である。直列共振 DAB コンバータの出力電力 P は, $v_{ac\_1}$  と  $v_{ac\_2}$  の位相差  $\delta$  により次式で表される [87]。

$$P = 4E_1 E_2 f_{\text{sw}} \frac{C_{\text{r}}}{2} \left[ \frac{\cos\left\{\frac{f_{\text{r}}}{f_{\text{sw}}} \left(\frac{\pi}{2} - \delta\right)\right\}}{\cos\left(\frac{f_{\text{r}}}{f_{\text{sw}}} \cdot \frac{\pi}{2}\right)} - 1 \right]$$

(2.4)

$$f_{\rm r} = \frac{1}{2\pi\sqrt{LC_{\rm r}}}\tag{2.5}$$

ここで、fr は共振周波数である。

#### **2.1.4 DAB** コンバータの回路方式の比較

表 2.1 に図 2.1 の回路方式による比較を示す。単純化のために変圧器の巻数比は 1:1 とする。図 2.1(a) は 2 台の単相インバータの交流端子を外付けインダクタと変圧器を介して接続する構成であり,最も単純な回路構成である。ブリッジ間の位相シフト制御により Zero-Voltage Switching (ZVS) 動作を容易に実現できる点に特長がある [3–9]。

図 2.1(b) は (a) の単相インバータを三相インバータに置き換えた構成である。交流側のインダクタ電流の高調波が低減されることにより、インダクタ・変圧器の鉄損削減、入出力の直流キャパシタの電流リプル幅の低減に効果がある [3,70,80–84]。三相三脚変圧器を使用する場合、三脚鉄心の構造上各相の漏れインダクタンスなどの回路パラメータが非対称となり、三相不平衡や直流偏磁を引き起こす可能性がある。これを解決する三次元の立体対称構造 [85] が提案されているが、リボン状のファインメットを使用した

ノーカットコア変圧器への適用は困難である。代替案として単相変圧器を3個使用する場合、体積・重量が大型化する課題がある。さらに、三相平衡を保つ必要があるため、制御自由度の制約も課題である。

図 2.1(c) は交流側の共振インダクタ L と直列接続した共振キャパシタ  $C_r$  が直列共振回路 を構成し、ZVS 動作に加えて Zero-Current Switching (ZCS) 動作が可能である [29,86–89]。 この共振キャパシタは直流阻止キャパシタ (dc-blocking capacitor) としても動作し、定常 時には変圧器の直流偏磁を抑制できる。しかし、過渡時には異常振動・現象の発生要因 となる。しかも、高周波大電流が直接流れるため、大電力 DAB コンバータでは共振キャパシタの体積・重量を無視できない [5]。

本論文では、大容量化の観点から図 2.1(a) の非共振形・単相 DAB コンバータを採用する。

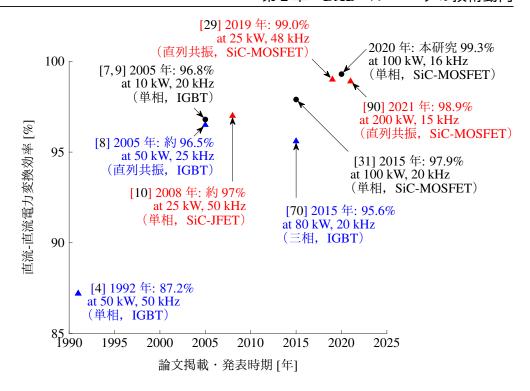

## 2.2 DAB コンバータの電力変換効率の動向

図 2.8 に大容量 DAB コンバータの直流-直流電力変換効率の動向を示す。変換効率は同程度の容量で比較を行う必要があるため、定格出力電力が 10 kW 以上のものに絞って文献調査を行った。対象は図 2.1 の回路方式の実機での効率評価に関する論文に限定している。黒は本研究グループ、青と赤は他の研究機関の論文である。特に青は Si-IGBTを、赤は SiC デバイスを使用した実験に関する論文である。以下に各論文についての要約を示す。

- 1. 1992 年 [4]: 50-kW 50-kHz DAB コンバータの効率評価に関する論文が報告された。図 2.1(a) に示す単相 DAB コンバータをベースとしたテストベンチにより、定格 50 kW で変換効率 87.2%を実証した。ZVS を適用しているにもかかわらず変換効率が低い要因は、第一世代プレーナゲート IGBT モジュールとフェライトコアの変圧器を使用したためである。変圧器の小型・軽量化の観点からスイッチング周波数をフェライトコアに適した 50 kHz と高く設定した結果として、IGBT のスイッチング損失が増大し、変換効率の低下につながっている。

- 2. 2005 年 [7,9]: 本研究グループから 350-V 10-kW 20-kHz DAB コンバータの効率評価に関する論文が報告され、定格 10 kW で変換効率 96.8%の向上を達成した。この効率向上は 600-V トレンチゲート Si-IGBT 2-in-1 モジュールとナノ結晶軟磁性材料(日立金属、商品名「ファインメット」) リングコアの変圧器を使用した結果

図 2.8: 大容量(10 kW 以上) DAB コンバータの定格時の直流-直流電力変換 効率の動向

である。ファインメットはフェライトに比べて、飽和磁束密度が約4倍高いため、スイッチング周波数を20kHz程度まで下げても変圧器の小型・軽量化を実現できる。これ以降、多くのパワーエレクトロニクス研究者や技術者が定格時や軽負荷時の変換効率向上を目指してDABコンバータの研究に着手するようになった。

- 3. 2005 年 [8]: 入力電圧 750-V 出力電圧 600-V 50-kW 25-kHz DAB コンバータの効率評価に関する論文が報告された。回路方式は図 2.1(a) をベースとしているが,直流リンクキャパシタ  $C_{dc}$  の静電容量を意図的に小さく設定し,変圧器の漏れインダクタンスを含む交流側の共振インダクタ L と共振を発生させることで,共振形 DC-DC コンバータのように動作する。変換効率は定格 50 kW で約 96.5%を実証し,変換効率向上を実証した。これはスイッチング周波数を [3,4] の 50 kHz に対して半分の 25 kHz に下げていることが主な要因であると考えられる。変圧器のコア磁性材料には大容量用途に適したアモルファス金属を使用している。

- 4. 2008 年 [10]: 図 2.1(a) をベースとした入力電圧 5-kV 出力電圧 700-V 25-kW 50-kHz DAB コンバータの効率評価に関する論文が報告された。変換効率は定格 25 kW で約 97%を実証し、50 kHz の高周波動作であるにも関わらず、変換効率向上を実証した。これは SiC-JFET を使用したためである。変圧器のコア磁性材料にはに

はフェライトを使用し、動作周波数を 50 kHz に設定している。

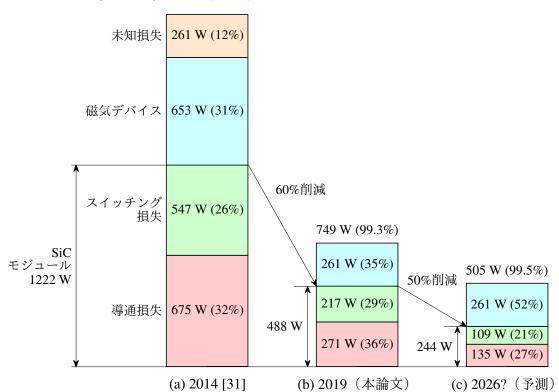

- 5. 2015 年 [31]: 本研究グループから図 2.1(a) をベースとした 750-V 100-kW 20-kHz DAB コンバータの効率評価に関する論文が報告され,定格 100 kW で変換効率 97.9%を達成し,さらなる高効率化を実現した。これは,1.2-kV SiC-MOSFET/SBD 2-in-1 モジュールとファインメットを使用した変圧器を適用したためであり,DAB コンバータが SiC-MOSFET モジュールに適した回路であることを示した論文である。

- 6. 2015 年 [70]: 入力電圧 750-V 出力電圧 600-V 80-kW 20-kHz DAB コンバータの効率評価に関する論文が報告された。回路方式は図 2.1(b) に示すようにな三相 DAB コンバータを採用しており、定格 80 kW で変換効率は 95.6%であった。これは IGBT モジュールを使用していることと、図 2.1(a) と比較して部品点数が多いためであると推察できる。

- 7. 2019 年 [29]: 高圧側に 10-kV SiC-MOSFET モジュール, 低圧側に 1.2-kV SiC-MOSFET モジュールを使用した 7-kV 400-V 25-kW 48-kHz DAB コンバータの効率評価に関する論文が報告された。図 2.1(c) に示す直列共振 DAB コンバータをベースとしたテストベンチにより, 定格 25 kW で変換効率 99.0%を実証した。変圧器のコア磁性材料にはフェライトを使用している。

- 8. 2021 年 [90]: 1.7-kV SiC-MOSFET モジュールを使用した 1.3-kV 200-kW 15-kHz DAB コンバータの効率評価に関する論文が報告された。図 2.1(c) に示す直列共振 DAB コンバータをベースとしたテストベンチにより、定格 200 kW で変換効率 98.85%を実証した。変圧器のコア磁性材料にはファインメットを使用している。

調整結果から 10 kW 以上の大容量 DAB コンバータの効率評価を実施している研究機関は本学(東工大),ヨーロッパの RWTH Aachen University,ETH Zurich,アメリカのThe University of Texas at Austin,オランダの Delft University,Eindhoven University の 6大学のみである。Si-IGBT を使用した場合,変換効率は 97%程度にとどまっていたが,SiC-MOSFET を使用することで 99%以上に到達可能となった。これはパワーモジュールだけでなく,変圧器やインダクタを含む磁気デバイスの低損失化も大きく影響している。本論文では,1.2-kV 400-A SiC-MOSFET/SBD 4-in-1 モジュールとファインメット変圧器を使用した図 2.1(a) をベースとした 850-V 100-kW 16-kHz 非共振形・単相 DABコンバータのテストベンチにより,定格 100 kW で変換効率 99.3%を達成し,筆者が調査した限り,現時点での世界最高効率である。大容量 100 kW テストベンチを使用して

図 2.9: 図 2.2 の出力電力変動時と負荷電圧変動時の理論波形

軽負荷時・昇降圧動作時を含む詳細な効率評価の研究は、筆者が調査した限り、発表されていない。よって、大容量 DAB コンバータの効率評価を行うことは学術的・技術的に意義がある。

### **2.3 DAB** コンバータの損失低減に向けた課題

DAB コンバータには以下の2点の課題が長年指摘されている。

- 1. 軽負荷時の損失増大 [36,37]

- 2. 昇降圧動作時の損失増大 [43-46]

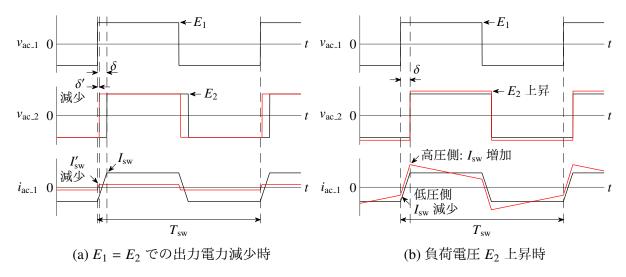

図 2.9 に出力電力変動時と負荷電圧変動時の理論波形を示す。図 2.9(a) に示すように  $E_1 = E_2$  で出力電力が低下した場合,MOSFET のターンオフ時のスイッチング電流が低下し,ZVS 動作が不可能となり,MOSFET のターンオン損失が増大する。図 2.9(b) に示すように負荷電圧が上昇した場合,高圧側の Bridge 2 の MOSFET のスイッチング電流が上昇し,ターンオフ損失が増大する。以下では,これらの発生メカニズムについて説明する。

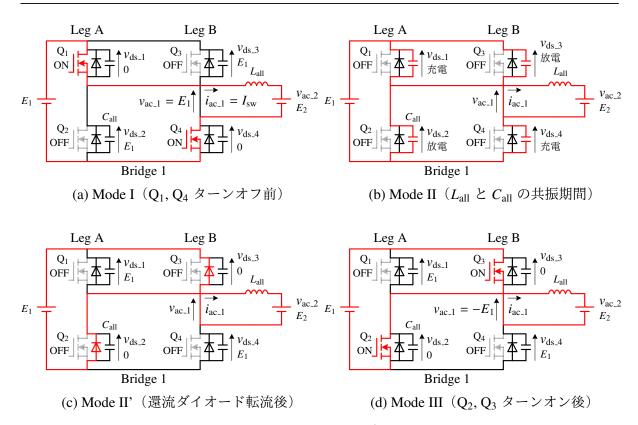

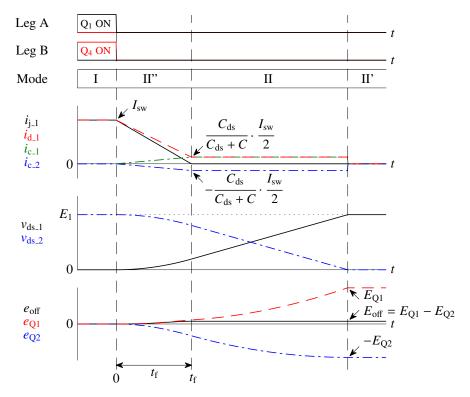

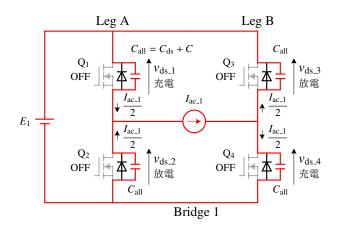

#### 2.3.1 ZVS の動作原理とターンオン損失の発生原理

図 2.10 に図 2.2 の DAB コンバータの Bridge 1 のデッドタイム期間前後の動作モード を,図 2.11 に MOSFET  $Q_2$ ,  $Q_3$  のドレイン-ソース間電圧の理論波形を示す。レグの上下

図 2.10: 図 2.2 の DAB コンバータの Bridge 1 のデッドタイム期間前後の動作モード

の MOSFET の同時オンによる電源短絡防止のために、上下の MOSFET が同時にオフとなるデッドタイムを設ける必要がある。DAB コンバータはこのデッドタイム期間中に発生する交流側の合成インダクタ  $L_{\rm all}$  と MOSFET のドレイン-ソース間の合成容量  $C_{\rm all}$  の 共振を利用することで、ZVS 動作が可能となる。図 2.3 のスイッチングパターンで ZVS 動作を可能にする最小のスイッチング電流は次式で与えられる [4]。

$$I_{\text{ZVS\_min}} = \frac{2\sqrt{E_1 E_2}}{Z} \tag{2.6}$$

$$Z = \sqrt{\frac{L_{\text{all}}}{C_{\text{all}}}} \tag{2.7}$$

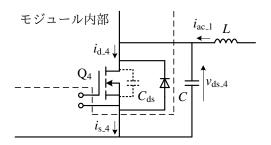

$$C_{\text{all}} = C_{\text{ds}} + C \tag{2.8}$$

ここで、Z は特性インピーダンス、 $C_{\rm all}$  は MOSFET の出力容量  $C_{\rm ds}$  と外付けのスナバキャパシタ C の和である。スイッチング電流が  $I_{\rm ZVS\_min}$  以下となる軽負荷時では ZVS が行えないため、MOSFET のターンオン損失が発生する。MOSFET  $Q_2, Q_3$  の ZVS 動作に着目して、図 2.10 の各動作モードを以下に説明する。

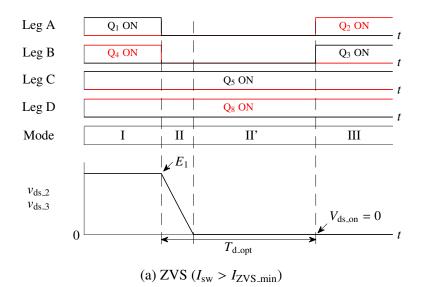

1. Mode  $I: Q_1, Q_4$  がオンでデッドタイム期間の直前

(b) ZVS 可能な最小スイッチング電流 ( $I_{sw} = I_{ZVS\_min}$ )

図 2.11: 図 2.10 の MOSFET Q<sub>2</sub>, Q<sub>3</sub> のドレイン-ソース間電圧の理論波形

- 2. Mode II:  $Q_1$ ,  $Q_4$  がターンオフし,すべての MOSFET がオフとなるデッドタイム 期間中で, $L_{all}$  と  $C_{all}$  の共振により, $Q_2$ ,  $Q_3$  の  $C_{all}$  が放電される。

- 3. Mode II': Mode II と同様にデッドタイム期間中であり、 $Q_2$ ,  $Q_3$  の  $C_{all}$  の放電が 完了し、ドレイン-ソース間電圧が零になった後、 $C_{all}$  から還流ダイオードに転流 する。

- 4. Mode III: Q<sub>2</sub>, Q<sub>3</sub> がターンオンした後の期間

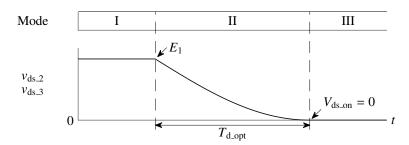

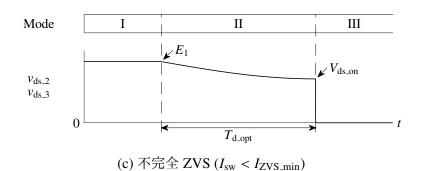

図 2.11(a), (b) に示すように  $I_{sw} \ge I_{ZVS\_min}$  の場合, $Q_2$ ,  $Q_3$  の  $C_{all}$  の放電が完了し,ドレイン-ソース間電圧が零になった後, $Q_2$ ,  $Q_3$  がターンオンするため,ZVS が可能となる。図 2.11(b) の  $I_{sw} = I_{ZVS\_min}$  での波形より,デッドタイムの最適値  $T_{d\_opt}$  は共振周期の 1/4 であり,次式のように表される [31]。

$$T_{\text{d\_opt}} = \frac{\pi}{2} \sqrt{L_{\text{all}} C_{\text{all}}}$$

(2.9)

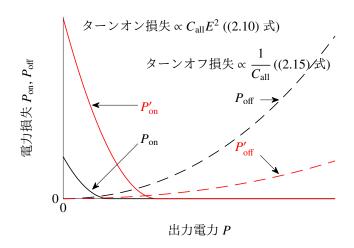

図 2.11(c) に示すように  $I_{sw} < I_{ZVS\_min}$  の場合,Mode II で  $Q_2$ ,  $Q_3$  の  $C_{all}$  の放電が完了せず, $Q_2$ ,  $Q_3$  がターンオンするため, $C_{all}$  に蓄積されたエネルギーが MOSFET のオン抵抗や配線抵抗などで損失として消費され,不完全 ZVS 動作となる。 $E_1 = E_2$  の場合,8 つの MOSFET の合計の不完全 ZVS でのターンオン時の損失  $P_{on}$  は次式で表される。

$$P_{\rm on} = 8C_{\rm all}V_{\rm ds on}^2 f_{\rm sw} {(2.10)}$$

$$V_{\rm ds\_on} = E_1 - \frac{ZI_{\rm sw}}{2}$$

(2.11)

ここで、 $V_{ds.on}$  はターンオン時のドレイン-ソース間電圧である。厳密には Bridge 1, 2 のターンオン時のドレイン-ソース間電圧は異なる。

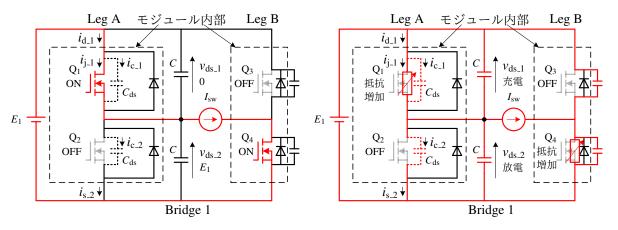

#### 2.3.2 **ZVS** 時のターンオフ損失の発生原理

図 2.12 に図 2.2 の Bridge 1 の MOSFET  $Q_1$ ,  $Q_4$  のターンオフ前後の動作モードを,図 2.13 に  $Q_1$  ターンオフ時の理論波形を示す。以下の理論解析では以下の仮定を導入する。

- $\bullet$  ブリッジ交流端子の電流は一定値  $I_{sw}$  とする。

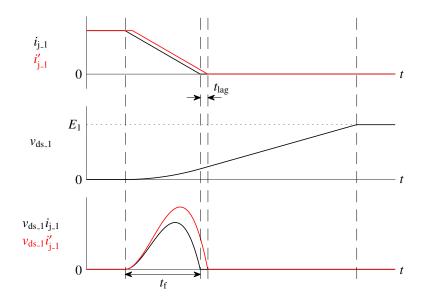

- MOSFET のターンオフ後にジャンクション電流  $i_{i,1}$  は直線的に立ち下がる。

$\mathbf{Q}_1$  のターンオフ時に消費されるエネルギー $e_{\mathrm{off}}$ ,  $\mathbf{Q}_1$  の蓄積エネルギー $e_{\mathrm{Q}1}$ ,  $\mathbf{Q}_2$  の放出エネルギー $e_{\mathrm{O}2}$  は次式で表される。

$$e_{\text{off}} = \int v_{\text{ds}\_1} i_{j\_1} dt \tag{2.12}$$

$$e_{\rm Q1} = \int v_{\rm ds\_1} i_{\rm d\_1} dt \tag{2.13}$$

$$e_{Q2} = \int v_{ds,2} i_{c,2} dt \tag{2.14}$$

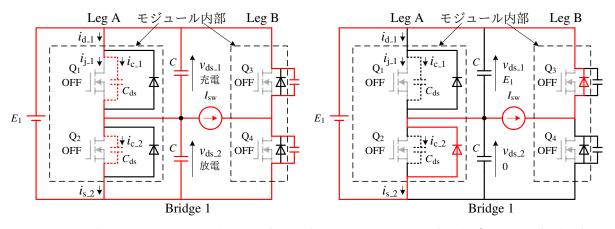

(a) Mode I  $(Q_1, Q_4 ターンオフ前)$

(b) Mode II"(ジャンクション電流立下り期間)

(c) Mode II (ジャンクション電流立下り終了後)

(d) Mode II' (還流ダイオード転流後)

図 2.12: 図 2.2 の Bridge 1 の Q<sub>1</sub>, Q<sub>4</sub> ターンオフ前後の動作モード

ここで、 $v_{ds.1}$  は  $Q_1$  のドレイン-ソース間電圧、 $i_{j.1}$  はジャンクション電流、 $i_{d.1}$  はドレイン電流、 $v_{ds.2}$  は  $Q_2$  のドレイン-ソース間電圧、 $i_{c.2}$  は MOSFET のドレイン-ソース間の寄生容量  $C_{ds}$  の電流である。 $Q_1$  のターンオフ動作に着目して、図 2.12 の各動作モードを以下に説明する。

- 1. Mode  $I: Q_1, Q_4$  がオンでデッドタイム期間の直前

- 2. Mode II":  $Q_1$ ,  $Q_4$  がターンオフし, $Q_1$  のジャンクション電流  $i_{j-1}$  が直線的に減少し,寄生容量  $C_{ds}$  の電流  $i_{c-1}$  は直線的に増加する。

- 3. Mode II:  $i_{i,1}$  が零になった後, $i_{c,1}$  は一定値となる。

- 4. Mode II':  $Q_1$  の  $C_{all}$  の充電が完了した後, $i_{c,1}$  は零となる。

図 2.13: 図 2.12 の Q<sub>1</sub> ターンオフ時の理論波形

$Q_1$  のターンオフ時に消費されるエネルギー  $E_{\text{off}}$  は Mode II" のジャンクション電流  $i_{j,1}$  とドレインソース間電圧  $v_{\text{ds},1}$  の積の積分から次式で表される [31,91,92]。

$$E_{\text{off}} = \int_0^{t_f} v_{\text{ds}\_1} i_{j\_1} dt = \frac{I_{\text{sw}}^2 t_f^2}{48C_{\text{all}}}$$

(2.15)

ここで、 $t_f$  はジャンクション電流の立下り時間である。実際の MOSFET の場合、 $t_f$  のスイッチング電流依存性や、ドレイン-ソース間の寄生容量の電圧依存性が存在するため、さらに複雑な式となる。上式から「ZVS 時のスイッチング損失がターンオフ時の電流にのみ依存し、入出力電圧とはほぼ無関係」であることが明らかになった。

# **2.4 ZVS** 時のスイッチング損失の測定

DAB コンバータのさらなる高効率化のためには、スイッチング損失を定量的に評価する必要がある。軽負荷時に発生するターンオン損失は (2.10) 式によりターンオン時の残留電圧から容易に測定可能である。一方、定格時に支配的となるターンオフ損失は近似した (2.15) 式から容易には算出できない。これは実機の SiC-MOSFET ではさらに複雑な要素が含まれるためである。

スイッチング損失の測定・推定法は以下の4種類に大別できる。

- 1. MOSFET のデータシートからの推定: 一般にダブルパルス試験によるハードスイッチング動作時の結果であり、ZVS 動作時には適用できない。

- 2. 実機のドレイン・ソース間電圧とドレイン電流の瞬時値積による直接測定:スイッチングが高速な SiC-MOSFET の場合,特にプローブの検出遅れの補正 (deskew)が厄介である [25,26]。電流検出遅れを立下り時間の 10%の精度で補正しても,スイッチング損失の測定精度は約 50%で実用的ではない。通常, SiC モジュールと DC バスとの配線距離は寄生インダクタンスを低減するために最短となるように設計する。このため,ドレイン電流測定用のプローブを挿入するためのスペースが狭く,大電流であるほど困難である。測定用のスペースを意図的に確保する場合,寄生インダクタンスが増加し,測定結果に影響を及ぼすことになる。さらに, ZVS の場合,レグ上下の MOSFET の蓄積・放出エネルギーの差分から測定するため,ドレイン-ソース間の合成容量が大きいほど測定が困難となる [93-96]。

- 3. 温度による間接測定 [26–30]: 測定精度は 10 ~ 20%で, 直接測定に比べて高精度 な測定が可能であるが, 測定時間が長いことや温度測定の基準を固定するために 恒温槽などの特別な測定環境が必要である点から簡便であるとは言えない。

- 4. 高精度に測定した全損失からの損失分離 [31]: 異なる動作周波数で高精度に測定した全損失から、スイッチング損失を分離する。異なる動作周波数での全損失、インダクタや変圧器の磁気デバイスの鉄損の測定誤差の差分がスイッチング損失の測定誤差に影響する。特に磁気デバイスの鉄損の測定精度は力率角が 90° に近づくほど、低くなる。本研究で使用するテストベンチの場合、インダクタ鉄損の測定誤差が支配的であり、最悪のケースとしてインダクタ鉄損の測定誤差が±10%の場合、スイッチング損失の測定誤差は 20%となる。温度による間接測定と同程度の測定精度を保ちつつ、短時間で、特別な測定環境なしで、簡便に測定可能であるため、実用的な手法である。しかし、昇降圧動作時には入出力のブリッジ変換器の損失が異なるため、[31] で提案された損失分離法ではブリッジ変換器ごとの損失を分離することができない。

本論文では、[31]をベースとして、式 (2.15)の「実用的な昇降圧動作の範囲では、零電圧スイッチング時のスイッチング損失がターンオフ時の電流にのみ依存し、入出力電圧にはほぼ無関係」である理論に着目することで、昇降圧動作時にも適用可能なスイッチング損失の評価法を提案する。

(a) 入出力電力からの効率測定

(b) 高精度な効率測定を実現する構成

図 2.14: 2 種類の電力変換効率の測定法

#### 2.4.1 全損失・変換効率の測定誤差

図 2.14 に 2 種類の電力変換効率の測定法を示す。図 2.14(a) は入出力電力を個別に測定し、それらの差分から全損失を測定する手法である。全損失  $P_{loss}$  と変換効率  $\eta$  は次式で算出できる。

$$P_{\text{loss}} = P_{\text{in}} - P \tag{2.16}$$

$$\eta = \frac{P}{P_{\rm in}} \tag{2.17}$$

ここで、 $P_{\rm in}$  は入力電力で、P は出力電力である。上式から全損失の測定誤差率  $\Delta P_{\rm loss}/P_{\rm loss}$  と変換効率の測定誤差率  $\Delta \eta/\eta$  は次式で算出できる。

$$\frac{\Delta P_{\text{loss}}}{P_{\text{loss}}} = \frac{1}{1 - \eta} \left( \frac{\Delta P_{\text{in}}}{P_{\text{in}}} - \frac{\Delta P}{P} \right) \tag{2.18}$$

$$\frac{\Delta \eta}{\eta} = \frac{\Delta P}{P} - \frac{\Delta P_{\rm in}}{P_{\rm in}} \tag{2.19}$$

ここで, $\Delta P_{\rm in}/P_{\rm in}$  は入力電力の測定誤差率, $\Delta P/P$  は出力電力の測定誤差率である。変換効率 99.3%の場合,現在入手可能な高精度なパワーアナライザ(電力測定誤差: 0.2% [32])を使用しても,全損失の測定誤差率は (2.18) 式から 57%,変換効率の測定誤差率は (2.19) 式から 0.4%となり,測定精度は不十分である。

図 2.14(b) は入出力の端子を直接接続した構成で、全損失を直接高精度に測定可能な点に特長がある [33]。変換効率  $\eta$  は出力電力 P と電力損失  $P_{loss}$  を個別に測定することによって、次式で算出できる。

$$\eta = \frac{P}{P + P_{loss}} \tag{2.20}$$

上式から変換効率の測定誤差率 Δη/η は次式で近似できる。

$$\frac{\Delta \eta}{\eta} = (1 - \eta) \frac{\Delta P}{P} \tag{2.21}$$

上記と同条件で全損失の測定誤差率はパワーアナライザの電力測定精度で決定するため,全損失の測定誤差は0.2%となり,変換効率の測定誤差率は(2.21)式から0.0014%となり,高効率な変換効率の評価に適した測定法である。

[31] で提案された損失分離法は、図 2.14(b) を使用し、「全損失が高精度に測定可能」である特長を活用することで簡便かつ実用的なスイッチング損失の分離を可能にする。

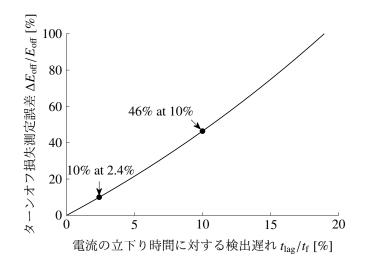

#### 2.4.2 電流検出遅れによるターンオフ損失の測定誤差

図 2.15 に図 2.13 で電流検出遅れが発生した場合の理論波形を示す。電流検出遅れによるターンオフ損失の測定誤差  $\Delta E_{

m off}/E_{

m off}$  は次式で表される。

$$\frac{\Delta E_{\text{off}}}{E_{\text{off}}} = d\left(4 + 6d + 4d^2 - d^3\right) \tag{2.22}$$

$$d = \frac{t_{\text{lag}}}{t_{\text{f}}} \tag{2.23}$$

ここで、d は電流の立下り時間  $t_f$  に対する検出遅れ  $t_{lag}$  の割合である。図 2.16 に (2.22) 式から算出した電流検出遅れに対するターンオフ損失の測定誤差を示す。ターンオフ損失の測定誤差を 10%以下に抑えるためには、電流の立下り時間に対して 2.4%以下の高精度な補正が要求される。SiC-MOSFET の場合、電流の立下り時間はターンオフ時の電流に依存するが、数十 ns となる。検出遅れの短い CT で電流を測定する場合でも、同軸ケーブル 1 m 当たり約 5 ns の遅延が発生するため、立下り時間に対して 10%以上の補正誤差が含まれる。この場合、ターンオフ損失には 46%以上の測定誤差が発生するため、測定精度は不十分である。

### 2.4.3 ターンオフ損失と測定可能なエネルギーの関係

ZVS 時のターンオフ損失を実機のドレイン・ソース間電圧とドレイン電流の瞬時値積から測定する場合,MOSFET の構造上ジャンクション電流を直接測定できないため,レグ上下の MOSFET の蓄積・放出エネルギーの差分から測定する必要がある [93–96]。図 2.13 の  $Q_2$  が放出するエネルギー  $E_{Q2}$  は次式で表される。

$$E_{\rm Q2} = \frac{1}{2} C_{\rm ds} E_1^2 \tag{2.24}$$

$Q_1$  が蓄積するエネルギー $E_{O1}$  は (2.15), (2.24) 式の和から次式で表される。

$$E_{\rm Q1} = E_{\rm Q2} + E_{\rm off} \tag{2.25}$$

図 2.15: 図 2.12 で電流検出遅れが発生した場合の理論波形

図 2.16: 図 2.15 の電流検出遅れに対する ZVS 時のターンオフ損失の測定誤差

測定可能なエネルギー  $E_{Q2}$  に対するターンオフ時に消費されるエネルギー  $E_{off}$  の割合は (2.15), (2.24) 式から次式で表される。

$$\frac{E_{\text{off}}}{E_{\text{Q2}}} = \frac{I_{\text{sw}}^2 t_{\text{f}}^2}{24(C + C_{\text{ds}})C_{\text{ds}}E_1^2}$$

(2.26)

スナバキャパシタ C, MOSFET のドレイン-ソース間の寄生容量  $C_{ds}$ , 直流電圧  $E_1$  が大きいほど、上式が小さくなるため、測定誤差が大きくなる。

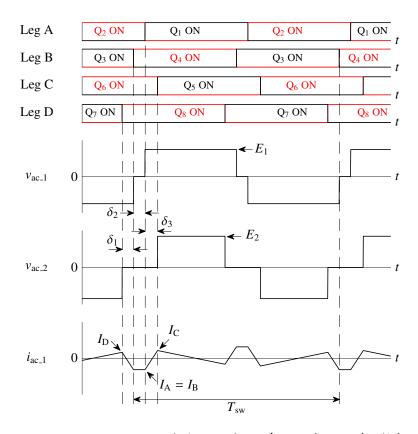

図 **2.17:** 図 **2.2** の  $E_1 < E_2$  での入出力の両方のブリッジのレグ間位相シフト制御適用時の理論波形

# 2.5 軽負荷時や昇降圧動作時の低損失化

軽負荷時や昇降圧動作時の損失を低減するための手法は大きく2つに分類される。以下では、これらの手法の特長と課題について述べる。

#### 2.5.1 レグ間位相シフト

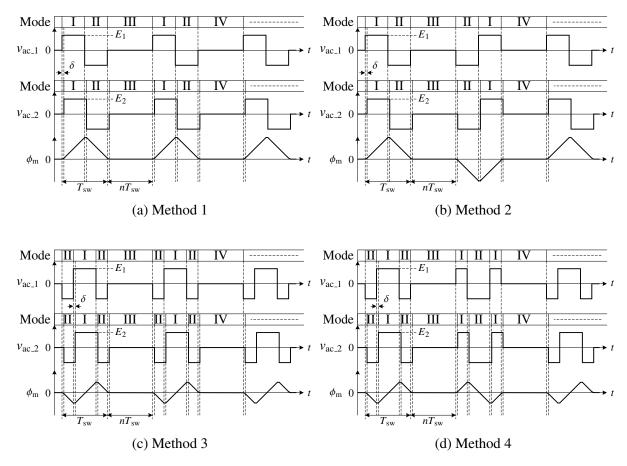

DAB コンバータはブリッジ間の位相シフト制御を採用するのが一般的であるが、昇降圧動作時には高圧側ブリッジの MOSFET のターンオフ時の電流が増加するため、スイッチング損失が増大する。これに対して、いわゆる "one-pulse PWM" あるいはレグ間位相シフト制御の適用が古くから知られている [5,43,47]。入出力の一方のブリッジにレグ間位相シフト制御を適用する手法は、phase shift plus one side modulation (PSPM) [48–50]または extended-phase-shift (EPS) control [51]、両方のブリッジにレグ間位相シフト制御を適用する手法は、dual-phase-shift (DPS) control [52–54] または triple-phase-shift (TPS) control [55–63] などと呼ばれている。

図 2.18: 間欠運転の制御概念

図 2.17 に図 2.2 の  $E_1 < E_2$  での入出力の両方のブリッジのレグ間位相シフト制御適用時の理論波形を示す。制御変数はブリッジ間の位相シフト制御に比べて,2 つ増加する。3 つの位相シフト角には 2 つの自由度が存在し,無効電力,電流ピーク値,電流実効値,あるいは損失の最小化という制約条件を課すのが一般的である。インダクタ電流波形の形状は Leg A, B, C, D の 4 つのスイッチングパターンを任意に入れ替えることで変化するため,4!/2 = 12 パターン存在する [56]。ただし,Leg A と Leg B,Leg C と Leg D が同時に入れ替わった場合,インダクタ電流波形の形状は変化しないことに注意する必要がある。このため,制御変数を決定するためのアルゴリズムは複雑であり,実用的ではない。

これに対して、高圧側ブリッジのみにレグ間位相シフトを適用する手法は、入出力の両方のブリッジのレグ間位相シフト制御に比べて制御アルゴリズムが単純である。しかし、文献 [49] では、損失解析結果から全出力領域で DAB コンバータの全損失が最小となるように高圧側ブリッジのレグ間位相シフト制御の二次元の制御変数を決定しているが、制御アルゴリズムが複雑であった。本論文では、昇降圧動作時の定格出力領域の損失低減に焦点を絞って制約条件を設けることで、制御アルゴリズムが単純な高圧側ブリッジへのレグ間位相シフト制御を提案する。

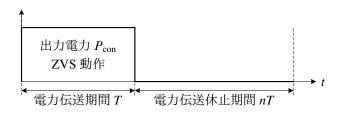

#### 2.5.2 間欠運転

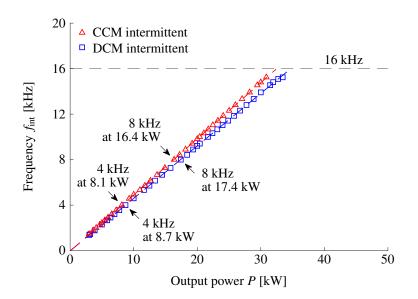

間欠運転 (intermittent operation) は電力伝送休止期間を設け、伝送電力を平均的に調整しようとする制御法であり、パルス密度変調 (PDM: Pulse-Density Modulation) [64,65]、バーストモード (Burst Mode) [66–72]、line-cycle skipping (LCS) [73] を包含する広い制御概念である。英語で"burst"は「破裂する、爆発する」という意味であり、通信分野では一度に複数のパルス状のデータを「一括」で転送するという概念として使用されている [75,76]。本論文で提案する手法は電力を送る動作と休む動作が 1 周期ごとに交互に行われることから、より適切な用語として「間欠運転」 (intermittent operation) を使用する。

図 2.18 に間欠運転の制御の概念図を示す。間欠運転時の出力電力  $P_{int}$  は電力伝送期間 T の出力電力  $P_{con}$ ,電力伝送休止期間 nT から次式で表される。

$$P_{\rm int} = \frac{P_{\rm con}}{1+n} \tag{2.27}$$

$P_{\text{con}}$  を ZVS 動作可能な出力電力に設定することで、軽負荷時でも ZVS 動作が可能となる。 $P_{\text{con}}$  は ZVS 可能な最小の出力電力に固定すればよいため、制御変数は n の 1 つのみで、TPS などと比べて制御アルゴリズムが単純である点が特長である。図 2.1(c) のような直列共振コンバータの場合、n は整数となるが、本研究で扱う図 2.1(a) のようなの非共振コンバータの場合には上記の制約はなく、n は実数として自由に調整できる。

DAB コンバータの軽負荷時の低損失化を実現する制御法として、電流不連続モード (DCM: Discontinuous-Current Mode) 間欠運転があるが、電力伝送の開始時と終了時のみ ZVS が達成できないため、さらなる低損失化の可能性が残されている [70,74,77]。本論文では、DCM間欠運転の発展形として新たに電流連続モード (CCM: Continuous-Current Mode) 間欠運転を提案する [79]。これは電力伝送休止期間に意図的に電流を還流させることで、すべてのスイッチング時で ZVS が可能になる点に特長がある。還流電流により MOSFET の導通損失の増加が懸念されるが、低オン抵抗の SiC-MOSFET を適用することで、この欠点は克服できる。CCM間欠運転が実現できれば、MOSFET のドレイン-ソース間のスナバキャパシタの静電容量を意図的に大きく設定し、広範囲な出力領域での高効率化を達成できる。

# 2.6 本章のまとめ

本章では、大容量 DAB コンバータの回路方式や電力変換効率の動向について要約した。本論文では、大容量化と単純化に適した図 2.2 の DAB コンバータを研究対象とする。10 kW 以上の大容量 DAB コンバータの変換効率の文献調査により、大容量で効率評価を実施している研究機関は、本学(東工大)を含めて 6 大学しか存在しないことと、本論文で実証した変換効率 99.3%が現時点での世界最高効率であることを示した。よって、大容量 DAB コンバータの詳細な効率評価を行うことには学術的・技術的な意義がある。

次に、変換効率向上のための課題と解決策を整理した。本論文の位置付けを以下の3 点に要約する。

1. DAB コンバータのさらなる高効率化のためには、軽負荷時や昇降圧動作時に増大

2.6 本章のまとめ

するスイッチング損失を定量的に評価する必要がある。電圧・電流の瞬時値積からスイッチング損失を測定する方法では、SiC-MOSFET のスイッチングが高速であるため、電流検出遅延の影響を取り除くことが困難であり、実用的な測定精度を得ることは期待できない。これに対して、[31] で提案された高精度に測定した全損失からの損失分離が実用的であるが、昇降圧動作時では入出力のブリッジ変換器の損失が異なるため、適用できない。本論文では、「零電圧スイッチング時のスイッチング損失がターンオフ時の電流にのみ依存し、入出力電圧とはほぼ無関係」であることを理論と実験で確認し、昇降圧動作時にも適用可能なターンオフ時の電流からのスイッチング損失の評価法を提案する

- 2. DAB コンバータの1つ目の課題として軽負荷時の損失増大が挙げられ、これは ZVS 動作が不完全となることによるターンオン損失の増大が原因である。この 解決策として制御アルゴリズムが単純な間欠運転を検討する。従来の電流不連続 モード間欠運転では電力伝送の開始時と終了時のみ ZVS が不可となるため、さら なる低損失化の可能性が残されている。本論文では、1.で測定したスイッチング 損失を用いて従来の間欠運転の損失増大を定量的に明らかにし、電力伝送休止期 間中に電流を意図的に還流させることにより、すべてのスイッチング時で ZVS が 可能な電流連続モード間欠運転を提案するこれは低オン抵抗な SiC-MOSFET に 適した手法である。

- 3. 2つ目の課題として昇降圧動作時の損失増大が指摘されており、これはターンオフ時の電流の増加によるターンオフ損失の増大が原因である。これを低減する制御法としてレグ間位相シフト制御が検討されているが、制御アルゴリズムが複雑であった。本論文では、1.で測定したスイッチング損失に基づいて、定格出力領域の損失低減に焦点を絞って制約条件を設けることで、制御アルゴリズムが単純な高圧側ブリッジへのレグ間位相シフト制御を提案する。

# 第3章

# スイッチング損失の分離

本章では、昇降圧動作時にも適用可能な零電圧スイッチング時のスイッチング損失の分離法を検討する。これは [31] をベースとしており、電圧・電流の瞬時値積による直接測定が困難な SiC-MOSFET のスイッチング損失をターンオフ時の電流から簡便かつ実用的に分離可能である点に特長がある。1.2-kV 400-A SiC-MOSFET/SBD 4-in-1 モジュールを用いた 100-kW 16-kHz DAB コンバータのテストベンチを設計・製作し、損失分離を行う。分離したスイッチング損失の測定誤差について検討し、温度による間接測定と同程度であることを示す。「実用的な昇降圧動作の範囲では、零電圧スイッチング時のスイッチング損失が入出力電圧とはほぼ無関係」であることを理論と実験により議論し、提案法が昇降圧動作時にも適用できることを実証する。

# 3.1 実験システム

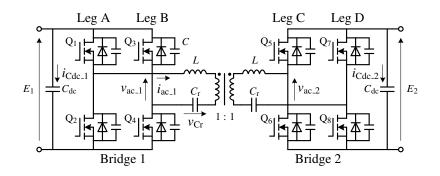

### 3.1.1 システム構成

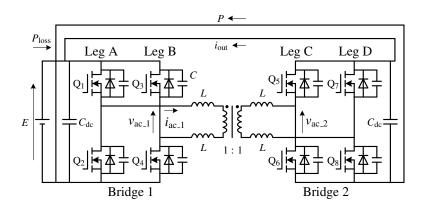

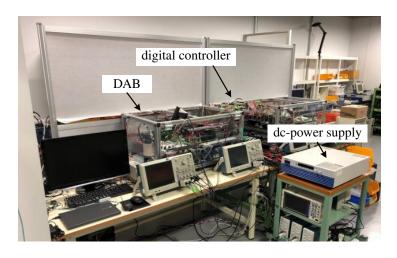

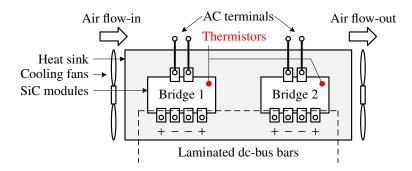

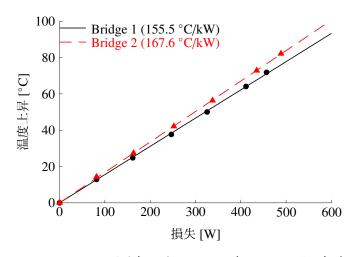

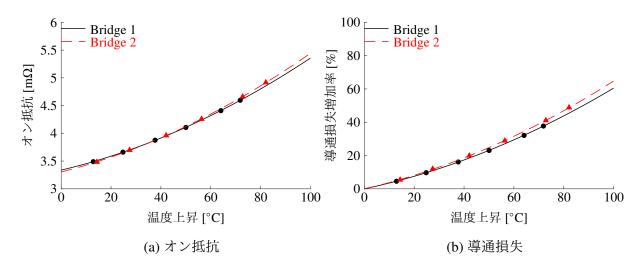

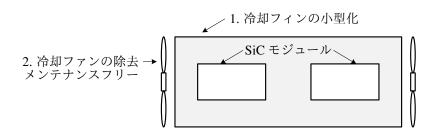

図 3.1 に 850-V 100-kW 16-kHz DAB コンバータの変換効率を高精度に測定可能なテストベンチを,表 3.1 に実験定数を,表 3.2 に冷却システム示す。本実験では,1.2-kV 400-A SiC-MOSFET/SBD 4-in-1 モジュール(三菱電機,FMF400BX-24A)を 2 個使用した [97]。表 3.3 に SiC モジュールの代表的な電気的特性を示す。図 3.2 にテストベンチと測定機器の外観を示す。本論文のテストベンチは効率向上を最優先に設計されており,SiC-MOSFET モジュールの冷却フィンは小型化することができる。しかし,小型化に関しての最適設計は本論文の目的ではないため,テストベンチの中で冷却フィンの体積は変圧器の約 7 倍であり,最大である。

変圧器の磁性材料には厚さ 14 µm の最新のノーカットナノ結晶軟磁性材料(日立金属,

図 3.1:  $E_1 = E_2 = E$  での 750-V 100-kW 16-kHz DAB コンバータのテストベンチ

表 3.1: 図 3.1 の 750-V 100-kW 16-kHz DAB コンバータの実験定数

| Continuous power rating                 |              | 100 kW                              |

|-----------------------------------------|--------------|-------------------------------------|

| Short-term power rating                 |              | 150 kW                              |

| Input/output dc voltage                 | $E_1 = E_2$  | 750 V                               |

| Switching frequency                     | $f_{ m sw}$  | 16 kHz                              |

| Drain current rating of each SiC-MOSFET |              | 400 A                               |

| Inductor rms current                    | $I_{ m rms}$ | 147 A at 100 kW<br>(36.8% of 400 A) |

| DC capacitor                            | $C_{ m dc}$  | $400\mu\mathrm{F}$                  |

| Unit capacitance constant [98]          | $H_{ m dc}$  | 1.1 ms at 750 V                     |

| Snubber capacitor                       | С            | 9 nF                                |

| Auxiliary inductor                      | L            | 4.3 μH (7.6%*)                      |

| Total leakage inductance                | l            | 1 μH (1.8%*)                        |

| Dead time                               | $T_{\rm d}$  | $0.8 \mu\mathrm{s}$                 |

| Transformer core material               |              | FINEMET**                           |

| Saturation magnetic-flux density        |              | 1.23 T                              |

| Maximum magnetic flux density           |              | 0.64 T at 0 kW                      |

| Maximum magnetic-flux density           |              | (52.0% of 1.23 T)                   |

| Transformer turns ratio                 |              | 1:1                                 |

| Auxiliary inductor core material        |              | Sendust***                          |

| Saturation magnetic-flux density        |              | 1 T                                 |

| Maximum magnatic flux dancity           |              | 0.21 T at 100 kW                    |

| Maximum magnetic-flux density           |              | (21.0% of 1 T)                      |

<sup>\*</sup>On a single-phase 750-V 100-kW 16-kHz base.

商品名「ファインメット」)を使用している [23]。絶縁試験により一次側と二次側の絶縁 耐圧  $5 \, kV$  が実証されている。直流キャパシタは  $100 \, \mu F$  のフィルムキャパシタ (Cornell Dubilier 944U101K122AC, 耐圧  $1.2 \, kV$ , 最大電流実効値  $64 \, A$  [99]) を使用しており,一次側と二次側でそれぞれ  $4 \, 並$ 列接続した。外付けインダクタの磁性材料には Fe-Si-Al

<sup>\*\*</sup>Nano-crystalline soft-magnetic material from Hitachi Metals.

<sup>\*\*\*</sup>Fe-Si-Al alloy from magnetics.

3.1 実験システム 39

表 3.2: 図 3.1 の 750-V 100-kW 16-kHz DAB コンバータの冷却システム

| Cooling for SiC modules | forced-air convection |

|-------------------------|-----------------------|

| Cooling for transformer | natural convection    |

| Cooling for inductors   | natural convection    |

表 3.3: 1.2-kV 400-A SiC-MOSFET/SBD 4-in-1 モジュールの電気的特性(三菱電機, FMF400BX-24A) [97]

| Drain-source voltage (maximum)                                                                                                 | $V_{ m DS}$  | 1200 V                 |

|--------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------|

| Drain current (maximum, DC)                                                                                                    |              | 400 A                  |

| Gate-source voltage (maximum)                                                                                                  |              | ±20 V                  |

| Gate-source threshold voltage                                                                                                  | $V_{th}$     | 1 V                    |

| Static drain-source on resistance (terminals) $(I_D = 400 \text{ A}, \ V_{GS} = 15 \text{ V}, \ T_{vj} = 25 ^{\circ}\text{C})$ | $r_{\rm on}$ | 4.15 mΩ                |

| Static drain-source on resistance (chip)                                                                                       |              |                        |

| $(I_{\rm D} = 400 \text{ A}, \ V_{\rm GS} = 15 \text{ V}, \ T_{\rm vj} = 25 ^{\circ}\text{C})$                                 | $r_{\rm on}$ | $3.2~\mathrm{m}\Omega$ |

| Internal stray inductance (P-N)                                                                                                | $L_{\rm s}$  | 18 nH                  |

|                                                                                                                                |              |                        |

図 3.2: 図 3.1 のテストベンチと測定機器の外観

合金(Magnetics,商品名「センダスト」)を使用した [20]。4個の外付けインダクタは各ブリッジの交流側に対称に配置されている。これにより変圧器,外付けインダクタ,SiC-MOSFET モジュールに存在する寄生容量を通して流れるコモンモード電流を低減することができる。図 3.1 のテストベンチには外付けインダクタと直列に DC ブロッキングキャパシタを接続していないため,変圧器に直流偏磁がする可能性がある。しかし,DC ブロッキングキャパシタなしでも,定常時と過渡時を含めて変圧器の直流偏磁が発生しないことを後の実験で実証する。

### 3.1.2 全損失と変換効率の定義

本論文で設計・製作したテストベンチは企業の製品ではなく大学の試作装置である。 そのため、体積、重量、電力密度について議論することは意味がない。主な理由は試作 装置は製品より大きな空間が必要なためである。例えば、電圧や電流を測定するために、 空間的に余裕のある装置設計を行う必要がある。もう一つの理由は、今回の試作装置で は最適化が目的でなく、損失分析が目的であるためである。

本論文ではデジタルコントローラ、8枚のゲートドライブ回路、ヒートシンクに取り付けた4台の冷却ファンのような補機の損失<sup>1</sup>を除いた損失の和を「全損失」と定義する。補機損失は出力電力と無関係であるため、分離しても問題ない。

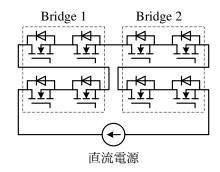

#### 3.1.3 変換効率

Bridge 2 の出力端子を Bridge 1 の入力端子に接続することで、出力電力 P を直流電源側(入力側)に回生する。これにより、入力側の直流電源は DAB コンバータで生じる電力損失  $P_{loss}$  相当分のみを供給するので、大学の実験室の直流電源でも 100 kW 定格運転が可能になる。さらに、出力電力 P と電力損失  $P_{loss}$  を個別に測定することによって、DAB コンバータの入力から出力までの電力変換効率  $\eta$  を (2.20) 式から高精度に計算できる。実験に使用したパワーアナライザ (HIOKI 3390-10 [32]) の直流電力の測定精度はフルスケールで 0.2%、定格 100 kW 時の全損失の割合は 1%であるため、(2.21) 式より効率の測定誤差は 0.002%となる。将来的に、全損失  $P_{loss}$  の低減やディジタルパワーアナライザの測定精度の向上が進めば、効率の測定誤差をさらに低減できる。なお、本論文の全損失にはゲート駆動回路、制御回路、冷却ファンなどの補機損失は含まない。

# 3.2 実験結果

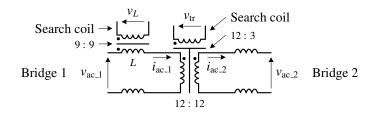

### **3.2.1** $v_L, v_{\rm tr}, i_{\rm m}$ の測定法

図 3.3 に外付けインダクタの誘導起電力 $v_L$ ,変圧器の誘導起電力 $v_{tr}$ の測定環境を示す。外付けインダクタのコアには主巻線(巻数 9)とサーチコイル(巻数 9)を巻いており、センスコイルから誘導起電力 $v_L$ を測定する。変圧器のコアには一次二次巻線(巻数

<sup>&</sup>lt;sup>1</sup> 定格 100 kW での補機損失は合計で 82 W であり、4 台の冷却ファンが約半分を占める。しかし、本研究では補機の最適化は行っていない。最適化することで補機損失をさらに低減できる。

3.2 実験結果 41

図 3.3: 図 3.1 の v<sub>L</sub>, v<sub>tr</sub> の測定環境

12)とサーチコイル(巻数 3)を巻いており、同様に誘導起電力 $\nu_{tr}$ を測定する。変圧器の励磁電流 $i_{m}$ は次式のように変圧器の一次側の電流 $i_{ac.1}$ と二次側の電流 $i_{ac.2}$ の差分から測定する。

$$i_{\rm m} = i_{\rm ac\_1} - i_{\rm ac\_2} \tag{3.1}$$

これらの実験波形から3.3節の損失分離で外付けインダクタと変圧器の鉄損を算出する。

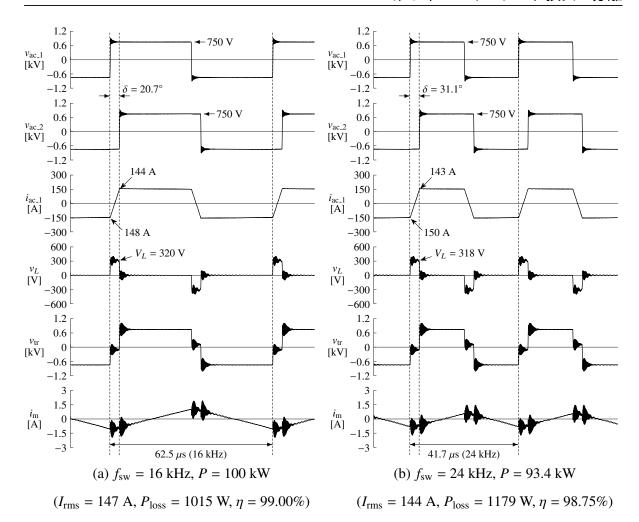

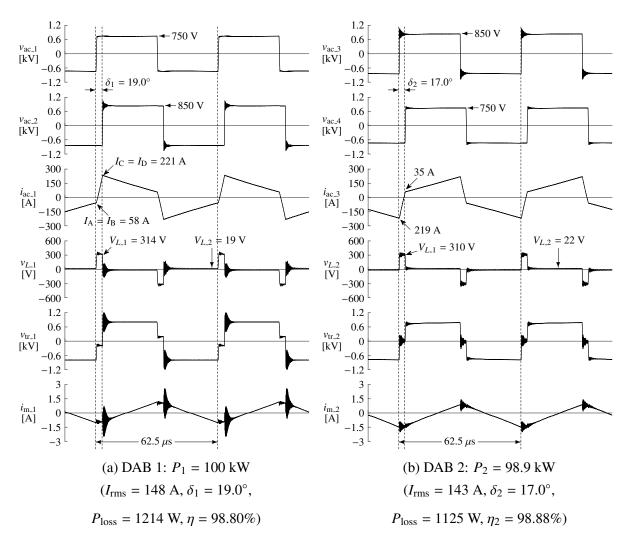

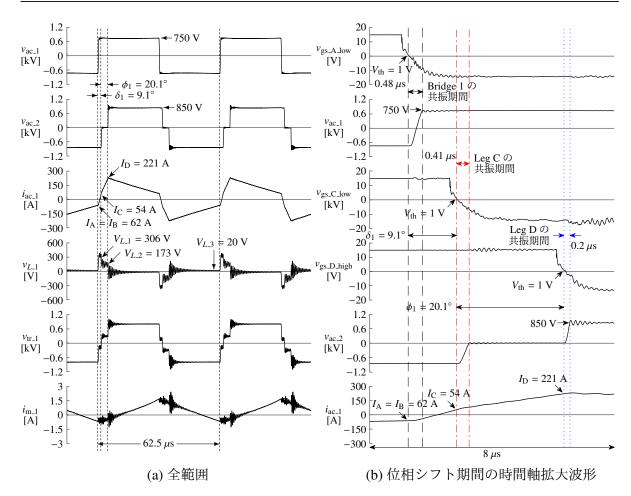

#### 3.2.2 実験波形

図 3.4(a) に図 3.1 のテストベンチで得られた  $E_1 = E_2 = 750$  V,  $f_{sw} = 16$  kHz, P = 100 kW での実験波形を示す。図 3.4(b) に MOSFET のターンオフ時の電流が図 3.4(a) と等しくなるように設定した場合の  $f_{sw} = 24$  kHz での実験波形を示す。以降,MOSFET のターンオフ時の電流をスイッチング電流と呼ぶ。スイッチング電流を等しくするために,位相シフト角は 16 kHz の 20.7° に対して 24 kHz では 1.5 倍の 31.1° に設定した。16 kHz での全損失 1015 W は,24 kHz で 1179 W となり,164 W 増加した。ただし,一次側二次側の直流リンク間を接続するリッツ線の配線抵抗損失は事前に差し引いた。(2.20) 式から計算した変換効率は 16 kHz で 99.00%,24 kHz で 98.75%となり,0.3%低下した。これは,スイッチング周波数に比例して,SiC モジュールのスイッチング損失が 1.5 倍に増加したためであり,3.3 節ではこの仮定を使用して損失分離を行う。インダクタの誘導起電力  $\nu_L$  は位相シフト期間の短い時間幅を有するパルス波形となり,実効値は 16 kHzで 107 V,24 kHzで 131 V となり,1.22 倍で理論と同様に周波数の平方根に比例する。変圧器の誘導起電力  $\nu_{tr}$  は 180° から位相シフト期間を引いた時間幅を有するパルス波形となり,180° 通電波形に近い。変圧器の励磁電流  $i_{tr}$  から DC ブロッキングキャパシタなしでも直流偏磁が発生しないことを実証した。

図 3.4: 図 3.1 の  $E_1 = E_2 = 750$  V でのターンオフ時の電流を等しく設定した場合の実験波形

## 3.3 損失分離

本論文では電流・電圧の瞬時値積による直接測定が困難な ZVS 時のスイッチング損失を簡便かつ実用的に分離する手法を提案する。これは、スイッチング電流が等しい条件で、異なる 2 種類のスイッチング周波数での実験波形からスイッチング損失を分離する点に特長がある。SiC モジュール、インダクタ、変圧器などの温度上昇による損失増加を無視するために、実験はすべて 1 分以内の短時間動作で行い、十分な冷却期間を設けた。以下の損失計算はすべて室温を仮定して行う。

3.3 損失分離 43

図 3.5:  $E_1 = E_2$  での損失分離手順

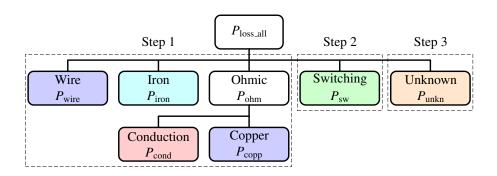

#### 3.3.1 概要

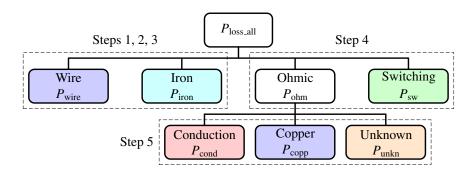

図 3.5 に [31] をベースとして新たに提案する損失分離の手順を示す。本論文では、高精度に測定した全損失を以下の損失に分離する。

- 一次側二次側の直流リンク間を接続するリッツ線の配線抵抗損失 Pwire

- 外付けインダクタと変圧器の銅損  $P_{\text{copp}}$ , 鉄損  $P_{\text{iron}}$

- MOSFET の導通損失  $P_{cond}$ , スイッチング損失  $P_{sw}$

- 未知損失 P<sub>unkn</sub>

未知損失には具体的に以下の損失が含まれる。

- 1. DC バスバーの抵抗損失

- 2. 直流キャパシタの等価直列抵抗での損失

- 3. 巻線の表皮効果や近接効果による抵抗損失増加分

- 4. SiC モジュールや磁気デバイスの巻線の温度上昇による抵抗損失増加分

未知損失 1.はラミネートバスバーを使用し、その長さは 23 cm、幅は 13 cm であるため、無視できると考えられる。未知損失 2.の直流キャパシタの等価直列抵抗による損失  $P_{Cdc}$  はフィルムキャパシタを一次側と二次側でそれぞれ 4 並列接続していることから次式で算出できる。

$$P_{\rm Cdc} = 8R_{\rm Cdc}I_{\rm Cdc\_rms}^2 \tag{3.2}$$

上式に実験で使用した等価直列抵抗  $R_{Cdc}=1.3~\text{m}\Omega$  [99],定格 750 V, 100 kW, 16 kHz での電流実効値の理論値  $I_{Cdc\_rms}=14.2~\text{A}$  を代入すると 2 W となり,全損失 1015 W に対して 0.2%であるため,無視できる。未知損失 3.については使用する周波数が 16 kHz と 24 kHz であり,リッツ線を使用しているため,無視できると考えられる。未知損失 4.に

図 3.6: 正弦波でのインダクタ・変圧器の誘導起電力, 励磁電流の理論波形

ついては SiC モジュールの場合,短時間動作でも温度上昇による抵抗損失増加分は無視できないため,支配的であると考えられる。具体的な手順について, $Step\ 1\sim 5$  に分けて説明する。

### 3.3.2 Step 1: 配線抵抗損失

一次側と二次側の直流リンクを接続するリッツ線の配線抵抗損失  $P_{\text{wire}}$  は配線の直流抵抗  $R_{\text{wire}}$  と出力直流電流  $I_{\text{out}}$  から次式で計算できる。

$$P_{\text{wire}} = R_{\text{wire}} I_{\text{out}}^2 \tag{3.3}$$

ここで、配線の直流抵抗値  $R_{\rm wire}=0.54~{

m m}\Omega$  を使用する。

DAB コンバータの全損失  $P_{loss}$  はパワーアナライザで測定したテストベンチ全体の損失  $P_{loss,all}$  から上式の配線抵抗損失  $P_{wire}$  を差し引いた値から次式で計算できる。

$$P_{\text{loss}} = P_{\text{loss\_all}} - P_{\text{wire}} \tag{3.4}$$

### 3.3.3 Step 2: 変圧器鉄損

変圧器の鉄損  $P_{\text{tr.iron}}$  は誘導起電力  $v_{\text{tr}}$  と励磁電流  $i_{\text{m}}$  の瞬時値の積から次式で計算できる。

$$P_{\text{tr.iron}} = \frac{1}{T_{\text{sw}}} \int_{0}^{T_{\text{sw}}} v_{\text{tr}} i_{\text{m}} dt$$

(3.5)

ここで、 $T_{sw}$  (=  $1/f_{sw}$ ) はスイッチング周期である。

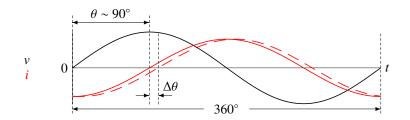

図3.6に正弦波での誘導起電力、励磁電流の理論波形を示す。電圧と電流の瞬時値の積から損失を算出する場合、電圧と電流の位相差が重要なファクターとなる。正弦波で

3.3 損失分離 45

の電力損失誤差  $\Delta P$  は次式で表される。

$$\Delta P = \left(\frac{\cos(\theta + \Delta\theta)}{\cos(\theta)} - 1\right) \times 100\tag{3.6}$$

ここで、 $\theta$  は電圧と電流の位相差、 $\Delta\theta$  は位相誤差である。

誘導起電力 $\nu_{tr}$ はサーチコイルから受動プローブ(Tektronix TPP1000,周波数帯域:  $\sim 1~\text{GHz}$ )で測定した。励磁電流 $i_m$ は交流成分測定用のCT(UR\_D CTL-35-S162-5F-1R10-CL1,周波数帯域:  $20~\text{Hz} \sim 15~\text{MHz}$ )と,直流成分測定用のAC/DC電流プローブ(Tektronix TCP0150,周波数帯域:  $\sim 20~\text{MHz}$ )を併用して測定した。使用した変圧器の場合には誘導起電力と励磁電流の位相差は 16~kHzで最大  $84^\circ$ であり,(3.6)式から損失誤差 10%では位相誤差 105~ns ( $0.6^\circ$ )が許容される。使用した受動プローブと CT の検出による位相誤差は 20~ns 以下であるため,(3.5)式から損失誤差 2%以下で算出可能である。

### 3.3.4 Step 3: インダクタ鉄損

使用したセンダストインダクタの  $16 \, \mathrm{kHz}$  での位相差は  $89.9^\circ$  と極めて  $90^\circ$  に近いため,(3.6) 式から損失誤差 10%に抑えるためには電流の検出遅れを  $1.7 \, \mathrm{ns}$  以下の精度で補正する必要がある。検出遅れの短い CT で電流を測定する場合でも,同軸ケーブル  $1 \, \mathrm{m}$  当たり約  $5 \, \mathrm{ns}$  の遅延が発生するため,現実的ではない。

4 つの外付けインダクタの合計の鉄損  $P_{L,iron}$  は矩形波励磁で適用可能な次式の拡張スタインメッツ方程式 (improved Generalized Steinmetz Equation) から概算することができる [100–104]。

$$P_{L.\text{iron}} = \frac{4S l}{T_{\text{sw}}} k_{\text{i}} \int_{0}^{T_{\text{sw}}} \left| \frac{dB}{dt} \right|^{\alpha} B_{\text{p-p}}^{\beta-\alpha} dt$$

(3.7)

$$k_{\rm i} = \frac{k}{(2\pi)^{\alpha-1} \int_0^{2\pi} |\cos(\theta)|^{\alpha} 2^{\beta-\alpha} d\theta}$$

(3.8)

ここで、k,  $\alpha$ ,  $\beta$  は正弦波励磁でのスタインメッツ係数、 $B_{p-p}$  は磁束密度の peak-to-peak 値、S はコアの有効断面積、l は平均磁路長である。磁束密度 B と誘導起電力  $v_L$  には次式の関係がある。

$$B = \frac{1}{NS} \int v_L dt \tag{3.9}$$

ここで、N はサーチコイルの巻数である。 $v_L$  が図 3.4 に示すような矩形波の場合、(3.7)

図 3.7: センダストインダクタのインピーダンス, 位相の周波数特性

式は(3.9)式から次式で表される。

$$P_{L\text{-iron}} = P_{L\text{-iron}}(\delta, V_L, f_{\text{sw}})$$

$$= 4S lk_i \frac{\delta}{\pi} \left| \frac{V_L}{NS} \right|^{\beta} \left( \frac{\delta}{2\pi f_{\text{sw}}} \right)^{\beta - \alpha}$$

(3.10)

ここで、 $\delta$  は $\nu_L$  のパルス幅に相当する位相シフト角、 $V_L$  は矩形波振幅の平均値、 $f_{\rm sw}$  はスイッチング周波数である。Magnetics 社の Sendust のデータシートからスタインメッツ係数は [Hz], [T], [m³] を基準に単位換算した k=1.25,  $\alpha=1.54$ ,  $\beta=1.99$ ,有効断面積は $S=358~{\rm mm}^2$ ,平均磁路長は  $l=243~{\rm mm}$  を使用した [20]。

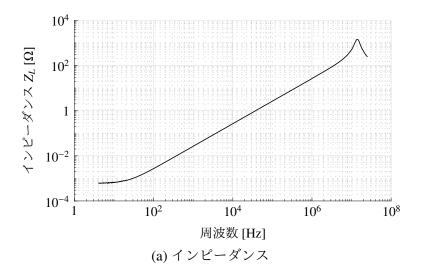

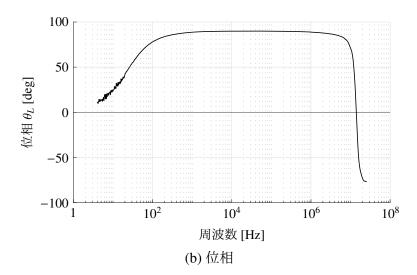

図 3.7 にインピーダンスアナライザで測定したセンダストインダクタのインピーダンス, 位相の周波数特性を示す。インピーダンスアナライザは  $4~\rm{Hz}\sim 1~\rm{MHz}$  では HIOKI IM3570 (測定周波数  $4~\rm{Hz}\sim 5~\rm{MHz}$ ), $1\sim 50~\rm{MHz}$  では HIOKI IM7581 (測定周波数  $100~\rm{Hz}$

3.3 損失分離 47

|                                                                                 | $P_{L,\mathrm{iron}}\left[\mathbf{W}\right]$ |                 |  |

|---------------------------------------------------------------------------------|----------------------------------------------|-----------------|--|

| 動作条件                                                                            | 拡張スタインメッツ                                    | インピーダンスアナライザ    |  |

|                                                                                 | (3.10) 式                                     | (3.11) 式        |  |

| $\boxtimes$ 3.4(a) $E_1 = E_2 = 750 \text{ V}$ , 100 kW, 16 kHz                 | 31                                           | 29 (-6% of 31)  |  |

| $\boxtimes$ 3.4(b) $E_1 = E_2 = 750 \text{ V}, 93.4 \text{ kW}, 24 \text{ kHz}$ | 46                                           | 37 (-20% of 46) |  |

表 3.4: 図 3.4 のインダクタ鉄損(1 個当たり)の推定値の比較

kHz ~ 300 MHz)を使用した。4つの外付けインダクタの合計の鉄損  $P_{L,iron}$  はスイッチング周波数  $f_{sw}$  の n 次の周波数成分のインダクタのインピーダンス  $Z_L(nf_{sw})$ ,位相  $\theta_L(nf_{sw})$  と,FFT 解析した誘導起電力の実効値  $V_{L,rms}(nf_{sw})$  から次式で概算することができる。

$$P_{L\text{-iron}} = 4 \sum_{n=1}^{\infty} \frac{V_{L\text{-rms}}(nf_{\text{sw}})^2}{Z_L(nf_{\text{sw}})} \cos(\theta_L(nf_{\text{sw}}))$$

(3.11)

周波数範囲はインダクタ鉄損の周波数成分を考慮して 1 MHz までとした。このインピーダンスアナライザ (HIOKI IM3570) を使用した, $E_1=E_2=750$  V, 100 kW, 16 kHz での外付けインダクタ 1 個当たりの鉄損は 29 W であった。しかし,このインピーダンスアナライザの位相誤差は 16 kHz で  $89.9^{\circ}\pm0.79^{\circ}$  である [105]。この位相誤差を考慮すると,推定値が 29 W の場合の真値は  $-88\sim148$  W の範囲に存在する。換言すると,推定値 29 W に対し  $-307\sim517\%$ の測定誤差を含むことを意味し,推定値として使用できない。以下では,参考のために,拡張スタインメッツ方程式による推定値とインピーダンスアナライザによる推定値を比較する。

表 3.4 は,拡張スタインメッツ方程式を使用した (3.10) 式からの推定値と,インピーダンスアナライザを使用して取得した実測データをベースに (3.11) 式から算出したインダクタ鉄損の推定値を比較したものである。図 3.4(a) の  $E_1=E_2=750$  V, 100 kW, 16 kHzでは,外付けインダクタ 1 個当たりの鉄損は拡張スタインメッツ方程式からの推定値は 31 W となり,インピーダンスアナライザによる実測値は 29 W で,31 W に対して -6%である。図 3.4(b) の  $E_1=E_2=750$  V, 93.4 kW, 24 kHz では,外付けインダクタ 1 個当たりの鉄損は拡張スタインメッツ方程式からの推定値は 46 W となり,インピーダンスアナライザによる推定値は 37 W で,46 W に対して -20%である。

表 3.4 の比較では、拡張スタインメッツ方程式を使用した推定値とインピーダンスアナライザを使用した実測値とに大きな乖離は存在しない。これは偶然の結果であって、インピーダンスアナライザの位相誤差を考慮すると、インピーダンスアナライザを本研究の鉄損測定に使用することはできない。これに対して拡張スタインメッツ方程式は、他の研究機関での採用例も多く [90,103,104]、工学的な信頼性も高い。このため本論文

では、インダクタ鉄損の推定に拡張スタインメッツ方程式を使用した。

### 3.3.5 Step 4: 抵抗損失とスイッチング損失の分離

図 3.4 ではスイッチング電流を等しく設定しているため,スイッチング損失の比はスイッチング周波数の比  $16~\mathrm{kHz}$ :  $24~\mathrm{kHz}=1$ :  $1.5~\mathrm{c}$ 近似できる。全損失から磁気デバイスの鉄損を差し引いた損失  $P_\mathrm{loss}-P_\mathrm{Liron}-P_\mathrm{tr.iron}$  が,インダクタ電流実効値  $I_\mathrm{rms}$  の  $2~\mathrm{乗}$ に比例する回路内の合計の抵抗損失  $P_\mathrm{ohm}$  とスイッチング損失  $P_\mathrm{sw}$  の和に等しいことから次式のが成立する。

$$\begin{bmatrix} P_{\text{loss}}^{16k} - P_{\text{L.iron}}^{16k} - P_{\text{tr.iron}}^{16k} \\ P_{\text{loss}}^{24k} - P_{\text{L.iron}}^{24k} - P_{\text{tr.iron}}^{24k} \end{bmatrix} = \begin{bmatrix} 1 & 1 \\ a & b \end{bmatrix} \begin{bmatrix} P_{\text{ohm}}^{16k} \\ P_{\text{sw}}^{16k} \end{bmatrix}$$

(3.12)

$$a = \left(\frac{I_{\rm rms}^{24k}}{I_{\rm rms}^{16k}}\right)^2 \tag{3.13}$$

$$b = \frac{24}{16} \tag{3.14}$$

ここで、上付き文字 "16k"、"24k" はスイッチング周波数 16 kHz と 24 kHz での各値を、a はインダクタ電流実効値の二乗の比、b はスイッチング周波数の比を表わす。 (3.12) 式から 16 kHz での抵抗損失  $P_{\rm ohm}^{16k}$  とスイッチング損失  $P_{\rm sw}^{16k}$  は次式で分離できる。

$$\begin{bmatrix} P_{\text{ohm}}^{16k} \\ P_{\text{sw}}^{16k} \end{bmatrix} = \frac{1}{b-a} \begin{bmatrix} bP_{\text{loss}}^{16k} - P_{\text{loss}}^{24k} - (bP_{L,\text{iron}}^{16k} - P_{L,\text{iron}}^{24k}) - (bP_{\text{tr.iron}}^{16k} - P_{\text{tr.iron}}^{24k}) \\ P_{\text{loss}}^{24k} - aP_{\text{loss}}^{16k} - (P_{L,\text{iron}}^{24k} - aP_{L,\text{iron}}^{16k}) - (P_{\text{tr.iron}}^{24k} - aP_{\text{tr.iron}}^{16k}) \end{bmatrix}$$

(3.15)

上式の  $P_{sw}$  はスイッチング周波数に比例する損失である。よって,MOSFET のターンオフ損失だけでなく,デッドタイム期間中に発生する SBD の導通損失や,スイッチング時のサージ電圧の振動に起因する損失が含まれる。本論文では,スイッチング周波数に比例する損失を広義のスイッチング損失と定義する。

[31] ではスイッチング損失がスイッチング電流の二乗に比例すると仮定していたが、 提案法ではスイッチング損失とスイッチング電流との関係が未知の場合でも損失分離が 可能な点に特長がある、

# **3.3.6** Step 5: 導通損失, 銅損, 未知損失の算出

MOSFET の導通損失  $P_{\text{cond}}$  はオン抵抗  $R_{\text{on}}$  とインダクタ電流実効値  $I_{\text{rms}}$  から次式で計算できる。

$$P_{\rm cond} = 4R_{\rm on}I_{\rm rms}^2 \tag{3.16}$$

3.3 損失分離 49

図 3.8:  $E_1 = E_2 = 750$  V, P = 100 kW,  $f_{sw} = 16$  kHz での損失分離結果

ここで、オン抵抗は室温での抵抗値  $R_{\rm on}=4.15~{

m m}\Omega$  を使用する [97]。

外付けインダクタの銅損  $P_{Lcopp}$  は巻線の直流抵抗  $R_{Lwind}$  とインダクタ電流実効値  $I_{rms}$  から次式で計算できる。

$$P_{L\text{-copp}} = 4R_{L\text{-wind}}I_{\text{rms}}^2 \tag{3.17}$$

ここで、外付けインダクタの巻線の直流抵抗値  $R_{L\text{-wind}}=0.57~\mathrm{m}\Omega$  を使用する。

変圧器の銅損  $P_{\rm tr}$  は巻線の直流抵抗  $R_{\rm tr\_wind}$  とインダクタ電流実効値  $I_{\rm rms}$  から次式で計算できる。

$$P_{\text{tr\_copp}} = R_{\text{tr\_wind}} I_{\text{rms}}^2$$

(3.18)

ここで、変圧器の巻線の直流抵抗値  $R_{\text{tr-wind}} = 4 \, \text{m}\Omega$  を使用する。

最後に、未知損失  $P_{\text{unkn}}$  は合計の抵抗損失から導通損失と銅損を差し引くことで、次式で推定できる。

$$P_{\text{unkn}} = P_{\text{ohm}} - P_{\text{cond}} - P_{L\text{-copp}} - P_{\text{tr-copp}}$$

(3.19)

図 3.9:  $E_1 = E_2 = 750$  V,  $f_{sw} = 16$  kHz での出力電力に対する全損失と損失分離結果

#### 3.3.7 結果と考察

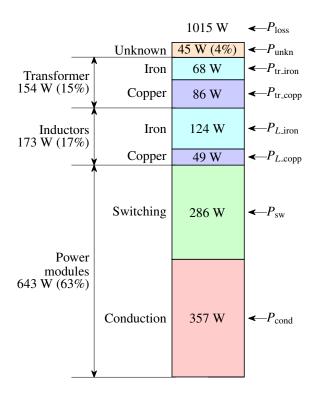

図 3.8 に 750 V, 100 kW, 16 kHz での損失分離結果を示す。未知損失は全損失に対して 4%であり、SiC モジュールや磁気デバイスの巻線の温度上昇による抵抗損失の増加分が 支配的であると考えられる。SiC モジュールの損失は全損失に対して 63%を占めており、 支配的である。外付けインダクタと変圧器の損失は全損失に対してそれぞれ 17%, 15% である。入出力電圧が等しい場合には Bridge 1, 2 のスイッチング電流がほぼ等しいこと から損失が等しいと仮定できる。この仮定から 1 つの Bridge 当たりの損失は 321 W となり、単相フルブリッジインバータとしての変換効率は 99.68%に到達すると推定できる。さらなる高効率化のためには SiC モジュールの性能向上が必要不可欠である。

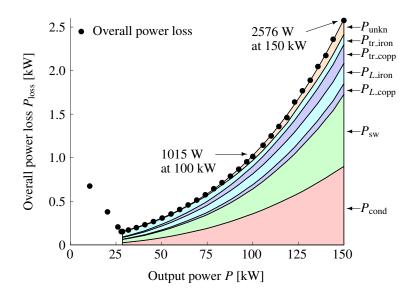

図 3.9 に  $E_1 = E_2 = 750$  V, 16 kHz での出力電力に対する全損失の測定値と損失分離結果を示す。 ZVS 動作可能な出力電力  $28.6 \sim 150$  kW の範囲で損失分離を行った結果,未知損失は全損失に対して最大でも 8%以下であり広範囲な出力電力領域で良好に分離できることを実証した。 SiC モジュールの損失の全損失に対する割合は出力電力に対して増加傾向にあり,150 kW では 67%を占め,100 kW での 63%と比べて 4%高い。このため,出力電力が大きいほど,SiC モジュールの損失低減の重要性がより高くなる。

### **3.4** スイッチング損失の測定誤差

#### 3.4.1 電流・電圧の瞬時値積による直接測定

スイッチング損失を実機のドレイン・ソース間電圧とドレイン電流の瞬時値積から測定する場合,電流検出遅れが測定誤差に大きく影響を与える。使用する SiC-MOSFET の場合,定格 100~kW のスイッチング電流 150~A で電流の立下り時間は約 50~ns となるため,検出遅れの短い CT で電流を測定する場合でも,同軸ケーブル 1~m 当たり約 5~ns の遅延が発生する。遅延時間の補正誤差が立下り時間に対して 10% (5~ns) の場合,スイッチング損失の測定誤差は (2.22) 式から 46%であるため,実用的であるとはいえない。

ZVS 時のスイッチング損失を測定する場合,MOSFET の構造上,ジャンクション電流を直接測定できないため,レグ上下の MOSFET の蓄積・放出エネルギーの差分から測定する必要がある。 (2.26) 式に図 3.1 のテストベンチの定格  $E_1=E_2=750$  V, 100 kW, 16 kHz での条件  $I_{\rm sw}=151$  A,  $t_{\rm f}=50$  ns,  $C_{\rm all}=13$  nF,  $C_{\rm ds}=4$  nF を代入することで, $E_{\rm off}/E_{\rm Q2}=0.08$  が得られる。一例として,MOSFET  $Q_1$  の蓄積エネルギー  $E_{\rm Q1.meas}$  の測定誤差が +5%,MOSFET  $Q_2$  の放出エネルギー  $E_{\rm Q2.meas}$  の測定誤差が -5%である場合,ターンオフ損失に相当するエネルギーの測定値  $E_{\rm off.meas}$  は次式で算出できる。

$$E_{\text{off\_meas}} = E_{\text{Q1\_meas}} - E_{\text{Q2\_meas}}$$

=  $1.05 \times 1.08 E_{\text{Q2}} - 0.95 E_{\text{Q2}}$

=  $0.184 E_{\text{Q2}}$

=  $2.3 E_{\text{off}}$  (3.20)

よって、スイッチング損失の測定誤差は +130%であり、より測定が困難である。

### 3.4.2 提案する全損失からの損失分離

図 3.8 の定格 100 kW でのスイッチング損失は (3.13) 式の 16 kHz と 24 kHz での電流 実効値の二乗比は a = 1 であるため,(3.15) 式から次式で近似できる。

$$P_{\text{sw}}^{16k} = 2[P_{\text{loss}}^{24k} - P_{\text{loss}}^{16k} - (P_{L,\text{iron}}^{24k} - P_{L,\text{iron}}^{16k}) - (P_{\text{tr,iron}}^{24k} - P_{\text{tr,iron}}^{16k})]$$

(3.21)

16 kHz と 24 kHz での全損失,インダクタ鉄損,変圧器鉄損の測定誤差の差分がスイッチング損失の測定誤差に影響する。全損失の測定誤差はパワーアナライザによって 0.2%,変圧器鉄損は電圧・電流の瞬時値積から 2%以下で高精度に測定可能である。一方,インダクタ鉄損は (3.10) 式の拡張スタインメッツ方程式から推定しているため,推定誤差

図 3.10:  $E_1 = E_2 = 750$  V,  $f_{sw} = 16$  kHz での出力電力に対する Bridge 1, 2 のスイッチング電流

は無視できないと考えられる。例えば最悪のケースとして, $P_{L,\text{iron}}^{16k}$  の測定誤差が +10%, $P_{L,\text{iron}}^{24k}$  の測定誤差が -10% の場合,スイッチング損失の測定誤差は +20%となる。

一般的な計測・測定システムを使用して、例えば 16 kHz と 24 kHz でのインダクタ鉄 損を測定した場合、その測定誤差は正または負の同極性となると考えられる。(3.21) 式 から明らかなように、同極性の測定誤差の一部は打ち消し合うため、鉄損推定誤差がス イッチング損失の誤差に及ぼす影響を大幅に軽減できる。これは本論文で提案する損失 分離法の優れた特長である。その結果、温度による損失測定での測定誤差 10 ~ 20% [28] と同程度の測定精度であるため、実用的な損失分離手法であると結論できる。

# **3.5** スイッチング損失の分離

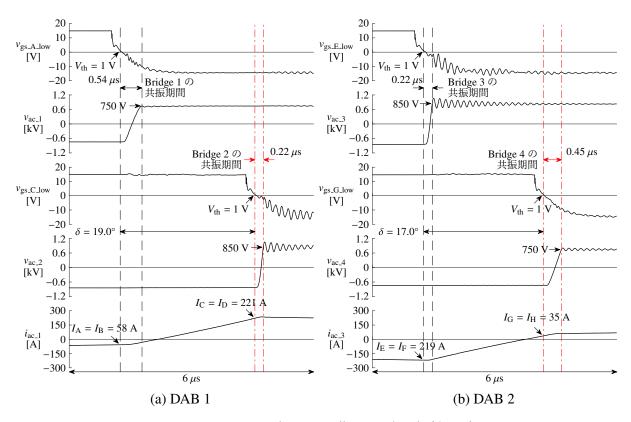

# 3.5.1 Bridge 1, 2 のスイッチング電流の比較

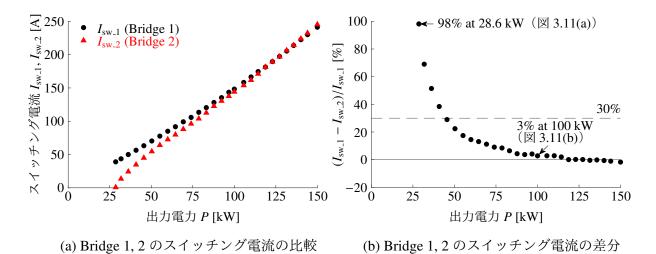

図 3.10(a) に  $E_1 = E_2 = 750$  V, 16 kHz での出力電力に対する Bridge 1, 2 のスイッチング電流を示す。図 3.10(b) は次式で算出した Bridge 1 のスイッチング電流に対する両者の差分の割合である。

$$\alpha = \frac{I_{\text{sw}\_1} - I_{\text{sw}\_2}}{I_{\text{sw}\_1}} \tag{3.22}$$

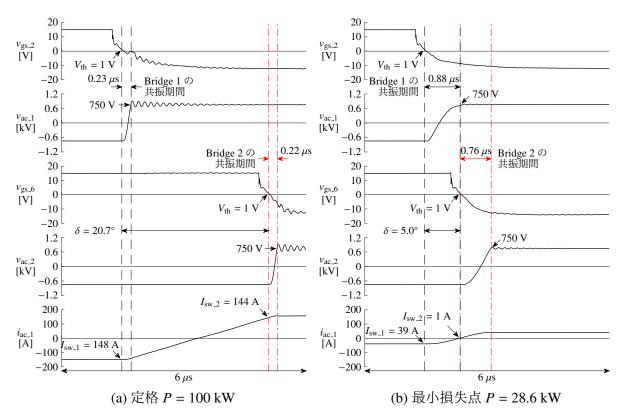

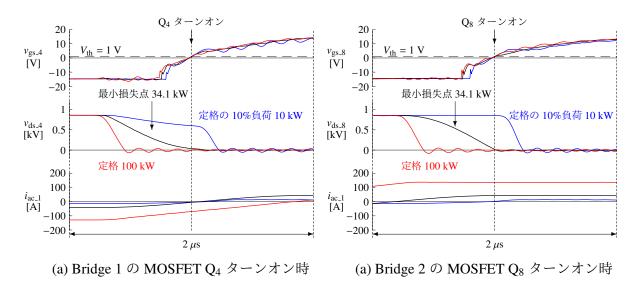

ここで、 $I_{\text{sw-1}}$  は Bridge 1 のスイッチング電流、 $I_{\text{sw-2}}$  は Bridge 2 のスイッチング電流である。出力電力が低下するほど、両者の差分は増加する。図 3.11(a) に図 3.1 で測定した定格  $E_1=E_2=750$  V, 100 kW. 16 kHz での位相シフト期間の時間軸拡大波形を、図 3.11(b)

図 3.11: 図 3.1 の  $E_1 = E_2 = 750$  V,  $f_{sw} = 16$  kHz での位相シフト期間の時間軸拡大波形