# T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

# 論文 / 著書情報 Article / Book Information

| 題目(和文)            | 高信頼性・大容量SRAMの微細化に向けた先端プロセス技術                                                                                                                                                                   |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | Advanced Process Technologies for High-Reliability and High-Capacity SRAM Scaling                                                                                                              |

| 著者(和文)            | 石丸一成                                                                                                                                                                                           |

| Author(English)   | Kazunari Ishimaru                                                                                                                                                                              |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第12273号,<br>授与年月日:2022年6月30日,<br>学位の種別:課程博士,<br>審査員:若林 整,筒井 一生,宮本 恭幸,菅原 聡,角嶋 邦之                                                                          |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第12273号,<br>Conferred date:2022/6/30,<br>Degree Type:Course doctor,<br>Examiner:,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                           |

| Type(English)     | Doctoral Thesis                                                                                                                                                                                |

# Advanced Process Technologies for High-Reliability and High-Capacity SRAM Scaling

$\mathbf{b}\mathbf{y}$

## Kazunari Ishimaru

Submitted to the

Electrical and Electronic Engineering Graduate Major, Department of Electrical and Electronic Engineering, School of Engineering, Tokyo Institute of Technology on May 27th, 2022 in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering

Author: \_\_\_\_\_

Electrical and Electronic Engineering Graduate Major, Department of Electrical and Electronic Engineering

Certified by:

Hitoshi Wakabayashi Professor of Electrical and Electronic Engineering Thesis Supervisor

Certified by:

Kazuo Tsutsui Professor of Electrical and Electronic Engineering Thesis Supervisor Certified by:

Yasuyuki Miyamoto Professor of Electrical and Electronic Engineering Thesis Supervisor

Certified by: \_\_\_\_\_

Satoshi Sugahara Associate Professor of Electrical and Electronic Engineering Thesis Supervisor

Certified by: \_\_\_\_\_

Kuniyuki Kakushima Associate Professor of Electrical and Electronic Engineering Thesis Supervisor

# Advanced Process Technologies for High-Reliability and High-Capacity SRAM Scaling

by

## Kazunari Ishimaru

Submitted to the

Electrical and Electronic Engineering Graduate Major, Department of Electrical and Electronic Engineering, School of Engineering, Tokyo Institute of Technology on May 27th, 2022 in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering

#### Abstract

This year marks 75 years since the birth of the transistor in 1947. During this time, semiconductor technology has progressed dramatically, continuing to miniaturize, increasing integration and improving performance with Moore's Law. The market for semiconductor devices has expanded from the original large computers for industrial use to include small office computers, personal computers, and mobiles in the pockets while changing the shapes. The metaverse has been attracting attention as a new market in recent years. While applications have shifted from industry to businesses, homes, and individuals in the past, the metaverse is once again targeting society.

In conjunction with this trend, the amount of information generated annually is also exploding. While there are continuous attempts to increase computational power to process this large amount of data, the increase in power consumption is a significant obstacle. In recent years, with calls for green and carbon neutrality, there has been a strong desire to reduce power consumption and improve energy efficiency in computing as well.

Memory is an essential component in computing and is responsible for storing information. Current computing systems use the von Neumann architecture, and frequent data transfer between CPUs and memories consumes a lot of energy and degrades performance, known as the "memory wall" problem. Much research on parallel computing by using GPUs and the development of accelerators for efficient computing. If information processing can be performed inside the memory, the load on the CPU can be significantly reduced, and power-efficient computing systems can be realized. There is a strong requirement for a non von Neumann computing architecture to overcome power issues. A deep neural network (DNN) has been paid much attention to image recognition and classifications. Computing in memory (CiM) architecture with the DNN can significantly improve energy efficiency, and there is much research on this topic, including accelerator development. In order to accommodate exploding data, the CiM systems with high-capacity memory are strongly desired.

A NAND flash memory is widely used as a low-cost and high-capacity memory element for storage. Suppose it becomes possible to provide energy-efficient computer systems using a 3D NAND flash memory, which is more than two orders of magnitude larger capacity than the DRAM and cheaper than the DRAM. In order to realize this 3D NAND CiM, the high-capacity SRAM needs to be combined to improve performance and efficiency. This thesis aims to provide technology to embed high-capacity SRAM into 3D NAND without losing the low-cost and high-capacity advantages. From the manufacturing process point of view, package-level integration is the easiest approach. However, its size and cost are the concern. Thus, from a manufacturing cost view points, both 3D NAND and high-capacity SRAM on the same wafer are preferable. However, the manufacturing process and thermal budget between 3D NAND and high-capacity SRAM are different. Therefore, key process modules are extracted from front-end-of-line, middle-of-line, and back-end-of-line modules and studied for modification and/or optimization. The first base process technology node of 90 nm, which is similar to the current peripheral circuits of 3D NAND, was selected. Then, a scalable SRAM cell layout was studied. Mechanical stress affects SRAM cell reliability, and optimum cell layout with MOSFET structure was proposed. This SRAM cell design guideline was validated by the hardware and showed good scalability at least down

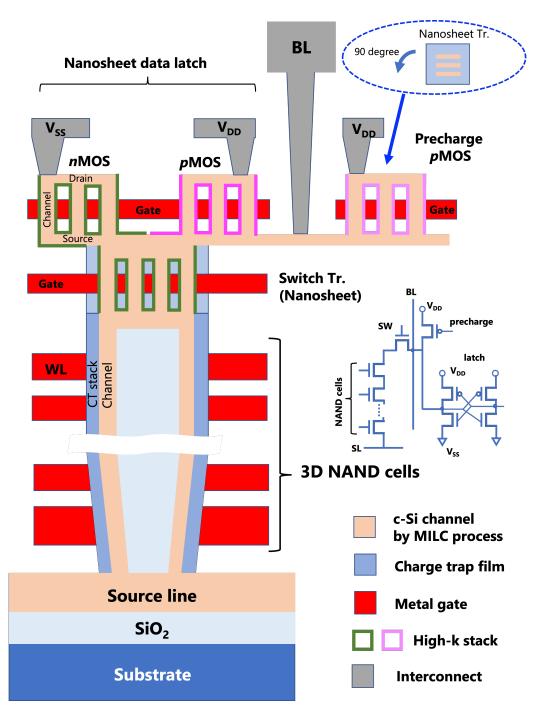

to 45 nm node. A gate insulator needed to be optimized to satisfy the standby leakage current specifications of SRAM, and a high- $\kappa$ /metal gate (HK/MG) should be introduced. To accommodate the process temperature of 3D NAND, a gate-first HK/MG was the only option, and the Hf base gate insulator with poly-Si gate electrode was evaluated. Both optimum Hf and nitrogen concentrations were proposed down to a 32 nm node. A local interconnect (L.I.) technology is beneficial for reducing the SRAM cell size and relaxing bit-line pitches for speed improvement since the conventional copper interconnect cannot be used because of the thermal budget. The impact on device characteristics was studied, and an optimum shallow trench isolation height with MOSFET sidewall structure was proposed. A low- $\kappa$ inter layer dielectric film was evaluated for future scaling, and material requirements were studied with barrier metal selection. A redundancy fuse process by copper blowing scheme was evaluated, and issues were identified. A high-capacity SRAM can be embedded into 3D NAND with down to 45 nm CMOS technology. Beyond 32 nm node SRAM integration with 3D NAND, a gate-last HK/MG should be introduced from both leakage current and CMOS scaling points of view. A die-to-die bonding between 3D NAND and CMOS peripheral circuits with high-capacity SRAM will be a possible solution. Preliminary results of die warpage impact on the device were presented. An SRAM keep-out area (KOA) is needed to be introduced with further studies. Using above-mentioned design guidelines, one package solid-state drive can be realized as a stepping stone for future one package servers. As a next step, one package server with cryogenic temperature operation will enable further energy reduction and combination with quantum computing systems. Manufacturing cost reduction of future LSIs is one of the issues to satisfy the carbon-neutral requirements. The 3D NAND introduced a breakthrough in the manufacturing process, which realized an efficient manufacturing process with low cost for storage memory. Surprisingly, future CMOS device structure, such as nanosheet CMOS, resembles that of 3D NAND cells. This means that the 3D NAND base manufacturing process can be applied to future CMOS devices, bringing lower cost and higher capacity simultaneously. Thus, the CiM systems realized by 3D NAND with high-capacity SRAM are indispensable for a future sustainable society.

Thesis Supervisor: Hitoshi Wakabayashi Title: Professor of Department of Electrical and Electronic Engineering

Thesis Supervisor: Kazuo Tsutsui Title: Professor of Department of Electrical and Electronic Engineering

Thesis Supervisor: Yasuyuki Miyamoto Title: Professor of Department of Electrical and Electronic Engineering

Thesis Supervisor: Satoshi Sugahara Title: Associate Professor of Department of Electrical and Electronic Engineering

Thesis Supervisor: Kuniyuki Kakushima Title: Associate Professor of Department of Electrical and Electronic Engineering

#### Acknowledgements

The support and encouragement of many individuals contributed to the successful completion of this work. I would like to express sincere gratitude to Professor Hitoshi Wakabayashi for providing technical guidance. I was very fortunate to have had the opportunity to learn from him. I would like to thank Professor Kazuo Tsutsui, Professor Yasuyuki Miyamoto, Associate Professor Satoshi Sugahara and Associate Professor Kuniyuki Kakushima for reading this thesis.

I would like to express deep gratitude to Dr. Nobuo Hayasaka, CEO & President of KIOXIA Corporation, Mr. Masaki Momodomi, CTO of KIOXIA Corporation and Mr. Susumu Yoshikawa, Director of the Institute of Memory Technology Research & Development, KIOXIA Corporation for their managements, helpful advices, and encouragements of this study.

I would like to thank Dr. Yasuo Naruke, former President & CEO of KIOXIA Holding, who helped and encouraged my work since I joined Toshiba Corporation. I also would like to thank my former managers of Toshiba Corporation, Mr. Kenji Maeguchi, Dr. Masakazu Kakumu, Mr. Masaaki Kinugawa, Dr. Fumitomo Matsuoka, Mr. Hidemi Ishiuchi, Mr. Yoshiaki Toyoshima for continuous encouragement and support.

I would like to express my sincere gratitude to Professor Chenming Hu, Professor Tue-Jae King Liu, Dr. John F. Chen, Dr. James Chen, for their guidance during my research period at the University of California, Berkeley, as a visiting industrial fellow.

I also would like to thank to Mr. Kunihiro Kasai, Mr. Yasuhiro Fukaura, Yasunori Okayama, Ms. Yukari Unno, Mr. Toshiyuki Kondo, Mr. Ms. Mariko Takayanagi, Dr. Satoshi Inaba, Mr. Kazuya Ohuchi, Mr. Nobuaki Yasutake, Mr. Makoto Fujiwara, Mr. Akira Hokazono, Ms. Kanna Adachi, Dr. Takeshi Watanabe, Mr. Hirohisa Kawasaki, Dr. Naoyuki Shigyo, Dr. Nobutoshi Aoki, Dr. Hiroyoshi Tanimoto, Mr. Toshiyuki Enda, Dr. Yoshitaka Tsunashima, Dr. Kazuhiro Eguchi, Hideshi Miyajima, Dr. Atsushi Yagishita, Dr. Akio Kaneko, Dr. Dr. Hideki Shibata, Mr. Noriaki Matsunaga, Dr. Takamasa Usui, Mr. Naofumi Nakamura of Toshiba Corporation (some are now with KIOXIA

Corporation) for their significant discussions and practical advices.

The author has been strongly supported by my wife, Yoko, and daughters, Ai and Moe and would like to thank them gratefully.

May 27th, 2022

Kazunari Ishimaru

# Contents

| 1        | Intr          | coduction                                                                            | 1  |

|----------|---------------|--------------------------------------------------------------------------------------|----|

|          | 1.1           | Data explosion and energy crisis                                                     | 1  |

|          | 1.2           | Advantage of embedding high-capacity SRAM into 3D NAND                               | 6  |

|          | 1.3           | Process comparison between SRAM and 3D NAND $\ldots$                                 | 12 |

|          |               | 1.3.1 Embedded SRAM process                                                          | 14 |

|          |               | 1.3.2 Stand-alone SRAM process                                                       | 15 |

|          |               | 1.3.3 3D NAND process $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 16 |

|          |               | 1.3.4 Key process modules                                                            | 17 |

|          | 1.4           | Thesis focus and organization                                                        | 19 |

| -        | Ŧ             |                                                                                      |    |

| <b>2</b> | v             | out and transistor structure design for high-reliability                             |    |

|          | $\mathbf{SR}$ |                                                                                      | 21 |

|          | 2.1           | Background                                                                           | 21 |

|          | 2.2           | Selection of SRAM cell layout                                                        | 24 |

|          |               | 2.2.1 Cell layout comparison                                                         | 24 |

|          |               | 2.2.2 Validation by the hardware                                                     | 29 |

|          | 2.3           | Process flow and simulation setup                                                    | 31 |

|          | 2.4           | Simulation results                                                                   | 36 |

|          |               | 2.4.1 Mechanical stress and defect generation model                                  | 36 |

|          |               | 2.4.2 Cell layout design for 90 nm node $\ldots$ $\ldots$ $\ldots$ $\ldots$          | 40 |

|          |               | 2.4.3 Universality of presented guideline                                            | 49 |

|          |               | 2.4.4 DRC implementation                                                             | 52 |

|          | 2.5           | Summary of this chapter                                                              | 54 |

| 3        | Rel           | iability of SRAM cell transistors                                                    | 55 |

|          | 3.1           |                                                                                      | 55 |

|          |               |                                                                                      |    |

|          | 3.2               | Past study on $n$ MOSFETs                                   | 56  |

|----------|-------------------|-------------------------------------------------------------|-----|

|          | 3.3               | Reliability in narrow channel width $p$ MOSFETs             | 60  |

|          |                   | 3.3.1 Characteristics of narrow channel width $p$ MOSFETs . | 60  |

|          |                   | 3.3.2 Hot-carrier stress results                            | 61  |

|          |                   | 3.3.3 Fowler-Nordheim stress results                        | 68  |

|          |                   | 3.3.4 Mechanical stress by STI                              | 69  |

|          | 3.4               | Summary of this chapter                                     | 71  |

| 4        | FE                | OL and MOL process issues and optimization                  | 72  |

|          | 4.1               | Background                                                  | 72  |

|          | 4.2               | Estimation of SRAM capacity and corresponding CMOS          |     |

|          |                   | technology node                                             | 74  |

|          | 4.3               | Optimization of gate stack process                          | 80  |

|          | 4.4               | Implementation of local interconnect                        | 85  |

|          |                   | 4.4.1 Advantage of local interconnect                       | 85  |

|          |                   | 4.4.2 Process optimization                                  | 87  |

|          | 4.5               | Summary of this chapter                                     | 91  |

| <b>5</b> | BE                | OL process issue and optimization                           | 92  |

|          | 5.1               | Background                                                  | 92  |

|          | 5.2               | Copper fuse experiments                                     | 94  |

|          |                   | 5.2.1 Barrier metal evaluation                              | 94  |

|          |                   | 5.2.2 Fuse blow experiments                                 | 94  |

|          |                   | 5.2.3 Study on low- $\kappa$ dielectrics                    | 98  |

|          | 5.3               | Summary of this chapter                                     | 100 |

| 6        | Rer               | naining issues for embedding high-reliable high-capacity    |     |

|          | $\mathbf{SR}$     | AM 1                                                        | .01 |

|          | 6.1               | Background                                                  | 101 |

|          | 6.2               | Technologies and issues for 3D integration                  | 104 |

|          | 6.3               | Summary of this chapter                                     | 112 |

| -        |                   |                                                             |     |

| <b>7</b> | Cor               | nclusions 1                                                 | 13  |

| 7        | <b>Cor</b><br>7.1 | Inclusions     1       Thesis summary     1                 |     |

# List of Figures

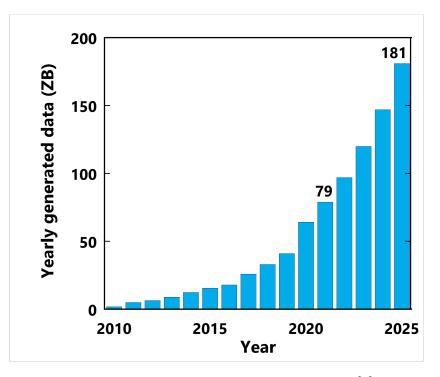

| 1.1  | Trend of yearly data generation [1]                                   | 2  |

|------|-----------------------------------------------------------------------|----|

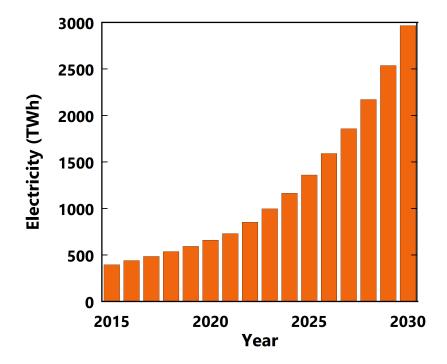

| 1.2  | Trend of world-wide datacenter electricity usage [7]                  | 2  |

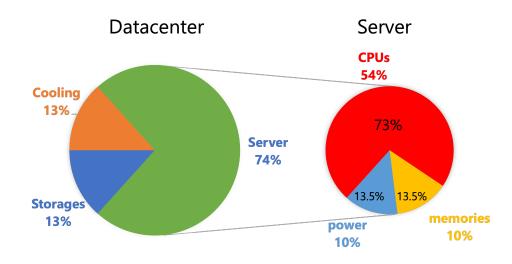

| 1.3  | Breakdown of electricity usage for both datacenter and server [8].    | 3  |

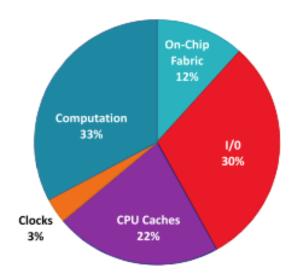

| 1.4  | CPU power breakdown [8]                                               | 4  |

| 1.5  | Trade-off between DRAM capacity and refresh latency (left             |    |

|      | axis) and percentage of performance loss (right axis) [13]            | 5  |

| 1.6  | High-capacity SRAM stacked on the processor [16]. $\ldots$ .          | 5  |

| 1.7  | Trade-off between memory size flexibility and energy efficiency       |    |

|      | of computing. In-memory computing is suitable for energy              |    |

|      | efficient computing [40]. $\bigcirc$ 2019 IEEE                        | 6  |

| 1.8  | 3D NAND fabricated by CNA (CMOS Next to cell Array)                   |    |

|      | process                                                               | 7  |

| 1.9  | $3\mathrm{D}$ NAND fabricated by CUA (CMOS Under cell Array) process. | 8  |

| 1.10 | 3D NAND fabricated by wafer bonding process                           | 8  |

| 1.11 | Photo of enterprise SSD drive [38] $\bigcirc$ KIOXIA and image of     |    |

|      | components inside SSD                                                 | 9  |

| 1.12 | Image of two approaches to realize one package SSD. One is            |    |

|      | stacking 3D NAND, high-capacity SRAM and controller (a).              |    |

|      | The other is stacking SRAM embedded NAND and controller               |    |

|      | (b)                                                                   | 10 |

| 1.13 | Image of one package SSD drive [38] $\bigcirc$ KIOXIA                 | 11 |

| 1.14 | Interface speed trend of both DRAM and NAND                           | 13 |

| 1.15 | Process flow and schematic image for embedded SRAM. $\ . \ .$ .       | 14 |

| 1.16 | Process flow and schematic image for stand-alone SRAM                 | 15 |

| 1.17 | Process flow and schematic image for 3D NAND                          | 17 |

#### LIST OF FIGURES

|            | Schematic image of each process module                                                                                              | 18<br>20 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2.1<br>2.2 | SRAM cell layouts study by M. Ishida <i>et al.</i> [54].ⓒ 1998 IEEE The first demonstration of SRAM cell used the Type-4 layout     | 22       |

| 2.3        | in Figure 2.1 by K. Osada <i>et al.</i> [55]. © 2001 IEEE<br>Example of Type-1a SRAM cell layout used for 90 nm node                | 23       |

|            | logic product [59]. The cell size is $1 \ \mu \text{m}^2$ . C 2002 IEEE                                                             | 24       |

| 2.4        | SRAM cell layouts with dimensions used for the scalability                                                                          |          |

| 05         | study. (a) Conventional cell layout used until 90 nm node and<br>(b) low height (thin) cell that consists of all straight patterns. | 26       |

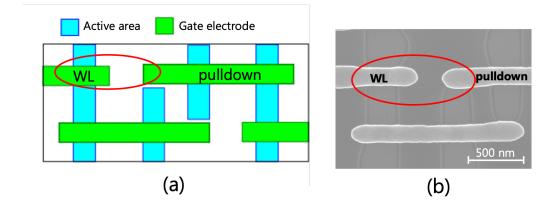

| 2.5        | (a) Schematic layout of conventional cell, and (b) SEM photograph of the WL and pulldown gate resist pattern. (c)                   |          |

|            | Resist pattern connection occurs due to the narrow distance                                                                         |          |

| 0.6        | between pulldown GEs and WL.                                                                                                        | 27       |

| 2.6        | (a) Schematic image of cell layout, and (b) corresponding<br>SEM photograph of the WL and pulldown gate patterns after              |          |

|            | gate patterning process in a thin cell. Good gate length                                                                            |          |

|            | uniformities without pattern connection were observed                                                                               | 28       |

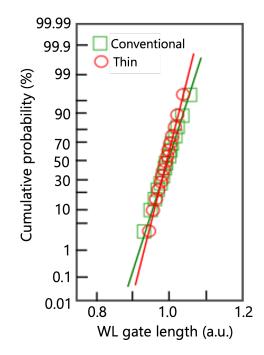

| 2.7        | Simulated cumulative probability of WL gate length for both                                                                         |          |

|            | conventional and thin types SRAM cells.                                                                                             | 28       |

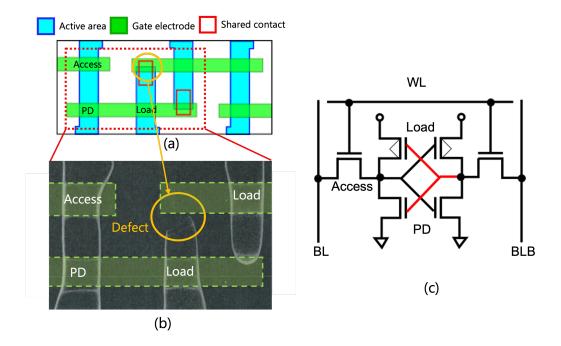

| 2.8        | (a) SRAM cell layout and (b) corresponding SEM photograph                                                                           |          |

|            | after Wright etching where single-bit failure were observed.                                                                        |          |

|            | The active area edge of $p$ MOSFET load transistor was missing                                                                      |          |

|            | where shared contact connected both GE and AA, indicated                                                                            |          |

|            | as red lines in SRAM cell circuit shown in (c). $\ldots$ . $\ldots$ .                                                               | 30       |

| 2.9        | Process flow of fabricated SRAM. The process steps, a through                                                                       |          |

|            | g, are candidates that may generate crystal defects                                                                                 | 31       |

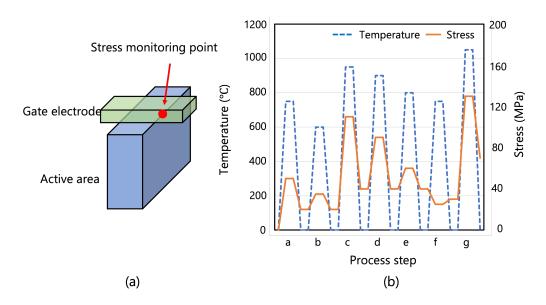

| 2.10       | (a) Monitoring location of mechanical stress and (b) simulated                                                                      |          |

|            | stress values at each process steps, a - g, in Figure 2.9 with                                                                      |          |

|            | the temperature profile                                                                                                             | 32       |

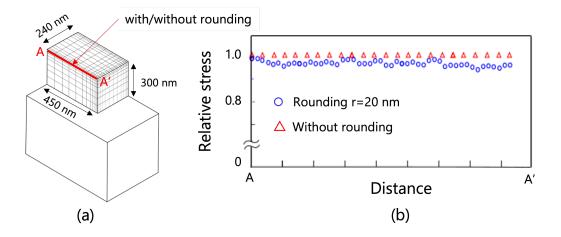

| 2.11 | (a) Structure used for the simulation. Only AA portion                                                 |    |

|------|--------------------------------------------------------------------------------------------------------|----|

|      | was shown. (b) Simulated results of von Mises stress with                                              |    |

|      | and without top corner rounding. The stress values were                                                |    |

|      | normalized by the stress without top corner roundings                                                  | 33 |

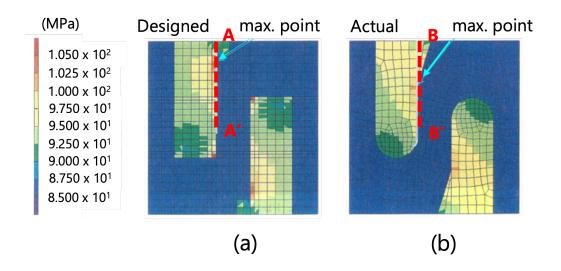

| 2.12 | Contour plots of simulated von Mises stress of (a) designed                                            |    |

|      | layout and (b) actual device shape                                                                     | 34 |

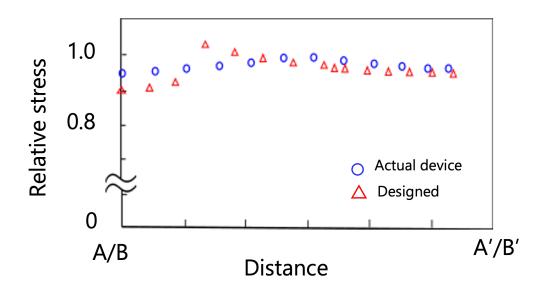

| 2.13 | Relative stress values along the active area, indicated as dotted                                      |    |

|      | lines A–A' and B–B' in the Figure 2.12. $\ldots$ $\ldots$ $\ldots$                                     | 35 |

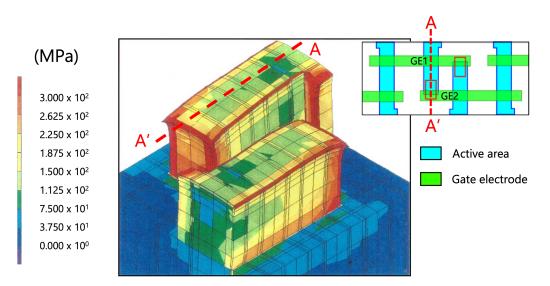

| 2.14 | Simulated results of maximum resolved shear stress during the                                          |    |

|      | source/drain activation annealing process with displacement                                            |    |

|      | values. The displacement values are multiplied 200 $\times$ for easy                                   |    |

|      | observation                                                                                            | 36 |

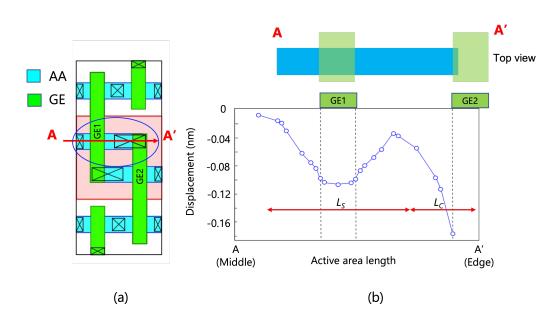

| 2.15 | (a) Schematic layout of SRAM cell and (b) displacement of                                              |    |

|      | the AA surface along the dotted line A–A' in Figure 2.14. $$ .                                         | 37 |

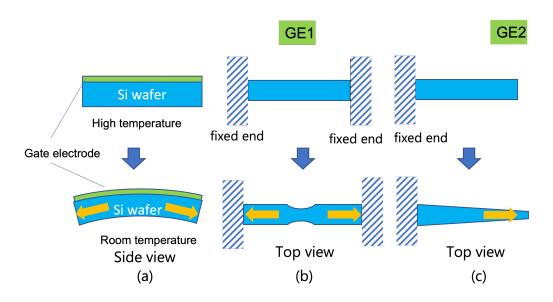

| 2.16 | Schematic images of displacement difference between GE1 and                                            |    |

|      | GE2. (a) Wafer warpage after the gate electrode material                                               |    |

|      | deposition. (b) AA under GE1 is pulled by the fixed ends on                                            |    |

|      | both sides as it returns to room temperature. (c) AA under                                             |    |

|      | GE2 is pulled toward the open end when returning to room                                               |    |

|      | temperature. $\ldots$ | 38 |

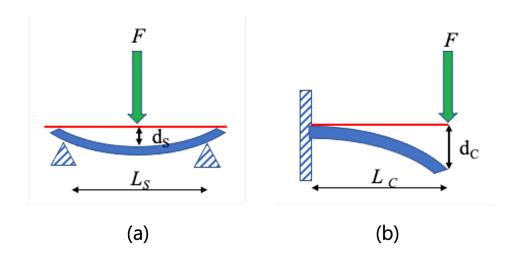

| 2.17 | Models for explaining the mechanical stress and deflection                                             |    |

|      | under GE1 and GE2 shown in Figure 2.15. (a) A simply                                                   |    |

|      | supported beam structure for under GE1 and (b) cantilever                                              |    |

|      | beam structure for under GE2                                                                           | 39 |

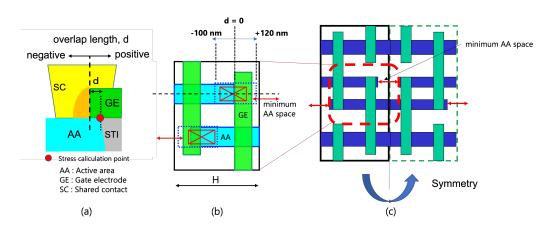

| 2.18 | (a) Schematic cross-section image of AA–GE overlap. The                                                |    |

|      | stress monitoring point is indicated at red circle. (b) Top                                            |    |

|      | view of the SRAM cell. The overlap length d is varied from                                             |    |

|      | -100 nm to $+120$ nm. (c) Schematic image of SRAM cell                                                 |    |

|      | arrangement.                                                                                           | 41 |

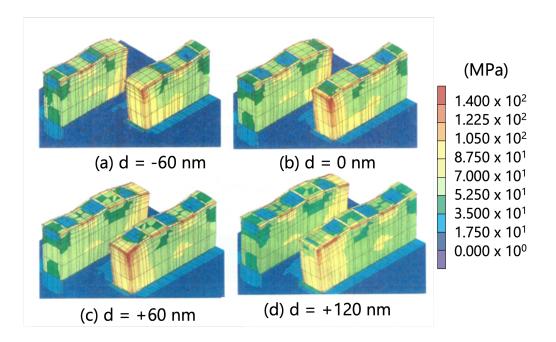

| 2.19 | Simulated mechanical stress for each AA–GE overlap amount $% \mathcal{A}$                              |    |

|      | with AA deflection, where (a) $d = -60 \text{ nm}$ , (b) $d = 0 \text{ nm}$ ,                          |    |

|      | (c) d = + 60 nm and (d) d = + 120 nm, respectively                                                     | 42 |

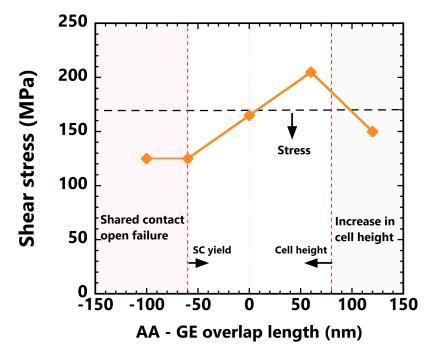

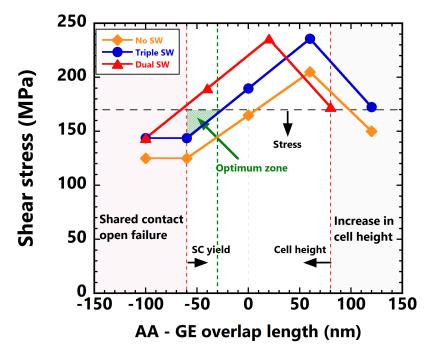

| 2.20 | Simulated shear stresses and their $AA - GE$ overlap length                |    |

|------|----------------------------------------------------------------------------|----|

|      | dependence shown in Figures 2.19 (a) - (d). The stress criteria            |    |

|      | of 170 MPa is indicated as a red dotted line                               | 43 |

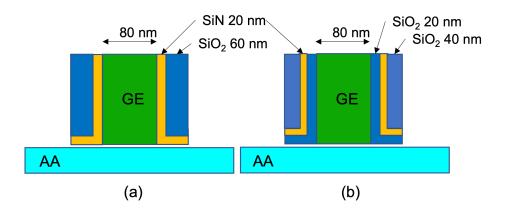

| 2.21 | Sidewall configurations used for simulations: (a) dual-layer               |    |

|      | sidewall and (b) triple-layer sidewall structures.                         | 44 |

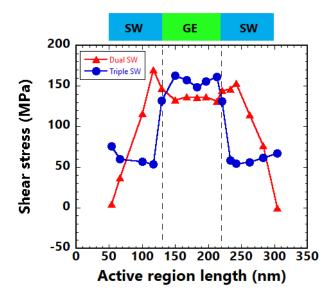

| 2.22 | Simulated shear stress under GE along the active area for both             |    |

|      | sidewall structures. Dual-layer sidewall shows the maximum                 |    |

|      | stress under the sidewall region while triple-layer sidewall               |    |

|      | shows the maximum stress uner GE region                                    | 44 |

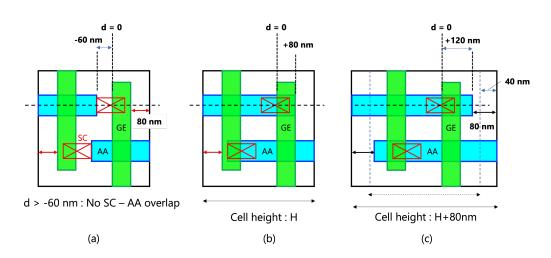

| 2.23 | Schematic images of cell size impact by AA–GE overlap                      |    |

|      | length. The overlap length $d = -60 \text{ nm}$ (a), $d = +80 \text{ nm}$  |    |

|      | (b) and $d = +120 \text{ nm}$ (c) are shown with cell height impact.       | 45 |

| 2.24 | AA-GE overlap length dependence of simulated shear stresses                |    |

|      | under the GE with sidewall structure dependence. The                       |    |

|      | optimum overlap length regions $(-60 \text{ nm to} - 30 \text{ nm})$ are   |    |

|      | indicated as green triangle                                                | 46 |

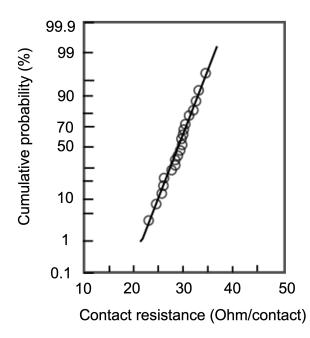

| 2.25 | Cumulative probability of the shared contact resistance                    |    |

|      | extracted from 6.5 k chain                                                 | 47 |

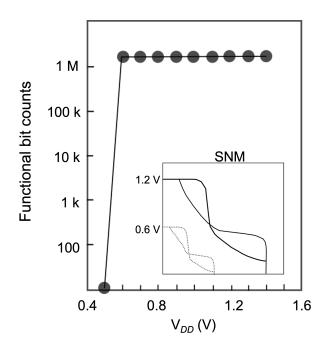

| 2.26 | Functional bit counts of fabricated 1 Mb SRAM test vehicle                 |    |

|      | with SNM of both $V_{DD} = 0.6$ and 1.2 V                                  | 48 |

| 2.27 | A 45 nm node embedded SRAM cell layout used for mass                       |    |

|      | production [86]. © 2006 IEEE                                               | 48 |

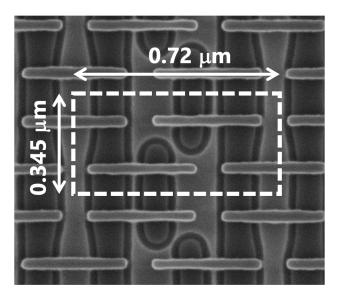

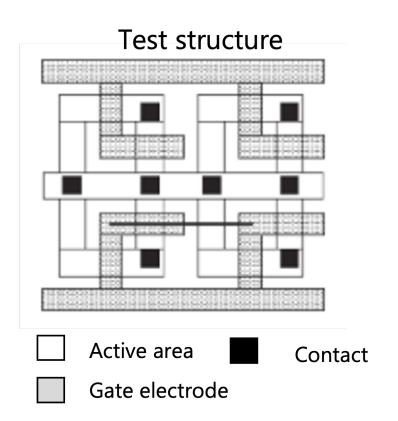

| 2.28 | Layout of the structures electrically tested for defect-formation          |    |

|      | monitoring $[65]$ . $\bigcirc$ 2007 IEEE $\ldots$                          | 49 |

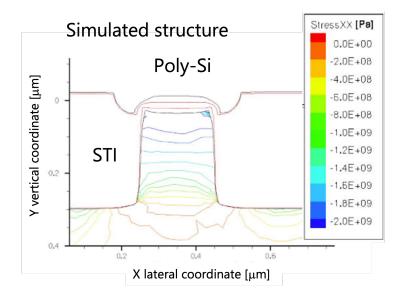

| 2.29 | Cross-sectional the simulates structure and level curves of the            |    |

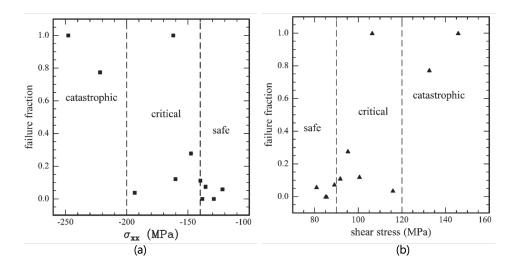

|      | $\sigma_{xx}$ [65]. © 2007 IEEE                                            | 50 |

| 2.30 | Calculated fraction of the failed structure for both (a) $\sigma_{xx}$ and |    |

|      | (b) shear stress $[65]$ . $\bigcirc$ 2007 IEEE                             | 50 |

| 2.31 | SRAM cell size definition by key design rules.                             | 51 |

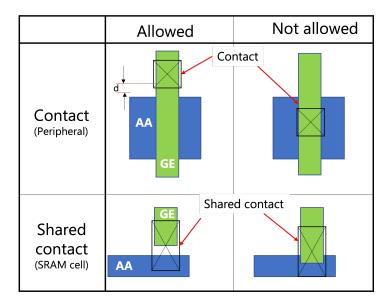

|      | Layouts that are allowed and not allowed by conventional DRC.              | 53 |

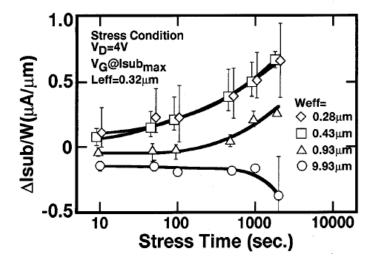

| 3.1  | Stress time dependence on the substrate current change,                                                                                                             |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | delta $I_{sub}$ , for various channel widths. $W_{eff}$ is the effective                                                                                            |    |

|      | channel width corrected from the electrical characteris-                                                                                                            |    |

|      | tics [101]. © 1996 IEEE                                                                                                                                             | 56 |

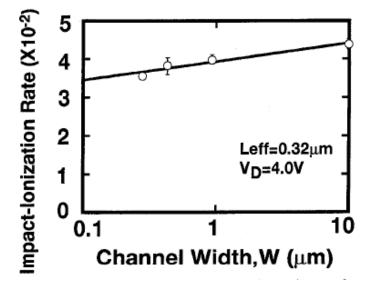

| 3.2  | Channel width dependence of the impact ionization rate for                                                                                                          |    |

|      | measured $n$ MOSFETs [101]. © 1996 IEEE                                                                                                                             | 57 |

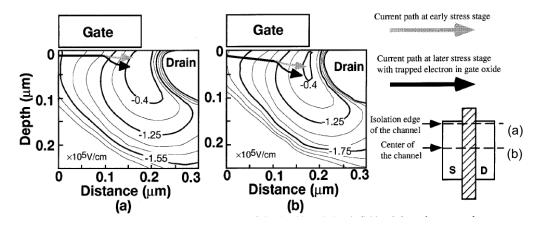

| 3.3  | Simulated electric field with drain current path. (a) The                                                                                                           |    |

|      | channel near the STI edge and (b) center of the channel                                                                                                             |    |

|      | $[101]. \textcircled{O} 1996 \text{ IEEE } \ldots $ | 58 |

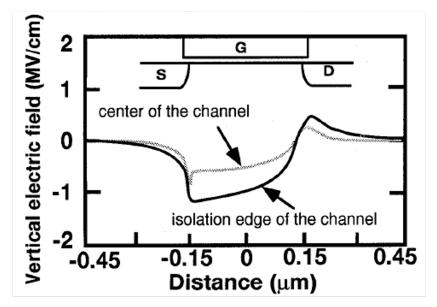

| 3.4  | Simulated vertical electric field along the channel for both                                                                                                        |    |

|      | isolation edge of the channel and center of the channel                                                                                                             |    |

|      | $[101]. \textcircled{O} 1996 \text{ IEEE } \ldots $ | 59 |

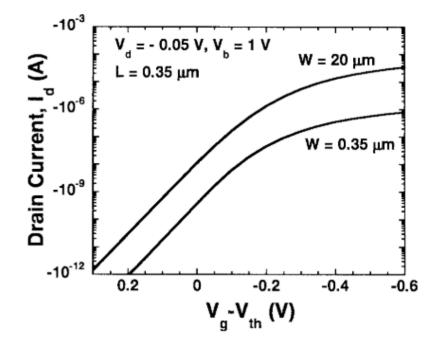

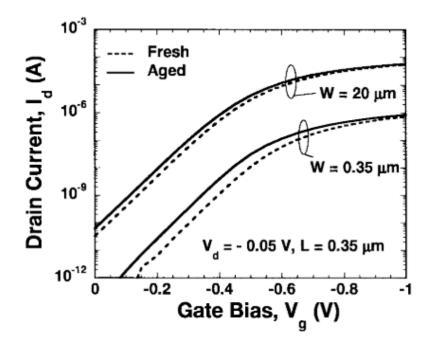

| 3.5  | Initial $I_d$ - $V_g$ characteristics of pMOSFETs whose channel                                                                                                     |    |

|      | width W = 0.35 $\mu$ m and 20 $\mu$ m. Since STI process is                                                                                                         |    |

|      | optimized, no hump characteristics was observed. $\hdots$                                                                                                           | 61 |

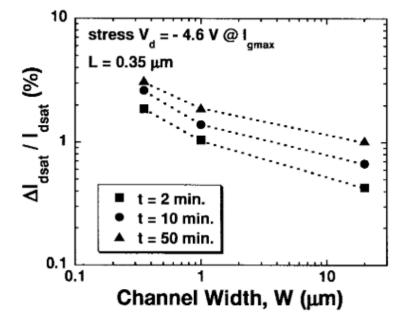

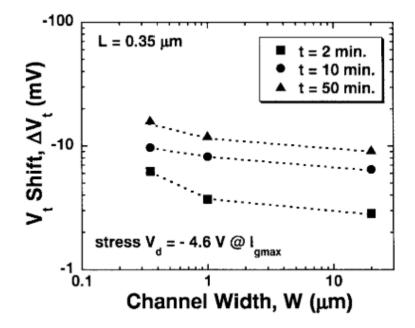

| 3.6  | Channel width dependence of drain current change,                                                                                                                   |    |

|      | $\Delta I_{dsat}/I_{dsat}$ , monitored at stress time t = 2, 10 and 50 minutes.                                                                                     | 62 |

| 3.7  | $\mathbf{I}_d$ - $\mathbf{V}_g$ characteristics of both W = 0.35 and 20 $\mu \mathrm{m} \ p \mathrm{MOSFETs}$                                                       |    |

|      | after the hot-carrier stress (solid lines). Initial characteristics                                                                                                 |    |

|      | also shown as dotted lines                                                                                                                                          | 62 |

| 3.8  | Channel width dependence of the threshold voltage degrada-                                                                                                          |    |

|      | tion $(\Delta V_{th})$ as a parameter of hot-carrier stress time. Narrow                                                                                            |    |

|      | width devices show larger degradation as same as $\Delta I_{dsat}/I_{dsat}$ .                                                                                       | 63 |

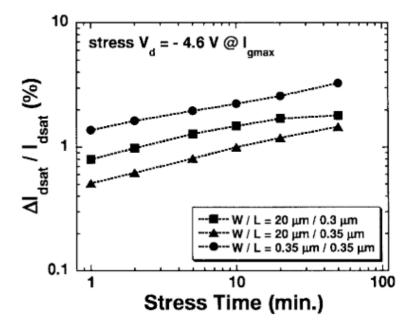

| 3.9  | Stress time dependence of drain current degradation,                                                                                                                |    |

|      | $\Delta I_{dsat}/I_{dsat}$ , for MOSFETs with various W/L dimensions                                                                                                | 64 |

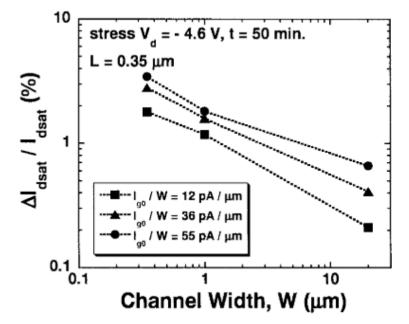

| 3.10 | Channel width dependence of $\Delta I_{dsat}/I_{dsat}$ as a parameter of                                                                                            |    |

|      | initial gate current normalized for W, $I_{g0}/W$ . Narrow width                                                                                                    |    |

|      | devices show larger degradation for each stress condition                                                                                                           | 65 |

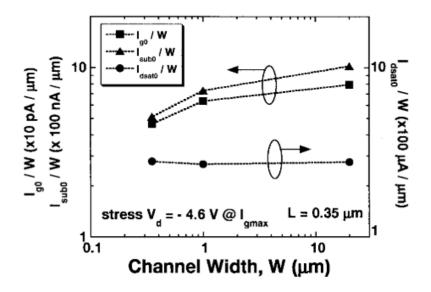

| 3.11 | Channel width dependence of the normalized gate $(I_{g0})$ ,                                                                                                        |    |

|      | substrate $(I_{sub0})$ , and drain $(I_{dsat0})$ current                                                                                                            | 65 |

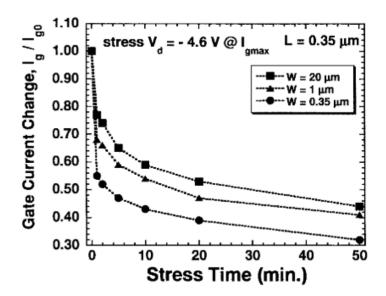

| 3.12 | Stress time dependence of the gate current change for various                                                                                                       |    |

|      | channel width devices.                                                                                                                                              | 67 |

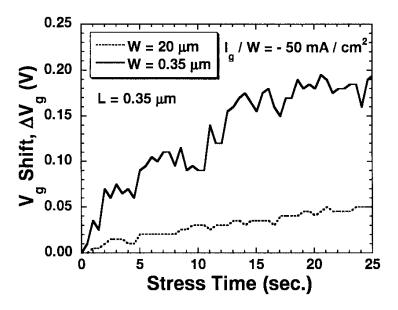

| 3.13 | Fowler-Nordheim stress results for both wide and narrow<br>width devices. The narrow device shows larger electron |    |

|------|-------------------------------------------------------------------------------------------------------------------|----|

|      | trapping efficiency, explained by the large $V_g$                                                                 | 68 |

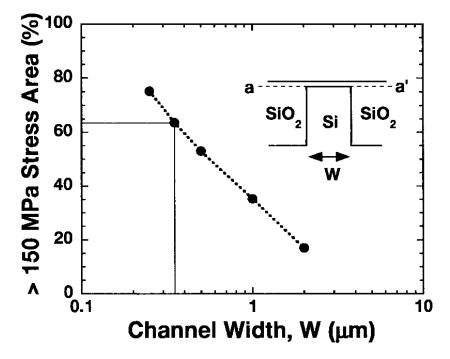

| 3.14 | Simulated channel width dependence of shear stress at $SiO_2/Si$                                                  |    |

|      | interface (shown as dotted line a - a' in the figure). Narrow                                                     |    |

|      | channel width MOSFETs, such as below W = 0.5 $\mu$ m, show                                                        |    |

|      | more than $50\%$ of channel area is occupied shear stress larger                                                  |    |

|      | than 150 MPa by STI filling material                                                                              | 70 |

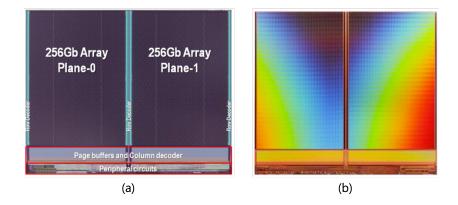

| 4.1  | Die photos of 512 Gb 3D NAND presented at ISSCC 2017                                                              |    |

|      | (a) [127] and (b) [128]. $\bigcirc$ 2017 IEEE                                                                     | 74 |

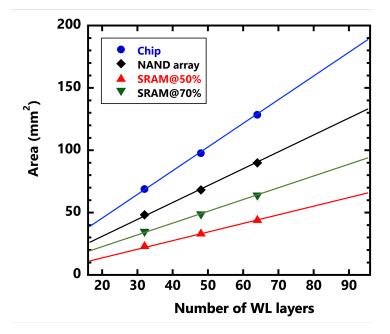

| 4.2  | 3D NAND memory layer dependence of chip size, NAND array                                                          |    |

|      | area, and SRAM cell areas                                                                                         | 75 |

| 4.3  | 3D NAND memory layer dependence of chip size, NAND array                                                          |    |

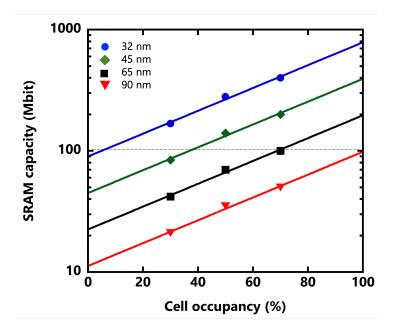

|      | area, and SRAM cell areas                                                                                         | 76 |

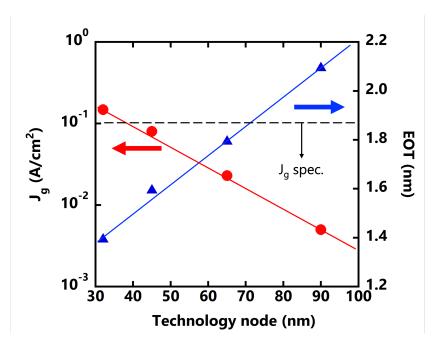

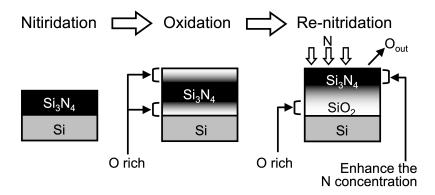

| 4.4  | Target EOT and $J_g$ for each technology node                                                                     | 77 |

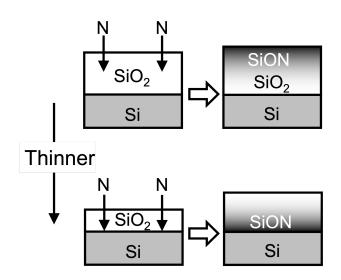

| 4.5  | Issue of thickness scaling in plasma nitrided SiON                                                                | 78 |

| 4.6  | Schematic images of novel SiON process and nitrogen profile                                                       | 78 |

| 4.7  | EOT dependence of $J_g$ for plasma SiON, novel SiON, and                                                          |    |

|      | HfSiON.                                                                                                           | 79 |

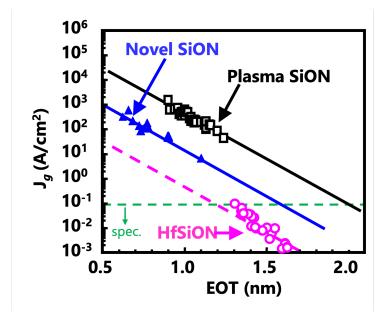

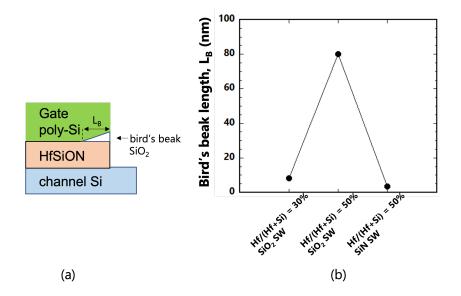

| 4.8  | (a) Schematic image of undesired oxidation at the gate                                                            |    |

|      | edge and (b) bird's beak length $(L_B)$ dependence on Hf                                                          |    |

|      | concentration with sidewall (SW) materials.                                                                       | 80 |

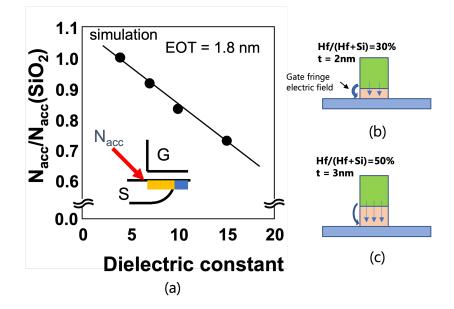

| 4.9  | (a) Simulated Hf concentration dependence of accumulated                                                          |    |

|      | charge at the gate edge region. Under the same $EOT = 1.8 \text{ nm}$                                             |    |

|      | condition, $Hf/(Hf+Si) = 30\%$ shows more gate fringe electric                                                    |    |

|      | field (b) compare to $Hf/(Hf+Si) = 50\%$ (c) because of the                                                       |    |

|      | difference of physical thickness.                                                                                 | 81 |

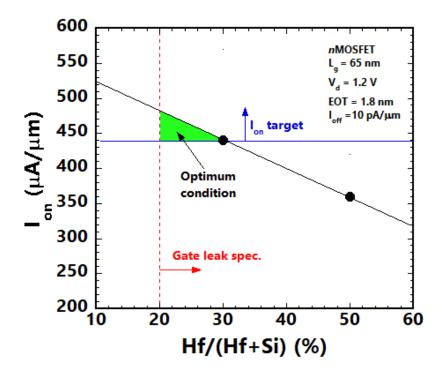

| 4.10 | Hf/(Hf+Si) dependence on <i>n</i> MOSFET I <sub>on</sub>                                                          | 82 |

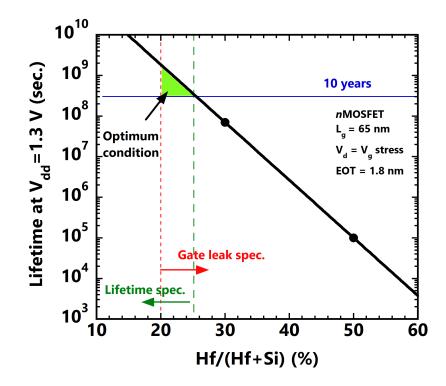

| 4.11 | Hf concentration dependence on hot carrier lifetime of                                                            |    |

|      | $\mathbf{L} = 65 \text{ nm } n \text{MOSFET}.$                                                                    | 83 |

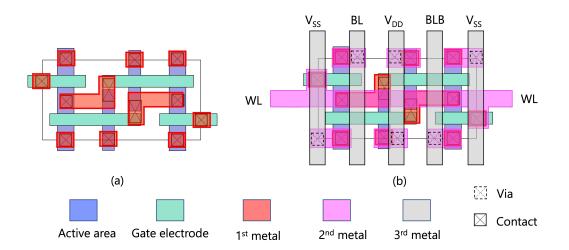

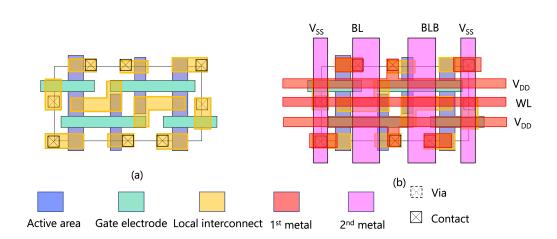

| 4.12 | Cell layout of embedded SRAM and interconnect layer                                                               |    |

|      | configuration. (a) Only AA, GE and L.I. layers are shown.                                                         |    |

|      | (b) All layers are shown                                                                                          | 85 |

|      |                                                                                                                   |    |

| 4.13 | Cell layout of stand-alone SRAM and interconnect layer<br>configuration. (a) Only AA, GE and L.I. layers are shown.<br>(b) All layers are shown.                                                           | 86  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

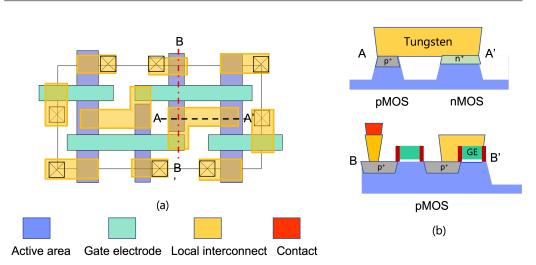

| 4.14 | Schematic image of L.I. chain test structure. (a) Top view of cell. (b) Cross-sectional images of both directions along $A-A'$ and $B-B'$ shown in (a).                                                    | 87  |

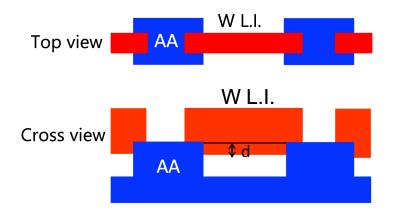

| 4.15 | Schematic image of L.I. chain test structure of both top and                                                                                                                                               |     |

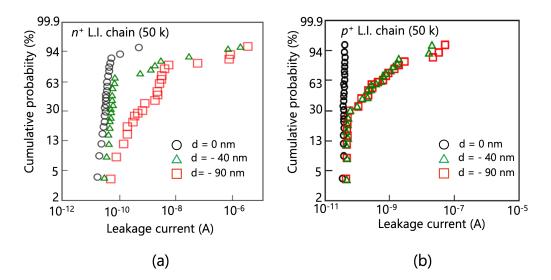

| 4.16 | cross views                                                                                                                                                                                                | 87  |

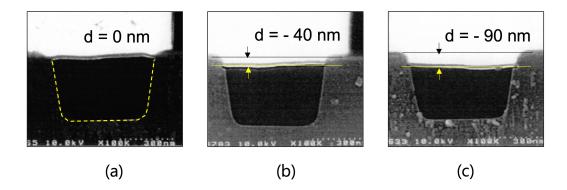

| 4.17 | $p^+$ contacts as a parameter of STI height                                                                                                                                                                | 88  |

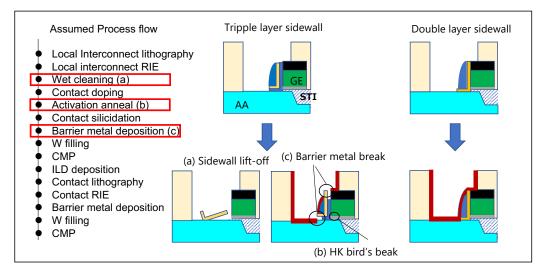

| 4.18 | STI height, d, (a) 0 nm, (b) $-40$ nm, and (c) $-90$ nm<br>Assumed process flow and critical process (a) - (c) that may                                                                                    | 88  |

| -    | affect MOSFET characteristics                                                                                                                                                                              | 90  |

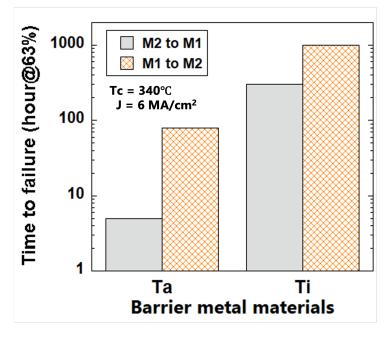

| 5.1  | Barrier metal material dependence of electromigration. Ti shows better characteristics compare to the Ta                                                                                                   | 95  |

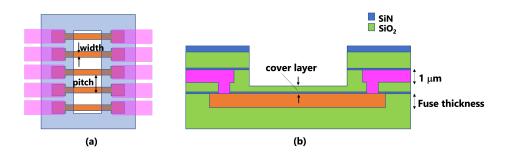

| 5.2  | Schematic images of test structure of fuse blow evaluation, (a) top view and (b) side view.                                                                                                                | 96  |

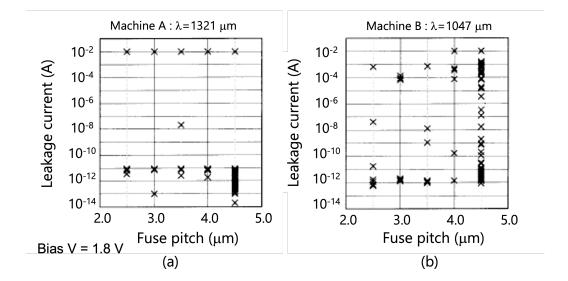

| 5.3  | Pitch dependence of fuse blow yield. Wave lengths of the laser                                                                                                                                             |     |

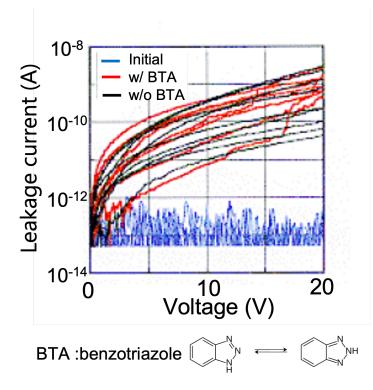

| 5.4  | are (a) $\lambda = 1321 \ \mu m$ and (b) $\lambda = 1047 \ \mu m$ , respectively<br>Leakage current characteristics of blown fuse with and<br>without BTA treatment. Initial (before blow process) leakage | 96  |

| 5.5  | characteristics is also shown                                                                                                                                                                              | 97  |

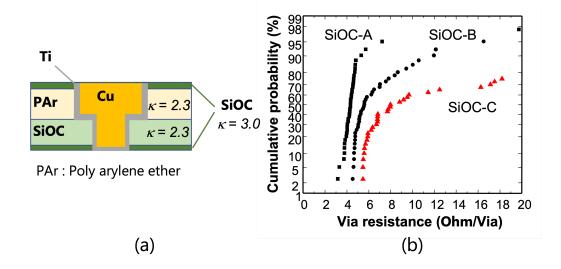

|      | Samples more than 100 Ohm/via were removed in this figure.                                                                                                                                                 | 99  |

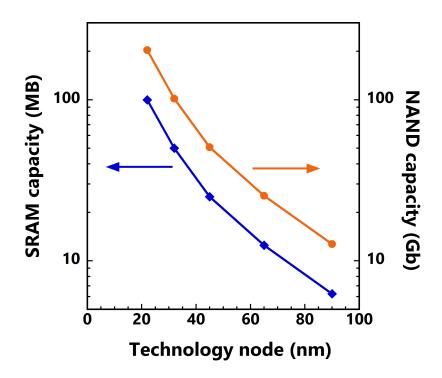

| 6.1  | Available maximum SRAM capacity and corresponding 3D<br>NAND capacity for each technology node based on the<br>assumption used in Chapter 4                                                                | 102 |

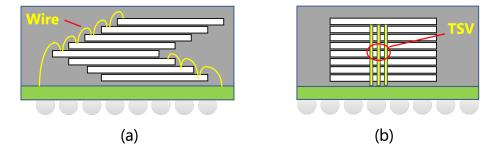

| 6.2  | Schematic images of (a) conventional wire bonding and (b)<br>TSV. TSV enables smaller package size.                                                                                                        |     |

#### LIST OF FIGURES

| 6.3  | Concept of future one package storage by heterogeneous integration with high-capacity SRAM embedded 3D NAND 105                                                                                                                                                                                                           |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.4  | Example of chip module/substrate/package warpage from                                                                                                                                                                                                                                                                     |

| 6.5  | reflow to room temperature. [150].© 2019 IEEE 106<br>Example of wafer warpage after backside                                                                                                                                                                                                                              |

| 6.6  | grinding [151].© 2013 IEEE                                                                                                                                                                                                                                                                                                |

|      | device [152]. $\textcircled{O}$ 2016 IEEE $\ldots$                                                                                                                                                                                                                                                                        |

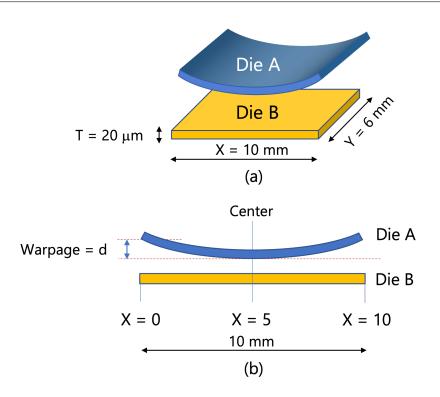

| 6.7  | Schematic images of simulated structure. (a) Bird's eye view of<br>both dies A and B with dimension. (b) Cross-sectional image<br>of the die shape used in the simulation. The warp amount d<br>is defined as shown in the figure. It is assumed the die A has<br>a symmetrical warp structure in the X direction         |

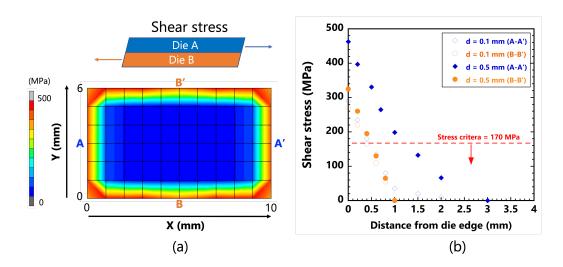

| 6.8  | Simulation results of shear stress in die A beside die B. (a)<br>Contour plot of shear stress in the case of die A warp amount<br>d is 0.1 mm. (b) Shear stress in die A from the die edge for<br>both X direction (along A-A') and Y direction (along B-B').<br>The die warpage amount $d = 0.1$ and 0.5 mm are plotted. |

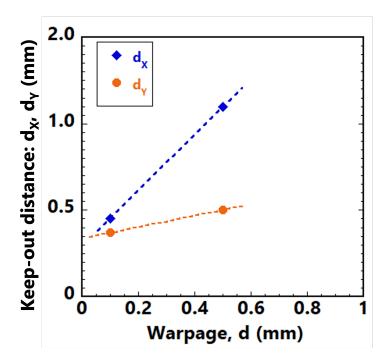

| 6.9  | Stress criteria, 170 MPa, is shown as a red dotted line 109 Keep-out distance, $d_X$ and $d_Y$ obtained from the simulation results shown in Figure 6.8. $d_X$ shows strong dependence on                                                                                                                                 |

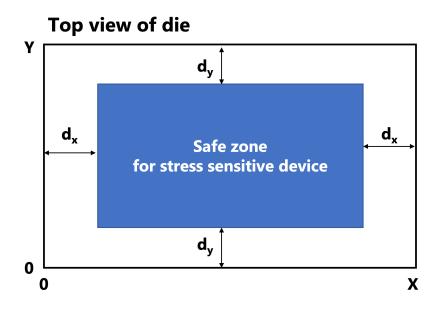

| 6.10 | the amount of warpage                                                                                                                                                                                                                                                                                                     |

| 7.1  | Schematic image of liquid cooling system that is commercially                                                                                                                                                                                                                                                             |

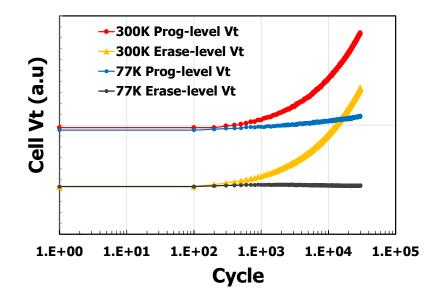

| 7.2  | available for server system [3,4]                                                                                                                                                                                                                                                                                         |

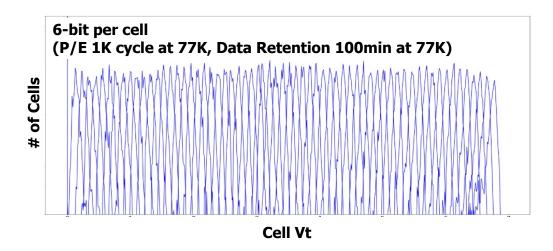

| 7.3  | istics compare to 300 K operation [161].<br>© 2021 IEEE 117 3D NAND shows HLC capability under 77 K opera-                                                                                                                                                                                                                |

|      | tion [161]. $\bigcirc$ 2021 IEEE $\ldots$                                                                                                                                                                                                                                                                                 |

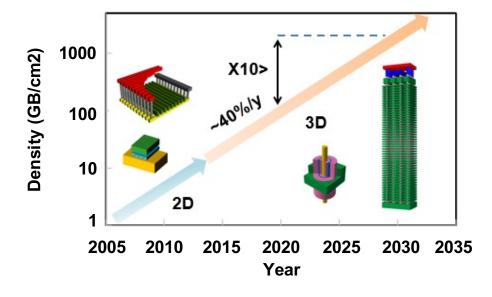

| 7.4 | NAND flash memory density increases roughly $40\%$ /year by   |

|-----|---------------------------------------------------------------|

|     | shifting 2D to 3D structure                                   |

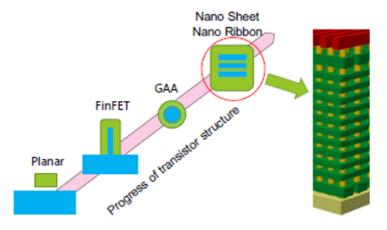

| 7.5 | Progress of transistor structure. The best practice to reduce |

|     | manufacturing costs of 3D NAND can be applied for future      |

|     | transistor manufacturing process                              |

| 7.6 | Future structure of the 3D NAND embedded with high-           |

|     | capacity SRAM by nanosheet transistors                        |

# List of Tables

| 1.1 | Price per giga-bit of both DRAM and NAND [42]                 | 12 |

|-----|---------------------------------------------------------------|----|

| 1.2 | Process modules and differences among three devices           | 18 |

| 2.1 | Advantages and disadvantages of both conventional and thin    |    |

|     | cells.                                                        | 25 |

| 2.2 | Design rules used for 90 nm node SRAM cell                    | 27 |

| 2.3 | Material parameters used for the simulation                   | 31 |

| 2.4 | Design rules of key layers with target cell size and AA-GE    |    |

|     | overlap length from 90 nm to 32 nm technology node            | 52 |

| 4.1 | Target EOT and recommended gate insulator for each            |    |

|     | technology node.                                              | 79 |

| 4.2 | Proposed Hf and nitrogen concentration for 45 and 32 nm node. | 84 |

| 5.1 | Example of BEOL structure roadmap for 130, 90, 65 and         |    |

|     | 45 nm node technologies [142].<br>© 2004 IEEE                 | 93 |

# Chapter 1

# Introduction

#### 1.1 Data explosion and energy crisis

In today's advanced information society, information is exploding, and the annual amount of data generated last year reached 79 ZB (zettabyte) [1]. The amount of data generated will continue to increase and is expected to reach 181 ZB by 2025, as shown in Figure 1.1. In 2019, the annual amount of data generated in 2025 was estimated to be 175 ZB, which means an increase of 6 ZB over the past two years. If this trend continues, the amount of data generated in the future will far exceed the current estimation. This data includes text data generated by people, such as e-mails and chats, photos and videos taken using smartphones and data generated by industrial equipment, and new data generated by devices than by people, and this percentage is expected to increase in the future [2].

As the amount of data generated increases, the need to improve the computing performance to process the enormous amount of data increases. As proof of this, datacenters are being built worldwide [3]. As the number of datacenters increases, so does the amount of power they consume. The energy consumed by datacenters worldwide was 190 TWh (terawatt-hour) in 2017, which was about half of the previously predicted amount as shown in Figure 1.2 [4–6].

Figure 1.1: Trend of yearly data generation [1].

Figure 1.2: Trend of world-wide datacenter electricity usage [7].

#### CHAPTER 1. INTRODUCTION

It is expected to increase significantly to 3,000 TWh by 2030 due to the explosive growth of generated data [7]. Although current consumption is less than predicted, this amount of electricity dramatically exceeds the total amount of electricity generated in Japan. From preventing global warming point of view, it is essential to use renewable energy and reduce electricity consumption. Servers consume about 74% of the total power consumption in datacenters, and about 73% of the power consumption in servers is consumed by the CPU (Central Processing Unit) [8], as shown in Figure 1.3. Since these CPUs consume a large amount of power and generate heat, large-scale cooling systems are equipped in datacenters, accounting for nearly 13% of the total power consumption of datacenters.

Figure 1.3: Breakdown of electricity usage for both datacenter and server [8].

A breakdown of the power consumed by the CPU is shown in Figure 1.4. Only 33% of the power is used for computation itself, while two-thirds is spent on accessing the cache SRAM (Static Random Access Memory) and main memory, DRAM (Dynamic Random Access Memory), which means "moving data for computation." In particular, machine learning, which has recently been the focus of much research, handles enormous amounts of data, and the frequent transfer of data from main memory has become a bottleneck in

Figure 1.4: CPU power breakdown [8].

computing capability and power consumption, known as a "memory wall" [9–11].

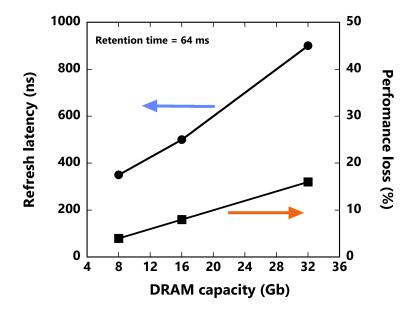

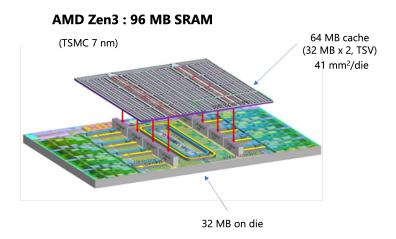

In recent years, to improve this problem, stacked DRAM modules using TSV (Through Silicon Via) technology, so-called HBM (High Bandwidth Memory) [12], are directly attached to the processor. However, since DRAMs have a data retention time of less than one second, they require frequent refresh operations to overwrite the data, and as the capacity of DRAMs increases, the delay caused by these refresh operations becomes non-negligible, as shown in Figure 1.5 [13]. There have been attempts to increase the size of the SRAM on the CPU in order to reduce the data movement [14]. In this example, as shown in Figure 1.6, eight processor cores share a total of 96 MB of SRAM by using 7 nm node technology [15, 16], and it has been reported that this stacked SRAM is suitable for energy-efficient However, the TPD (Thermal Design Power) of this accelerators [17]. processor is still quite large at 105 W. Parallel processing is being done with more processor cores using GPU (Graphics Processing Unit), but it does not replace the traditional von-Neumann architecture, and dramatic power reductions are difficult to achieve.

Figure 1.5: Trade-off between DRAM capacity and refresh latency (left axis) and percentage of performance loss (right axis) [13].

Figure 1.6: High-capacity SRAM stacked on the processor [16].

## 1.2 Advantage of embedding high-capacity SRAM into 3D NAND

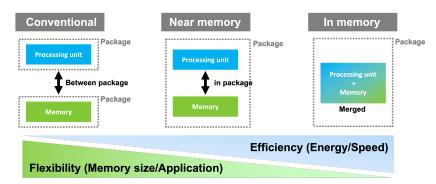

In recent years, new computational methods utilizing artificial intelligence (AI) that use non von Neumann architecture are attracting much attention. This approach is being considered to efficiently process data at the edge side, rather than doing it on the conventional servers in the cloud, as shown in Figure 1.7. An architecture of computing in memory (CiM) or in-memory computing has also been attracting attention that can handle huge data efficiently. Since SRAMs have no endurance limit, studies are

Figure 1.7: Trade-off between memory size flexibility and energy efficiency of computing. In-memory computing is suitable for energy efficient computing [40]. © 2019 IEEE

being conducted using not only conventional 6T (six transistors) SRAMs but also 8T (eight transistors) and 9T (nine transistors) SRAMs in terms of energy efficiency [18–20].

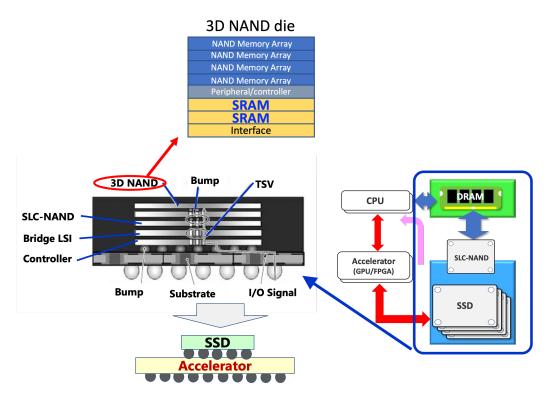

On the other hand, various CiMs using non-volatile memory that can store large amounts of data are also being considered [21, 22]. There are also many studies on utilizing NAND flash memory for in-memory computing [23–30]. NAND flash memory is already a proven product and has the potential to realize high-capacity, low-cost CiM. One of the studies showed that a combination of 6.5 Gb (gigabit) of SLC-NAND (single-bit per cell NAND) and 3.2 MB (megabyte) of SRAM with 16 core system is effective [26]. Their study assumes that a CMOS (Complementary Metal Oxide Semiconductor) chip and 3D NAND (three-dimensional cell NAND flash memory) are fabricated separately, and both SRAM and 3D NAND dies are bonded together, which causes process complexity and manufacturing cost increase.

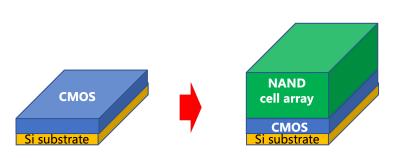

In the early days of 3D NAND products, it was fabricated by first forming CMOS transistors and then NAND memory cells. As shown in Figure 1.8, after the CMOS transistors were formed, the NAND memory cell arrays were formed beside it. This method is called CMOS Next to cell Array (CNA) process. The source lines of the NAND cell arrays are formed below the memory cells by a process that etches a trench in the Si (silicon) substrate and fills it with electrodes [31, 32]. This meant that the area of the CMOS circuit was small, and it was impossible to embed high-capacity SRAMs.

#### CMOS Next to cell Array (CNA)

Figure 1.8: 3D NAND fabricated by CNA (CMOS Next to cell Array) process.

3D NAND has increased its capacity by increasing the number of memory layers in each generation. However, as memory capacity increases, the peripheral circuits (decoders and sense amplifiers) used to access the memory cells also increase in size. The conventional CNA process could no longer accommodate the peripheral circuits increase, so a CMOS circuit was proposed to be placed under the NAND cell arrays. This is called the CUA (CMOS Under cell Array) process, as shown in Figure 1.9. This process accommodates more CMOS circuits in the die [33, 34].

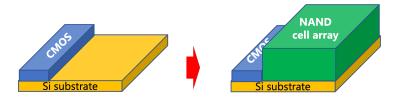

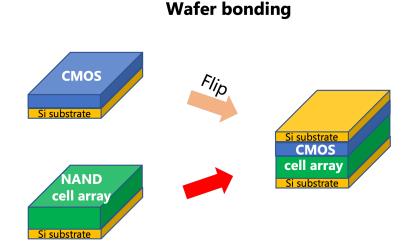

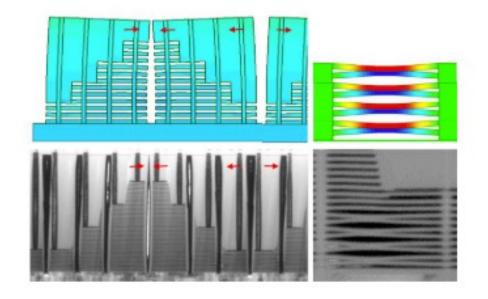

As 3D NAND capacity continues to increase, it will again become more difficult to accommodate CMOS circuits. In the future, CMOS circuits may be stacked like NAND cells. One such proposal is to create CMOS circuits and NAND cell arrays separately and finally stack them together to form one chip, as shown in Figure 1.10 [35, 36]. In this process, the CMOS circuit is

#### CMOS Under cell Array (CUA)

Figure 1.9: 3D NAND fabricated by CUA (CMOS Under cell Array) process.

not affected by the thermal process of NAND memory cell formation, thus increasing the choice of technology to be applied. However, this process only allows stacking two chips. Also, the manufacturing cost increases by fabricating separate chips. Since the bonding is done on the wafer rather than chip by chip, there are many issues that need to be addressed in order to achieve mass production, such as yield degradation. For these reasons, the CUA structure is suitable as the process for NAND with high-capacity SRAM at this moment.

Figure 1.10: 3D NAND fabricated by wafer bonding process.

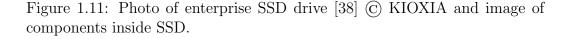

Another advantage of embedding high-capacity SRAM into 3D NAND is the replacement of DRAM used in the SSD (Solid-State Drive). Figure 1.11 shows the SSD image and components inside SSD used for a computing system. Typically, the SSD housing contains NAND flash memory according to its installed capacity, a controller that controls reading and writing, and DRAM as a buffer memory for exchanging data with the outside world at high speed. In a single NAND flash memory package, eight to sixteen NAND memory dies are stacked. Normally, the capacity of DRAM used as a cache is about one-thousandth of the SSD capacity. There was a study for embedding DRAM in NAND flash memory [37]. However, it was a planar capacitor DRAM and could not replace off-chip DRAM. If high-capacity SRAM could be embedded in 3D NAND, DRAM would no longer be needed, and the result would be a smaller, faster, and less expensive SSD.

# KIOXIA PM6 © BICS FLASH\* Enterprise SAS SSD NAND NAND NAND NAND

## 2.5 inch SSD

100 x 70 x 15 (mm)

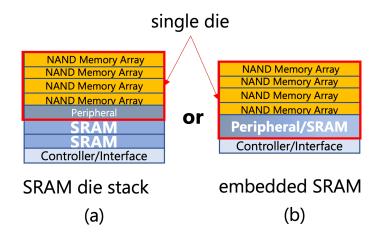

One approach is stacking NAND, SRAM, and controller by using TSV technology [39]. The other is embedding high-capacity SRAM in 3D NAND, as shown in Figure 1.12. If it is possible to create a process for integrating high-capacity SRAM that is compatible with the 3D NAND manufacturing process, it will be possible to significantly reduce the size of SSD, as shown in Figure 1.13.

#### CHAPTER 1. INTRODUCTION

In the future, together with the technology for stacking controller die with high-capacity SRAM embedded in 3D NAND, it will be possible to integrate server functions into a single package [40]. This will allow for smaller, more power-efficient servers and improved performance through massively parallel processing.

Figure 1.12: Image of two approaches to realize one package SSD. One is stacking 3D NAND, high-capacity SRAM and controller (a). The other is stacking SRAM embedded NAND and controller (b).

#### CHAPTER 1. INTRODUCTION

11.5 x 13.0 x 1.0 (mm)

Figure 1.13: Image of one package SSD drive [38] ⓒ KIOXIA.

## 1.3 Process comparison between SRAM and 3D NAND

There are some differences in the fabrication process between embedded SRAM with the logic process, stand-alone SRAM, and 3D NAND. In comparing the logic process used for embedded SRAM, stand-alone SRAM process, and NAND processes, it is important to know which generation to compare. The required technology generation depends on the required CMOS transistor performance. Embedded SRAM is manufactured using logic processes and design rules. In state-of-the-art logic, CMOS transistors are formed using a combination of FinFET (Fin Filed-Effect Transistor) and high- $\kappa$ /metal gate (HK/MG) [41]. On the other hand, stand-alone SRAMs are designed for high capacity while maintaining the high speed, and some special processes and design rules are used to keep manufacturing costs as low as possible.

NAND flash memory is mainly designed to reduce the cost per bit and is inferior in speed compared to DRAM. That is why the bit price of NAND flash is about 1/40th of that of DRAM (Table 1.1 [42]).

| Memory  | Capacity     | *Price (\$) | Gb price(\$) |      |

|---------|--------------|-------------|--------------|------|

| DRAM    | 16Gb<br>DDR4 | \$7.5       | \$0.47       | 1/40 |

| 3D NAND | 256Gb<br>TLC | \$3.07      | \$0.012      | 1/40 |

Table 1.1: Price per giga-bit of both DRAM and NAND [42].

\*Mar. 25<sup>th</sup>, 2022

The process is built with priority on the memory cells, and the CMOS transistors are formed in the process that forms the memory cells. Therefore, materials and transistor structures similar to those used in advanced logic are not applicable. Until now, it has been difficult to apply advanced logic processes to DRAM and NAND flash memory because the memory cells are

#### CHAPTER 1. INTRODUCTION

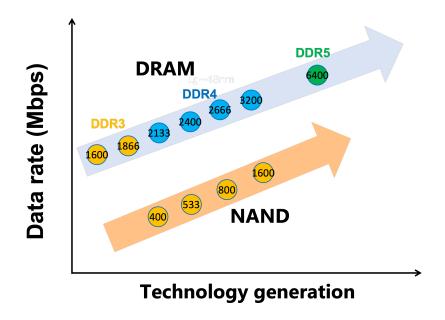

formed after CMOS transistor fabrication, and the process temperature for forming memory cells is more than 600°C, which is much higher than the conventional logic process. However, interface speeds have been increasing in recent years due to the demand for high-speed data processing, which in turn requires higher performance CMOS transistors. Therefore, DRAM is shifting to adopt HK/MG to improve CMOS performance. The interface speed of NAND flash memory follows DRAM as shown in Figure 1.14, and therefore the performance and process requirements for CMOS transistors are also following DRAM.

Figure 1.14: Interface speed trend of both DRAM and NAND.

The current CMOS generation used for 3D NAND is about 130 to 90 nm node technology. Therefore, as a starting point, it is beneficial to compare SRAM and 3D NAND processes based on the 90 nm generation CMOS technology and aims to extract the issues involved in the final integration of high-capacity SRAM into NAND flash memory.

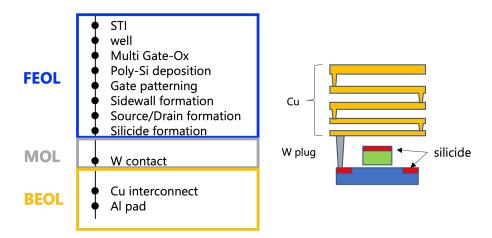

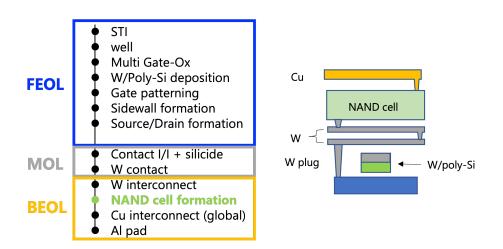

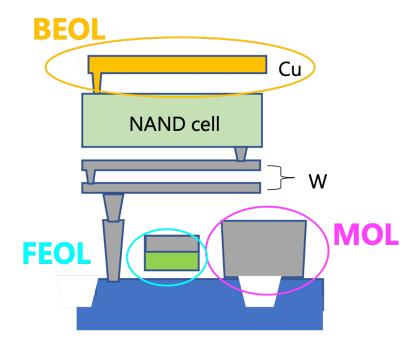

#### 1.3.1 Embedded SRAM process

Figure 1.15 shows a typical process flow of 90 nm node logic that is used for embedded SRAM fabrication [43, 44]. The process is divided into three parts. FEOL (Front End Of Line) process covers from STI (Shallow Trench Isolation) to before contact formation. MOL (Middle Of Line) process covers after silicide process to before first metal formation. BOEL (Back End Of Line) process covers the first interconnect layer and beyond. After gate electrode patterning, source and drain were formed, followed by a silicidation process. Cobalt silicide (CoSi<sub>2</sub>) [45–49] was formed in both the active area and the gate poly-Si. Copper (Cu) is used for all the interconnect layers. Low- $\kappa$  intermetal dielectric film was applied to reduce intermetal capacitance.

Figure 1.15: Process flow and schematic image for embedded SRAM.

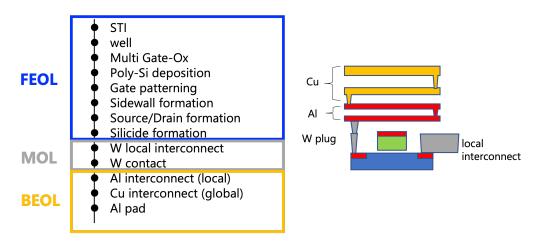

#### 1.3.2 Stand-alone SRAM process

The process flow of stand-alone SRAM is shown in Figure 1.16. The FEOL process is the same as that of embedded SRAM fabrication. The differences in both MOL and BEOL. The process difference is that the tungsten (W) used for contact formation is also used for short-distance wiring. As mentioned earlier, stand-alone SRAM requires not only performance but also cost Therefore, wiring is formed using tungsten used in contact reduction. embedding for short-distance wiring, the so-called "Local Interconnect (L.I.)" [50–52], and which does not affect performance. The details of the process are described in the MOL chapter, but by using L.I., it is possible to reduce the number of interconnect layers that form the SRAM cell by one layer. BEOL also differs slightly from the logic process. In high-capacity stand-alone SRAM, where low cost is required, aluminum (Al) interconnect is used for the bottom two layers. The upper two layers use copper interconnections for higher speed and power supply enhancement.

Figure 1.16: Process flow and schematic image for stand-alone SRAM.

#### **1.3.3 3D NAND process**

The process of 3D NAND is very different from that of the SRAM process, each in FEOL, MOL, and BEOL, as shown in Figure 1.17. First, FEOL requires a high voltage of nearly 30 V for programming NAND. Hence, an additional gate-oxide film for high-voltage transistors that is more than twice as thick as the gate oxide film for I/O (Input/Output) devices typically used in logic is necessary. Also, the gate electrode is not made of silicide but rather a polymetal gate made of polycrystalline silicon with tungsten layers. Furthermore, no silicide is formed in the source and drain diffusion layer regions at this step. The minimum gate length is also longer than that of conventional logic or SRAM because impurities in the source and drain diffuse during the high-temperature thermal process. After opening the contact hole, additional ion implantation to reduce contact resistance is carried out for the MOL process, followed by an activation anneal process. After that, cobalt is deposited in the contact hole to make CoSi<sub>2</sub> followed by a tungsten filling process [53]. For the BEOL process, since NAND cell formation requires a high-temperature thermal process of more than 600°C, multiple layers of tungsten, which has high thermal resistance, are used as interconnect instead of aluminum to connect CMOS devices. After NAND cell formation, copper interconnect for bit lines is formed. Due to the high-temperature thermal process after contact formation, the latest logic process, such as the gate-last HK/MG process, cannot be applied to CMOS. Low- $\kappa$  interlayer dielectric (ILD) film also cannot be applied to interconnect layers before the NAND cell formation.

Figure 1.17: Process flow and schematic image for 3D NAND.

#### **1.3.4** Key process modules

As analyzed in previous sections, the processes can be divided into three areas: FEOL, MOL, and BEOL. The same process is basically used for both embedded SRAM and stand-alone SRAM, but in order to reduce the manufacturing cost, stand-alone SRAM uses tungsten for local (short distance) wiring to reduce the number of interconnect layers after contact formation. In some cases, Al interconnect is used instead of Cu interconnect for lower-layer interconnections when high-speed performance is not required. In contrast, 3D NAND has a different gate dielectric and gate electrode structure, and polymetal gate electrodes are used instead of silicide. In addition, tungsten, which has high thermal resistance, is basically used for CMOS device connections, and usage of Cu interconnect kept to a minimum. Table 1.2 summarizes differences of process modules among three devices, and their impact on embedding high-capacity SRAM in the 3D NAND process should be studied. Process modules discussed in this thesis are indicated in Figure 1.18.

| Module   | Process                      | Embedded<br>SRAM    | Stand alone<br>SRAM | 3D NAND         |

|----------|------------------------------|---------------------|---------------------|-----------------|

| FEOL     | Gate<br>insulator            | SiON/high- $\kappa$ | SiON/high-ĸ         | SiON            |

| FEOL     | Gate<br>electrode            | Silicide/Metal      | Silicide/Metal      | Polymetal       |

| MOL      | Local<br>interconnect        | not available       | w                   | not available   |

| BEOL     | Interconnect                 | Cu/Low-k            | Al<br>Cu/Low-k      | W<br>Al<br>Cu   |

| MOL/BEOL | Temperature<br>after contact | < <b>400</b> ℃      | < <b>400</b> °C     | <b>600</b> °C < |

Table 1.2: Process modules and differences among three devices.

Figure 1.18: Schematic image of each process module.

### **1.4** Thesis focus and organization

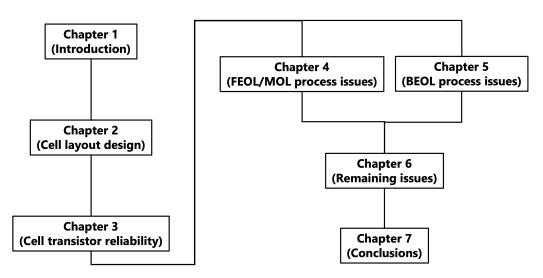

As mentioned in the previous section, there are advantages to realizing a small and power-efficient computing system for the advanced information society. Computing-in-Memory is a promising technology to satisfy this requirement, and a 3D NAND-based system with high-capacity SRAM can play an important role. The critical manufacturing processes are identified in FEOL, MOL, and BEOL, respectively, to embed high-capacity SRAM into 3D NAND. This thesis discusses the process technology challenges and implementation methods required for integrating high-capacity SRAM with 3D NAND memory with scalability, as 90 nm node technology is a starting point. The scaling scenario until moving to 3D stacking is discussed.

Figure 1.19 shows the organization of this thesis.

After introductory discussions in Chapter 1, Chapter 2 discusses the cell layout optimization methodology to realize high-reliable high-capacity SRAM. The importance of mechanical stress control, which is caused by manufacturing processes and device structure, is discussed.

In Chapter 3, the reliability of the CMOS transistor used in the SRAM cell is analyzed. The minimum dimension MOS transistors show enhanced degradation. The mechanism and design guidelines are proposed to realize high-reliable high-capacity SRAM embedded in 3D NAND.

Chapter 4 describes FEOL and MOL process technologies that enable high-capacity SRAM in 3D NAND. Gate-first HK/MG process options for future scaling and impact of local interconnect with process guidelines are presented.

Chapter 5 proposes the BEOL processes to realize high-reliable highcapacity SRAM. Low- $\kappa$  interlayer dielectric film options for future multi-layer copper interconnect, and redundancy fuse processes are discussed.

Chapter 6 discusses the remaining technical issues and proposes viable solutions for 3D integration which realize future single-package computing systems.

The conclusion of this thesis is shown in Chapter 7.

Figure 1.19: Thesis organization.

### Chapter 2

# Layout and transistor structure design for high-reliability SRAM

### 2.1 Background

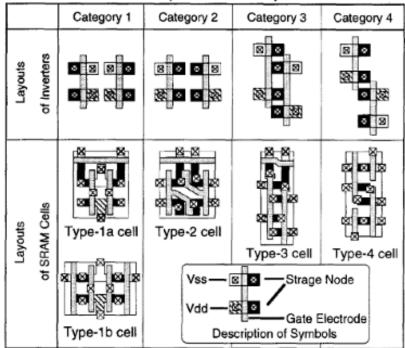

This chapter aims to study a suitable layout for SRAM cells, considering that they are embedded in 3D NAND. As mentioned in the previous chapter, the CMOS process used for 3D NAND is very different from the process used for embedded or stand-alone SRAM. Various cell layouts for SRAM have been studied in the past. Figure 2.1 compares cell designs for high-speed SRAM at the 180 nm generation by M. Ishida *et al.* [54]. They showed that the Type-1b cell, in which the active area (AA) is arranged in a straight line and the gate electrode (GE) is also placed in parallel, is superior in terms of scalability and speed by shorter bit-line length compared to the Type-1a cell (referred to as conventional cell). However, no concrete studies have been conducted on Type-4 cells (referred to as thin cells).

Table-1: Variations of the inverter layouts and SRAM cell layouts.

Figure 2.1: SRAM cell layouts study by M. Ishida *et al.* [54].ⓒ 1998 IEEE

Figure 2.2: The first demonstration of SRAM cell used the Type-4 layout in Figure 2.1 by K. Osada *et al.* [55]. $\bigcirc$  2001 IEEE

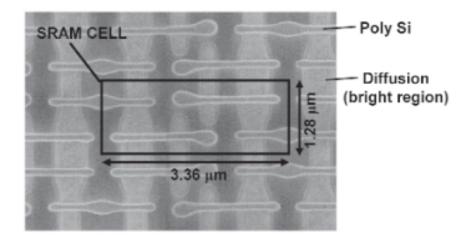

In 2001, K. Osada *et al.* demonstrated the results of the first prototype of a 180 nm generation 32 kb high-speed cache SRAM using the thin cell, as shown in Figure2.2 [55]. While the bit-line (BL) length can be further shortened compared to Type-1b, the word-line (WL) length becomes longer, and the WL decoder circuit needs to be redesigned due to the lower cell height, resulting in the decoder circuit extending in the horizontal direction with chip size increase. However, conventional cells (Type-1a and Type-2) have still been used for high-capacity SRAM cells [56–58] and embedded applications at 90 nm generation, as shown in Figure 2.3 [59]. Therefore, it is important to select an SRAM cell layout with excellent scalability and verify that there are no characteristic problems with that SRAM cell. The following sections discuss the optimum SRAM cell layout to embed in the 3D NAND.

Figure 2.3: Example of Type-1a SRAM cell layout used for 90 nm node logic product [59]. The cell size is 1  $\mu$ m<sup>2</sup>. © 2002 IEEE

### 2.2 Selection of SRAM cell layout

### 2.2.1 Cell layout comparison

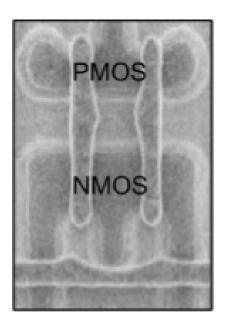

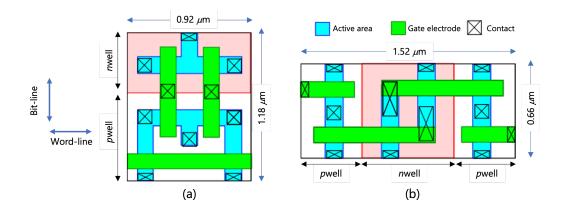

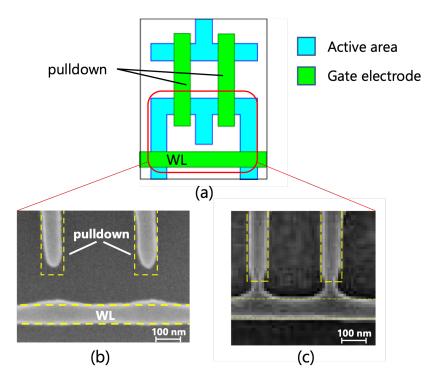

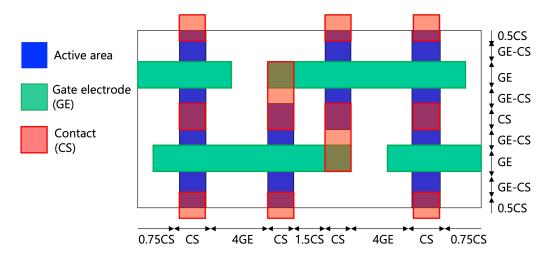

As mentioned in Chapter 1, the transistor technology used in 3D NAND is about 130 to 90 nm nodes, so it is important to consider scalability starting from the 90 nm node design rule. Since two types of SRAM cell layouts are proposed in 90 nm nodes, it is important to evaluate and decide on the scalable SRAM cell layout considering the extendibility. The advantages and disadvantages of both conventional and thin cells are summarized in Table 2.1. For a conventional cell (a), the aspect ratio of the unit cell is closed to one, which is easy to design large cell arrays with peripheral circuits. However, active areas have bending patterns that cause rounding shapes at corners resulting in dimension variation. The orthogonal layout of gate electrodes also needs attention to prevent pattern short by lithography process fluctuation. In contrast, thin cells are composed only of straight patterns. Therefore, the controllability of dimensions is considered superior to that of the conventional cell. The lower cell height shortens

| Cell type           | Advantage                                     | Disadvantage                                            |

|---------------------|-----------------------------------------------|---------------------------------------------------------|

| Conventional<br>(a) | Peripheral design<br>cell spect ~ 1           | Bending active area<br>Orthogonal gate electorde        |

| Thin<br>(b)         | Simple (straight) pattern<br>Shorter bit line | Longer WL<br>WL decorder congestion<br>Chip size impact |

Table 2.1: Advantages and disadvantages of both conventional and thin cells.