# T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

## 論文 / 著書情報 Article / Book Information

| 題目(和文)            |                                                                                                                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | 1T1C FeRAM memory array with Hf0.5Zr0.5O2-based ferroelectric film                                                                                                                              |

| 著者(和文)            | 奥野潤                                                                                                                                                                                             |

| Author(English)   | Jun Okuno                                                                                                                                                                                       |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第12384号,<br>授与年月日:2023年3月26日,<br>学位の種別:課程博士,<br>審査員:角嶋 邦之,筒井 一生,舟窪 浩,渡辺 正裕,大見 俊一郎,若林 整                                                                    |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第12384号,<br>Conferred date:2023/3/26,<br>Degree Type:Course doctor,<br>Examiner:,,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                            |

| Type(English)     | Doctoral Thesis                                                                                                                                                                                 |

## 1T1C FeRAM memory array with $Hf_{0.5}Zr_{0.5}O_2$ -based ferroelectric film

Jun Okuno

Thesis

Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Engineering

Thesis Advisor: Professor Hitoshi Wakabayashi

Department of Electrical and Electronic Engineering, School of Engineering, TOKYO INSTITUTE OF TECHNOLOGY

## Table of Contents

| List of | Tables                                                                   | iv  |

|---------|--------------------------------------------------------------------------|-----|

| List of | Figures                                                                  | V   |

| Acknow  | wledgements                                                              | xiv |

| ABSTR   | ACT                                                                      | 1   |

| Chapte  | er 1 Introduction                                                        | 2   |

| 1.1     | Background                                                               | 2   |

| 1.2     | Ferroelectricity of hafnium-oxide-based material                         | 6   |

| 1.3     | Application of hafnium-oxide-based ferroelectric material                | 8   |

| 1.4     | Challenges of conventional methods                                       | 10  |

| 1.5     | Motivation of this thesis                                                | 12  |

| 1.6     | Structure of this thesis                                                 | 14  |

| Chapte  | er 2 Material development                                                | 15  |

| 2.1     | Introduction                                                             | 15  |

| 2.2     | Material selection for ferroelectric films                               | 15  |

| 2.3     | Thermal stability of the ferroelectric material                          | 20  |

| 2.4     | Summary                                                                  | 24  |

| Chapte  | er 3 Fabrication and design of $Hf_{0.5}Zr_{0.5}O_2$ -based 1T1C FeRAM   | 25  |

| 3.1     | Introduction                                                             | 25  |

| 3.2     | Capacitor under bitline structure                                        | 26  |

| 3.3     | Process flow                                                             | 28  |

| 3.4     | Design of 1T1C FeRAM memory array                                        | 31  |

| 3.5     | CMOS characteristics                                                     | 34  |

| 3.6     | Summary                                                                  | 35  |

| Chapte  | er 4 Memory array performance of $Hf_{0.5}Zr_{0.5}O_2$ -based 1T1C FeRAM | 36  |

| 4.1     | Introduction                                                             | 36  |

| 4.2     | Validation of read operation                                             | 37  |

| 4.3     | Shmoo plots                                                                                         | 40  |

|---------|-----------------------------------------------------------------------------------------------------|-----|

| 4.4     | Switching kinetic analysis                                                                          | 42  |

| 4.5     | Summary                                                                                             | 44  |

| Chapte  | er 5 Memory window analysis of Hf <sub>0.5</sub> Zr <sub>0.5</sub> O <sub>2</sub> -based 1T1C FeRAM | 46  |

| 5.1     | Introduction                                                                                        | 46  |

| 5.2     | Distribution of bitline voltage difference                                                          | 47  |

| 5.3     | MFM memory window capacitance area dependency                                                       | 53  |

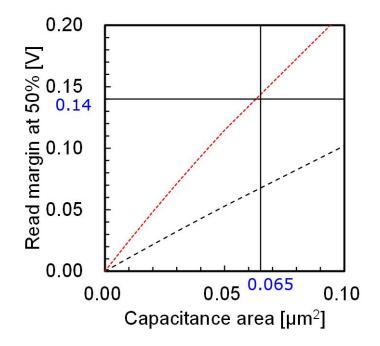

| 5.4     | Memory window prediction for future technology node                                                 | 57  |

| 5.5     | Summary                                                                                             | 62  |

| Chapte  | er 6 Reliability study on $Hf_{0.5}Zr_{0.5}O_2$ -based 1T1C FeRAM                                   | 64  |

| 6.1     | Introduction                                                                                        | 64  |

| 6.2     | Experiments                                                                                         | 67  |

| 6.3     | Validation of ferroelectric performance on thinner HZO                                              | 69  |

| 6.4     | Cycling tolerance for hard breakdown                                                                | 79  |

| 6.5     | Fatigue and its recovery                                                                            | 88  |

| 6.6     | Summary                                                                                             | 103 |

| Chapte  | er 7 Conclusions                                                                                    | 105 |

| 7.1     | Summary of this thesis                                                                              | 105 |

| 7.2     | Future technologies and directions                                                                  | 110 |

| Refere  | nces                                                                                                | 119 |

| Publica | ations and Presentations                                                                            | 129 |

### List of Tables

| 1.1 | Comparison table of performance in embedded memories.               | 5   |

|-----|---------------------------------------------------------------------|-----|

| 1.2 | Comparison table of ferroelectric properties <sup>1,2</sup> .       | 7   |

| 1.3 | Comparison table of performance in $Hf_{0.5}Zr_{0.5}O_2$ -based mem | ory |

|     | devices <sup>1</sup> .                                              | 9   |

| 1.4 | Target performance comparing with another technology.               | 13  |

| 5.1 | FeRAM technology roadmap from ITRS road map 2013 <sup>3</sup> .     | 54  |

| 5.2 | Estimated MFM specification for 40 nm technology node.              | 54  |

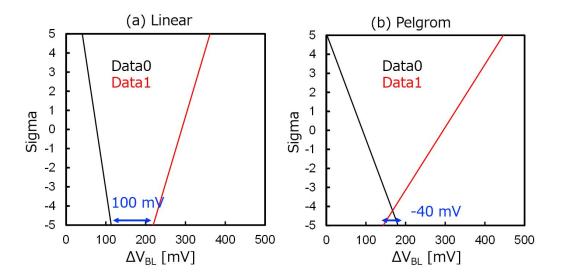

| 5.3 | Input parameters for Monte Carlo simulation.                        | 59  |

| 5.4 | Output parameters for MFM area of 0.1 $\mu$ m <sup>2</sup> .        | 60  |

| 5.5 | Input parameters for Monte Carlo Simulation for 40 nm CMO           | DS  |

|     | technology.                                                         | 61  |

| 5.6 | Comparison table with target.                                       | 63  |

| 6.1 | Comparison table with target.                                       | 104 |

| 7.1 | Comparison table with this technology.                              | 109 |

| 7.2 | Diameter of the cylinder for each technology nodes.                 | 115 |

| 7.3 | Height of the cylinder for the numbers of metal layer.              | 115 |

| 7.4 | Summary of memory cell area and aspect ratio for each               |     |

|     | technology node.                                                    | 117 |

## List of Figures

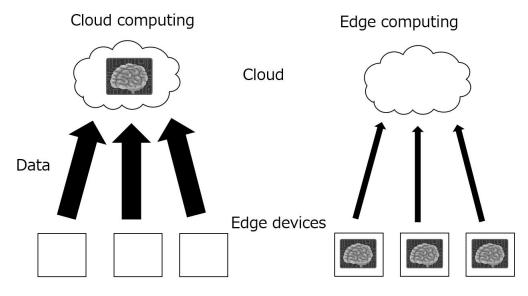

| 1.1 | Illustration of cloud computing and edge computing                                                                                                                                                      |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | architectures.                                                                                                                                                                                          | 3  |

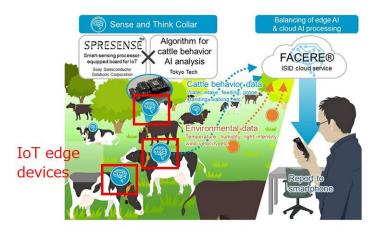

| 1.2 | Use case of the edge IoT device application <sup>4</sup> .                                                                                                                                              | 3  |

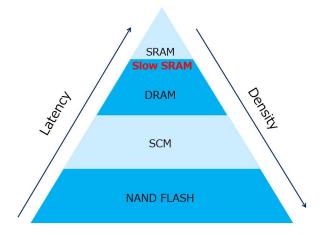

| 1.3 | Hierarchical structure of memory showing trade-off between capacity and latency.                                                                                                                        | 4  |

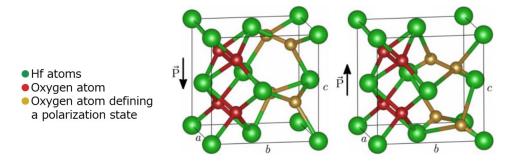

| 1.4 | Schematic diagram of a $Pca2_1$ unit cell corresponding to polar-<br>orthorhombic phase with two opposite polarization directions in<br>hafnium oxide. Picture was taken with permission <sup>5</sup> . | 6  |

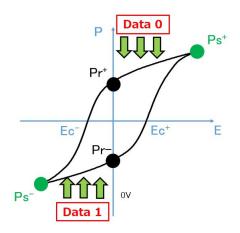

| 1.5 | Polarization vs. electric field for ferroelectric behavior.                                                                                                                                             | 7  |

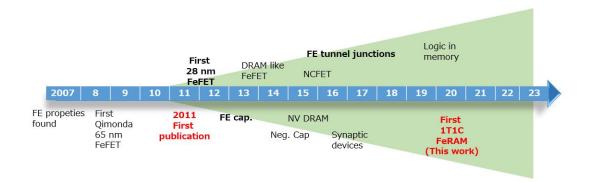

| 1.6 | Chronology of semiconductor ferroelectric science and industry discoveries and advances since first reported. Picture is adapted from work <sup>6</sup> .                                               | 9  |

| 1.7 | Illustration of a conventional test structure for MFM with larger than 100 $\mu m^2.$                                                                                                                   | 11 |

| 1.8 | Structure of this thesis.                                                                                                                                                                               | 14 |

| 2.1 | Schematic illustration of crystal phase of ferroelectric HZO. <sup>7–13</sup>                                                                                                                           | 16 |

| 2.2 | Schematic illustration of an ALD cycle.                                                                                                                                                                 | 17 |

| 2.3 | Remanent polarization as a function of the Zr content in the film for different Hf- and Zr-based precursor combinations <sup>14–16</sup> . Picture was taken with permission <sup>14</sup> .            | 19 |

| 2.4 | Contour plots for a remanent polarization as a function of Zr content and ozone dose time <sup>14–16</sup> . Picture was taken with permission <sup>14</sup> .                                          | 19 |

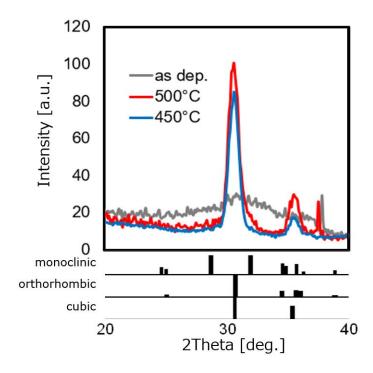

| 2.5 | GIXRD spectrum of the TiN/HZO/TiN stack annealed at 450°C, 500°C and without annealing.                                                                                                                 | 21 |

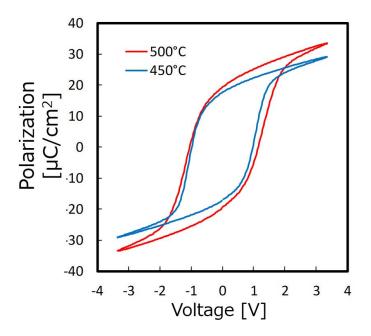

| 2.6 | Polarization vs voltage hysteresis of the MFM capacitors after RTA at 450 and 500°C and for 30 s after 100 cycles at 1 kHz. The                                                                         |    |

|     | bottom electrode was fixed to ground and the applied voltage of<br>the top electrode was swept.                                                                                                                                                                        | 22 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

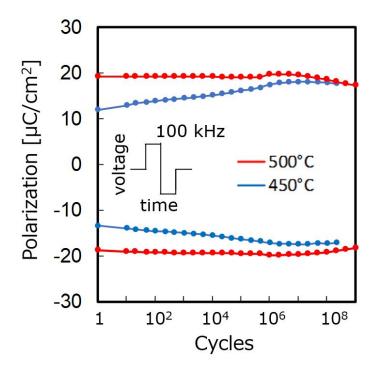

| 2.7 | Cycling tolerance of the MFM capacitors after RTA at 450 and 500°C for 30 s. Cycling tolerance for 3 V amplitude at 100 kHz up to 10 <sup>9</sup> cycles. Inset Figure shows the pulse shape.                                                                          | 23 |

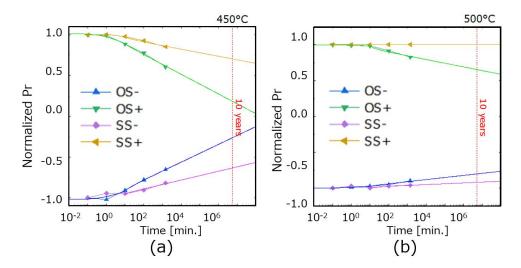

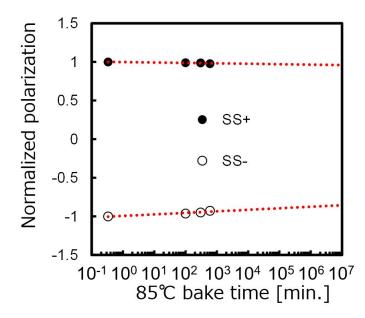

| 2.8 | Data retention up to 1000 min baking time at 85°C for the same<br>state (SS) and the opposite state (OS) after RTA at (a) 450°C for<br>30 s and (b) 500°C for 30 s. The lines are prediction to 10 years<br>using fitting model of previous report <sup>17</sup> .     | 23 |

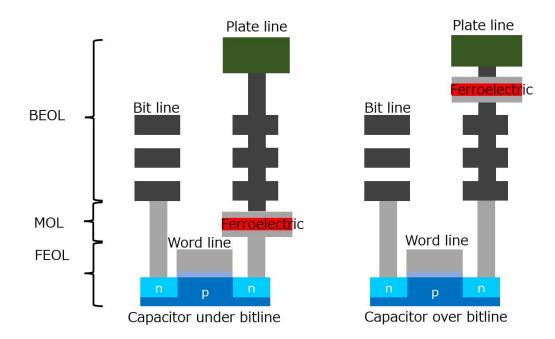

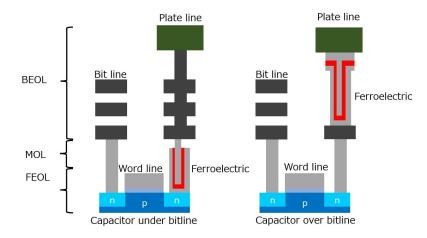

| 3.1 | Schematic illustration of capacitor under bitline structure (left) and capacitor over bitline structure (right).                                                                                                                                                       | 27 |

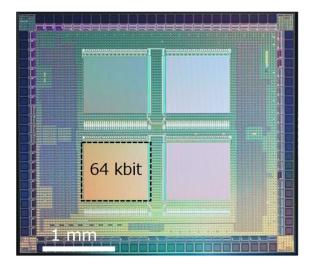

| 3.2 | Optical microscope image of the 64 kbits 1T1C FeRAM test chip.                                                                                                                                                                                                         | 28 |

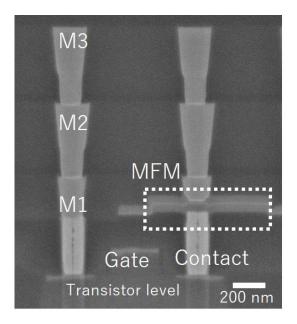

| 3.3 | Scanning Electron Microscope cross section of one 1T1C cell.                                                                                                                                                                                                           | 29 |

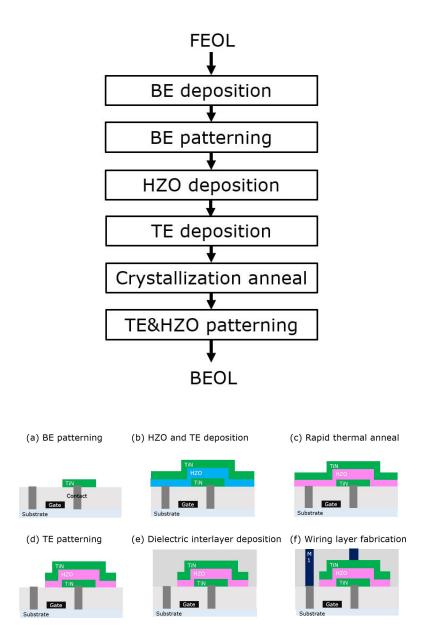

| 3.4 | Process flow for the fabrication of the capacitor under bitline structure.                                                                                                                                                                                             | 30 |

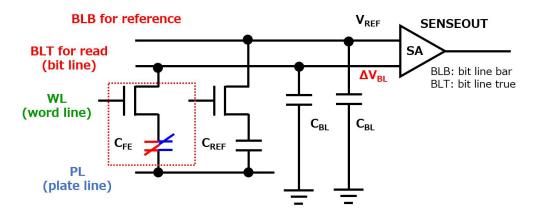

| 3.5 | Schematic design of SA for read-out operation.                                                                                                                                                                                                                         | 31 |

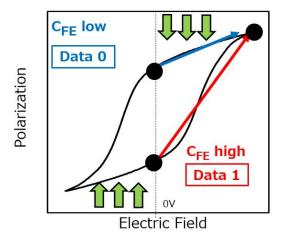

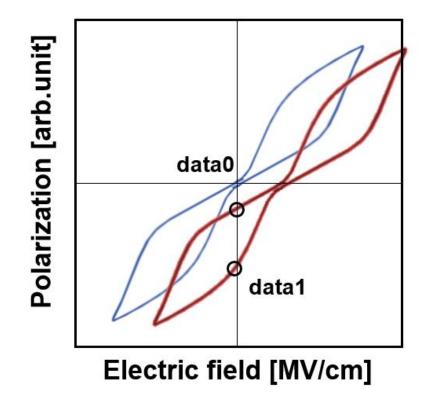

| 3.6 | Definition of two different polarity states, data0 and data1. Data0 is defined as the polarization up state, whereas data1 is defined as the polarization down state.                                                                                                  | 33 |

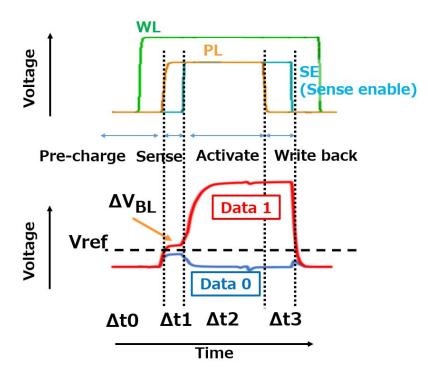

| 3.7 | Schematic illustration of a step pulse sensing scheme using SA.                                                                                                                                                                                                        | 33 |

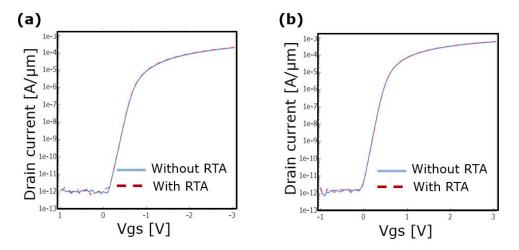

| 3.8 | Id-Vg transfer characteristics of CMOS transistors for (a) PMOS and (b) NMOS with and without 500°C RTA.                                                                                                                                                               | 34 |

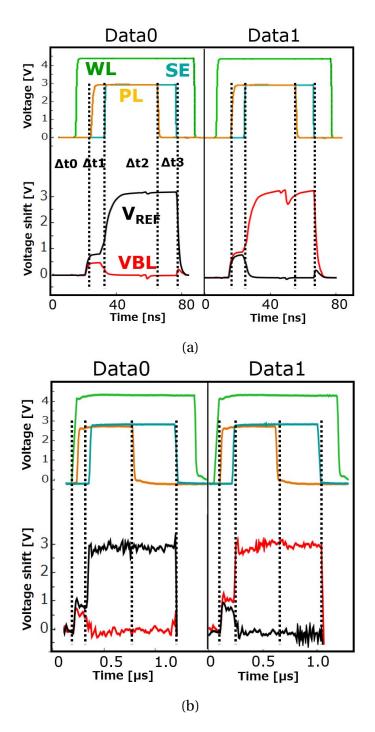

| 4.1 | Timing diagrams for the read operation scheme of the 1T1C<br>FeRAM cell for data0 and data1: (a) simulation results and<br>(b) experimental waveforms. The time scale of the experimental<br>result was limited to 1 MHz due to the test environmental<br>restriction. | 38 |

| 4.2 | Enlarged image of the simulated waveform during the sense period in the Figure 4.1(a).                                                                                                                                                                                                                                                       | 39 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

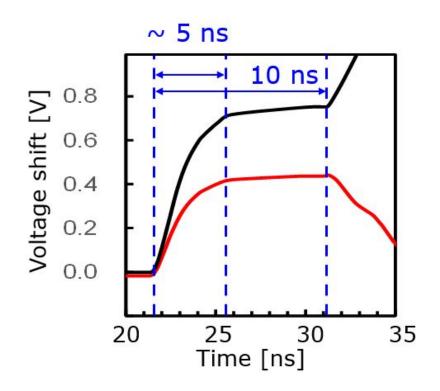

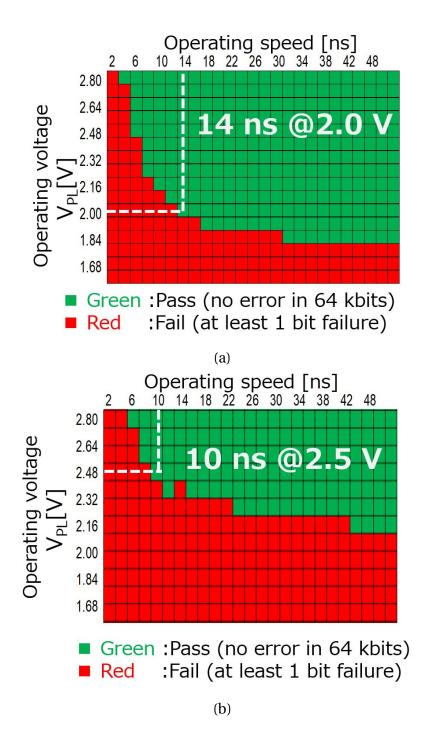

| 4.3 | Shmoo plot of time ranging from 1 to 50 ns and operation voltage ranging from 2.0 to 3.5 V obtained on the 64 kbits CUB-structured 1T1C FeRAM memory array with the capacitor size of 0.4 $\mu$ m <sup>2</sup> for (a) write and (b) sense (green: pass, red: fail).                                                                         | 41 |

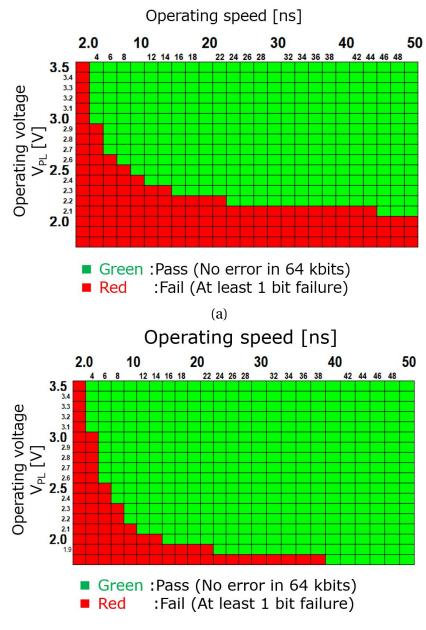

| 4.4 | Switching models.                                                                                                                                                                                                                                                                                                                            | 42 |

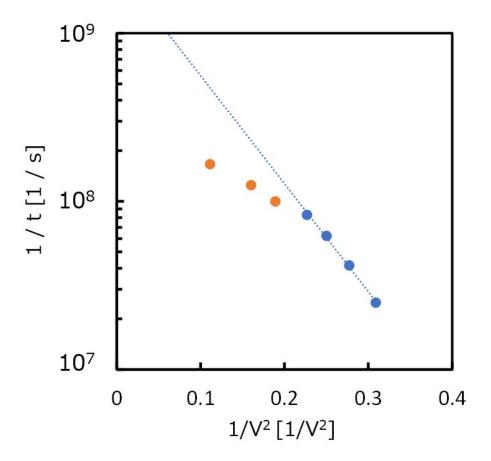

| 4.5 | Reciprocal switching time versus $1/V^2$ for the CUB-structured FeRAM. Switching time and voltage are extracted from the shmoo plot. The line in the Figure is a least-squares fitting using data over 10 ns.                                                                                                                                | 44 |

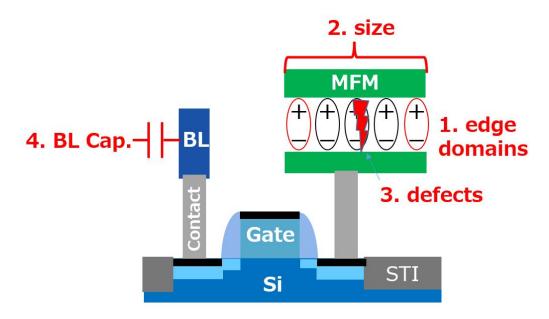

| 5.1 | Root causes of variation in ferroelectric materials.                                                                                                                                                                                                                                                                                         | 48 |

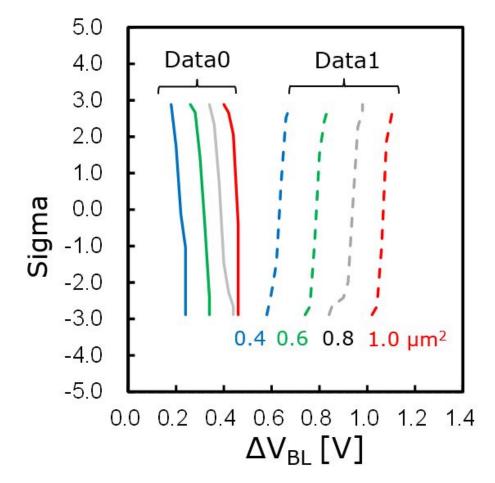

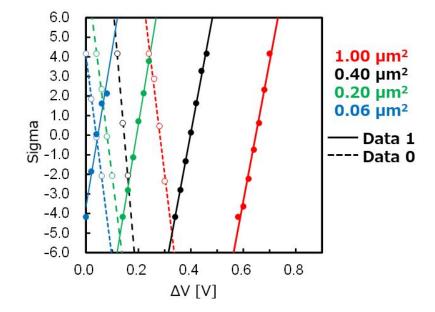

| 5.2 | Normal distribution plot of $\Delta V_{BL}$ for the CUB-structured 64 kbits 1T1C FeRAM operated at 2.5 V, 100 ns for capacitors having 0.4, 0.6, 0.8 and 1.0 $\mu$ m <sup>2</sup> capacitor area.                                                                                                                                            | 50 |

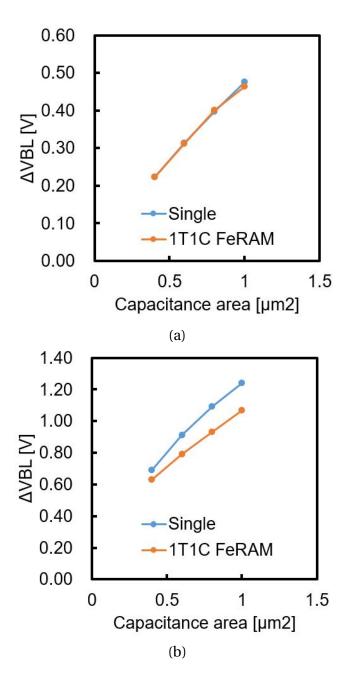

| 5.3 | Comparison of $\Delta V_{BL}$ between single large capacitor and 1T1C FeRAM at 0.4, 0.6, 0.8 and 1.0 $\mu$ m <sup>2</sup> capacitor area for (a) data0 and (b) data1. The $\Delta V_{BL}$ of the single capacitor was calculated using the capacitance using C <sub>BL</sub> with 250 fF and capacitance extracted from Figure 2.6 at 500°C. | 51 |

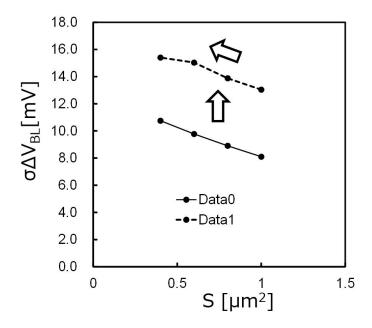

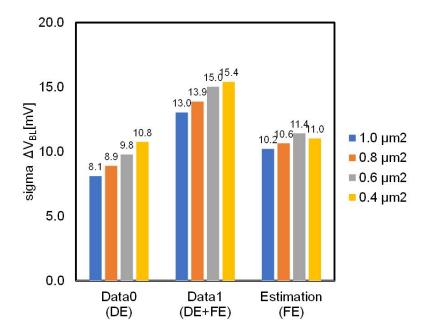

| 5.4 | Variability of $\Delta V_{BL}$ for the CUB-structured 64 kbits 1T1C FeRAM operated at 2.5 V, 100 ns for capacitors having 0.4, 0.6, 0.8 and 1.0 $\mu m^2$ capacitor area.                                                                                                                                                                    | 52 |

| 5.5 | Variability of $\Delta V_{BL}$ comparison between DE and FE components having 0.4, 0.6, 0.8 and 1.0 $\mu m^2$ capacitor area.                                                                                                                                                                                                                | 52 |

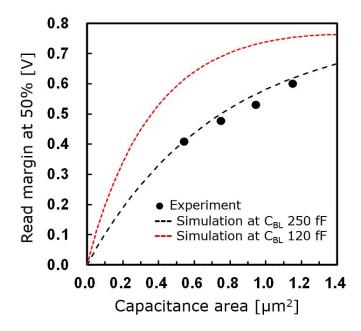

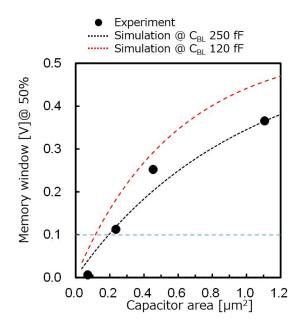

| 5.6 | Read margin of the test chip for 2.5 V, 100 ns operation as a function of the capacitor area. The values of $C_{BL}$ were determined as 250 fF for the 130 nm technology.                                                                                                                                                                    | 55 |

|     |                                                                                                                                                                                                                                                                                                                                              |    |

| 5.7  | Read margin of the test chip for 2.5 V, 100 ns operation as a function of the capacitor area. The values of $C_{BL}$ were determined as 250 fF for the 130 nm technology and 120 fF for 40 nm technology.                                                                                                                                                         | 56 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

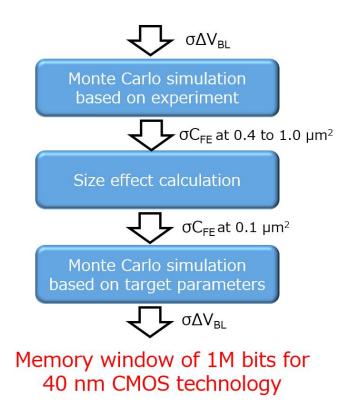

| 5.8  | Schematic illustration of method for predicting memory window combining Monte Carlo simulation.                                                                                                                                                                                                                                                                   | 58 |

| 5.9  | Monte Carlo simulation result for $\sigma \Delta V_{BL}$ with different variability<br>of $\sigma C_{FE}$ for MFM area of 1.0, 0.8, 0.6 and 0.4 µm <sup>2</sup> for data1 (left)<br>and data0 (right).                                                                                                                                                            | 59 |

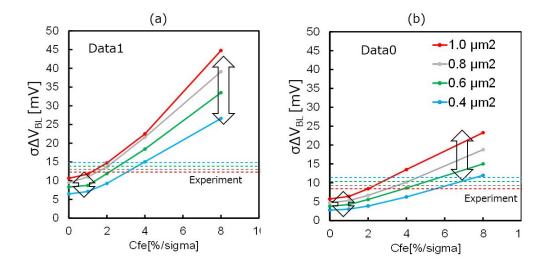

| 5.10 | $\sigma C_{\rm FE}$ as a function of MFM area for (a) Linear fitting plot and (b) Pelgrom plot.                                                                                                                                                                                                                                                                   | 60 |

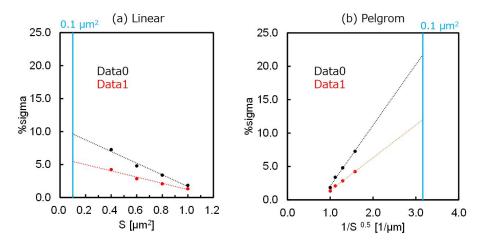

| 5.11 | Memory window of 1 Mbits distribution at MFM area of 1.0 $\mu m^2$ for (a) Linear fitting plot and (b) Pelgrom plot.                                                                                                                                                                                                                                              | 61 |

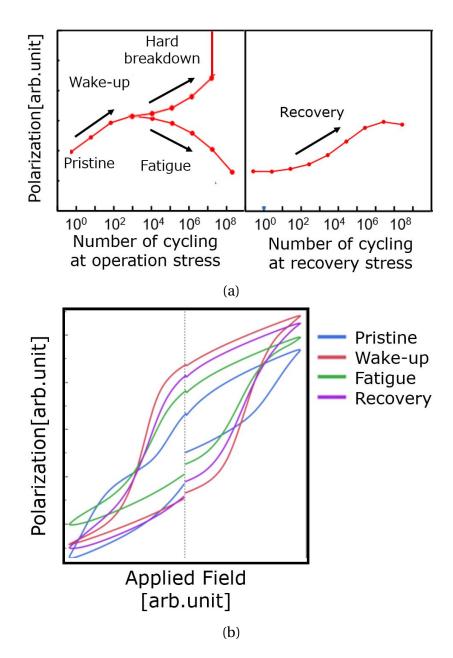

| 6.1  | Schematic illustration of ferroelectricity in 4 stages; pristine,<br>Wake-up, fatigue and recovery (a) Polarization during cycling<br>stress for operation stress and recovery stress. The recovery<br>stress should higher stress than operation stress. (b) Example of<br>ferroelectric behaviour of polarization vs. electric field plots for<br>the 4 stages. | 66 |

| 6.2  | Schematic illustration of a motivation of film thickness scaling of HZO and band diagram in the HZO in this thesis.                                                                                                                                                                                                                                               | 67 |

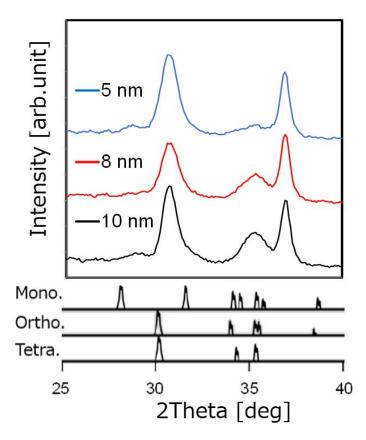

| 6.3  | GIXRD spectra on 5, 8 and 10 nm thick HZO MFM capacitors.                                                                                                                                                                                                                                                                                                         | 69 |

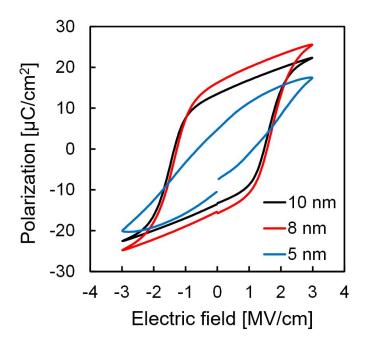

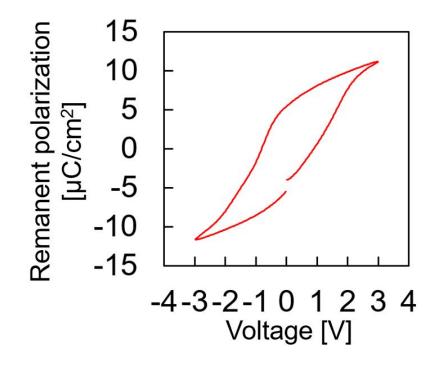

| 6.4  | Polarization vs electric filed for MFM capacitors with 5, 8 and 10 nm thick HZO at maximum applied electric field of 3 MV/cm at 1 kHz.The bottom electrode was fixed to ground and the applied voltage of the top electrode was swept.                                                                                                                            | 70 |

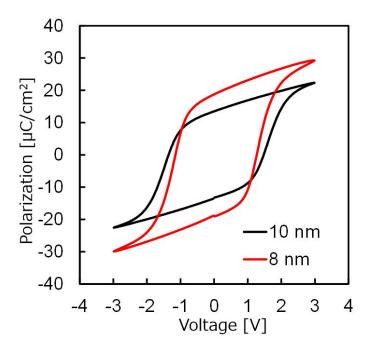

| 6.5  | Polarization vs voltage hysteresis of a MFM capacitor for 8 and<br>10 nm thick HZO samples with applied voltage of 3 V at 1 kHz.<br>5 nm thick HZO sample has been broken during measurement                                                                                                                                                                      |    |

|      | and not shown in this figure. The bottom electrode was fixed to ground and the applied voltage of the top electrode was swept.                                                                                                                                                | 71 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

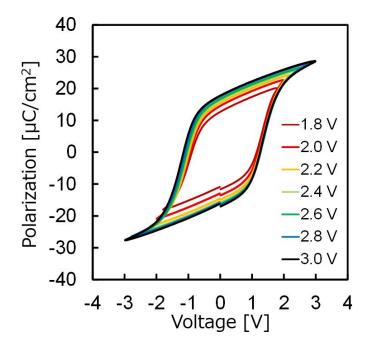

| 6.6  | Dependence on applied voltage ranging from 1.8 to 3.0 V for the<br>8 nm sample. The bottom electrode was fixed to ground and the<br>applied voltage of the top electrode was swept.                                                                                           | 72 |

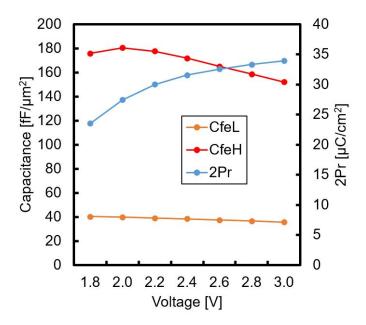

| 6.7  | Applied voltage dependence of capacitance and remanent<br>polarization (2Pr) for data0 and data1 extracted by definition in<br>Figure 3.6.                                                                                                                                    | 72 |

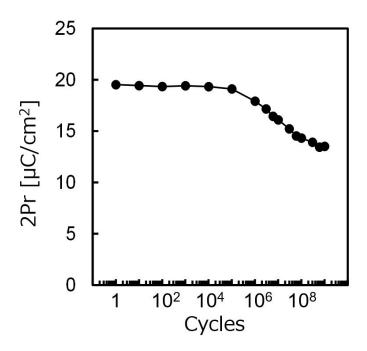

| 6.8  | Reliability result for endurance at 2.0 V stress voltage and<br>at 100 kHz Dynamic Hysteresis Measurement post wake-up<br>cycling for the 8 nm thick sample. Measurement was stopped at<br>10 <sup>9</sup> cycles.                                                            | 73 |

| 6.9  | Retention tests have been performed on HZO with a thickness<br>of 8 nm for firing times up to 60 min at 85°C and prediction up<br>to 10 years under the same conditions. The line in the Figure is a<br>least-squares fitting using data.                                     | 74 |

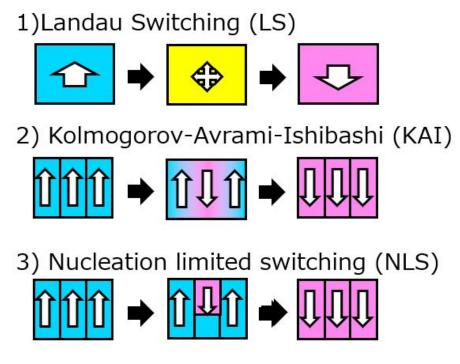

| 6.10 | Shmoo plot of time ranging from 1 to 50 ns and operation voltage ranging from 1.6 to 2.8 V obtained (green: pass, red: fail) on the 64 kbits 1T1C FeRAM memory array for (a) 8 nm thick HZO at 0.2 $\mu$ m <sup>2</sup> and (b) 10 nm thick HZO at 0.4 $\mu$ m <sup>2</sup> . | 76 |

| 6.11 | $\Delta V_{BL}$ distribution of the 1T1C FeRAM for 64 kbits at 2.0 V with 100 ns operation at 0.06, 0.20, 0.40 and 1.0 $\mu$ m <sup>2</sup> capacitor areas using the 8 nm sample.                                                                                            | 77 |

| 6.12 | Read margin of test chip 2.0 V, 100 ns operation as a function of capacitor area. Values of $C_{BL}$ were determined as 250 fF for the 130 nm technology and 120 fF for the 40 nm technology.                                                                                 | 77 |

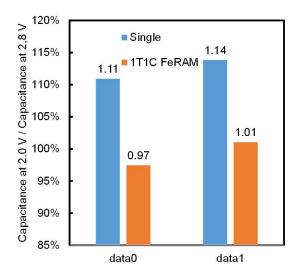

| 6.13 | The rate of capacitance change due to lower voltage operation<br>from 2.8 to 2.0 V for single capacitor and 1T1C FeRAM. The<br>parameter of single capacitor was calculated using Figure 6.7.                                                                                 |    |

|      | The capacitance of 2.0 V for 1T1C FeRAM was calculated by Figure 6.11 and 2.8 V by Figure 6.31 using Equation 5.4.                                                                                                                                                                                                                                                                                                                                                                        | 78 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

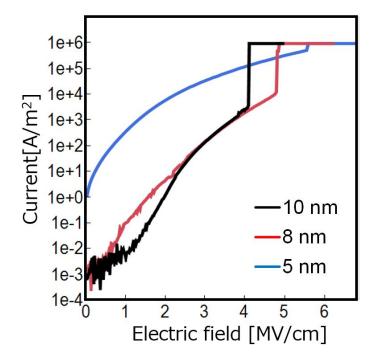

| 6.14 | J-E characteristics of 5 (blue), 8 (red) and 10 nm (black) samples consisting of one large MFM capacitor at 1,000 $\mu$ m <sup>2</sup> with 1,000 capacitors connected in parallel (1 $\mu$ m <sup>2</sup> each). The bottom electrode was fixed to ground and the applied voltage of the top electrode was swept at 2 V/s.                                                                                                                                                               | 80 |

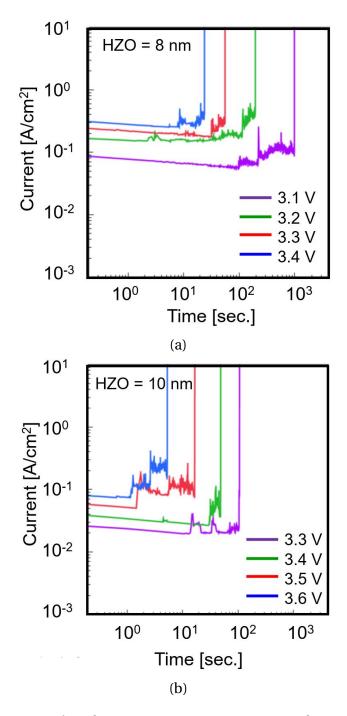

| 6.15 | Results of current trace measurements for (a) 8 nm and (b) 10 nm<br>thick samples with one large MFM capacitor of 1,000 $\mu$ m <sup>2</sup> area<br>and 1,000 capacitors (1 $\mu$ m <sup>2</sup> each) connected in parallel. The<br>5 nm thick HZO was excluded from the TDDB measurement<br>because of its large leakage current and inability to detect clear<br>breakdowns.                                                                                                          | 82 |

| 6.16 | P–E characteristics post soft breakdown during the current–time<br>trace measurement on another device under the same test<br>conditions. The bottom electrode was fixed to ground and the<br>applied voltage of the top electrode was swept.                                                                                                                                                                                                                                             | 83 |

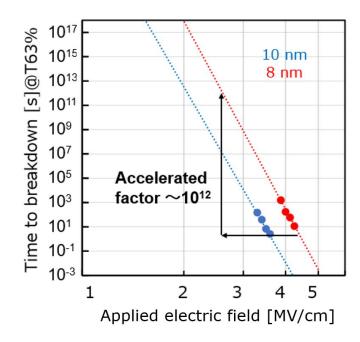

| 6.17 | The tBD at 63% (T63) versus electric field in a log–log graph for<br>both 8 nm (red) and 10 nm (blue) samples. A total of 22 devices<br>were tested for stress for each sample. Weibull slopes of 1.01 and<br>1.00 were used for the 8 nm and 10 nm samples plots, respectively.                                                                                                                                                                                                          | 84 |

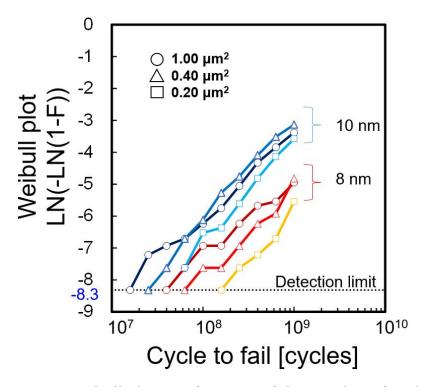

| 6.18 | Weibull plot as a function of the number of cycles to failure for<br>4 kbits of the 8 nm and 10 nm samples at a capacitance area in a<br>memory cell of 0.20, 0.40 and $1.00 \mu\text{m}^2$ with a same bipolar stress<br>electric field of 4.4 MV/cm on both samples. The detection limit<br>was obtained by substituting 1/4000 for the probability of failure<br>F in the Weibull formula. The measurement for 5 nm thick HZO<br>has not been performed due to extremely high leakage. | 86 |

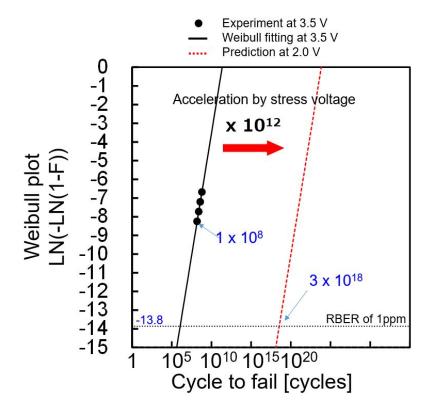

| 6.19 | Weibull fitting plot as a function of the number of cycles to failure for the 8 nm sample at a capacitance area in a memory                                                                                                                                                                                                                                                                                                                                                               |    |

х

cell of  $0.20 \ \mu m^2$ . The black line shows a fitting curve based on the experimental results at an operating voltage of  $3.5 \ V$ . The red line shows a prediction at  $2.0 \ V$  using accelerated factor extracted from Figure 6.17. The detection limit was obtained by substituting 1 ppm for the probability of failure F in the Weibull formula.

87

90

91

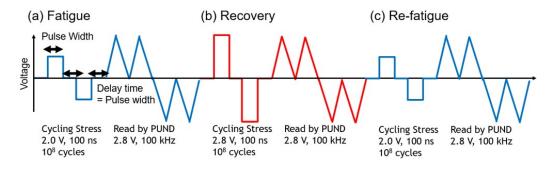

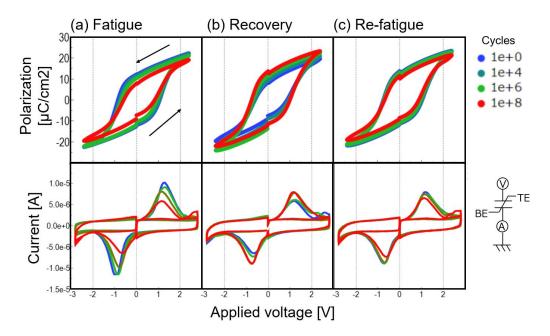

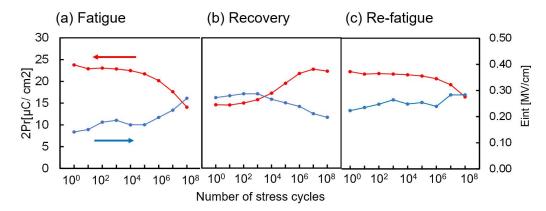

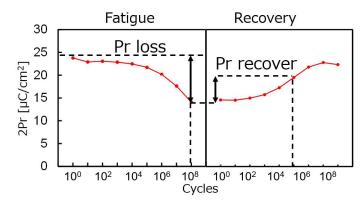

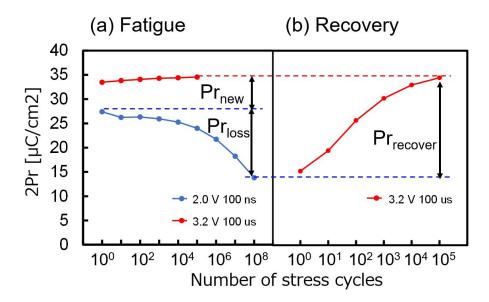

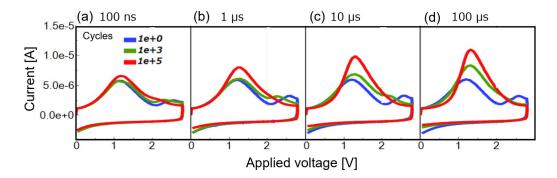

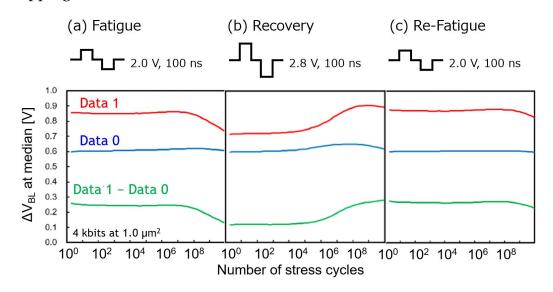

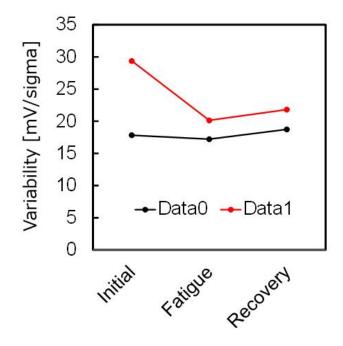

- 6.20 Measurement sequence during (a) Fatigue up to 10<sup>8</sup> cycles with a cycling stress voltage of 2.0 V and the pulse width of 100 ns (b) Recovery up to 10<sup>8</sup> cycles with a cycling stress voltage of 2.8 V and the pulse width of 100 ns, and (c) Re-fatigue up to 10<sup>8</sup> cycles with a cycling stress voltage of 2.0 V and the pulse width of 100 ns. PUND ranging from -2.4 to 2.4 V was applied to exclude the 2Pr without current peak split.

- 6.21 P-V curve and I-V curve obtained from PUND results during (a) Fatigue, (b) Recovery, and (c) Re-fatigue phases with 8 nm thick HZO at 1,000  $\mu$ m<sup>2</sup> area with 1,000 capacitors (1  $\mu$ m<sup>2</sup> each) connected in parallel. Positive bias was applied from top electrodes. PUND ranging from -2.4 to 2.4 V was applied to exclude the 2Pr without current peak split.

- 6.22Remanent polarization and  $E_{int}$  as a function of cycling stress<br/>during (a) Fatigue, (b) Recovery, and (c) Re-fatigue phases. 2Pr<br/>was extracted by PUND pulse subscribing dielectric contribution<br/>in the left vertical axis.  $E_{int}$  was extracted by a formula of<br/> $\frac{1}{2}(|Ecp|-|Ecn|)$  in the right vertical axis. The coercive fields were<br/>extracted from the voltage with peak current in Figure 6.21<br/>bottom I-V curves.90

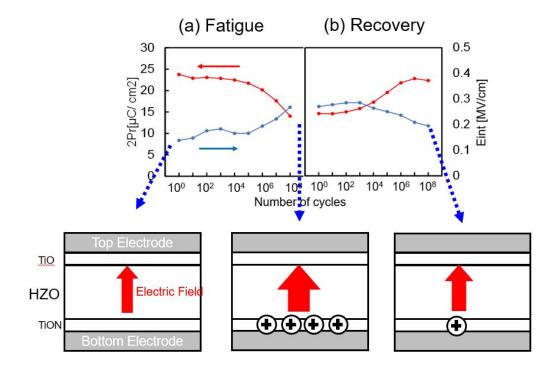

- 6.23 Schematic illustrations for E<sub>int</sub> shift during (a) fatigue and (b) recovery.

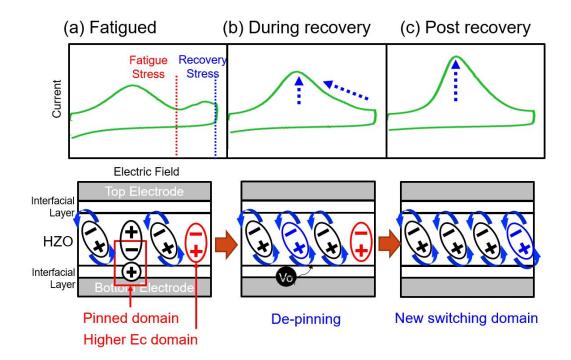

- 6.24 Recovery model during (a) fatigue, (b) recovery, and (c) furtherrecovery phases. I-V image extracted from Positive pulse in

|      | PUND sequence at upper row. Image of switching behavior of domains at bottom row.                                                                                                                                                                                                                                                                                                                                                      | 93  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

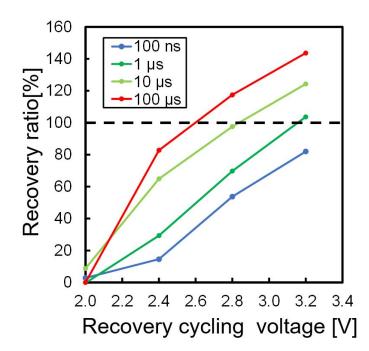

| 6.25 | Definition of the recovery ratio.                                                                                                                                                                                                                                                                                                                                                                                                      | 95  |

| 6.26 | Recovery ratio calculation as a function of recovery cycling voltage ranging from 2.0 to 3.4 V (step 0.4 V) with different pulse width of 100 ns, 1 $\mu$ s, 10 $\mu$ s and 100 $\mu$ s.                                                                                                                                                                                                                                               | 95  |

| 6.27 | Remanent polarization as a function of cycling number during (a) fatigue with different conditions as $3.2 \text{ V}$ with $100 \mu\text{s}$ in red and $2.0 \text{ V}$ with $100 n\text{s}$ in blue and (b) recovery at $3.2 \text{ V}$ with $100 \mu\text{s}$ .                                                                                                                                                                      | 96  |

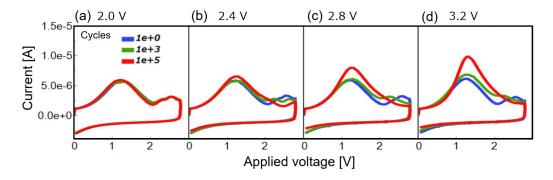

| 6.28 | I-V curve during recovery cycling post fatigue stress with a different voltage condition of (a) 2.0 V, (b) 2.4 V, (c) 2.8 V and (d) 3.2 V, respectively. Only positive pulse during PUND pulse subscribing was described for simplicity.                                                                                                                                                                                               | 98  |

| 6.29 | I-V curve during recovery cycling post fatigue stress with a pulse width condition of (a) 100 ns, (b) 1 $\mu$ s, (c) 10 $\mu$ s and (d) 100 $\mu$ s, respectively. Voltage of the pulses were fixed as 3.2 V among these conditions. Only positive pulse during PUND pulse subscribing was described for simplicity.                                                                                                                   | 98  |

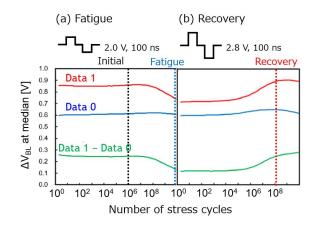

| 6.30 | (a) Fatigue test result for $10^{10}$ cycles under a stress voltage of 2.0 V at 10 MHz, (b) Recovery test result of $10^{10}$ cycles under a stress voltage of 2.8 V at 10 MHz, (c) Re-fatigue test results for $10^{10}$ cycles post recovery under the same stress condition as (a). Median value of $\Delta V_{BL}$ in 4 kbits 1T1C memory cells with 1.0 $\mu$ m <sup>2</sup> capacitor areas are extracted at each cycling phase. | 100 |

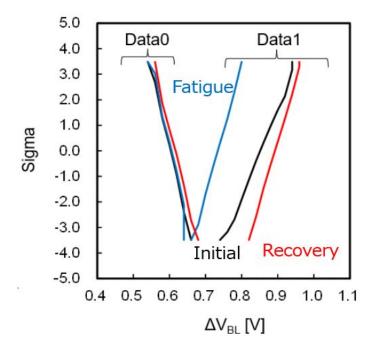

| 6.31 | Definition of a data which was extracted in Figure 6.32. post $10^6$ cycles and blue lines for $10^{10}$ cycles are extracted from Figure 6.30 (a). Red line shows a distribution post recovery stress at $10^8$ cycles extracted from Figure 6.30 (b).                                                                                                                                                                                | 101 |

| 6.32 | $\Delta V_{BL}$ distribution of data0 and data1 during endurance test.           |        |

|------|----------------------------------------------------------------------------------|--------|

|      | Black lines show an initial distribution, blue lines for $10^{10}$ cyc           | cles   |

|      | and red line shows a distribution post recovery stress.                          | 101    |

| 6.33 | Variability of $\Delta V_{BL}$ in 4 kbits of 1.0 $\mu m^2$ capacitor area during | Ş      |

|      | initial, fatigue and recovery phase.                                             | 102    |

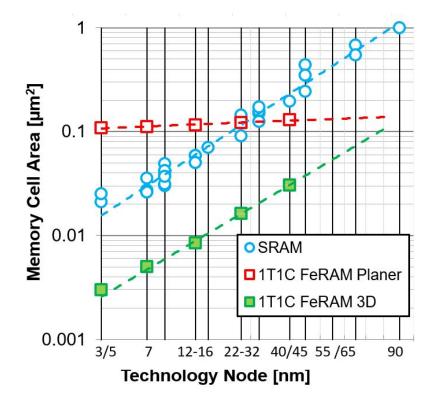

| 7.1  | Relationship between technology node and cell size. Blue lin                     | ie     |

|      | describes a trend of SRAM. Red line describes a that of 1T1C                     | ,      |

|      | FeRAM with planer type MFM structure and green line for 31                       | D      |

|      | MFM structure.                                                                   | 111    |

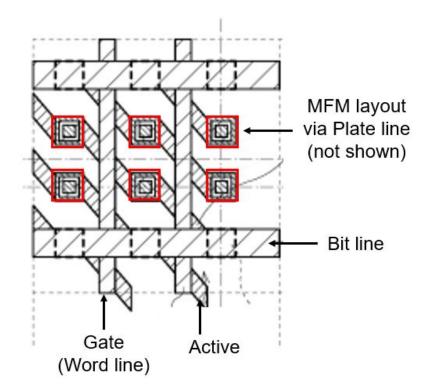

| 7.2  | Concept of memory cell layout design of 1T1C FeRAM for a                         |        |

|      | planer-type MFM structure.                                                       | 112    |

| 7.3  | Schematic illustration of capacitor under bitline structure (le                  | eft)   |

|      | and capacitor over bitline structure (right) for 3D cylinder MF                  | FM.113 |

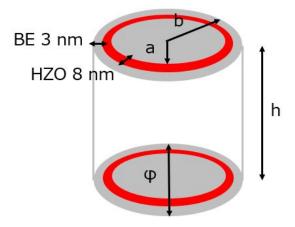

| 7.4  | Schematic illustration of 3D cylinder MFM for the capacitan                      | ce     |

|      | area calculation.                                                                | 115    |

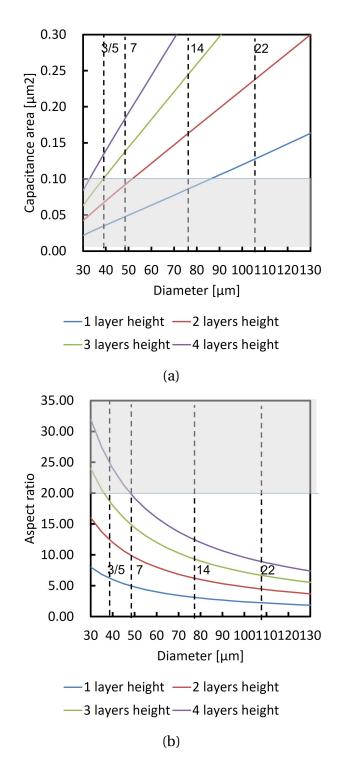

| 7.5  | Capacitor area dependence on the cylinder diameter (a) and                       | l      |

|      | aspect ratio dependence on cylinder diameter (b).                                | 116    |

| 7.6  | Schematic illustration of polarization vs. electrical field for                  |        |

|      | anti-ferroelectric material with same work function electrod                     | es     |

|      | among top and bottom electrodes in blue and different worl                       | κ.     |

|      | function in red.                                                                 | 118    |

#### Acknowledgements

First, I would like to express my sincere gratitude to Professor Hitosh Wakabayashi in Tokyo Institute of Technology for providing a great deal of advice and tremendous support. I would also like to thank Professor Kazuo Tsutsui, Professor Hiroshi Funakubo, Associate Professor Masahiro Watanabe, Associate Professor Shunichiro Ohmi and Associate Professor Kuniyuki Kakushima for valuable comments and helpful discussions.

I would like to express my gratitude to Mr. Taku Umebayashi and Mr. Masanori Tsukamoto of Sony Semiconductor Solutions Corporation for their management and encouragements of this study.

I would like to thank Mr. Tsubasa Yonai, Mr. Kenta Konishi, Dr. Yusuke Shuto, Mr. Takafumi Kunihiro and Mr. Fumitaka Sugata of Sony Semiconductor Solutions Corporation for ongoing discussions and advices throughout our team work on FeRAM.

I would like to express my gratitude to Professor Thomas Mikolajick, Dr. Uwe Schroeder, Dr. Monica Materano and Dr. Ruben Alcala of NaMLab GmbH for providing me valuable comments about ferroelectric material and experiment.

I would like to express my gratitude to Dr. Konrad Seidel, Dr. Tarek Ali, Dr. Maximilian Lederer of Fraunhofer IPMS for providing me practical solution about process integration of FeRAM.

Finally, I would like to express my gratitude to my wife, Shoko Okuno, for her great support for everything and my daughter, Lei Okuno, for her constant "yell" to me.

#### ABSTRACT

# 1T1C FeRAM memory array with $Hf_{0.5}Zr_{0.5}O_2$ -based ferroelectric film

#### Jun Okuno

Since the ferroelectric  $Hf_{0.5}Zr_{0.5}O_2$ -based material was reported in 2011, there has been much discussion about its application to 1T1C FeRAM. However, the feasibility of practical memory array operation using practical 1T1C memory cell structures has never been discussed. In this thesis, a novel 64 kbits of  $Hf_{0.5}Zr_{0.5}O_2$ -based 1T1C FeRAM memory array with dedicated CMOS logic circuit was integrated into 130 nm CMOS technology node and demonstrated the memory array operation for the first time. As a result, perfect functionalities in 64 kbits arrays and array operation at 2.0 V with sub 10 ns were demonstrated using 8 nm thick Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>. The memory window dependence on the ferroelectric capacitance area revealed that this technology has the potential for future scaling to capacitor areas of 0.1  $\mu m^2$ toward 40 nm CMOS technology node. Cycling tolerance of hard breakdown of the 1T1C FeRAM memory array was investigated, revealing the 1 ppm Raw-Bit-Error-Rate at 2.0 V, 100 ns, and 85°C operation was predicted to be >  $10^{15}$  cycles, based on the dependence of time to breakdown on the stress voltage. Considering a degradation of the remanent polarization due to a fatigue, the memory window was decreased post 10<sup>8</sup> cycles. This degradation can be recovered by applying higher stress cycling on the MFM with keeping the distribution of memory window. These results should encourage the mass production of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>-based 1T1C FeRAM, which has been at the research level until now.

## 1 Introduction

#### 1.1 Background

An edge computing architecture has been gaining attention in recent years due to its low latency, low data transaction, and high security communications compared to a cloud computing architecture<sup>18–20</sup>. In the edge computing, huge amount of calculation for inference of image, speech and language is required at distributed internet-of-things (IoT) edge devices illustrated in Figure 1.1. For applications where it is difficult to secure a power supply or replace batteries, low-power consumption and small-footprint edge IoT devices are desired (Figure 1.2). Such edge IoT devices use various types of memory, such as static random access memory (SRAM), dynamic random access memory (DRAM), and NAND FLASH memory, which serve as a storage or working memory. Therefore ultra-low-power and small-footprint memories are strongly desired.

Figure 1.1. Illustration of cloud computing and edge computing architectures.

Figure 1.2. Use case of the edge IoT device application<sup>4</sup>.

Figure 1.3 is illustrating a hierarchical structure of memory showing trade-off between capacity and latency. Because of the trade-off between capacity and latency, memory system needs to be divided according to the application. SRAM is commonly used for the highest speed application near Central Processing Unit (CPU) such as register, layer 1 cache (L1) to last level cache (LL). It has an advantage of high speed operation, but requires large footprint because a memory cell consists of more than 5 transistors. Since SRAM is a volatile memory, it has the problem that standby leakage increases power consumption. NAND flash memory is widely used as a storage memory because of its high density and non-volatility, although it operates at low speed. It requires high voltage (> 10 V) to store the data, resulting in large energy consumption during write operation. DRAM is used as primary working memory to bridge the performance gap between SRAM and NAND FLASH. Since it is volatile memory, it requires refresh operations at regular intervals (once every 64 ms), which increases power consumption. Since different memories are used for different purposes, the problem is that a lot of power consumption is generated during data transfer between memories. Therefore, embedded memory that replaces all or part of the memory system is desired to reduce power consumption.

Figure 1.3. Hierarchical structure of memory showing trade-off between capacity and latency.

Table 1.1 is a comparison table of performance in embedded memories. Although several emerging or emerged memories such as embedded flash memory (eFlash), resistive Random Access Memory (RRAM), spin torque transfer magnetic RAM (STT-MRAM) and perovskite-based ferroelectric RAM (barium titanate (BaTiO<sub>3</sub>)<sup>21</sup> and later in lead zirconate titanate (PZT)<sup>22</sup>, have been suggested to achieve the replacement, but no one accomplish it due to limitation of write energy, endurance and scaling resulting from high process cost caused by complex structures.

|               | SRAM      | eDRAM              | eFlash            | eRRAM             | STT MRAM        | Perovskite-              |

|---------------|-----------|--------------------|-------------------|-------------------|-----------------|--------------------------|

|               |           |                    |                   |                   |                 | FeRAM                    |

|               |           |                    |                   |                   |                 | -                        |

| Non-volatile  | No        | No                 | Yes               | Yes               | Yes             | Yes                      |

| Write voltage | > 0.5V    | $> 1.0 \mathrm{V}$ | $\sim 10  { m V}$ | $2\sim 3~V$       | 2 V             | $> 1.5 \mathrm{V}$       |

| Write speed   | < 1 ns    | $20 \sim 100 \ ns$ | $\sim 10\mu s$    | $1\sim 100~\mu s$ | 10 ns           | $10 \sim 100 \text{ ns}$ |

| Endurance     | $10^{16}$ | $10^{16}$          | $10^{5}$          | 106               | 10 <sup>9</sup> | $10^{15}$                |

| Energy        | Standby   | Dynamic            | High              | High              | High            | Low                      |

|               | leak      | refresh            |                   |                   |                 |                          |

| Scaling       | 5/7 nm    | 28 nm              | 28 nm             | 40 nm             | < 22 nm         | 180 nm                   |

|               |           |                    | discontinued      | discontinued      |                 | discontinued             |

Table 1.1. Comparison table of performance in embedded memories.

#### 1.2 Ferroelectricity of hafnium-oxide-based material

The ferroelectricity of hafnium silicon oxides (HfSiO<sub>2</sub>) was first reported in  $2011^{23}$ , showing the presence of a polar orthorhombic phase in HfSiO<sub>2</sub> thin films that contributes to their ferroelectricity. Compared to conventional perovskite ferroelectric materials, HfO<sub>2</sub>-based ferroelectric materials have the advantages that they can be deposited by an atomic layer deposition (ALD) method and have better compatibility with CMOS processes since HfO<sub>2</sub> is widely used in front-end processes. This advantages indicates that HfO<sub>2</sub>-based ferroelectric materials have potential for application in state-of-the-art CMOS technology nodes.

$HfO_2$  exhibits ferroelectricity due to an appearance of the polar orthorhombic  $Pca2_1$  phase group, which didn't exist in the conventional classical phase diagram as described in Figure 1.4. In this lattice configuration, the oxygen atoms can take two equilibrium positions corresponding to the two opposite directions of polarization. When an external electric field is applied, oxygen atoms move from one equilibrium position to another by polarization switching.

Figure 1.4. Schematic diagram of a  $Pca2_1$  unit cell corresponding to polar-orthorhombic phase with two opposite polarization directions in hafnium oxide. Picture was taken with permission<sup>5</sup>.

Figure 1.5 shows a polarization (P) vs. electric field (E) for the typical ferroelectric behavior. The electric dipole on the surface of a ferroelectric material is called "spontaneous polarization" because the centers of gravity changes to positive or negative spontaneously. The direction of spontaneous polarization is reversed when an external electric field is applied. The value of the polarization remaining on the surface at the absences of external electric field is called "remanent polarization (Pr)" and the value of the electric field when the polarization reverses is called the "coercive field (Ec)". When a sufficiently strong electric field is applied, all mobile charge is transferred to the surface. This is called the saturated state, and the value of polarization at this time is called the "saturation polarization value (Ps)". All of these parameters have a polarity of positive or negative.

Table 1.2 shows ferroelectric properties of  $Hf_{0.5}Zr_{0.5}O_2$  comparing with another ferroelectric materials. The Pr and Ec of  $Hf_{0.5}Zr_{0.5}O_2$  have been reported to be competitive with other materials.

Figure 1.5. Polarization vs. electric field for ferroelectric behavior.

|  | Table 1.2. | Comparison | table of ferro | electric pro | perties $^{1,2}$ . |

|--|------------|------------|----------------|--------------|--------------------|

|--|------------|------------|----------------|--------------|--------------------|

|                          | PZT        | SBT           | AlScN         | $Hf_{0.5}Zr_{0.5}O_2$ |

|--------------------------|------------|---------------|---------------|-----------------------|

| Pr [µC/cm <sup>2</sup> ] | $40\sim90$ | $10 \sim 20$  | $80 \sim 140$ | $30 \sim 60$          |

| Ec [MV/cm]               | 0.05       | $\sim 0.05$   | $2\sim 5$     | $0.8\sim 2$           |

| k                        | 1300       | $150\sim 250$ | $\sim 25$     | $\sim 30$             |

#### 1.3 Application of hafnium-oxide-based ferroelectric material

In past two decades, ferroelectric memory application based on  $Hf_{0.5}Zr_{0.5}O_2$ have been extensively discussed for their low switching current due to the polarization switching, their compatibility with the CMOS process, and their scaling potential as described in Figure 1.6. Table 1.3 shows a performance comparison table between three typical  $Hf_{0.5}Zr_{0.5}O_2$ -based memory application such as ferroelectric field effect transistors (FeFETs)<sup>24</sup>, ferroelectric tunnel junctions (FTJs)<sup>25,26</sup>, and one-transistor and one-capacitor ferroelectric random access memories (1T1C FeRAMs)<sup>27</sup>.

FeFETs are capable of non-destructive read schme and multi-bit write operations and are suitable for higher density devices. However, the dielectric film formed between the ferroelectric gate oxide film and the Si interface can cause charge trapping and degradation of reliability and variability of the characteristics. Several studies have been conducted to address these issues. The choice of a back-gate FeFET structure with a channel-last process flow can achieve the higher endurance behavior<sup>28</sup>.

FTJs have been proposed as two-terminal resistance-change devices with a ferroelectric layer and an interface layer between two metal electrodes. The device has advantages of nondestructive readout with high density, and proposed as potential applications in neuromorphic computing devices. The retention properties due to depolarizing magnetic fields are controversial. To overcome this challenge, optimization of the film stack and operating voltage has been proposed<sup>25</sup>.

1T1C FeRAM has an excellent interface layer between the metal electrode and the ferroelectric layer, which enables high endurance, low operating voltage, and disordered operation despite destructive readout operation. However, from the discovery of ferroelectric  $Hf_{0.5}Zr_{0.5}O_2$ , FeFETs attracted much attention owing to single transistor structure. On the other hand, the development of 1T1C FeRAM

has been delayed from FeFETs due to the complexity of the process to form integrated capacitors and the need for a dedicated circuit to identify minute capacitance changes and read them out destructively. Therefore, research has been limited to basic evaluation using the MFM structure.

Figure 1.6. Chronology of semiconductor ferroelectric science and industry discoveries and advances since first reported. Picture is adapted from work<sup>6</sup>.

|                        | FeFET <sup>28</sup> | FTJ <sup>25</sup> | 1T1C-<br>FeRAM <sup>29</sup> |

|------------------------|---------------------|-------------------|------------------------------|

| Non-destructive read   | Yes                 | Yes               | No                           |

| 2-terminal stucture    | No                  | Yes               | No                           |

| Write Voltage (< 2 V)  | No                  | No                | Yes                          |

| Endurance $(> 10^6)$   | No                  | No                | Yes                          |

| Memory array operation | Yes                 | No                | This thesis                  |

Table 1.3. Comparison table of performance in  $Hf_{0.5}Zr_{0.5}O_2$ -based memory devices<sup>1</sup>.

#### 1.4 Challenges of conventional methods

There have been many reports on fundamental properties of  $Hf_{0.5}Zr_{0.5}O_2$ -based materials toward 1T1C FeRAM application. In a conventional method, a large area (larger than 100  $\mu$ m<sup>2</sup>) of metal/ferroelectric/metal(MFM) capacitor has been commonly used to amplify small displacement currents as shown in Figure 1.7. However, following matters remains controversial.

- (1) CMOS process compatibility

- (2) Ferroelectric properties under practical use case (< 100 kHz)

- (3) Uniformity of ferroelectric properties at realistic MFM size.

- (4) Reliability of small MFM capacitors

First, integration process of MFM is needed to be optimized according to the CMOS process. In particular, the thermal budget is limited depending on the CMOS process, so material optimization is necessary. Second, large capacitor causes large RC delays during measurement and cannot apply ideal pulses shape, which limits their operating speed. It has been reported that this issue can be solved by extrapolating from the frequency dependence of lower than 100 kHz<sup>30</sup>, but for a more realistic study, direct measurements around 100 MHz are desired. Third, it is essential for 1T1C FeRAM to be able to separate high and low states even at several megabits, so it is important to investigate the capacitance variation of both states in a realistic MFM structure. Finally, reliability of ferroelectricity of realistic MFM capacitors using memory array under practical use case is inevitable for the feasibility study of 1T1C FeRAM application. Recently, process integration of memory arrays with realistic MFM structures with 110 nm CMOS technology node has been reported<sup>29</sup>. However, memory array operation using dedicated circuits such as address decoders and sense amplifiers (SA) in Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>-based 1T1C FeRAM under actual use conditions has never been reported.

Figure 1.7. Illustration of a conventional test structure for MFM with larger than 100  $\mu m^2.$

#### 1.5 Motivation of this thesis

In this thesis, a feasibility study of 1T1C FeRAM with  $Hf_{0.5}Zr_{0.5}O_2$ -based ferroelectric film was experimentally performed to address challenges as mentioned in Section 1.4. First,  $Hf_{0.5}Zr_{0.5}O_2$ -based ferroelectric film was developed for integrating it into 130 nm CMOS technology node considering the thermal budget in Chapter 2. Second, a novel 64 kbits 1T1C FeRAM memory array with small MFM capacitors (0.4 µm<sup>2</sup>) based on  $Hf_{0.5}Zr_{0.5}O_2$  film using a dedicated CMOS logic circuit was integrated into 130 nm CMOS technology in Chapter 3, and memory array performance was investigated to verify the ferroelectric properties under practical use case (100 kHz) in Chapter 4. Third, memory window analysis using the 1T1C FeRAM memory array was studied to reveal a variability of ferroelectricity of small MFM capacitors and predict the scalability toward more advanced CMOS technology in Chapter 5. Finally, film thickness scaling to reduce operating voltage and improve cycling tolerance for hard breakdown was studied and a recovery effect from the fatigue was comprehensively investigated by applying various operating condition to verify the reliability of small MFM capacitors.

The target performance was defined as shown in Table 1.4, taking other technologies into account. This thesis focuses on  $Hf_{0.5}Zr_{0.5}O_2$ -based 1T1C FeRAM as a slow SRAM replacement for ultra-low power and small area embedded memory as shown in Figure 1.3. The target of write voltage was defined to be around 2.0 V, assuming a 40nm CMOS technology node as the first stage of scaling. Aiming for a speed between SRAM and DRAM, the target of write speed was set at about 20 ns. Since high endurance was required for low-speed SRAM replacement, the target of write endurance was set to more than  $10^{15}$  cycles. No any other technologies, such as conventional FeRAM and  $Hf_{0.5}Zr_{0.5}O_2$ -based FeFET have never achieved these targets.  $Hf_{0.5}Zr_{0.5}O_2$ -based 1T1C FeRAM is included for reference, but as mentioned in Section 1.3, it is not the result based on memory array operation. To accomplish this targets, a 64 kbits of 1T1C FeRAM with  $Hf_{0.5}Zr_{0.5}O_2$ -based ferroelectric film was fabricated with dedicated CMOS logic circuits to demonstrate its memory array operation for the first time.

|               | SRAM               | eDRAM              | perovskite-      | Hf <sub>0.5</sub> Zr <sub>0.5</sub> O <sub>2</sub> | - Hf <sub>0.5</sub> Zr <sub>0.5</sub> O <sub>2</sub> - | Target         |

|---------------|--------------------|--------------------|------------------|----------------------------------------------------|--------------------------------------------------------|----------------|

|               |                    |                    | based            | based                                              | based                                                  |                |

|               |                    |                    | FeRAM            | FeFET <sup>24</sup>                                | 1T1C                                                   |                |

|               |                    |                    |                  |                                                    | FeRAM <sup>29</sup>                                    |                |

| Non-volatile  | No                 | No                 | Yes              | Yes                                                | Yes                                                    | Yes            |

| Write voltage | $> 0.5 \mathrm{V}$ | $> 1.0 \mathrm{V}$ | 1.0 V            | 4.2 V                                              | 4.0 V                                                  | $\sim$ 2.0 V   |

| Write speed   | < 1 ns             | $\sim$ 20 ns       | 20 ns            | 20 ns                                              | 100 ns                                                 | $\sim 10 \ ns$ |

| Endurance     | $10^{16}$          | $10^{16}$          | 10 <sup>15</sup> | $\sim 10^5$                                        | 10 <sup>11</sup>                                       | $\sim 10^{15}$ |

| Retention     | Volatile           | Volatile           | 125°C            | no data                                            | 125°C                                                  | 85°C           |

|               |                    |                    | 10 years         |                                                    | $10^4$ sec                                             | 100 min        |

| Scalability   | 5/7 nm             | 28 nm              | 180 nm           | 28 nm                                              | No data                                                | =< 40 nm       |

Table 1.4. Target performance comparing with another technology.

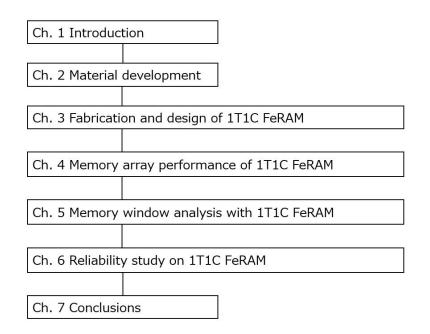

#### 1.6 Structure of this thesis

In this thesis, feasibility study of  $Hf_{0.5}Zr_{0.5}O_2$ -based 1T1C FeRAM was experimentally performed for the first time. Figure 1.8 explains the structure of this thesis. In Chapter 1, a target characteristics is defined comparing other emerging technologies. In Chapter 2, materials used in the 1T1C FeRAM are mentioned. In Chapter 3, experimental of the process integration and design of  $Hf_{0.5}Zr_{0.5}O_2$ -based 1T1C FeRAMs are mentioned. In Chapter 4, a memory array operation of  $Hf_{0.5}Zr_{0.5}O_2$ -based 1T1C FeRAM are discussed . In Chapter 5, an improvement to reduce the operation voltage is conducted by film thickness scaling of the ferroelectric layer using 1T1C FeRAM. In Chapter 6, the fatigue characteristics of the HZO based 1T1C FeRAM memory array, which has never been addressed before is discussed. In Chapter 7, all results on this thesis are summarized and matters which are not covered in this thesis are mentioned.

Figure 1.8. Structure of this thesis.

## 2 Material development

#### 2.1 Introduction

This chapter mentions about ferroelectric materials which was used for 1T1C FeRAM. To obtain ferroelectricity in  $Hf_{0.5}Zr_{0.5}O_2$ -based materials, appropriate thermal budget is required to crystallize the film. Since process conditions depend on dopants, thickness, and materials for the bottom and top electrodes, it is important to select dopants and check their thermal stability when incorporating them into conventional CMOS process flows. In this thesis, an intrinsic material properties were developed using a single large MFM capacitors prior to install them into a 1T1C FeRAMs. In Section 2.2, a selection of the dopant and optimization method for the  $Hf_{0.5}Zr_{0.5}O_2$ -based materials are described. In Section 2.3, the thermal stability emulating the thermal budget in CMOS process are mentioned including the intrinsic reliability.

#### 2.2 Material selection for ferroelectric films

In the past decade, ferroelectricity has been reported in HfO<sub>2</sub> thin films doped with many different elements<sup>31</sup> and ZrO<sub>2</sub><sup>14,32</sup>. Even un-doped HfO<sub>2</sub> is known to emerge ferroelectricity<sup>33</sup>. Unlike other dopant species, Zr substitutes Hf atoms in large amounts. In this case, the term "solid solution" is more appropriate than "doping". Since both Zr and Hf are IV-valent elements with identical atomic radius, they are often classified as "sister substances". One of the major advantages

of using Zr as a dopant of Hf is that it has wider concentration window to obtain ferroelectric properties with more flexible process<sup>7,34</sup>. Furthermore, its low thermal budget process allows to fabricate the ferroelectric material by compatible process with well developed knowledge from DRAM<sup>35</sup>. Therefore, HZO layers are widely studied in ferroelectric device applications.

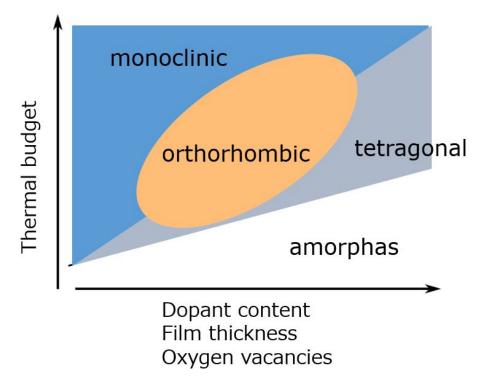

Various factors contributes to the stabilization of the metastable polar orthorhombic phase such as surface and volume effects<sup>7</sup>, dopant atom incorporation, the presence of oxygen vacancies<sup>8,9</sup>, and mechanical stress<sup>10–12</sup>, and rapid cooling<sup>13</sup> as described in Figure 2.1. The layers appear to transition from the monoclinic phase to the polar orthorhombic phase and then to the tetragonal phase with increasing content. Previous studies have obtained the dependence of the remanent polarization values as a function of concentration, finding a peak around a Hf:Zr ratio of 1:1, indicating that the orthorhombic phase is most sufficiently detected <sup>14,34,36</sup>. Therefore, this work focuses on the characterization of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> films.

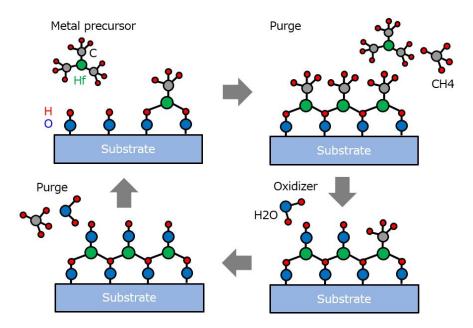

Figure 2.1. Schematic illustration of crystal phase of ferroelectric HZO.  $^{7\text{--}13}$

There is a lot of methods to fabricate the ferroelectric layer such as atomic layer deposition (ALD), physical vapor deposition (PVD)<sup>37</sup>, chemical vapor deposition (CVD)<sup>38</sup>, pulsed layer deposition (PLD)<sup>39</sup>. chemical solution deposition (CSD)<sup>40</sup>. However ALD is the most widely used for the ferroelectric layers since its monoatomic-layer deposition is suitable to deposit thin films with good uniformity and excellent step coverage. The ALD cycle consists of two self-limiting processes in Figure 2.2. First, when metal precursors are pulsed into the surface, then they are absorbed on the available sites of the substrate with a mono-atomic-layer. Next, the oxidizer such as H<sub>2</sub>O, O<sub>2</sub> and O<sub>3</sub> are then also introduced into the chamber reacting with the absorbed metal precursor molecules and creates mono-atomic-layer. It reacts with the absorbed metal precursor molecules to form a sub-mono-atomic-layer of metal oxide. In between these two steps, purging is performed to remove un-reacted molecules and byproducts. If theses precursor reaction and purging process are not optimized correctly, residual reactants can affect the quality and homogeneity of the layer.

Figure 2.2. Schematic illustration of an ALD cycle.

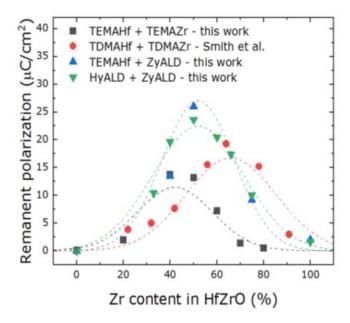

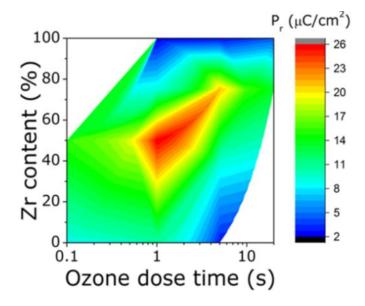

Since impurities, thermal stability, and dense layers depend on molecules in precursors, the choice of precursor is important to obtain high residual polarization. Figure 2.3 shows a remanent polarization as a function of Zr content in HZO for a different metal precursors, TEMA-Hf (Zr) (Hf[N(CH<sub>2</sub>)(C<sub>2</sub>H<sub>5</sub>)], Zr[N(CH<sub>3</sub>)(C<sub>2</sub>H<sub>5</sub>)]), TDMA-Hf (Zr) (Hf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>), Zr[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>)), cyclopentane (Cp)-based precursors (Zr-yALD, Hf-yALD). As a result, the largest remanent polarization is obtained by TEMAHf + ZyALD combination. The reason for this could be that ZyALD has high thermal stability because it belongs to the Cp group. Therefore, the precursor molecules are transported to the active surface of the substrate surface without dissociation even at film deposition temperatures, resulting in homogeneous Cp desorption and oxidation reactions. In addition, the residue of carbon-based reaction products generated by other organic precursors is less likely to be generated, which is said to reduce leakage paths in the film and provide good film quality.<sup>41,42</sup>

Process condition of the oxidizer is an important parameter that fluctuates the amount of oxygen deficiency in the film as described in Figure 2.1. Figure 2.4 shows a Contour plots report which is depicting the amount of each crystalline phase (m-phase, polar o-phase, and t-phase) as a function of ozone exposure time (x-axis) and Zr content (y-axis). The amount of the crystalline phase is calculated from the de-convolution of the measured grazing incidence X-ray diffraction (GIXRD) signals using TEMAHf + ZyALD precursors.

Therefore, TEMAHf + ZyALD precursors were chosen as precursors to deposit  $Hf_{0.5}Zr_{0.5}O_2$  layers films and the condition of oxidizer were optimized.

Figure 2.3. Remanent polarization as a function of the Zr content in the film for different Hf- and Zr-based precursor combinations<sup>14–16</sup>. Picture was taken with permission<sup>14</sup>.

Figure 2.4. Contour plots for a remanent polarization as a function of Zr content and ozone dose time<sup>14–16</sup>. Picture was taken with permission<sup>14</sup>.

#### 2.3 Thermal stability of the ferroelectric material

Large round MFM capacitors with a diameter of 100 µm were fabricated to investigate the ferroelectric characteristics dependence on the Rapid Thermal Anneal (RTA) temperature. Both 10 nm thick TiN electrodes were sputtered using PVD method. Different RTA temperatures of 450°C and 500°C were used to crystallize the MFM capacitors. 450°C for 30 s and 500°C for 30 s were performed, and control samples without RTA treatment were also processed. The existence of polarorthorhombic ferroelectric phase in large MFM capacitors of 100 µm diameter was investigated by grazing incidence X-ray diffraction (GIXRD). Figure 2.5 shows the GIXRD data for all three variations; the highest intensity was observed when annealing was performed at 500°C for 30 seconds, but no significant intensity was detected when no RTA was performed. This indicates that the films can be crystallized by annealing at a temperature of at least 450°C in this experiment. The remanent polarization of these capacitors with RTA at 450 and 500°C was characterized by polarization versus voltage measurements, as shown in Figure 2.6. Ferroelectric hysteresis behavior due to the ferroelectric polar-orthorhombic phase was obtained for both samples, with the sample annealed at 450°C showing lower remanent polarization than the sample annealed at 500°C (2Pr, 40  $\mu$ C/cm<sup>2</sup>). This indicates a greater proportion of ferroelectric orthorhombic crystals in the sample annealed at 500°C, as shown in the GIXRD results in Figure 2.5.

Figure 2.5. GIXRD spectrum of the TiN/HZO/TiN stack annealed at 450°C, 500°C and without annealing.

As shown in Figure 2.7, the cycling endurance performance was investigated up to  $10^9$  cycles with a cycle frequency of 100 kHz and a rectangular pulse shape. For the sample RTA at 500°C, stable residual polarization is observed up to  $10^9$  cycles, after which the capacitor begins to fatigue. Considering the difference from the frequency in actual use conditions (10 MHz), the cycle durability of  $10^9$  measured at 100 kHz is expected to be equivalent to  $10^{11}$  cycles at 10 MHz if the durability characteristics correspond to the accumulated stress energy. Figure 2.8 shows retention tests of the same state (SS) and opposite state (OS) measured on samples subjected to RTA at  $500^{\circ}$ C<sup>32</sup>. A smaller change in polarization was observed at  $500^{\circ}$ C than at  $450^{\circ}$ C during 1000 min at  $85^{\circ}$ C. The retention result at  $500^{\circ}$ C can be projected to result in a slight degradation, even after 10 years applying a fitting model of power-law for the result above 10 min, considering charge trapping and the migration<sup>17,43</sup>.

Figure 2.6. Polarization vs voltage hysteresis of the MFM capacitors after RTA at 450 and 500°C and for 30 s after 100 cycles at 1 kHz. The bottom electrode was fixed to ground and the applied voltage of the top electrode was swept.

Figure 2.7. Cycling tolerance of the MFM capacitors after RTA at 450 and 500°C for 30 s. Cycling tolerance for 3 V amplitude at 100 kHz up to  $10^9$  cycles. Inset Figure shows the pulse shape.

Figure 2.8. Data retention up to 1000 min baking time at 85°C for the same state (SS) and the opposite state (OS) after RTA at (a) 450°C for 30 s and (b) 500°C for 30 s. The lines are prediction to 10 years using fitting model of previous report<sup>17</sup>.

#### 2.4 Summary

$Hf_{0.5}Zr_{0.5}O_2$  was chosen as a ferroelectric material from large concentration window and CMOS compatibility point of view. TEMAHf + ZyALD precursors materials as precursors to deposit  $Hf_{0.5}Zr_{0.5}O_2$  films and the condition of oxidizer were optimized to obtain higher remanent polarization. The reason for this could be that ZyALD has high thermal stability because it belongs to the Cp group. Therefore, the precursor molecules are transported to the active surface of the substrate surface without dissociation even at film deposition temperatures, resulting in homogeneous Cp desorption and oxidation reactions. In addition, the residue of carbonbased reaction products generated by other organic precursors is less likely to be generated, which is said to reduce leakage paths in the film and provide good film quality.

The impact of the RTA temperature on the ferroelectricity was investigated using single large capacitors. Higher remanent polarization and better endurance for RTA at temperatures up to 500°C were demonstrated. This thermal budget is applicable for 1T1C FeRAM process with a capacitor under bit line structure. Cycling endurance on the single capacitor was projected to be more than 10<sup>11</sup> cycles considering accumulative energy. Retention characteristics on the single capacitor was projected to be more than 10 years at 85°C.

# 3 Fabrication and design of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>-based 1T1C FeRAM

#### 3.1 Introduction

This chapter mentions about experimental and design of 1T1C FeRAM with  $Hf_{0.5}Zr_{0.5}O_2$ -based ferroelectric film. A 64 kbits of 1T1C FeRAM with  $Hf_{0.5}Zr_{0.5}O_2$ -based ferroelectric film was fabricated with dedicated CMOS logic circuits to demonstrate its memory array operation for the first time. As described in Chapter 1, the conventional characterization method using a large capacitance MFM capacitor (larger than 100  $\mu$ m<sup>2</sup>) is difficult to read and write the state of the ferroelectric capacitor in the order of 100 ns due to the RC delay. To address the issue, practical size of MFM capacitors (smaller than 1  $\mu$ m<sup>2</sup>) was fabricated to avoid the RC delay, and dedicated sense amplifier (SA) was design to detect the small capacitance change derived from the small capacitor.

As mentioned in Chapter 2, since ferroelectric  $Hf_{0.5}Zr_{0.5}O_2$  requires appropriate thermal budget to obtain ferroelectricity, capacitor under bitline structures are selected to avoid a degradation of back-end-of-line process. In Section 3.2, the concept was described followed by the process flow in Section 3.3. In Section 3.4, design for the 1T1C FeRAM is described which is mainly focus on the read scheme to overcome a destructive read operation of the 1T1C FeRAM. In Section 3.5, the thermal stability of the characteristics of the CMOS transistor suffering from the RTA temperature was confirmed by electrical measurements.

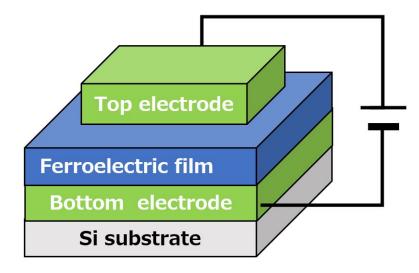

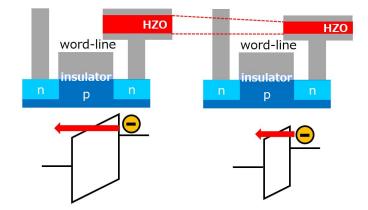

#### 3.2 Capacitor under bitline structure

There are mainly two MFM structures, capacitor under bit line (CUB) and capacitor over bitline (COB) described in Figure 3.1. In the case of CUB structure the MFM capacitors are fabricated prior to the back-end-of-line (BEOL) process as a middle-of-line (MOL), while MFM are located on top of the wiring layer of BEOL process for COB structure. The advantage of the COB structure is that the MFM is on the top layer, which allows for greater flexibility when creating a threedimensional MFM structure. While, CUB structure allows 1T1C FeRAM to avoid a degradation of BEOL wiring layers from thermal budget during crystallization anneal on metal/ferroelectric/metal (MFM).

Large area (> 1000  $\mu$ m<sup>2</sup>) MFM of ferroelectric materials. Most studies on doped Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> films employ high rapid thermal annealing (RTA) above 500°C to obtain large remanent polarization (2Pr > 40  $\mu$ C/cm<sup>2</sup>)<sup>31,44,45</sup>.However, high thermal budgets affect transistor performance and back-end-of-line (BEOL) reliability when incorporated into state-of-the-art CMOS manufacturing processes<sup>46</sup>, while high crystallization annealing temperatures contribute to higher density memory applications with capacitors with thinner ferroelectric layer, resulting in high remanent polarization.

To date, MFM capacitors made of TiN/HZO/TiN have been incorporated into the BEOL process with COB structure by applying temperatures below 450°C to avoid metal layer degradation, demonstrating the functionality of 1T1C FeRAM arrays without degrading CMOS characteristics<sup>29</sup>. In this work, we have applied the CUB structure to acquire larger remanent polarization by applying higher thermal budget over 450°C to the ferroelectric capacitors.

Figure 3.1. Schematic illustration of capacitor under bitline structure (left) and capacitor over bitline structure (right).

#### 3.3 Process flow

The ferroelectric material as described in Figure 2.2 was implemented in a 64 kbits one-transistor and one-capacitor (1T1C) FeRAM array fabricated in 130 nm CMOS technology. Figure 3.2 shows an optical micrograph of the test chip, showing the presence of four mats on the chip with MFM capacitor areas of 0.4, 0.6, 0.8 and  $1.0 \,\mu\text{m}^2$  in the 1T1C memory cells, respectively. Figure 3.3 shows a scanning electron microscope cross section of a 1T1C cell containing an MFM capacitor. The MFM capacitor, consisting of a TiN/HZO/TiN stack, is integrated directly on top of the transistor in the CUB structure and crystallized before the BEOL metal interconnect process at a maximum temperature of 500°C and a holding time of 30 s annealing was possible. A two-step etching process is used to protect the sides of the HZO film from processing damage (ion, electron, UV, etc.). Direct patterning process could allow to reduce a MFM capacitance area, but it is necessary to consider increased leakage current and mechanical stress fluctuations due to the etching damage.

Figure 3.2. Optical microscope image of the 64 kbits 1T1C FeRAM test chip.

Figure 3.3. Scanning Electron Microscope cross section of one 1T1C cell.