# T2R2 東京工業大学リサーチリポジトリ

## Tokyo Tech Research Repository

### 論文 / 著書情報 Article / Book Information

| 題目(和文)            | 標準CMOSプロセスとの整合性と高周波特性250GHz越のSiGe HBTを<br>有する0.18µm SiGe BiCMOSの研究                                                                                                                             |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Title(English)    | Study on 0.18 µm SiGe BiCMOS having compatibility with standard CMOS process and SiGe HBT with high frequency characteristics over 250 GHz                                                     |  |

| 著者(和文)            |                                                                                                                                                                                                |  |

| Author(English)   | Takashi Hashimoto                                                                                                                                                                              |  |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第12386号,<br>授与年月日:2023年3月26日,<br>学位の種別:課程博士,<br>審査員:筒井 一生,宮本 恭幸,若林 整,角嶋 邦之,大見 俊一郎                                                                        |  |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第12386号,<br>Conferred date:2023/3/26,<br>Degree Type:Course doctor,<br>Examiner:,,,, |  |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                           |  |

| Type(English)     | Doctoral Thesis                                                                                                                                                                                |  |

#### Doctoral dissertation

Study on 0.18 µm SiGe BiCMOS

having compatibility with standard CMOS process and SiGe HBT with high frequency characteristics over 250 GHz (標準 CMOS プロセスとの整合性と高周波特性 250GHz 越の SiGe HBT を有する 0.18μm SiGe BiCMOS の研究)

### March 2023

Department of Electrical and Electronic Engineering

School of Engineering at Tokyo Institute of Technology

Thesis supervisor: Prof. Kazuo Tsutsui

Takashi Hashimoto

## **Table of Contents**

| Background and Purpose of This Study                                                           | 1          |

|------------------------------------------------------------------------------------------------|------------|

| 1.1 Applications and Technical Challenges of BiCMOS and Bipolar Transistor Technologies        | 1          |

| 1.1.1 Application of Bipolar Transistor / BiCMOS Technology to Mainframe Computers             | 1          |

| 1.1.2 Challenges Relating to BiCMOS Technology Applied to the Communications Fields            | 2          |

| 1.1.3 Challenges Relating to Bipolar Transistors Applied to the Communications Fields          | 4          |

| 1.1.4 Positioning of Bipolar Transistors in the Trend Toward Higher CMOS Speeds                | 6          |

| 1.2 Overview of Conventional Techniques for Increasing the Frequency of Bipolar Transistors    | 7          |

| 1.3 Usefulness and Issues of Application of Thick-Layer SOI to BiCMOS for Analog Products      | 15         |

| 1.4 Purposes of This Study                                                                     | 17         |

| 1.5 References                                                                                 | 19         |

| 2. BiCMOS Maintaining Compatibility with Standard CMOS Processes                               | 24         |

| 2.1 Introduction                                                                               | 24         |

| 2.2 The 0.18 µm SiGe BiCMOS Process in This Study                                              |            |

| 2.2.1 Challenges in the 0.18 μm SiGe BiCMOS Process Technology                                 | 24         |

| 2.2.2 Overview of the 0.18 μm SiGe BiCMOS Process Technology Developed in This Study           | 26         |

| 2.3 Maintaining the Gate Pitch of Standard CMOS                                                | 30         |

| 2.4 Low-temperature H <sub>2</sub> Annealing to Prevent Boron Penetration from the P-type Gate | 32         |

| 2.4.1 Setting H <sub>2</sub> Annealing Conditions in the 0.25 μm Generation                    | 32         |

| 2.4.2 Lower-temperature H <sub>2</sub> Annealing in the 0.18 μm Generation                     | 35         |

| 2.5 Reducing Thermal Budget to Prevent Short-Channel Characteristics from Deteriorating        | 43         |

| 2.6 Confirmation of Scalability that Enables the Installation of 0.13μm CMOS in the BiCMOS     | 44         |

| 2.7 Conclusions                                                                                | 46         |

| 2.8 References                                                                                 | 47         |

| 3. Selective SiGe Epitaxial Growth Technology for Intrinsic Base Layer                         | 49         |

| 3.1 Introduction                                                                               | 49         |

| 3.2 Challenges in the SiGe Epitaxial Growth                                                    | 50         |

| 3.3 Ensuring Selectivity in the SiGe Epitaxial Growth                                          | <u></u> 52 |

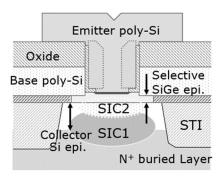

| 3.3.1 Overview of SiGe Epitaxial Growth Process that Realized the Self-aligned Structure       | 52         |

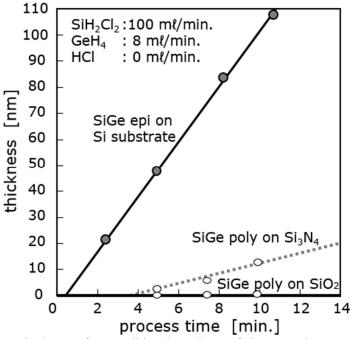

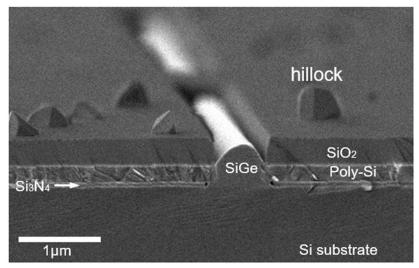

| 3.3.2 Selective SiGe Epitaxial Growth without HCl Gas Addition                                 | 52         |

| 3.3.3 Formation of Link Region in the Cavity under the Base Poly-Si Electrode                  | 55         |

| 3.4 Study on SiGe layer Specifications to Improve SiGe HBT Performance                         | 56         |

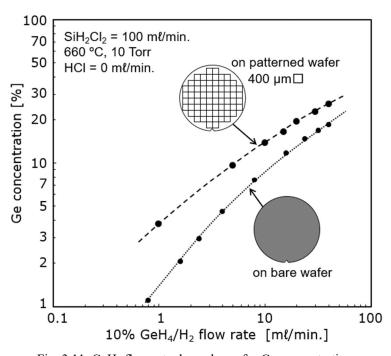

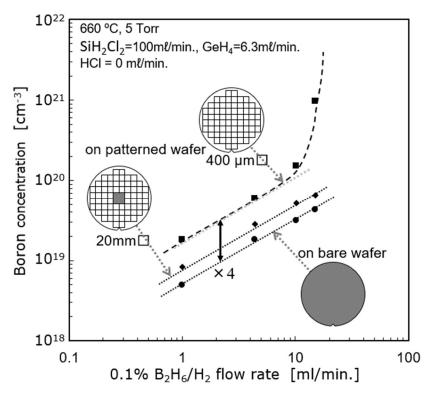

| 3.4.1 Concentration Increase of Ge and Boron in the SiGe Layer                                 | 56         |

| 3.4.2 Suppression of Boron Diffusion by Carbon Doping                                          |            |

| 3.5 Conclusions                                                                                |            |

| 3.6 References                                                                                 |            |

| 4. Study on Improvement of Frequency Characterization on SiGe HBTs                             |            |

| 4.1 Introduction                                                                        | 65  |

|-----------------------------------------------------------------------------------------|-----|

| 4.2 Items to be Addressed in SiGe HBT Speeds                                            | 65  |

| 4.3 Comparison of the intrinsic base profile and characteristics of Si BJT and SiGe HBT | 66  |

| 4.4 Typical SiGe HBT Specifications in This Study                                       | 67  |

| 4.5 Techniques for Higher Frequency as an Extension of Methods Used in Si BJTs          | 68  |

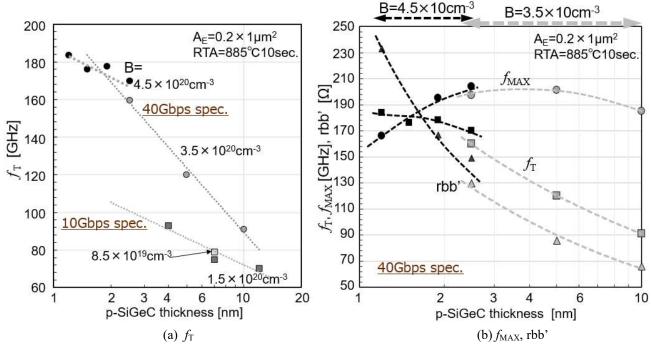

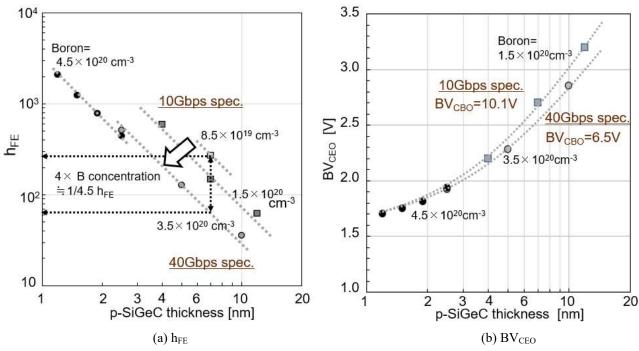

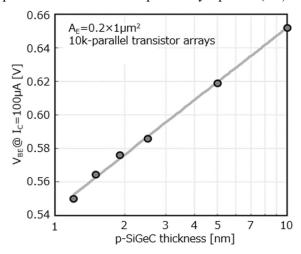

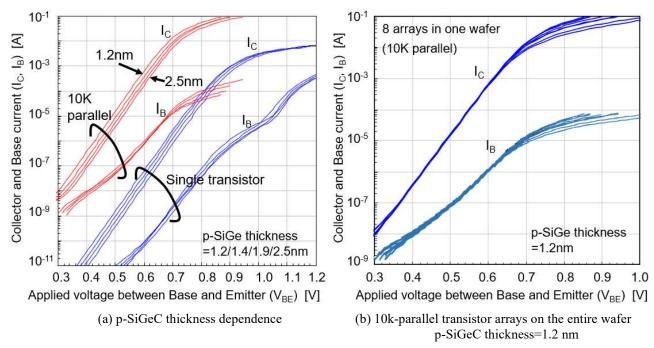

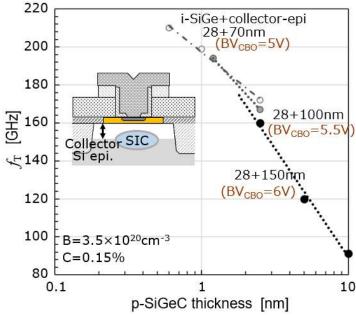

| 4.5.1 Thinning of the p-SiGeC Layer                                                     | 68  |

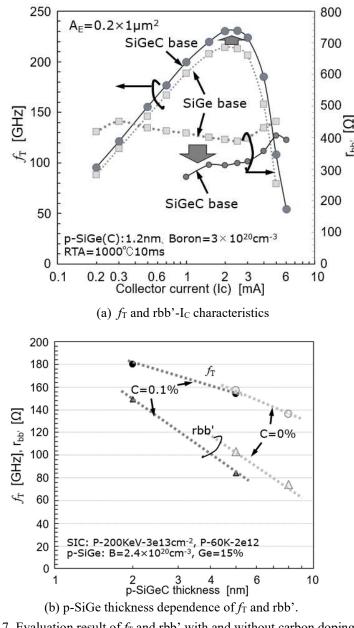

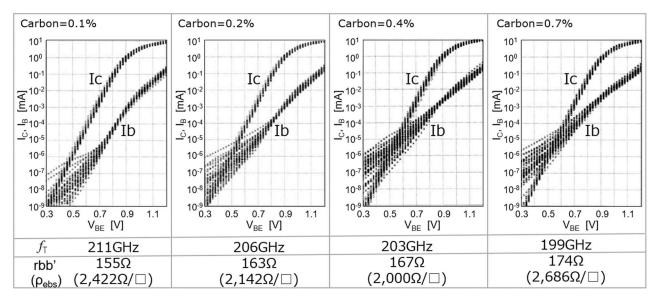

| 4.5.2 Suppression of Boron Diffusion by Carbon Doping                                   | 73  |

| 4.5.3 Increasing the Final Annealing Temperature                                        | 75  |

| 4.6 New initiatives for Higher Frequency Characteristics that Si BJTs did not Address   | 76  |

| 4.6.1 Optimization of Emitter-Base Depletion Layer Width                                | 76  |

| 4.6.2 Cap-Si/cap-SiGe Structure                                                         | 77  |

| 4.6.3 Effects of Step-type Ge Profiles on Device Characteristics                        | 78  |

| 4.7 Speeding up SiGe HBT by Suppressing Parasitic Characteristics                       | 81  |

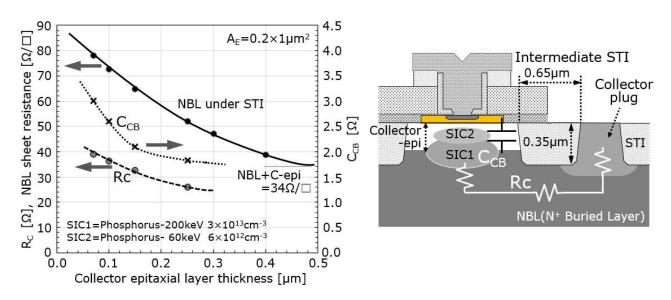

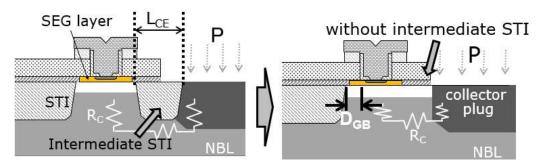

| 4.7.1 Reduction of Collector Resistance                                                 | 81  |

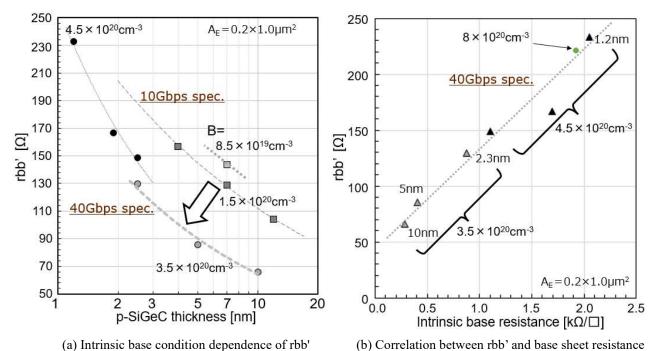

| 4.7.2 Reduction of Base Resistance                                                      | 84  |

| 4.8 Conclusions                                                                         | 89  |

| 4.9 References                                                                          | 90  |

| 5. Crosstalk Noise Propagation Characteristics in Thick-Layer SOI                       | 93  |

| 5.1 5.1 Introduction and Purposes of This Study                                         | 93  |

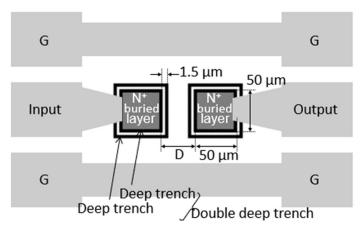

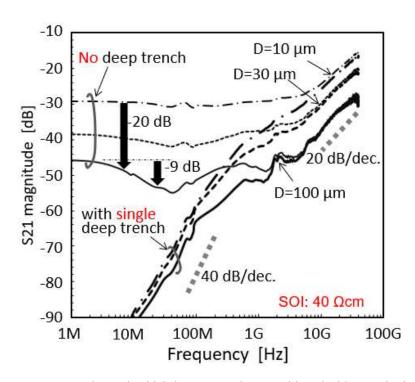

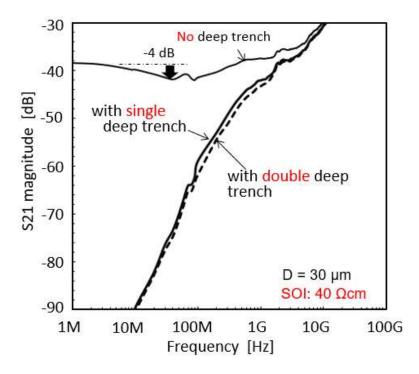

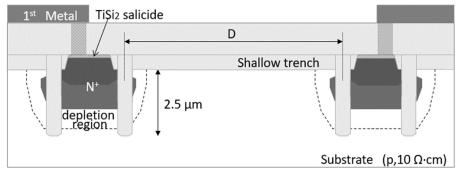

| 5.2 Outline of Study of Crosstalk Noise Propagation Characteristics                     | 94  |

| 5.3 Consideration of Noise Propagation Suppression Effect by Deep Trenches              | 96  |

| 5.4 Resistivity Dependence of the Base Substrates                                       | 100 |

| 5.5 Optimal Design Derived from Simulation                                              | 101 |

| 5.6 Conclusions                                                                         | 104 |

| 5.7 References                                                                          | 105 |

| 6. Technical Challenges to be Studied in the Future                                     | 108 |

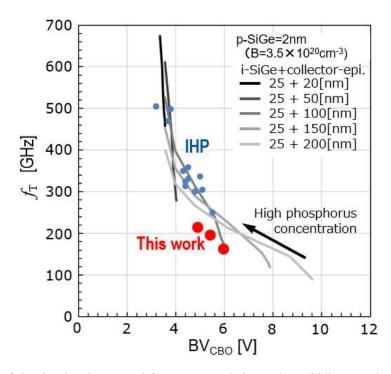

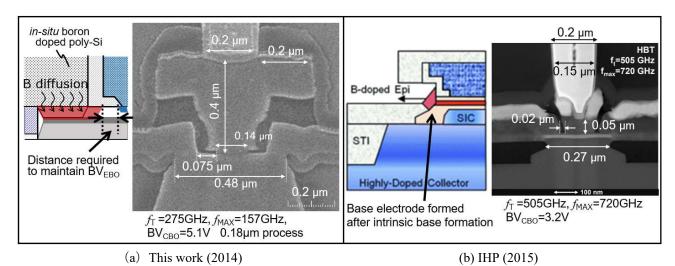

| 6.1 Comparison of SiGe HBT Performance Levels                                           | 108 |

| 6.2 Further Speed Improvement and the 90 nm Node SiGe BiCMOS Process                    | 110 |

| 6.3 Challenges in This Study in Comparison with Other Research                          |     |

| Institutions Related to High resistance Substrates                                      | 116 |

| 6.4 Conclusions                                                                         | 116 |

| 6.5 References                                                                          | 117 |

| 7. Conclusions of This Study                                                            | 121 |

| Research Achievements                                                                   | 123 |

| 1.1 Submission of Articles to Academic Journals                                         | 123 |

| 1.2 Technical Reports on Academic Conference                                            | 124 |

| 1.3 Patents                                                                             | 126 |

| Acknowledgments                                                                         | 128 |

|                                                                                         |     |

## Background and Purpose of This Study

## 1.1 Applications and Technical Challenges of BiCMOS and Bipolar Transistor Technologies 1.1.1 Application of Bipolar Transistor / BiCMOS Technology to Mainframe Computers

ENIAC, developed in 1946 at the University of Pennsylvania, was the first computer to support today's information society. The utilization of the large equipment using 17,468 vacuum tubes (floor area=100 m², weight=30 tons, power consumption=150 kW) was limited to ballistic calculations for military applications [1]. On the other hand, the transistor was invented to replace the vacuum tube at about the same time. The amplification effect of the point contact bipolar transistor was confirmed in December 1947 by William Bradford Shockley, John Barden, Walter House Brattain, etc., of Bell Laboratory. Robert Noyce of Fairchild and Jack St. Clair Kilby of Texas Instruments conceived the idea of integrated circuits using transistors in 1958-1959, and Intel started to manufacture 4-bit i-4004 processors for electronic desktop calculators using the 10 μm PMOS process in March 1971 [2]. Intel, Motorola, and Zilog subsequently developed 8-bit microprocessors and began full-fledged development of computers using semiconductor technologies. Initially, the scale of integrated circuits was limited, and the application was also limited to desktop calculators. However, as the scale of integrated circuits grew, the development of large-scale general-purpose computers (mainframes) became famous for batch processing like

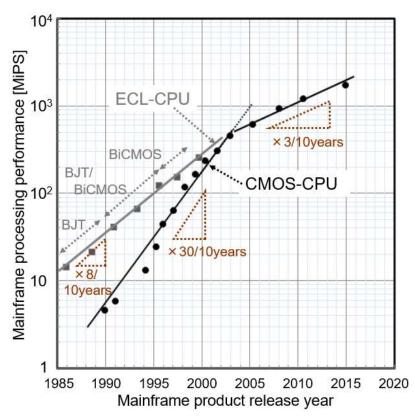

Fig. 1.1. Comparison of trends in the processing speed of mainframe computers by devices that made the CPU up.

accounting and inventory calculations and large-scale online processing systems like banks and train seat reservations. The technologies developed for these mainframe applications were applied to servers and personal computers. In 1985, the CPU consisting mainly of Si-based bipolar junction transistors (hereafter referred to as bipolar transistors) performed only about 20 MIPS alone. However, the performance of the CPU for the IBM mainframe (zEnterprise 196) that was developed in 2010 using the latest CMOS process at that time was 1,200 MIPS alone, and 52,000 MIPS (floor area=3 m², weight=1.5 tons, power consumption=27.5 kW) in parallel with 80 units. The supercomputer "Fugaku" that was in whole operation in 2021 at RIKEN (Institute of Physical and Chemical Research) has a CPU of 52 cores per node and parallelized 158,976 nodes. Its weight is about 1.6 t × 432 chassis, and its power consumption is 28.3 MW; it makes it a vast system in performance and scale.

In the case of an ECL circuit (Emitter Coupled Logic) using bipolar transistors, the through current flows in both the ON and OFF states. In the case of a CMOS circuit, the through current flows only when switching between ON and OFF states, resulting in a power consumption difference of more than two orders of magnitude. For this reason, CMOS was initially used in electronic desktop calculators that pursued portability because low power consumption was more critical than circuit performance. On the other hand, the mainframe capable of thoroughly preventing heat generation continued to improve the performance of bipolar transistors for adopting an ECL circuit faster than CMOS [4]. In addition, to control the increase in power consumption per chip as the scale of ECL circuits become more extensive and more integrated, the BiCMOS (Bipolar CMOS) technology was developed in the 1980s to enable the equipping of ECL circuits and CMOS circuits on the same chip. Using this technology, the ECL-CPU that appeared in 1991 was fitted with a chip that combined the secondary cache of CMOS memory and the logic of the ECL circuit. The processing capacity of ECL-CPU was improved 10-fold in 10 years by increasing the speed of ECL circuits and increasing the integration with BiCMOS technology (Fig. 1.1). However, the power consumption of the ECL-CPU chip introduced in 1999 reached 600 W even though more than half of the logic was made up of CMOS circuits. The power consumption of the ECL-CPU in the next generation was estimated to be around 2 kW, and it was judged that further high integration should reach the limitation of the cooling function. ECL-CPU was an aggregate of multiple chips due to the degree of gate integration and power consumption limitations. On the other hand, the CMOS-CPU has multiplied cores on a single chip to reduce processing delays due to transactions between chips to improve system performance. Although there was an 8-fold difference in processing performance in 1990, the performance of the CMOS-CPU was enhanced by 30-fold in 10 years, enabling it to catch up with the performance of the ECL-CPU in 2001. Since then, only the CMOS CPU has been used in the mainframes.

#### 1.1.2 Challenges Relating to BiCMOS Technology Applied to the Communications Fields

On the other hand, with the widespread use of the Internet and smartphones in corporate work and daily life, there have been demands for constructing communication infrastructure systems for higher-speed and large-capacity data transmission. Because communication infrastructure systems must operate at high speeds and over a wide range of areas, LSIs must be compatible with performance, cost, and reliability [5]. In addition, digital processing circuits for converting analog and digital signals have become large-scale for supporting communication systems, and low power consumption is also required for LSIs for communications. For this reason,

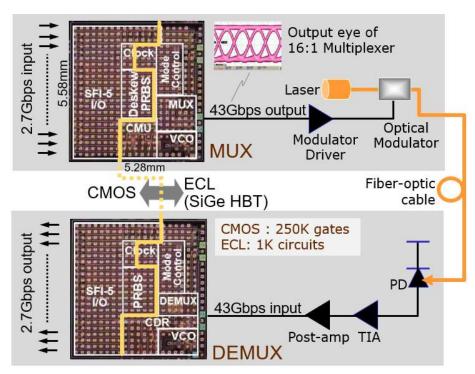

BiCMOS technologies have continued to be used in the communication fields. For example, at the 40 Gbps optical transceiver, the ECL was responsible for the 43 Gbps high-speed signal processing, and the CMOS was accountable for the 2.7 Gbps middle-speed processing, reducing power consumption (Fig. 1.2, [6]). The scale of the CMOS circuit was 250 times that of the ECL circuit, but the power consumption was half. The advantage of the BiCMOS technology against compound semiconductors is that high integrated circuits can be achieved by equipping the CMOS circuits with low power consumption on the same chip.

Even if a BiCMOS process with bipolar transistors and CMOS on the same chip was developed, product design could not begin without a series of PDKs ( $\underline{P}$ rocess Design  $\underline{K}$ its) for design. PDK consists of device parameters extracted from device characteristics, CMOS cell libraries, and various tools for automatically arranging CMOS

Fig. 1.2. Conceptual diagram of role-sharing between CMOS and SiGe HBT in LSI for optical communication [6].

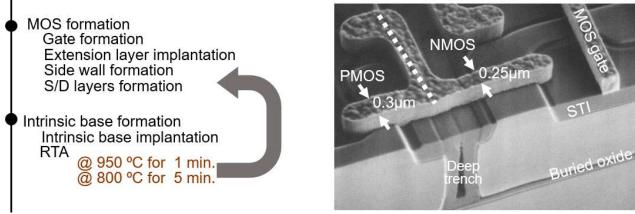

(a) 0.25 µm Si BiCMOS process flow

(b) Bird's-eye SEM photo-view of CMOS part in BiCMOS

Fig. 1.3. NMOS and PMOS equipped on the 0.25 µm Si BiCMOS [7].

cells. Since PDK requires confirmation of the cell operation, the development cost and effort shall be high. However, because LSIs for communications are small in volume and large in variety, it isn't easy to individually develop the PDKs that are expensive to produce, even if new devices are created exclusively for products. On the other hand, it was necessary to maintain a thin base layer to increase the frequency of the bipolar transistor, so the MOS formed up to the S/D (Source/Drain) region before forming the bipolar transistor in conventional BiCMOS processes (Fig. 1.3(a)). The short channel characteristics were maintained by making the PMOS gate length longer than the NMOS gate length due to the expansion of the MOS diffusion layer due to the thermal budget during the fabrication of the bipolar transistor (Fig. 1.3(b)) [7]. For this reason, conventional BiCMOS technologies could not achieve compatibility with standard CMOS and had to develop their PDK. Still, it was necessary to maintain compatibility with existing CMOS in the BiCMOS process to utilize the abundant design assets of standard CMOS.

#### 1.1.3 Challenges Relating to Bipolar Transistors Applied to the Communications Fields

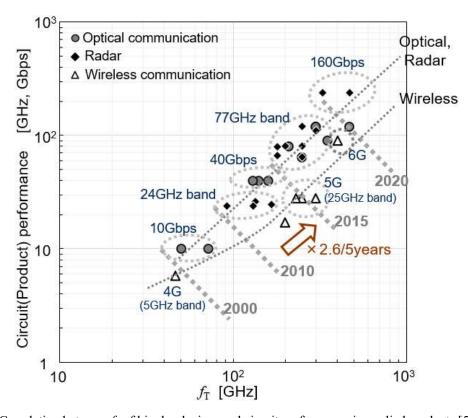

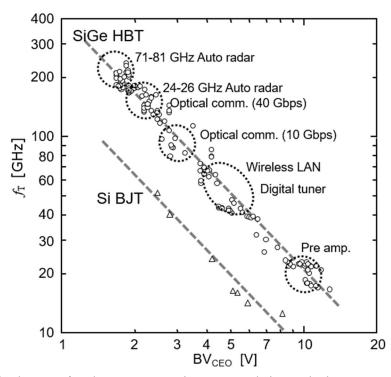

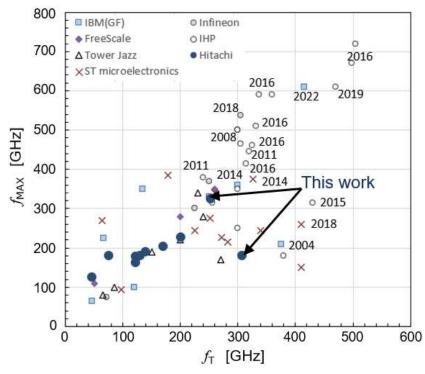

The three main applications for bipolar transistors/BiCMOS that were reported in academic conferences or technical papers have been optical communication [8]-[19], wireless communication [20]-[25], and in-vehicle radar [26]-[37]. There is a rough correlation between the operating frequency of each application and the cutoff frequency ( $f_T$ ) of bipolar transistors, and the operating frequency has increased by about 2.6 times in five years (Fig. 1.4).

SONET (Synchronous Optical NETWORK), one of the global standards for optical transmission, has a transmission speed of 9.952 Gbit/s (OC-192), 39.8 Gb/s (OC-768), and 159.252 Gbps (OC3072). In addition, Ethernet, one of the global standards of LAN (Local Area Network), includes IEEE802.3ae (10GE: 10G Ethernet) and IEEE802.3z with a transmission speed of 1 Gbit/. In optical communications, the bipolar transistors with  $f_T$

Fig. 1.4. Correlation between  $f_T$  of bipolar devices and circuit performance in applied products [5],[8]-[37].

Fig. 1.5. Tradeoff relation between  $f_T$  and BV<sub>CEO</sub> among SiGe HBTs and Si BJTs; both types were fabricated on Hitachi's 8-inch line. SiGe HBTs were manufactured in the 0.15-0.25  $\mu$ m process, and Si BJTs were manufactured in the 0.25-0.35  $\mu$ m process.

and  $f_{\text{MAX}}$  (Maximum oscillation frequency) of about 70 GHz were used to support communication speeds of 10 Gbps around the year 2000, and the bipolar transistors of about 140 GHz were used to support communication speeds of 40 Gbps. In 2015, communication technology exceeding 100 Gbps was announced with the advent of higher-frequency bipolar transistors. The bipolar transistor with  $f_T$  =300 GHz and  $f_{\text{MAX}}$  =350 GHz was used to research a communication rate of 120 Gbps, and it was estimated that the next generation OC-3072 with 160 Gbps requires  $f_T$  =500 GHz. In the wireless field, a product of 4G (5 GHz band) was reported for bipolar transistors with  $f_T$  and  $f_{\text{MAX}}$  of around 70 GHz around the year 2000, and the use of bipolar transistors with  $f_T$  of about 300 GHz resulted in 5G (25 GHz band) and 77 GHz band radar. In addition, around 2020, adopting bipolar transistors with  $f_T$  of 500 GHz or higher reported the possibility of 6G wireless communication and 120 Gbps optical communication [5]. In recent years, there has been an increasing need for the development of onboard radar that matches market prices in line with the trend toward commercializing automotive automated driving functions. Previously, announcements were centered on 24-26 GHz radars using bipolar transistors with  $f_T$  =130 GHz-160 GHz, but the emphasis has shifted to those of 77-79 GHz radars employing bipolar transistors with  $f_T$  =180 GHz-220 GHz.

The high frequencies of the bipolar transistors have increased following the high-speed operation of the application. However, the conventional Si BJT (<u>Bipolar Junction Transistor</u>) has a limit of  $f_T$  of 100 GHz. In the SiGe HBT (<u>Heterojunction Bipolar Transistor</u>) incorporated with Ge in the intrinsic base layer, the  $f_T$  of SiGe HBT has been approximately 2.5 times that of Si BJT compared with the same Collector-Emitter (CE) breakdown voltage (BV<sub>CEO</sub>) (Fig. 1.5). With  $f_T$  and  $f_{MAX}$  exceeding 250 GHz, the SiGe HBT has been extended to the high-

frequency range of optical communication and radar that were previously realized with compound semiconductors. Furthermore, with BV<sub>CEO</sub> higher at the same frequency, SiGe HBT has been applied to wireless communication and preamplifiers in HDD (<u>Hard Disc Drive</u>). However, because the production volume of semiconductor devices used in these markets has been limited, technology standardization has been an issue. In addition, the challenge was not the level of feasibility study described in the technical papers but the realization of bipolar transistors with  $f_T$  and  $f_{MAX}$  exceeding 250 GHz with the reliability of using them in the market.

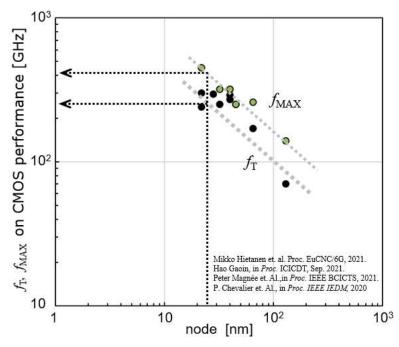

#### 1.1.4 Positioning of Bipolar Transistors in the Trend Toward Higher CMOS Speeds

On the other hand, the applications of CMOS, including SOI-CMOS, have been studied for high-frequency products, and the device performance of  $f_T$ =300 GHz and  $f_{MAX}$ =450 GHz at the 22 nm node was reported (Fig. 1.6). This performance is comparable to that of SiGe HBT using a 0.13 µm process. Studies on the combination of fine CMOS and high resistance SOI substrate have been presented, and fundamental studies [41] for the application of the 40 nm CMOS to 5G chips and the results of prototype and evaluation of 2.8 GHz PA (Power Amplifier) using the 45 nm CMOS [42] have been reported. By utilizing a high-resistance SOI having a resistivity of 1 to 10 k $\Omega$ •cm on the base substrate, the crosstalk noise propagation could be suppressed, and the Q value of the inductor equipped on the chip could be improved. Prototype and evaluation of 80-100 GHz bandpass filter using the 65 nm node [43], LNA (Low Noise Amplifier) using 0.13 µm node [44], and 5.8 GHz bandpass filter using 0.18 µm node [45] have been announced. Millimeter-wave circuits are expected to develop due to fine CMOS, such as the 22 nm node.

However, ArF liquid immersion scanner has been a prerequisite for fine CMOS of the 45 nm node or later, so the process cost shall be high. The 0.13  $\mu$ m node CMOS that has used a KrF scanner has a relatively low process cost, but its device performance is limited to  $f_T$ =70 GHz and  $f_{MAX}$ =140 GHz. On the other hand, SiGe BiCMOS technology can achieve high-frequency characteristics comparable to advanced CMOS even with a 200-mm $\phi$  0.18- $\mu$ m process that is not the most advanced.

Fig. 1.6. Node dependence of high-frequency characteristics of CMOS devices [5],[38]-[40].

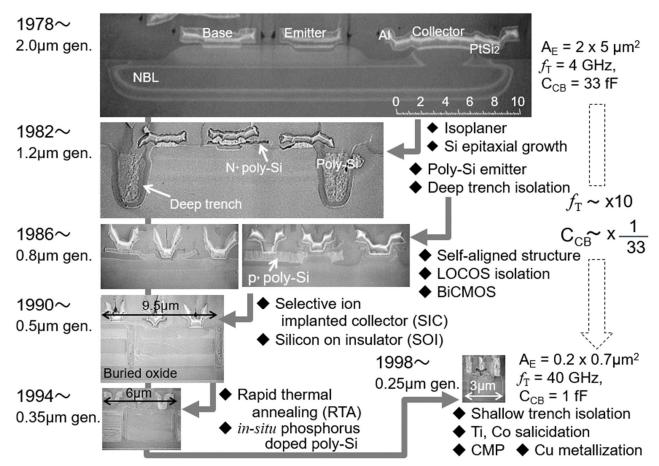

Fig. 1.7. SEM cross-sections of Si BJTs from 2.0 μm to 0.25 μm generation. Describe the main technology innovations of each generation [46].

#### 1.2 Overview of Conventional Techniques for Increasing the Frequency of Bipolar Transistors

The following techniques realized the performance improvement of Si BJTs developed in the past for large general-purpose computers (Fig. 1.7).

- (i) Improvement of  $f_T$  by thinner intrinsic base layers

- ... Low-acceleration ion implantation, RTA (Rapid Thermal Annealing), poly-Si emitter structure

- (ii) Improvement of  $f_T$  by thinner and higher-impurity-concentration collector layers

- ... Profile optimization in the SIC (Selective ion Implanted Collector) region

- (iii) Improvement of  $f_{MAX}$  by new device structure and narrow emitter width

- ... Double-polysilicon self-aligned structure, Fine lithography technology

- (iv) Improvement of  $f_{MAX}$  by using the same fine technology as CMOS

- ... Fine lithography technology, STI(Shallow Trench Isolation), Silicide process, etc.

From 2.0  $\mu$ m generation to 0.25  $\mu$ m generation, the adoption of (i)-(iv) increased  $f_T$  tenfold and reduced collector-base parasitic capacitance ( $C_{CB}$ ) to 1/33. The inverse of  $f_T$  can be indicated as Eq. (1.1), which is the sum of the emitter time constant ( $\tau_E$ ), the charge and discharge time in the collector-base parasitic capacity ( $\tau_C$ ), the transit time in the intrinsic base region ( $\tau_B$ ), and the transit time in the collector layer ( $\tau_{CSCL}$ ).

$$\frac{1}{2\pi f_{\rm T}} = \tau_{\rm EC} = \tau_E + \tau_C + \tau_B + \tau_{\rm CSCL} = \frac{kT}{qI_c} C_{EB} + \left(\frac{kT}{qI_c} + R_C + R_E\right) C_{CB} + \gamma \frac{W_B^2}{D_n} + \frac{W_{CSCL}}{2\nu_{SAT}}$$

(1.1)

I<sub>C</sub>: Collector current

W<sub>B</sub>: Intrinsic base thickness Dn: Electron diffusion coefficient

$\gamma$ : Constant that depends on accelerating built-in field

$W_{CSCL}$ : Collector depletion thickness  $v_{SAT}$ : Electron saturation speed

Thinning the intrinsic base layer could reduce the third term,  $\tau_B$ . The fourth term,  $\tau_{CSCL}$ , is the transit time of the collector layer of the low-impurity-concentration layer between the intrinsic base layer and the NBL (: N-type Buried Layer).  $\tau_{CSCL}$  could be reduced by suppressing the Kirk effect (: push-out of the base layer in the high current region). The Kirk effect could be stopped by thinning the collector layer or increasing the concentration of impurities in the collector layer.  $\tau_E$  in the first term and  $\tau_C$  in the second term are the charge/discharge time of the emitter-to-base parasitic capacitance ( $C_{CB}$ ) and the collector-to-base parasitic capacitance ( $C_{CB}$ ). Significantly, the CR time constant of the second term is the product of  $C_{CB}$  and the sum of the collector resistance ( $R_C$ ) and the emitter resistance ( $R_C$ ). Therefore, reducing parasitic capacitance and parasitic resistance by a self-aligned structure and device shrink has been effective. Here, making the junction shallower and narrowing the depletion layer width increases the junction capacitance, so  $\tau_C$  and  $\tau_{CSCL}$  are in a conflicting relationship. As one solution, the SIC region has been formed by implanting impurities only right under the intrinsic base layer. The increase in  $C_{CB}$  due to increased impurity concentration was somewhat suppressed.

Conventional higher frequency techniques familiar to the SiGe HBT device design are summarized below.

#### (i) Thinner the intrinsic base layer

Thinning the intrinsic base layer effectively improves  $f_T$  because  $\tau_B$  varies with the square of the intrinsic base layer width. To make the intrinsic base layer thinner, there has been a poly-Si emitter structure or combination of low-acceleration ion implantation (BF<sub>2</sub>, single-digit keV) and RTA.

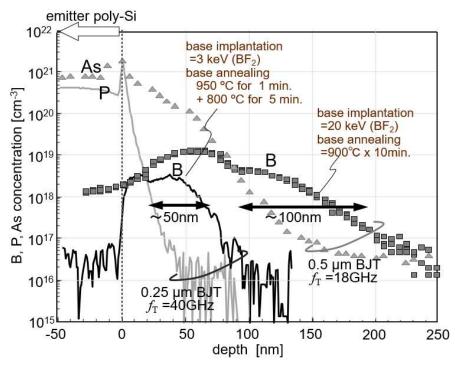

#### (i)-1. Thinning the intrinsic base layer by low-acceleration ion implantation

BF<sub>2</sub>, rather than boron, has been used as ion species to implant impurities into the intrinsic base layer because boron is too light in weight and has a deeper boron profile due to channeling effects even at the low-acceleration energy implantation. In 0.35 μm generation, annealing after impurity implantation was switched from batch-type furnace annealing (FA) to single-wafer RTA. The RTA facilitated shallow junction by instantaneously recovering damage to the substrate during ion implantation and suppressing enhanced boron diffusion through defects. Furthermore, emitter diffusion into the substrate switched from the arsenic diffusion after ions were implanted into the non-doped poly-Si layer to the phosphorus diffusion from the *in-situ* phosphorus-doped poly-Si layer. This technique suppressed the thermal budget for annealing from 900 °C for 10 minutes to 875 °C for 10 seconds, and both the emitter layer and the intrinsic base layer became shallow.

Based on the above, the intrinsic base layer formed by boron ion implantation in the 0.5  $\mu$ m generation was 100 nm thick and had a boron peak concentration of  $4\times10^{18}$  cm<sup>-3</sup>, whereas that in the 0.25  $\mu$ m generation was 50 nm thick and had a boron peak concentration of  $3\times10^{18}$  cm<sup>-3</sup> (Fig. 1.8). Including the contribution of changing the collector conditions,  $f_T$  was improved from 18 GHz for the 0.5  $\mu$ m BJT to 40 GHz for the 0.25  $\mu$ m BJT. In addition, in the 0.25  $\mu$ m BJT,  $f_T$  was increased from 47 GHz to 52 GHz by further reducing the acceleration of BF<sub>2</sub> ion

Fig. 1.8. Comparison of the emitter and base impurity profile on Si BJTs between generations.

Fig. 1.9. Dependence of high-frequency characteristics of Si-BJTs on base layer formation conditions.

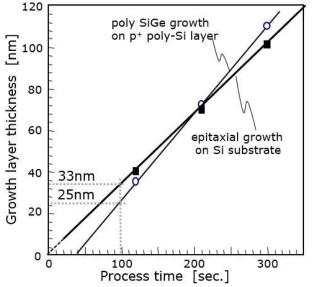

implantation under the same collector formation conditions (Fig. 1.9). However, because of thinning of the impurity diffusion layer by the combination of ion implantation and RTA was limited to 50 nm, it was aimed in this study to form a box-shaped boron profile by selective SiGe epitaxial (SEG: Selective Epitaxial Growth) technology to make the layer thinner.

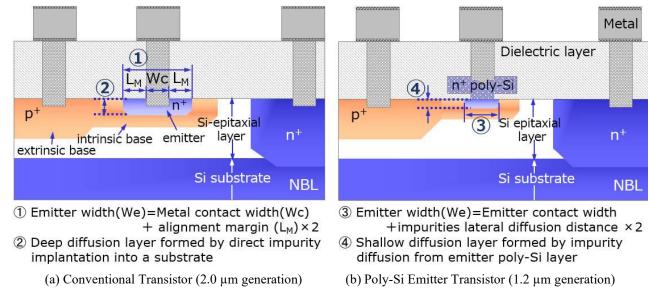

#### (i)-2. Thinning the intrinsic base layer by the poly-Si structure

In the 2 µm generation, emitter and base diffusion layers were formed by implanting impurities directly into the

Si epitaxial growth layer formed on the NBL [46]-[50]. In this method, the emitter and base diffusion layers needed to be deep because the emitter diffusion layer was etched to some extent during contact hole formation (Fig. 1.10(a)). On the other hand, thinning the base layer was required to improve the performance of the bipolar transistor, as shown in equation (1.1), so the emitter layer also needed to be shallow. When the impurity ions were implanted deep in the Si substrate, considering that the surface of the substrate was etched during contact hole processing, the impurity profile became deeper, making it difficult to thin the base layer. Therefore, the poly-Si emitter structure that forms the emitter region by diffusion of impurities from the poly-Si layer doped with arsenic or phosphorus was adopted in the 1.3 µm generation (Fig. 1.10(b)). The emitter poly-Si layer functioned as an etching stopper during contact hole formation, so the emitter and base diffusion layers were shallow. In addition, the emitter width, determined by the sum of the minimum dimensions and matching accuracy for lithography, could be shrunk to the minimum dimensions for lithography.

Up to the 0.5 μm generation, the non-doped poly-Si layer was ion-implanted with arsenic to form the emitter electrode (Fig.1.8). However, the crowding effect where the impurity diffusion becomes uneven due to the influence of the embedded shape of the poly-Si layer in the emitter hole was an issue. *In-situ* phosphorus-doped poly-Si that does not require ion implantation has been applied to the emitter electrode since the 0.35 μm generation. Furthermore, because the process temperature was lowered in the 0.25 μm generation, an *in-situ* boron-doped poly-Si was also applied to the base electrode.

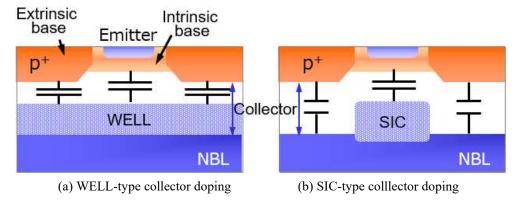

#### (ii) Thinning the collector layer and increasing impurity concentration in the collector layer

When the collector current increases during the forward operation of the bipolar transistor, the Kirk effect becomes apparent so that intrinsic base thickness effectively thickens and  $f_T$  decreases. Concerning the collector layer between the NBL and the intrinsic base layer, increasing the concentration of impurities and thin layers can increase the electric field to suppress the Kirk effect and improve the  $f_T$ . However, the side effect remains as increasing the  $C_{CB}$ . Unlike the WELL type (Fig. 1.11(a) that increases the concentration of impurities on the entire area of the collector layer, the SIC type (Fig. 1.11(b) that only increases the concentration under the intrinsic base

Fig. 1.10. Comparison of bipolar device structures with and without the emitter poly-Si layer.

Fig. 1.11. Differences in techniques for implanting impurities into the collector layer.

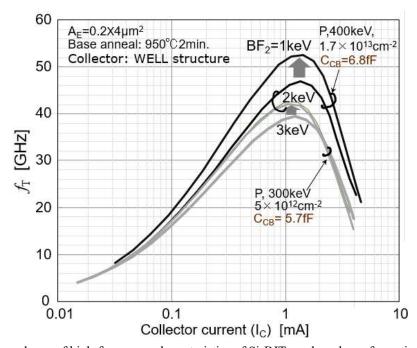

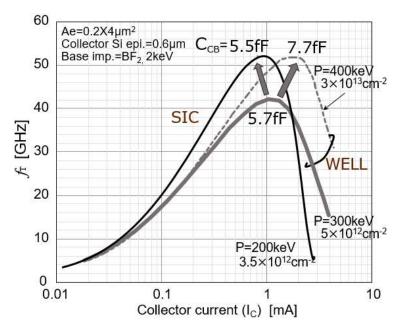

Fig. 1.12. Collector structure dependence of Si-BJT characteristics (intrinsic base layers formed by ion implantation and RTA).

layer is one of the measures to prevent the increase in  $C_{CB}$ . After the emitter hole is opened, the SIC region is formed by phosphorus ion implantation at an accelerating energy of 200-300 KeV. In the SIC type,  $C_{CB}$  increase could be suppressed by limiting the high impurity concentration region to just under the intrinsic base layer. For example,  $f_T$  was increased from 42 GHz to 52 GHz by changing the acceleration energy and dose of phosphorus ion implantation into the entire collector region from 300 keV,  $5 \times 10^{12}$  cm<sup>-2</sup> to 400 keV,  $3 \times 10^{13}$  cm<sup>-2</sup> (Fig. 1.12),  $C_{CB}$  increased 1.4 times. On the other hand, in the SIC type, the  $C_{CB}$  was reduced by 29 % from 7.7 fF to 5.5 fF while realizing the same  $f_T$  of 52 GHz under the conditions of 200 keV and  $3.5 \times 10^{12}$  cm<sup>-2</sup>.

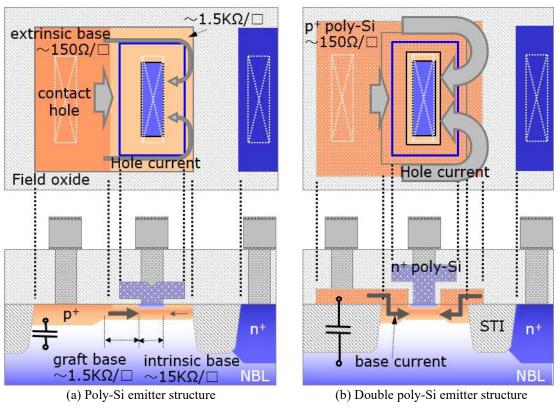

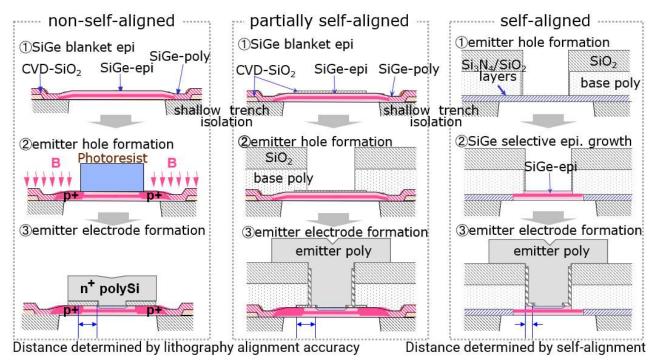

#### (iii) A double-polysilicon self-aligned structure

As an advanced one of the poly-Si emitter structure, a double-polysilicon structure in which the extrinsic base diffusion layer was switched to the poly-Si electrode in addition to the emitter layer appeared in the  $0.8 \mu m$  generation (Fig. 1.7). Although the same  $p^+$  diffusion layer as the PMOS S/D layer is used for the extrinsic base

region in the poly-Si emitter structure (Fig. 1.13(a)), the emitter is surrounded by the intrinsic base layer of a high sheet resistance of 1.5 k $\Omega$ / $\square$ . Therefore, the base current to the opposite side of the base contact hole is suppressed. On the other hand, at the double poly-Si emitter structure, the base resistance was lower than in the poly-Si emitter structure because the intrinsic base layer was surrounded by a poly-Si electrode of 150  $\Omega$ / $\square$  (Fig. 1.13(b)). Also,

Fig. 1.13. Comparison of layout and cross-section of bipolar devices with poly-Si emitter electrode.

Fig. 1.14. The formation process of sidewall structure for the E-B (Emitter electrode – Base electrode) isolation in a typical self-aligned structure.

the base poly-Si layer was formed on the field oxide, thus reducing parasitic capacitance.

The self-aligned structure is a technique that determines the distance between patterns without relying on the alignment accuracy of lithography. For bipolar transistors, the self-aligned structure is employed for the emitter-base (E-B) electrode separation distance, thereby further reducing the base resistance (rbb') and C<sub>CB</sub> [51]-[56]. Various structures other than those shown in Fig. 1.7 were developed. Still, the most utilized structure was the one in which a side wall layer consisting of a poly-Si layer and an oxide layer was formed in the emitter hole to separate the emitter and base (E-B) electrode layers (Fig. 1.14). Since the thickness of the sidewall layer determined the E-B electrode separation distance in a self-aligned manner, rbb' was reduced because the width of the connecting base region was reduced. In addition, the area around the emitter becomes narrower by decreasing the width of the connecting base, and the C<sub>CB</sub> could be reduced. The initial structure was a side wall structure with only an oxide layer. Still, a certain amount of the intrinsic base diffusion layer was also etched by the dry etching process for forming the oxide layer sidewalls, which caused variations in the thickness of the intrinsic base layer. Therefore, a stacked structure of poly-Si and oxide layers was obtained.

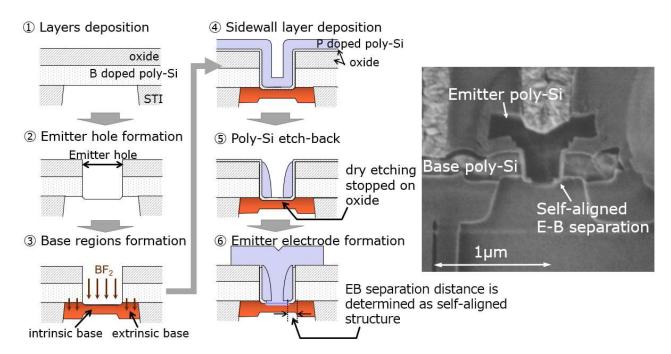

Most of the self-aligned structures were only between the emitter region and base region and not up to the extrinsic base region (region of connection between the base poly-Si electrode and the Si substrate layer) were self-aligned (Fig. 1.15(a)). The SICOS structure studied at the Central Research Laboratory of Hitachi, Ltd. was self-aligned both between the emitter and base poly-Si electrode and between the base poly-Si electrode and filed oxide layer (Fig. 1.15(b)). First, a dummy pattern of the emitter layer was formed on the mask up to the field oxide layer and the base poly-Si electrode layer. The Si substrate connection of the extrinsic base electrode was determined by self-alignment. In addition, the E-B electrode separation region was also formed as a self-aligned structure by

(a) Most common self-aligned structure

(b) SICOS (Side Wall Contact Structure) process flow

Fig.1.15. Comparison between widely adopted self-aligned and SICOS structures, including process flow [57].

thermally oxidizing the upper layer and sidewalls of the extrinsic base electrode. There were many process steps in a complex structure, and there was no continuous application of this structure.

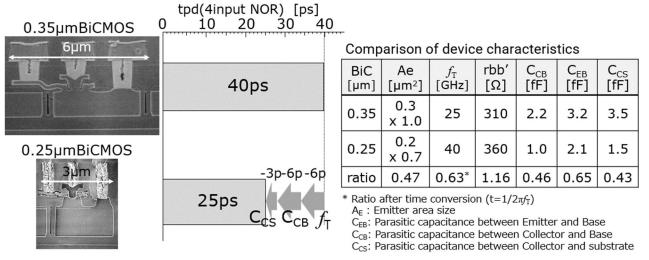

#### (iv) Fine process technology

Up to the 2.0 µm generations, the separation between devices was achieved by a combination of LOCOS: LOCal Oxidation of Silicon) and channel stoppers by impurity ion implantation. However, the reduction of the separation width was limited due to the lateral spread of the diffusion layer. After the 1.2 µm generation, the device-to-device distance was shortened by forming trenches deeper than the N<sup>+</sup> buried layer. Furthermore, in the 0.25 µm generation, technologies such as STI (Shallow Trench Isolation) and silicide newly developed by CMOS technologies were also incorporated in BiCMOS, thereby facilitating the reduction of the parasitic capacitance and resistance of bipolar transistors [58]. The isolation region was shrunk by applying the STI because there was no lateral broadening of the oxidation region by the bird's beak at the LOCOS structure. The device shrinkage in the fine process may cause an increase in parasitic resistance because of the decrease in the width of the current path. However, the increase in parasitic resistance was suppressed by the Ti salicide technology in the 0.25 µm generation and by the Co salicide technology in the 0.18µm generation. As the fine process technologies progressed from the 2.0 µm generation to the 0.25 µm generation for Si BJTs (Fig. 1.7), the substrate parasitic capacitance (C<sub>CS</sub>) was reduced to 1/50, and the collector-base parasitic capacitance (C<sub>CB</sub>) was reduced from 33 fF to 1 fF. In addition, the  $f_{\rm T}$  was increased from 4 GHz to 40 GHz with increasing the collector current density, and the emitter area was reduced from 2×5 μm² to 0.2×1 μm² to suppress various parasitic parameters. As a result, the ECL gate delay time (tpd) was reduced from 250 ps/gate for the 2.0 μm generation to 25 ps/gate for the 0.25 μm generation [55][58]. In addition, the delay time of the 4-input NOR circuit was shortened from 40 ps/gate for the 0.3 µm generation to 25 ps/gate for the 0.25 μm generation (Fig. 1.16)[58]. According to the sensitivity analysis of various device parameters by circuit simulation, the  $f_T$  improvement (from 25 to 40 GHz) contributed 6 ps of the 15 ps reduction. On the other hand, the total contribution of parasitic capacitance due to the fine process was 9 ps.

Other research and development institutes like IBM stopped applying BJTs to mainframe computers at the 0.5

Fig. 1.16. Circuit delay time (tpd) comparison between generations [56].

μm generation, temporarily halting the shrinking BJT development. On the other hand, this study continued to use the BJTs for the mainframe computers and to advance the shrinking BJT. It was also thought essential for the SiGe HBT to maintain superiority in the shrinking structure of the device.

#### 1.3 Usefulness and Issues of Application of Thick-Layer SOI to BiCMOS for Analog Products

In communication LSIs, realizing discrete devices around the chip in the metallization layers on the chip has contributed to product cost reduction and product performance improvement by reducing the area of the entire system (Module). Therefore, improving the performance of on-chip passive devices such as capacitors (MIM: Metal Insulator Metal) and inductors in the front-end process has also been a significant challenge. In the on-chip implementation of passive devices, the parasitic resistance and the parasitic capacitance with substrates

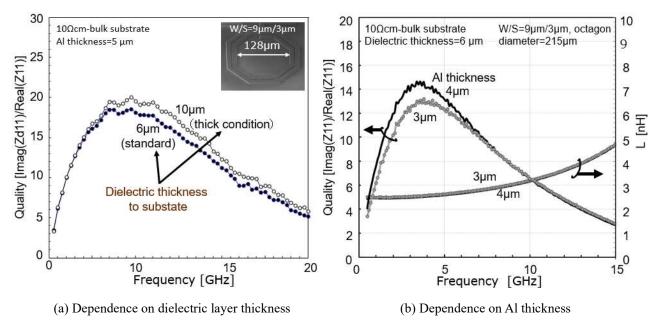

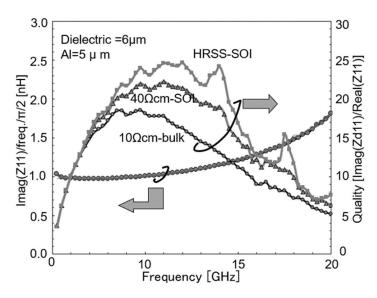

Fig. 1.17. Dependence of inductor Q value on metallization layer specifications.

Fig.1.18. Dependence of on-chip inductor characteristics on Si substrate specification. (Line/Space= $9/3 \mu m$ , Inner diameter= $128 \mu m$ , 2 turns, octagonal shape)

(b) BiCMOS using a thick-layer SOI wafer

Fig. 1.19. Cross-sectional comparison of CMOS using a thin-layer-SOI and BiCMOS using a thick-layer SOI.

significantly affect the operating frequency of analog circuits. Therefore, both the MIM and the inductor are formed the upper metallization layer. For example, because the thickness of the first to third layers of the wiring is only about 0.5 µm due to the wiring constituting logic circuits in the 0.18 µm SiGe BiCMOS, the series resistance is high, and a sufficient Q value of the inductor cannot be obtained. Therefore, an inductor was formed in the top layer which can maximize the thickness of the Al layer up to 3-5 µm thick. However, although the Q value was improved by the thickening of the interlayer dielectric layer and the thickening of the Al layer (Fig. 1.17), a significant improvement in characteristics is not expected even with changes to the wiring layout rule due to the extreme process conditions.

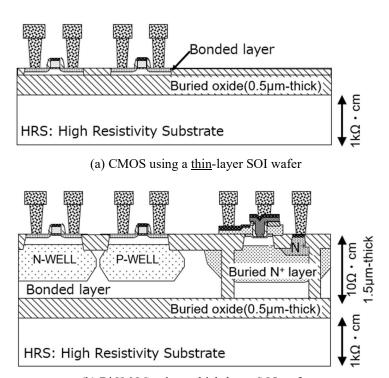

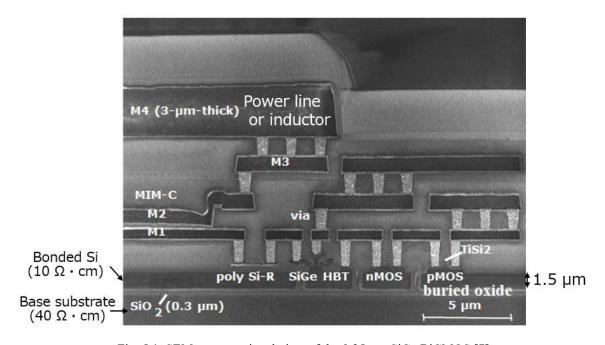

The Q value of the inductor could be significantly improved by changing the resistivity of the substrate (Fig. 1.18), but changing the resistivity of the substrate in a bulk wafer involves a significant change in CMOS IP (Intellectual Property) to change the device characteristics. On the other hand, the resistivity of the bonded Si layer on an SOI (Silicon On Insulator) substrate forming the devices remains unchanged, so the influence on CMOS IP can be minimized. However, the use of thick-layer SOI for high-speed applications was limited. BiCMOS had been used to prevent soft errors by α-rays when using LSIs for mainframe computers [52]-[54][56][58], and there were no published technical papers on crosstalk noise propagation in thick-layer SOI. In addition, in the thin-layer SOI, since a bonded layer thickness is 0.1 μm or less and the STI of the field oxide reaches the buried oxide layer, crosstalk noise propagates only to the base substrate side because only the bonded layer remains in the limited area for MOS formation (Fig. 1.19(a)). However, since the thick-layer SOI has a bonded layer of 1.5 μm, crosstalk noise that could be an issue in analog products propagates on both the base substrate and bonded layer sides (Fig. 1.19(b)). Therefore, it was necessary to clarify the effects of substrate resistivity and structure on the thick-layer SOI on crosstalk noise propagation.

#### 1.4 Purposes of This Study

#### (1) Purposes of this Study

The purposes of this study are as follows.

Because Si BJTs were prioritized in the process construction in conventional Si BiCMOS, CMOS device characteristics and design rules should have been changed. It was necessary to develop a new PDK for each product. However, reconstruction of individual PDK and IP was challenging for small-lot, wide-variety communication products in terms of development costs and product development time. It was aimed in this study to utilize existing CMOS IP by establishing the SiGe BiCMOS technology that maintained consistency with the standard CMOS. It was attempted to reduce the thermal budget of the SiGe HBT formation process and optimize the device height to this end. In addition, it aimed to realize a SiGe HBT with high-frequency characteristics while shifting from a BJT-centered design rule to a CMOS-centered design rule and building a high-performance BiCMOS that conformed to standard CMOS.

In addition, because Si BJTs have the highest value of  $f_T$  at around 100 GHz, they could not be used in fields such as 5G, 40 Gbps optical communication, and radar. Since a significant factor was that a thickness of about 50 nm of the intrinsic base layer was the limit for conventional impurity ion implantation, the purpose of this study was to further improve the  $f_T$  by the SiGe epitaxial growth technology. This technology formed the thin intrinsic base layer and Ge profile generating the accelerated electric field. Furthermore, it was aimed to improve  $f_{MAX}$  by realizing a self-aligned structure even in the SiGe HBT by forming the SiGe selective epitaxial growth, and  $f_T$  and  $f_{MAX}$  of 250 GHz or more could achieve with minimal changes in device structure and layout. This study aimed to realize these aims as a mass production technology.

Another purpose of this study was to clarify the substrate structure dependence of the frequency characteristics of crosstalk noise propagation in thick-layer SOI substrates. Thick-layer SOI has the advantage that the resistivity of the bonded layer in which the devices are performed remains at  $10~\Omega$ ·cm, so even if the base substrate has a high resistivity, there is little effect on IP. However, no technical paper has been published on crosstalk noise propagation in the thick-layer SOI substrate, including the bonded layer. This study aimed to clarify the guidelines for reducing crosstalk noise propagation by combining deep trenches isolating SiGe HBTs with the thick-layer SOI substrates.

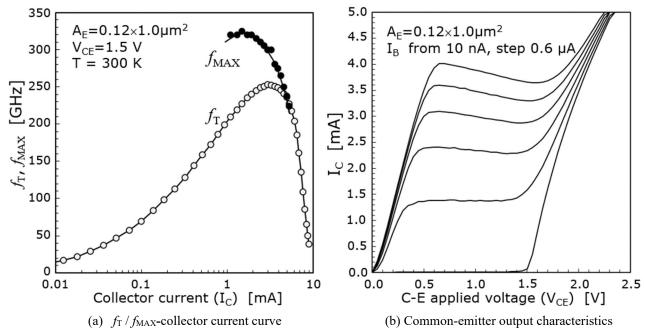

#### (2) Overview of this paper

In this study, the CMOS devices from the 0.13-0.18  $\mu$ m node could be integrated into the SiGe BiCMOS process without deteriorating the short channel characteristics by constructing the MOS priority process, and high-frequency characteristics of the SiGe HBT was achieved by forming the 2-nm-or-less SiGeC layer and reducing various parasitic resistances/capacitances. The low-thermal-budget process to maintain the short channel characteristics was realized by adopting single-wafer processes and the HCl-free selective SiGe epitaxial growth process. Furthermore, it was clarified that the moisture desorption from the CVD oxide layer was a particular issue for lowering the H<sub>2</sub> annealing temperature before SiGe epitaxial growth. A countermeasure was taken by changing to an HDP (High-Density Plasma) layer with less moisture desorption. 254 GHz of  $f_T$  and 325 GHz of  $f_{MAX}$  were achieved by shrinking the emitter size to 0.12×1.0  $\mu$ m<sup>2</sup> with a p-SiGeC layer thickness of 2 nm. In addition, it was clarified the frequency characteristics of crosstalk noise propagation in thick-layer SOI which has been limited to

BiCMOS for high-frequency applications.

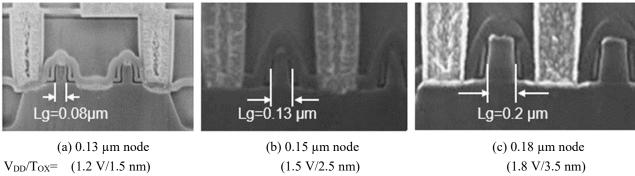

Chapter 2 describes a SiGe BiCMOS process with 0.13  $\mu$ m to 0.18  $\mu$ m CMOS. The thermal budget of the entire bipolar transistor formation process was suppressed by switching the heat-loading process from a batch process to a single-wafer process, and the temperature of the  $H_2$  annealing before the selective epitaxial growth was lowered by adopting an oxide layer that emits less moisture. This allowed the CMOS device to be incorporated into the BiCMOS process without degrading the short-channel characteristics and affecting the SiGe HBT characteristics and yield. Although this technology was studied and developed based on the 0.18  $\mu$ m node, it could be incorporated into BiCMOS up to the 0.13  $\mu$ m node without deteriorating the short channel characteristics, demonstrating the scalability of the process.

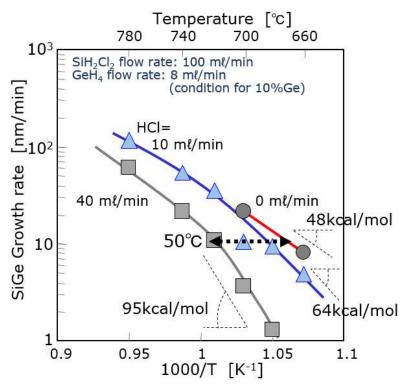

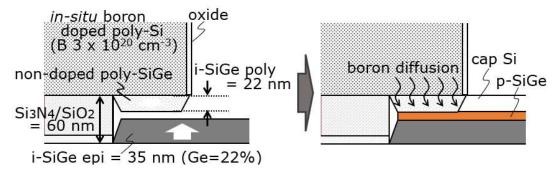

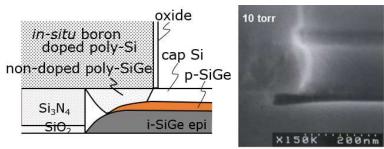

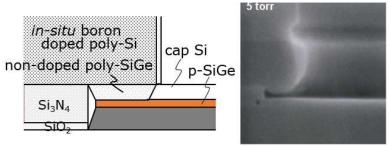

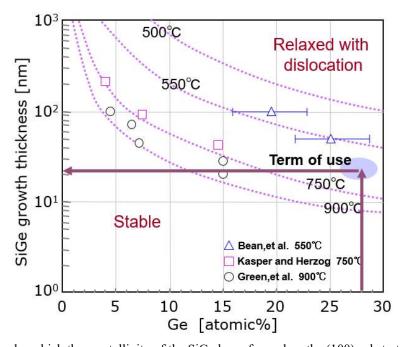

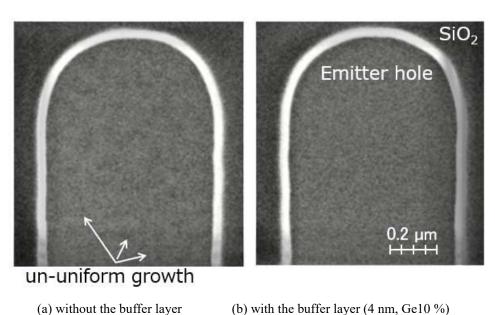

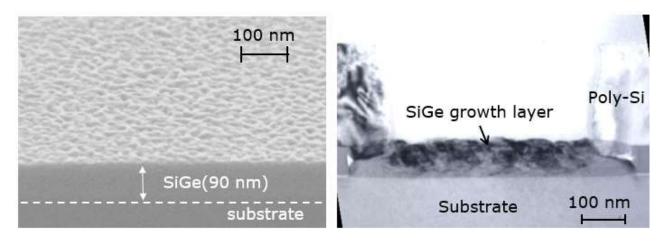

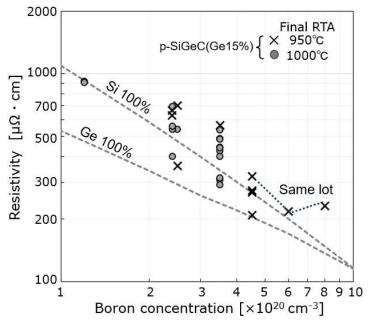

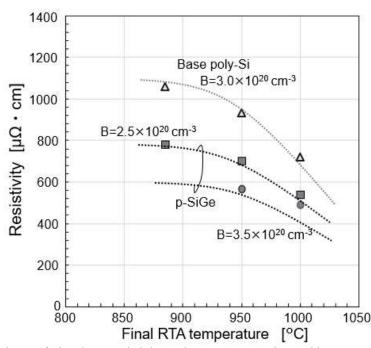

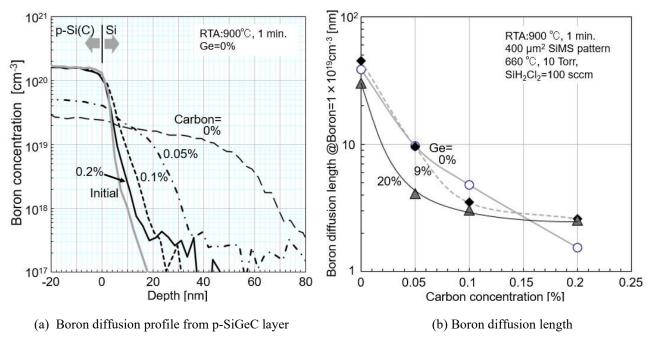

Chapter 3 describes the selective SiGe epitaxial growth technology for forming the intrinsic base layer. The structure covering the base poly-Si electrode with an oxide layer enabled the selective SiGe epitaxial growth without adding HCl gas, and the temperature of the epitaxial growth process was lowered. In addition, it was found that the concentration of boron and Ge in the SiGe layer depended on the area of the growing region, and the monitoring pattern of the concentration of boron and Ge was fixed for accurate monitoring. The boron concentration was finally increased to  $4.5 \times 10^{20}$  cm<sup>-3</sup>, the Ge concentration was increased to 30 %, and it was evaluated that 0.1-0.2 % carbon doping could suppress boron diffusion.

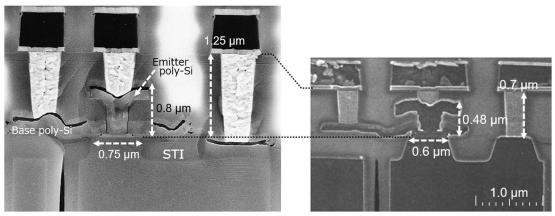

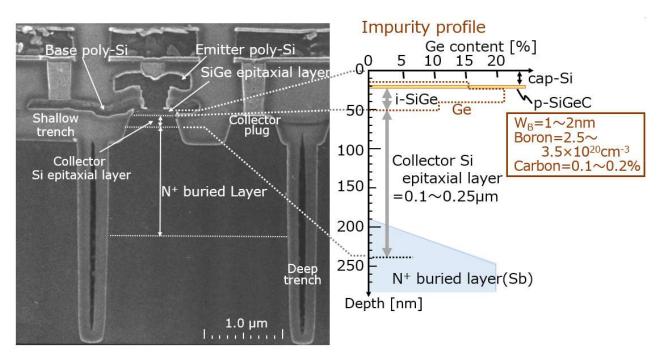

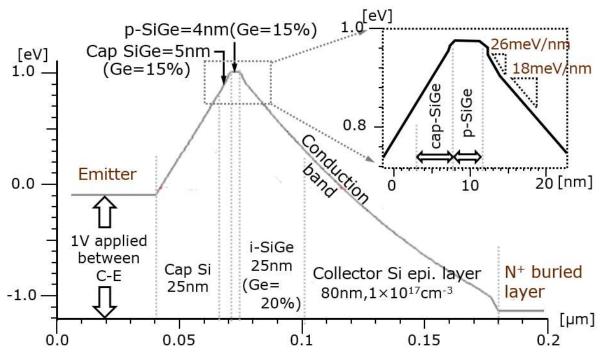

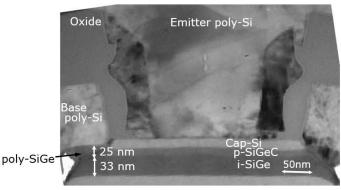

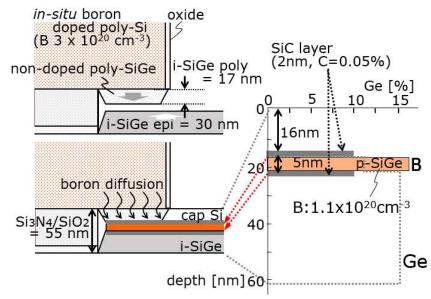

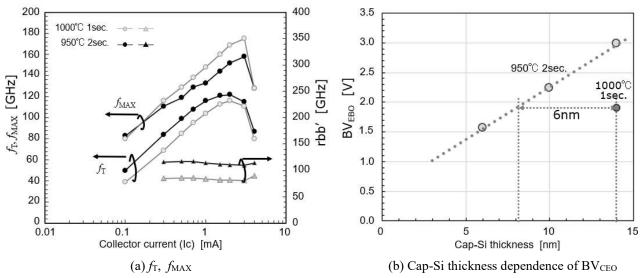

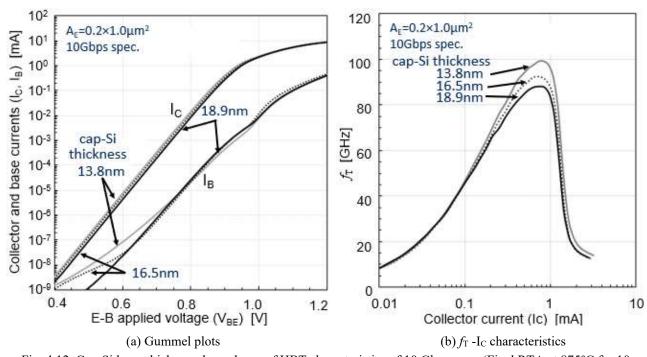

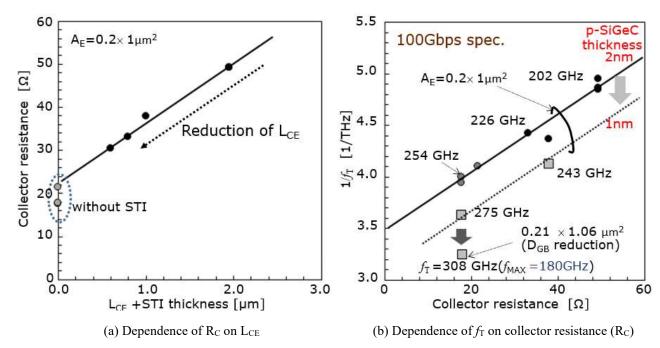

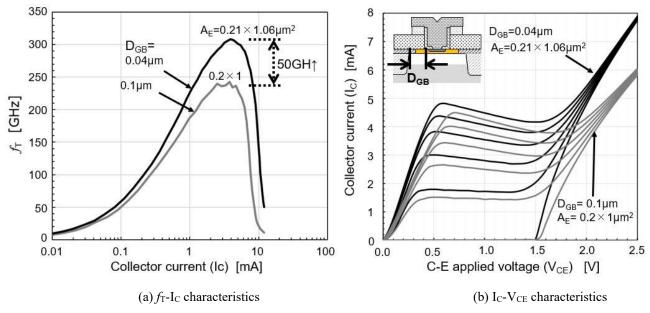

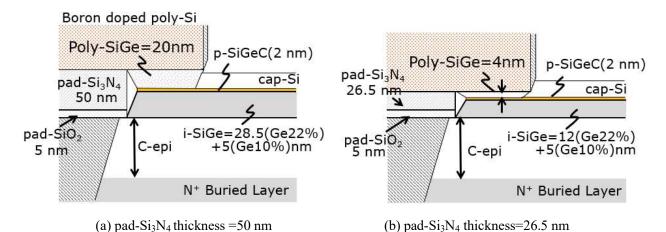

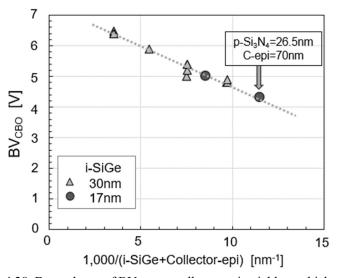

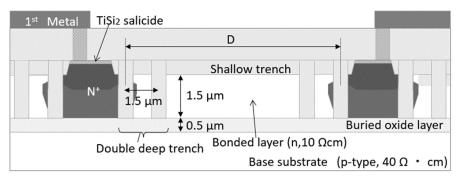

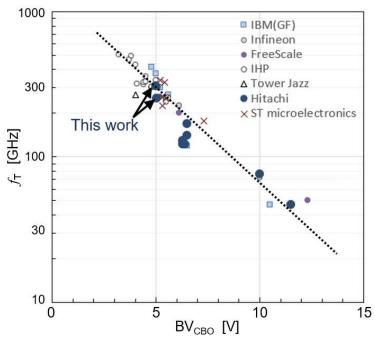

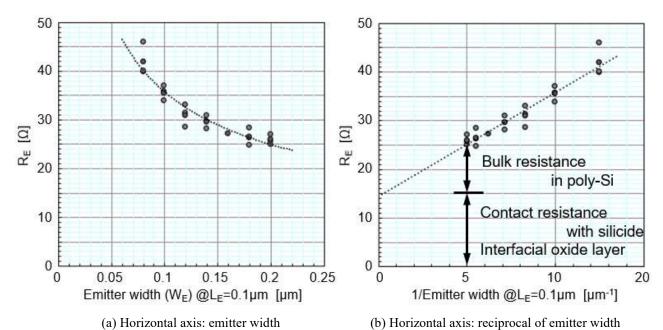

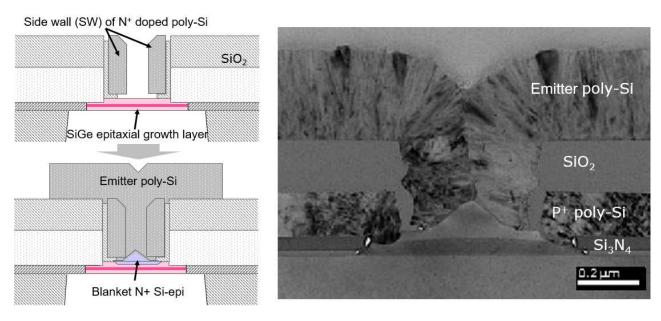

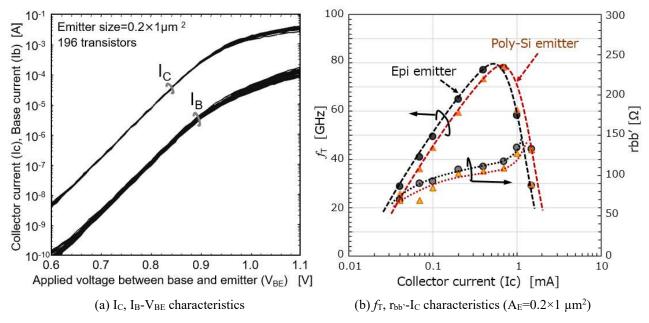

Chapter 4 describes that the SiGe HBT technology developed has suppressed parasitic capacitance and parasitic resistance through a self-aligned structure using the selective SiGe epitaxial growth technology. The step-type Ge profile with a high Ge concentration in the i-SiGe layer just under the p-SiGeC layer was able to improve  $f_T$ , and  $f_T$  of 200GHz has been achieved by thinning the intrinsic base layer and collector layer. In addition, the collector resistance was reduced by removing the intermediate STI between the collector plug and the intrinsic base region, and the  $f_T$  was improved from 226 GHz to 254 GHz. Furthermore,  $f_T = 307$  GHz and  $f_{MAX} = 180$  GHz were realized with a p-SiGeC layer thickness of 1 nm by reducing the collector time constant by narrowing the area of the connecting base region for reducing the collector-base parasitic capacitance ( $C_{CB}$ ). In addition, the collector-base parasitic capacitance and base resistance were suppressed by narrowing the emitter width to 0.12  $\mu$ m, and  $f_{MAX} = 325$  GHz was realized at  $f_T = 254$  GHz with the p-SiGeC layer thickness of 2 nm.

Chapter 5 describes that the deep trench pattern used for device isolation between SiGe HBTs should be considered as a means of suppressing crosstalk noise propagation in thick-layer SOI, depending on the resistivity of the base substrate. In particular, it was more effective to multiplex the deep trench pattern when the base substrate was a high-resistance substrate.

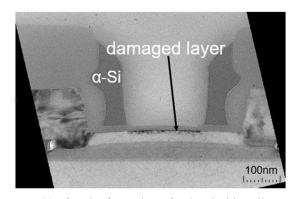

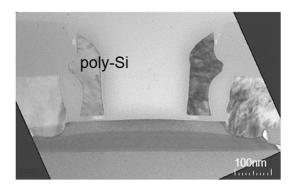

Chapter 6 describes that future issues for SiGe HBTs include the necessity of countermeasures against the increase in emitter resistance that accompanies the narrow emitter necessary for further performance improvement. One issue is the residue of the side wall oxide layer removed around the emitter. The other is the interfacial oxide layer between the emitter poly-Si electrode and the Si substrate. An epitaxial emitter structure was proposed to remove the interface native oxide layer between the emitter poly-Si electrode and the Si substrate surface. It obtained the same characteristics as the poly-Si emitter structure.

#### 1.5 References

- [1] 星野 力、「誰がどうやってコンピュータを創ったのか?」、共立出版

- [2] 嶋 正利「マイクロプロセッサ 4004 の開発」半導体産業人協会 会報№74, p.5-8, 2012 年 1 月.

- [3] 初鹿野凱、野宮 紘靖「電子式卓上計算機用半導体のこれまでの歴史と今後のすう勢」日立評論 1973 年 7月、vol.5 No.7、pp.725-730.

- [4] 小高 俊彦「「ユビキタスへの歩み」 大型コンピュータ開発小史-」 日立製作所評論 2005.5 号, pp. 28-33.

- [5] P. Chevalier, F. Gianesello, A. Pallotta, J. Azevedo Goncalves, G. Bertrand, J. Borrel, L. Boissonnet, E. Brezza, M. Buczko, E. Canderle, D. Celi, S. Cremer, N. Derrier, C. Diouf, C. Durand, F. Foussadier, P. Garcia, N. Guitard, A. Fleury, A. Gauthier, O. Kermarrec, J. Lajoini, C.A. Legrand, V. Milon, F. Monsieur, Y. Mourier, D. Muller, D. Ney, R. Paulin, N. Pelloux, C. Renard, M.L. Rellie, P. Scheer, I. Sicard, N. Vulliet, A. Jug, E. Granger, D. Gloria, J. Uginet, L. Garchery, and F. Paillardet, "PD-SOI CMOS and SiGe BiCMOS Technologies for 5G and 6G communications," in *Proc. IEEE IEDM*, 2020, pp.757-760.

- [6] Keiki Watanabe, Akio Koyama, Takashi Harada, Tatsuhiro Aida, Atsushi Ito, Tomoo Murata, Hiroyuki Yoshioka, Masahito Sonehara, Hiroki Yamashita, Kyosuke Ishikawa, Masahiro Ito, Nobuhiro Shiramizu, Takahiro Nakamura, Kenichi Ohhata, Fumihiko Arakawa, Takeshi Kusunoki, Hiroyuki Chiba, Tsutomu Kurihara, and Mamoru Kuraishi, "A Low-Jitter 16:1 MUX and a High-Sensitivity 1:16 DEMUX with Integrated 39.8 to 43 GHz VCO for OC-768 Communication Systems," in *Proc. IEEE ISSCC*, 2004.

- [7] T. Hashimoto, T. Kikuchi, K. Watanabe, N. Ohashi, T. Saito, H. Yamaguchi, S. Wada, N. Natsuaki, M. Kondo, S. Kondo, Y. Homma, N. Owada, and T. Ikeda, "A 0.2-µm Bipolar-CMOS Technology on Bonded SOI with Copper Metallization for Ultra-High-Speed Processors," in *Proc. IEEE IEDM*, 1998, pp. 209-212.

- [8] D. J. Friedman, M. Meghelli, B. D. Parker, J. Yang, H. A. Ainspan, A. V. Rylyakov, Y. H. Kwark, M. B. Ritter, L. Shan, S. J. Zier, M. Sorna, and M. Soyuer, "SiGe BiCMOS integrated circuits for high-speed serial communication links," *IBM J. RES. & DEV.*, Vol. 47, No. 2/3, pp.259-28, Mar./May 2003.

- [9] R. Tang, C. Leung, D. Nguyen, T. Hsu, L. Fritzinger, S. Molloy, T. Esry, T. Ivanov, J. Chu, M. Carroll, J. Huang, W. Moller, T. Campbell, W. Cochran, C. King, M. Frei, M. Mastrapasqua, K. Ng, C. Chen, R. Johnson, R. Pullela, V. Archer, J. Krska, S. Moinian, and H. Cong, "A Low-Cost Modular SiGe BiCMOS Technology and Analog Passives for High-Performance RF and Wide-Band Applications," in *Proc. IEEE BCTM*, 2000, pp. 102-105.

- [10] J. C. Huang, Y. S. Lai, and K. Y. J. Hsu, "Broadband Transimpedance Amplifier in 0.35-μm SiGe BiCMOS Technology for 10-Gb/s Optical Receiver Analog Front-End Application," in *Proc.* CICC, pp.245-248, 2008.

- [11] Ricardo Andres Aroca and Sorin P. Voinigescu," A Large Swing, 40-Gb/s SiGe BiCMOS Driver with Adjustable Pre-Emphasis for Data Transmission Over 75 Ω Coaxial Cable," *IEEE J. Solid-State Circuits*, Vol. 43, No. 10, pp.2177-2186, Oct. 2008.

- [12] Klaus Schuegraf, Marco Racanelli, Kalburge, Bruce Shen, Chun Hu, David Chapek, David Howard, David Quon, David Feiler, Dieter Dornisch, Greg URen, Hadi Abdul-Ridha, Jie Zheng, Jinshu Zhang, Ken Bell, Ken Ring, Kevin Yin, Pankaj Joshi, Sabrina Akhtar, Timothy Lee, and Paul Kempf, "0.18 pm SiGe BiCMOS Technology for Wireless and 40 Gb/s Communication Products," in *Proc. IEEE BCTM*, 2001, pp. 47-150.

- [13] Mesut Inac, Graduate Student, Adel Fatemi, Falk Korndorfer, Holger Rucker, Friedel Gerfers, and Andrea Malignaggi, "Performance Comparison of Broadband Traveling Wave Amplifiers in 130 nm SiGe:C SG13G2 and SG13G3 BiCMOS Technologies," *IEEE Microwave and Wireless Components Letters*, pp.1-4, 2021.

- [14] Stavros Giannakopoulos, Zhongxia Simon He, and Herbert Zirath, "Tunable Equalizer for 64 Gbps data communication systems in 130nm SiGe," in *Proc. Asia-Pacific Microwave Conference*, pp. 627-629, 2018.

- [15] B. A. Randall, S. M. Currie, K. Fritz, G. D. Rash, J. L. Fasig, B. K. Gilbert, and S. Daniel, "A 70 Gbps 16:1 Multiplexer and a 60 Gbps 1:16 Demultiplexer in a SiGe BiCMOS Technology," in *Proc. CSICS*, 2008, pp.239-242.

- [16] Pedro Rodriguez-Vazquez, Janusz Grzyb, Neelanjan Sarmah, Bernd Heinemann, and Ullrich R. Pfeiffer, "Towards 100 Gbps: A Fully Electronic 90 Gbps One Meter Wireless Link at 230 GHz," in *Proc. EuMA*, Sept. 2018, pp.1389-1392.

- [17] K. Vasilakopoulos, S. P. Voinigescu, P. Schvan, P. Chevalier, and A. Cathelin, "A 92 GHz Bandwidth SiGe BiCMOS HBT TIA with less than 6dB Noise Figure," in *Proc. IEEE BCTM*, 2005, pp. 168-171.

- [18] Mounir Meghelli, Ben Parker, Herschel Ainspan, and Mehmet Soyuer, "SiGe BiCMOS 3.3-V Clock and Data Recovery Circuits for 10-Gb/s Serial Transmission Systems," *IEEE J. Solid-State Circuits*, Vol. 35, No. 12, pp.1992-1995, Dec. 2000.

- [19] T. Tominari, S. Wada, K. Tokunaga, K. Koyu, M. Kubo, T. Udo, M. Seto, K. Ohhata, H. Hosoe, Y. Kiyota, K. Washio, and T. Hashimoto, "Study on extremely thin base SiGe:C HBTs featuring sub 5-ps ECL gate delay", *IEEE BCTM*, 2003.

- [20] Sang-Heung Lee, Ja-Yol Lee, Sang-Hoon Kim, Hyun-Cheol Bae, Seung-Yun Lee, Jin-Yeong Kang, and Bo Woo Kim, "A 5.8 GHz MMIC Down-Conversion Mixer for DSRC Receiver using SiGe BiCMOS Process," in *Proc. Asia-Pacific Conference on Communications*, pp.586-589, Oct. 2005.

- [21] Alessandro Fonte, Fabio Plutino, Laurence Moquillon, Stephane Razafimandimby, and Sebastien Pruvost, "5G 26 GHz and 28 GHz Bands SiGe:C Receiver with Very High-Linearity and 56 dB Dynamic Range," in *Proc. EuMA*, 2018, pp.57-80.

- [22] Bodhisatwa Sadhu and Scott K. Reynolds, "A Fully Decoupled LC Tank VCO based 16 to 19 GHz PLL in 130 nm SiGe BiCMOS Achieving -131dBc/Hz Phase Noise at 10MHz Offset," in *Proc. CSICS*, 2017.

- [23] Roee Ben Yishay, Evgeny Shumaker, and Danny Elad, "Key Components of a D-Band Dicke-Radiometer in 90 nm SiGe BiCMOS Technology," in *Proc. EuMA*, Sep. 2015, pp. 176-179.

- [24] Katharina Kolb, Julian Potschka, Tim Maiwald, Klaus Aufinger, Marco Dietz, and Robert Weigel, "A 28 GHz Broadband Low Noise Amplifier in a 130 nm BiCMOS Technology for 5G Applications," in *Proc. International Microwave and Radar Conference (MIKON)*, 2020, pp.192-195.

- [25] Janusz Grzyb, Pedro Rodriguez Vazquez, Neelanjan Sarmah, Wolfgang Förster, Bernd Heinemann, and Ullrich Pfeiffer, "High Data-Rate Communication Link at 240 GHz with On-Chip Antenna-Integrated Transmitter and Receiver Modules in SiGe HBT Technology," in *Proc. European Conference on Antennas and Propagation (EUCAP)*, 2017.

- [26] E. Ragonese, A. Scuderi, and G. Palmisano, "A 0.13-µm SiGe BiCMOS LNA for 24-GHz Automotive Short-Range Radar," in *Proc. EuMA*, Oct. 2017, pp.1537-1540.

- [27] Hugo Veenstra, Edwin van der Heijden, Marc Notten, and Guido Dolmans, "A SiGe BiCMOS UWB Receiver for 24 GHz Short-Range Automotive Radar Applications," in *Proc. IEEE/MTT-S International Microwave Symposium*, pp. 1791-1794, 2007.

- [28] Toru Masuda, Takahiro Nakamura, Masamichi Tanabe, Nobuhiro Shiramizu, Shin'ichiro Wada, Takashi Hashimoto, and Katsuyoshi Washio," SiGe HBT based 24-GHz LNA and VCO for Short-Range Ultra-Wideband Radar Systems," in *Proc. IEEE Asian Solid-State Circuits Conference*, pp.425-428, 2005.

- [29] E. van der Heijden, H. Veenstra, and R. Havens, "16-26 GHz Low Noise Amplifier for short-range automotive radar in a production SiGe:C technology," in *Proc. Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems*, pp.241-244, 2007.

- [30] Efe Öztürk, Uroschanit Yodprasit, Dietmar Kissinger, Wolfgang Winkler, and Wojciech Debski, "A Master/Slave 55.5 64.8 GHz 4x4 FMCW Radar Transceiver in 130 nm SiGe BiCMOS for Massive MIMO Applications," in *Proc. IEEE MTT-S International Microwave Symposium (IMS)*, pp.683-686, 2019.

- [31] Saeed Zeinolabedinzadeh, Ahmet C. Ulusoy, Farzad Inanlou, Hanbin Ying, Yunyi Gong, Zachary E. Fleetwood, Nicolas J.-H. Roche, Ani Khachatrian, Dale McMorrow, Stephen P. Buchner, Jeffrey H. Warner, Pauline Paki-Amouzou, and John D. Cressler, "Single-Event Effects in a Millimeter-Wave Receiver Front-End Implemented in 90 nm, 300 GHz SiGe HBT Technology," *IEEE Trans. on Nuclear Science*, vol. 64, no. 1, pp. 536-543, Jan. 2017.

- [32] J. Böck and R. Lachner, "SiGe BiCMOS and eWLB Packaging Technologies for Automotive Radar Solutions" in *Proc. IEEE MTT-S International Conference on Microwaves for Intelligent Mobility*, 2015.

- [33] Li Wang, Srdjan Glisic, Johannes Borngraeber, Wolfgang Winkler, and J. Christoph Scheytt, "A Single-Ended Fully Integrated SiGe 77/79 GHz Receiver for Automotive Radar," *IEEE J. Solid-State Circuits*, vol. 43, no. 9, pp.1897-1908, Sep. 2008.

- [34] Kiat Seng Yeo, Kok Meng Lim, Jiangmin Gu, Jinna Yan, Keping Wang, Yang Lu, Renjing Pan, Wei Meng Lim, and Jian-Guo Ma," A Fully Integrated 0.18 μm SiGe BiCMOS Low Power 60 GHz Receiver & Transmitter for High Data Rate Wireless Communications," in *Proc. IEEE International Conference of Electron Devices and Solid-State Circuits*, 2011.

- [35] Florian Vogelsang, David Starke, Jonathan Wittemeier, Holger Rucker, and Nils Pohl, "A Highly-Efficient 120 GHz and 240 GHz Signal Source in A SiGe-Technology," in *Proc. IEEE BCICST*, 2020.

- [36] Efe Öztürk, Dieter Genschow, Uroschanit Yodprasit, Berk Yilmaz, Dietmar Kissinger, Wojciech Debski, and Wolfgang Winkler, "A 120 GHz SiGe BiCMOS Monostatic Transceiver for Radar Applications," in *Proc. EuMA*, Sep. 2018, pp. 41-44.

- [37] Stefan Shopov, Juergen Hasch, Pascal Chevalier, Andreia Cathelin, and Sorin P. Voinigescu, "A 240 GHz Synthesizer in 55nm SiGe BiCMOS," in *Proc. IEEE Compound Semiconductor Integrated Circuit Symposium* (CSICS), 2015

- [38] Mikko Hietanen, Sumit Pratap Singh, Timo Rahkonen, and Aarno Pärssinen, "Noise Consideration of Radio Receivers Using Silicon Technologies Towards 6G Communication", in *Proc. Joint European Conference on Networks and Communications & 6G Summit (EuCNC/6G Summit): Components and Microelectronics (CME)*, pp,514-519, 2021.

- [39] Hao Gao, "Silicon-based sub-THz PA for Wireless Communication," in *Proc. International Conference on IC Design and Technology (ICICDT)*, Sep. 2021.

- [40] Peter Magnée, Domine Leenaerts, Mark van der Heijden, Thanh Viet Dinh, Ivan To, Ihor Brunets, "The future of SiGe BiCMOS: bipolar amplifiers for high-performance millimeter-wave applications," in *Proc.* IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS)", 2021.

- [41] Xiong Zhang, Payam Mehr, and Trevor J. Thornton, "Self-Heating in 40 nm SOI MOSFETs on High Resistivity, Trap-Rich Substrates," IEEE Trans on Nanotechnology, Vol. 19, pp.42-46, 2020.

- [42] Mohammad Khorshidian and Harish Krishnaswamy, "A Fully-Integrated 2.6GHz Stacked Switching Power Amplifier in. 45nm SOI CMOS with >2W Output Power and 43.5% Efficiency," in Proc. IEEE/MTT-S International Microwave Symposium, pp.323-326, 2019.

- [43] F. Gianesello, D. Gloria, C. Raynaud, S. Montusclat, S. Boret, C. Clement, C. Tinella, Ph. Benech, J.M. Fournier, and G. Dambrine, "State of the art integrated millimeter wave passive components and circuits in advanced thin SOI CMOS technology on High Resistivity substrate," in Proc. IEEE International SOI Conference, pp. 52-53, 2005.

- [44] Shyam Parthasarathy, Xi Sung Loo, Jen Shuang Wong, Tao Sun, Rui Tze Toh, Shaoqiang Zhang, Kok Wai Chew, and Purakh Raj Verma, "A Novel Device for Low Noise Amplification in 130nm High Resistivity RFSOI Technology Platform," in Proc. IEEE 17th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), pp.97-99, 2017.

- [45] Venkata Narayana and Rao Vanukuru, "Design and Implementation of 5.8 GHz LC Bandpass Filter in 0.18 µm HR-SOI Technology," in Proc. IEEE Asia-Pacific Microwave Conference (APMC), pp.210-212, 2019.

- [46] Takashi Hashimoto, Yusuke Nonaka, Tatsuya Tominari, Tsuyoshi Fujiwara, Tsutomu Udo, Hidenori Satoh, Kunihiko Watanabe, Tomoko Jimbo, Hiromi Shimamoto, and Satoru Isomura, "A flexible 0.18 μm BiCMOS technology suitable for various applications," *IEEE J. Electron Devices Soc.*, vol. 1, no. 11, Nov. 2013, pp. 181-190.

- [47] M. A. Polinsky, O. Schade Jr., and J. P. Keller, "CMOS-Bipolar Monolithic Integrated-Circuit Technology," in *Proc. IEEE IEDM*, 1973, pp. 229-231.

- [48] H. Higuchi, G. Kitsukawa, T. Ikeda, Y. Nishio, N. Sasaki, and K. Ogiue, "Performance and Structures of Scaled-Down Bipolar Devices Merged with CMOSFETS," in *Proc. IEEE IEDM*, 1984, pp. 694-697.

- [49] A. Watanabe, T. Ikeda, T. Nagano, N. Momma, Y. Nishio, N. Tamba, M. Odaka, and K. Ogiue, "High Speed BiCMOS VLSI Technology with Buried Twin Well Structure," in *Proc. IEEE IEDM*, 1985, pp. 423-426.

- [50] A. R. Alvarez, "Future Trends in BiCMOS Technology," in *Proc. ESSDERC*, 1991, pp. 493–500.

- [51] A. Watanabe, T. Nagano, S. Shukuri, and T. Ikeda, "Future BiCMOS Technology for Scaled Supply Voltage," in *Proc. IEEE IEDM*, 1985, pp. 429-432.

- [52] T. Nakamura and H. Nishizawa, "Recent Progress in Bipolar Transistor Technology," *IEEE Trans. Electron Devices*, vol. 42, no. 3, pp. 390-398, Mar. 1995.

- [53] T. Hiramoto, T. Tamba, M. Yoshida, T. Hashimoto, T. Fujiwara, K. Watanabe, M. Odaka, M. Usami, and T. Ikeda, "A 27 GHz Double Poly-Silicon Bipolar Technology on Bonded SOI with Embedded 58 μm² CMOS Memory Cells for ECL-CMOS SRAM Applications," in *Proc. IEEE IEDM*, 1992, pp. 39-42.

- [54] K. Higeta, M. Usami, M. Ohayashi, Y. Fujimura, M. Nishiyama, S. Isomura, K. Yamaguchi, Y. Idei, H. Nambu, K. Ohhata, and N. Hanta, "A Soft-Immune 0.9-ns 1.15-Mb ECL-CMOS SRAM with 30-ps 120K Logic Gates and On-Chip Test Circuitry," *IEEE J. Solid-State Circuits*, vol. 31, no. 10, pp. 1443-1450, Oct. 1996.

- [55] T. Yamaguchi, S. Uppili, J. S. Lee, G. H. Kawamoto, T. Dousluoglu, and S. Simpkins, "Process and Device Characterization for a 30-GHz  $f_T$  Sub micrometer Double Poly-Si Bipolar Technology Using BF<sub>2</sub>- Implanted Base with Rapid Thermal Process," *IEEE Trans. Electron Devices*, vol. ED-40, no. 8, pp. 1484-1495, Aug. 1993.

- [56] T. Kikuchi, Y. Onishi, T. Hashimoto, E. Yoshida, H. Yamaguchi, S. Wada, N. Tamba, K. Watanabe, Y. Tamaki, and T. Ikeda, "A 0.35 μm ECL-CMOS Process Technology on SOI for 1ns Mega-bits SRAM's with 40 ps Gate Array," in *Proc. IEEE IEDM*, 1995, pp. 923-926.

- [57] Tohru Nakamura, Kazuo Nakazato, Katsuyoshi Washio, Yoichi Tamaki, and Mitsuo Namba, "Advanced Self-Alignment Technologies and Resulting Structures of High-Speed Bipolar transistors," Ultra-Fast Silicon Bipolar Technology, Springer-Verlag, pp.95-110.

- [58] T. Hashimoto, T. Kikuchi, K. Watanabe, N. Ohashi, T. Saito, H. Yamaguchi, S. Wada, N. Natsuaki, M. Kondo, S. Kondo, Y. Homma, N. Owada, and T. Ikeda, "A 0.2-μm Bipolar-CMOS Technology on Bonded SOI with Copper Metallization for Ultra-High-Speed Processors," in *Proc. IEEE IEDM*, 1998, pp. 209-212.

# 2. BiCMOS Maintaining Compatibility with Standard CMOS Processes

#### 2.1 Introduction

Because the power supply voltage of CMOS and  $f_T$  of SiGe HBT required by the application are different, the SiGe BiCMOS process of a combination of CMOS and SiGe HBT has been newly developed for each new significant product development. On the other hand, it has been necessary to prepare device parameters for circuit simulation, the description of the vertical structure of wiring, and design verification rules for layout design as the PDKs for circuit designers for each process. In addition, Intellectual Property (IP) for product design, such as CMOS standard logic cells and standard input/output circuits, has been prepared in parallel with device process development. Therefore, when the device parameters of CMOS change in a new BiCMOS process, it is necessary to develop a new IP, including re-characterization in the CMOS standard logic cell, leading to an increase in development cost and development time. In addition, the diversification of CMOS circuits along with the fine process has increased the number of preparation steps for IP for design. BiCMOS process designs that do not change from the device parameters and design rules in the original CMOS process have become crucial for these reasons.

Although there have been technical papers emphasizing compatibility with standard CMOS technology when developing new SiGe BiCMOS technology [1][2][3], the process methodology to ensure compatibility has yet to be detailed. When the temperature in the bipolar formation process is lowered not to affect the MOS characteristics, the challenges are not to degrade the performance of the bipolar transistor from that of the bipolar single process and not to affect the yield and reliability of devices.

#### 2.2 The 0.18 µm SiGe BiCMOS Process in This Study

#### 2.2.1 Challenges in the 0.18 µm SiGe BiCMOS Process Technology

In this study, in addition to developing a SiGe BiCMOS process that simultaneously equipped SiGe HBT and 0.18 µm node CMOS, the purpose was to confirm that there was a scalability that could also be applied to the 0.15 µm node and 0.13 µm node [4][5]. This study addressed the following challenges associated with fine CMOS processes.

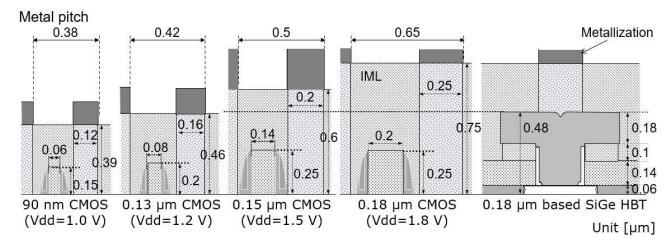

#### (i) Maintaining the gate pitch of the standard CMOS in the BiCMOS process

Although the gate pitch of BiCMOS was more expansive than that of the standard CMOS of the same generation up to the 0.25 µm node that was the conventional BiCMOS technology, the gate pitch in this study became the same as that of the CMOS of the same generation. The issue was that the interlayer dielectric became thinner as the contact pitch became shorter following the fine process development progressed. The height of the SiGe HBT with a two-layer poly-Si emitter structure had to be brought closer to the height of the MOS gate with a single-layer poly-Si structure. In addition, there was concern that the SiGe HBT device size

would increase and affect the SiGe HBT characteristics by changing the layout rule that prioritized bipolar transistors to prioritize MOS.

#### (ii) Higher temperature and shorter final RTA as progressing the CMOS fine process

(Study contents will be described in Chapter 4)

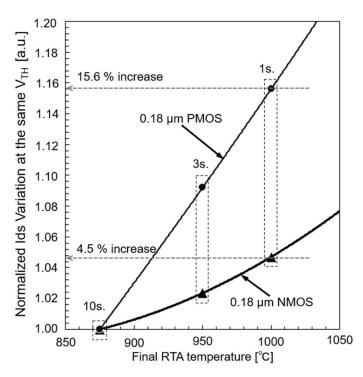

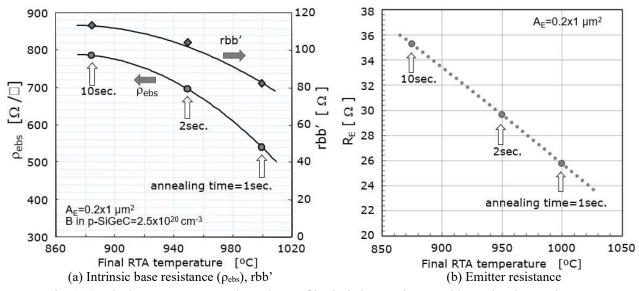

The temperature of the final RTA was raised as the CMOS generation progressed to reduce the sheet resistance of the heavily doped S/D regions, and the RTA time was shortened to suppress impurity diffusion (Table 2.1). In the case of the 0.18  $\mu$ m generation, raising the temperature from 875 °C to 1000 °C increased the impurities' activation rate and reduced the diffusion layer's resistivity. To these results, the S/D current (I<sub>DS</sub>) increased by 4.5 % for NMOS and 15.6 % for PMOS (Fig. 2.1). However, raising the temperature of the final RTA in the BiCMOS process raised concerns about a decrease in Emitter-Base (EB) breakdown voltage (BV<sub>EBO</sub>) due to enhanced diffusion of high-concentration phosphorus from the emitter poly-Si electrode and a reduction in  $f_T$  due to boron diffusion in the intrinsic base layer.

Table 2.1. Comparison of final annealing conditions by generation

| node    | Final RTA condition |

|---------|---------------------|

| 0.25 µm | 875 °C, 10 sec.     |

| 0.18 µm | 950 °C, 3 sec.      |

| 0.13 µm | 1000 °C, 1 sec.     |

| 90 nm   | 1050 °C, < 1 sec.   |

Fig. 2.1. Final RTA temperature dependence on  $I_{DS}$  of 0.18  $\mu m$  MOS. An increase in  $I_{DS}$  was plotted from the value at 875 °C. Annealing time was adjusted so that each condition's thermal budget was the same.  $I_{DS}$  values were normalized to that at the same  $V_{TH}$  for different annealing temperatures [14].

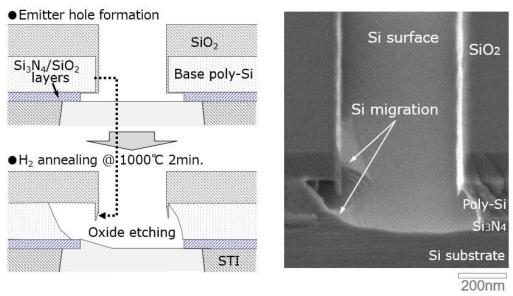

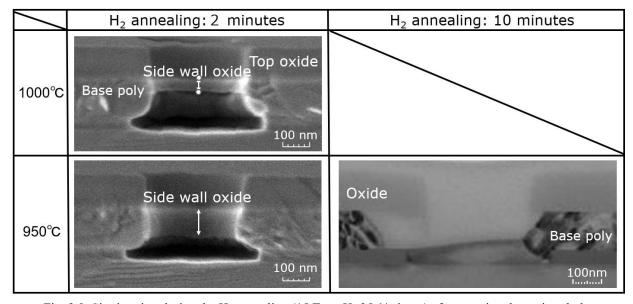

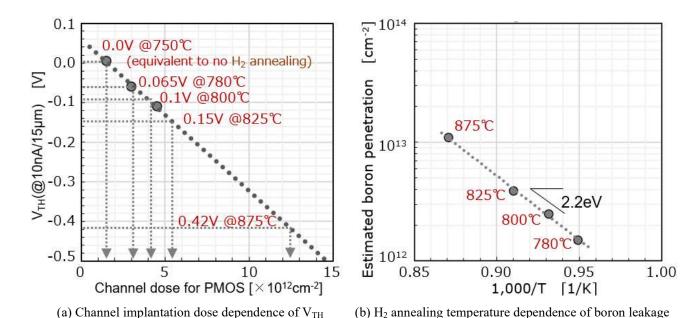

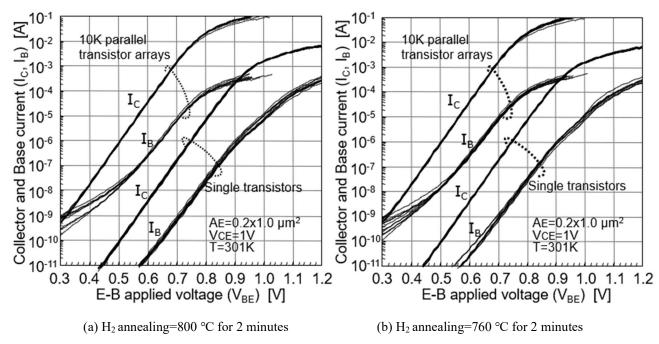

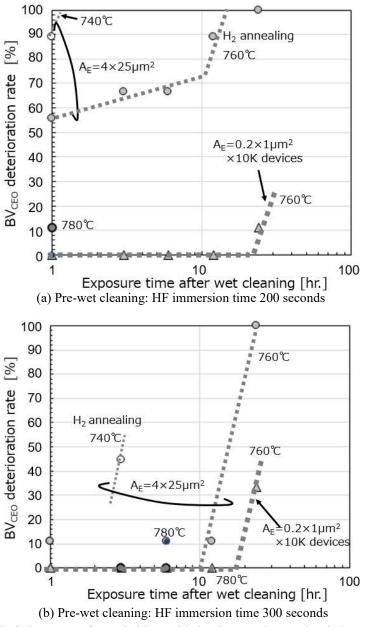

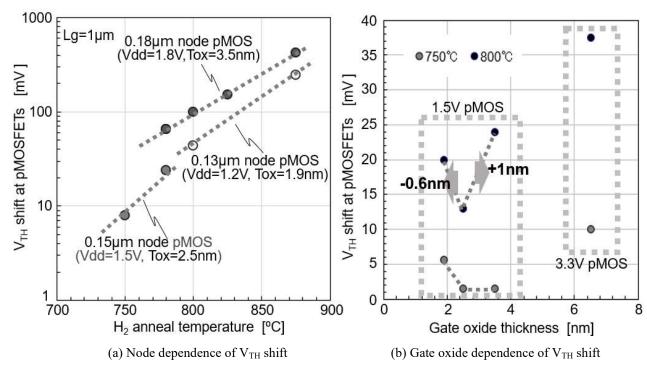

# (iii) Low-temperature H<sub>2</sub> annealing before the SiGe epitaxial growth to prevent boron penetration from the p-type gate

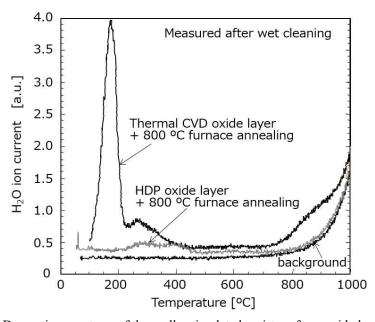

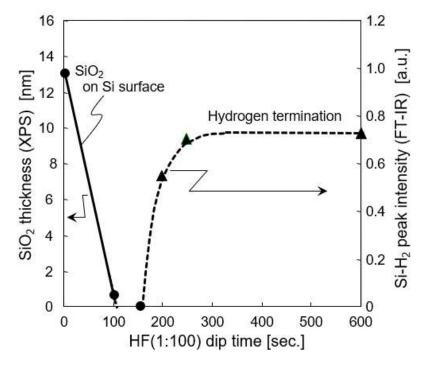

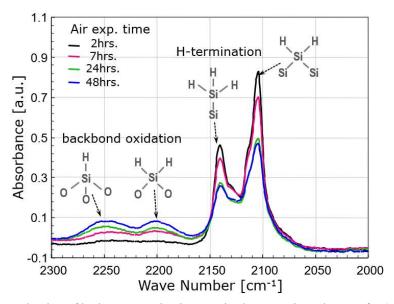

PMOS up to the 0.25 µm generation has used n-type gates that induce a buried channel structure with a depleted channel. However, the p-type gates have been applied to the surface channel PMOS from the 0.18 µm generation to improve the short-channel characteristics. Therefore, suppression of boron penetration from the p-type gate through the thin gate oxide layer became an issue. The first countermeasure was a reduction of the thermal budget in the HBT formation process to maintain the short channel characteristics. On the other hand, it was also known that H<sub>2</sub> annealing to remove carbon and oxygen from the substrate surface before the SiGe epitaxial growth could promote boron diffusion [6]. It had been initially considered that there would be no influence on the MOS gate because a 50-nm-thick nitride layer and a 125-nm-thick oxide layer were covering the MOS gate. Still, the influence was so significant that it was necessary to take measures against enhanced boron diffusion by the H<sub>2</sub> annealing.

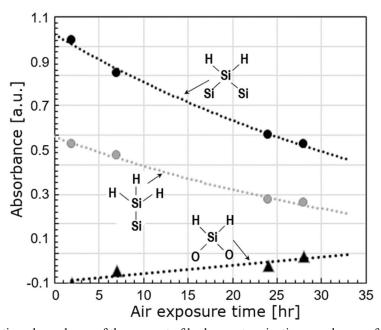

Regarding this issue, it was necessary to consider maintaining hydrogen termination to suppress natural oxide layer growth on the Si substrate. Si dangling bonds on the substrate surface are terminated by hydrogen atoms during dilute hydrofluoric acid wet cleaning, temporarily suppressing the formation of a natural oxide layer. Stable hydrogen termination is essential for lowering the temperature of the H<sub>2</sub> annealing. It became necessary to clarify the stable hydrogen termination formation conditions before SiGe epitaxial growth.

## (iv) Minimize the thermal budget of SiGe HBT formation to prevent degradation of the CMOS short channel characteristics

Maintaining the short channel characteristics has become challenging in the CMOS fine process, so the Halo structure has been adopted from the 0.18 µm CMOS. Therefore, the conditions to suppress the thermal budget for forming SiGe HBTs to maintain the short channel characteristics of CMOS have been becoming stricter along with the CMOS fine process. It was investigated that the reduction of thermal budget to form SiGe HBTs so as not to affect the short channel characteristics of CMOS in this study.

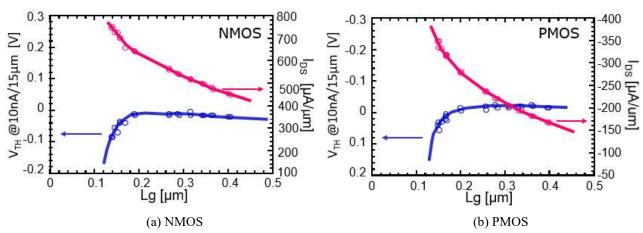

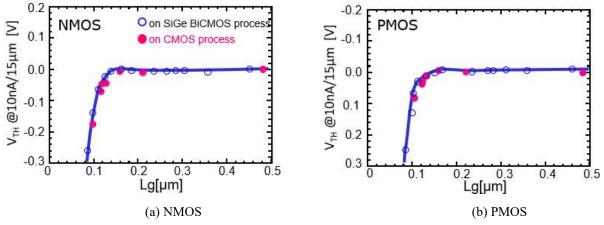

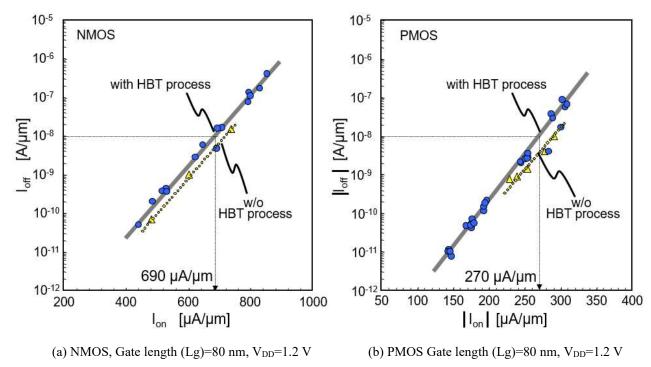

In the 0.18  $\mu$ m SiGe BiCMOS technology for being applied to the 43 Gbps optical communication semiconductor chip, the drain currents of NMOS and PMOS were increased to 660  $\mu$ A/ $\mu$ m and 295  $\mu$ A/ $\mu$ m respectively by lowering V<sub>TH</sub> to handle 2.7-Gbps signal in CMOS circuits [5]. Further fine CMOS is needed for high-speed signal processing, and it is necessary to confirm the scalability that this technology, which was researched and developed based on the 0.18  $\mu$ m node, could be applied to the 0.13  $\mu$ m and 0.15  $\mu$ m nodes.

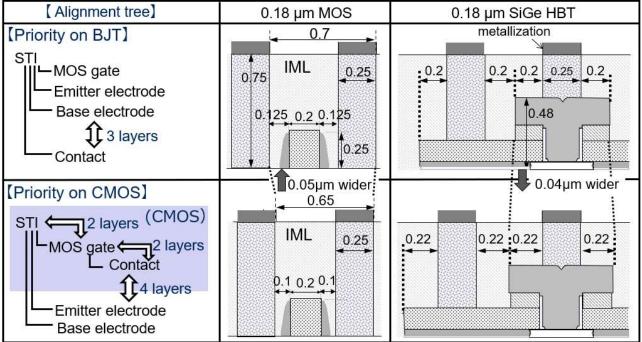

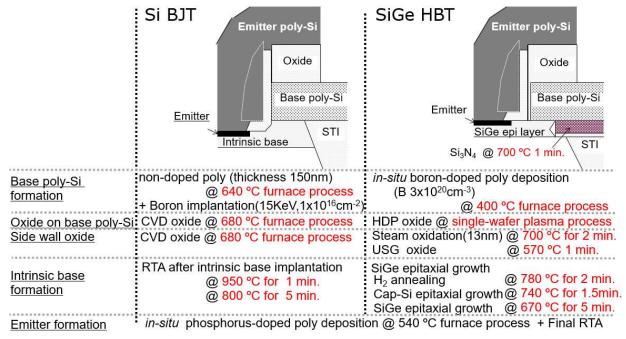

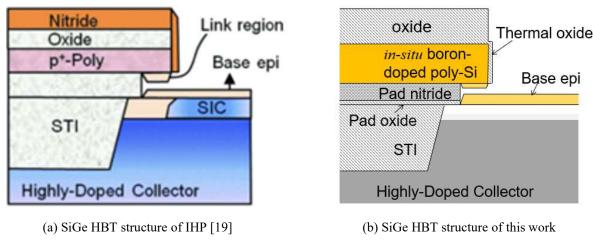

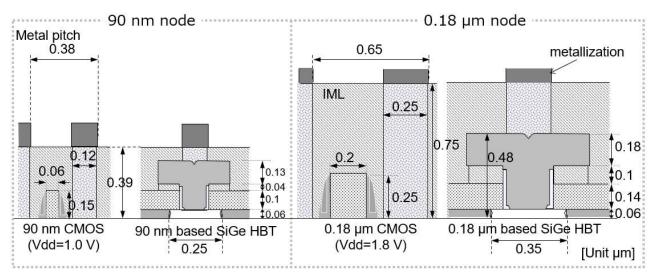

#### 2.2.2 Overview of the 0.18 µm SiGe BiCMOS Process Technology Developed in This Study

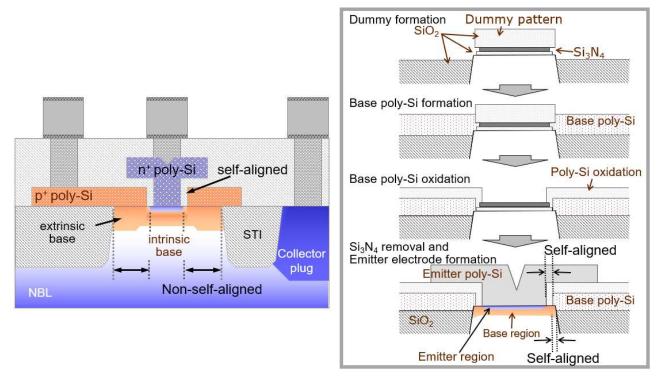

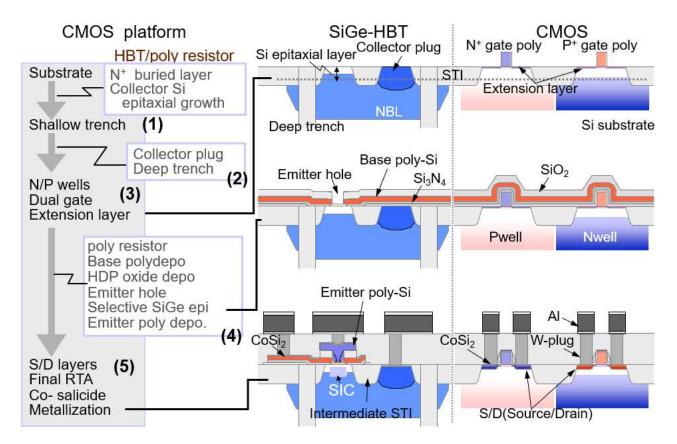

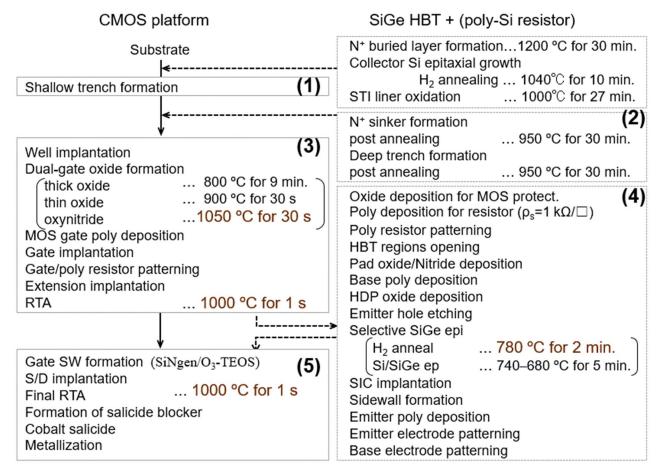

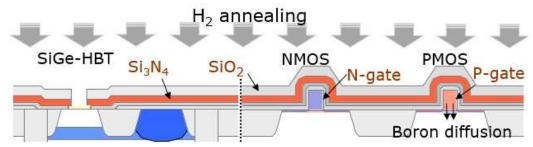

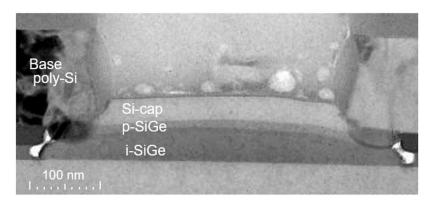

Even in conventional Si BiCMOS technology, there are two points for developing a new BiCMOS process: "Optimization of the order of processes considering the thermal budget in each process" and "Influence on processing accuracy due to level difference caused by devices structure." Therefore, the process flow has been designed to prevent interference between process modules. In the 0.18  $\mu$ m SiGe BiCMOS process developed in this study, the bipolar transistor formation process was divided into three blocks and inserted at the optimal location in the standard CMOS process (Figs. 2.2, 2.3) [4]. This was the same for the 0.13  $\mu$ m and 0.15  $\mu$ m SiGe BiCMOS, which will be described later.

#### (1) NBL(N<sup>+</sup> Buried Layer) formation (Figs. 2.2(1), 2.3(1))

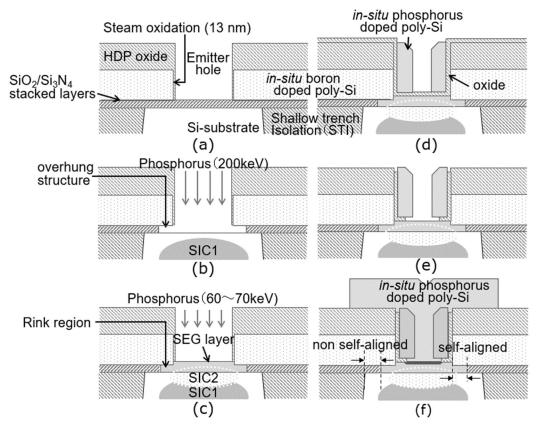

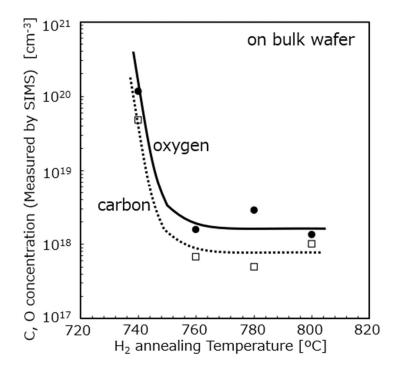

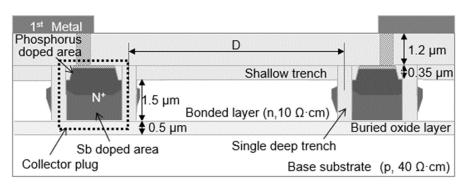

The heavy thermal processing steps for fabricating an N<sup>+</sup> buried layer (NBL), a collector Si epitaxial growth layer, collector plugs to an N<sup>+</sup> buried collector, and deep trenches were performed first. After processing the shallow trenches and forming a 30 nm thick pad oxide layer at 1000°C, an HDP oxide layer was deposited, and the STI was formed flattening by CMP (Chemical Mechanical Polishing). Directional ions shall damage the Si layer during the deposition of the HDP layer using plasma technology, but the pad thermal oxide layer absorbed the damage to the Si layer surface caused by the plasma.

#### (2) Collector plug/deep trench formation (Figs. 2.2(2), 2.3(2))

The Collector plug layer, which was the region to connect with the NBL layer, was then formed by phosphorus ion implantation at an accelerating energy of 80 keV (dose=5×10<sup>15</sup> cm<sup>-2</sup>) and annealing at 950 °C. The intermediate STI (in Fig. 2.2) was formed between a collector plug and an intrinsic base layer to thicken the oxide layer just below the extrinsic base poly-Si layer, thereby reducing the C<sub>CB</sub>. In addition, since the lateral diffusion of the collector plug was blocked by the intermediate STI, a high Collector-Base () breakdown voltage (BV<sub>CBO</sub>) was maintained even when the collector Si-epitaxial growth layer was thick.

After that, 0.4-µm-wide deep trenches were processed by dry etching in the Si substrate. The LP-CVD (<u>L</u>ow <u>Pressure-Chemical Vapor Deposition</u>) embedded the oxide layer in the deep trench at 800 °C after forming a 4-nm-thick thermal oxide layer on the sidewall at 750 °C. Both oxide layers in the STI and the deep trench were heat treated at 950 °C for 30 minutes to enhance oxide layer quality and prevent flatness deterioration due to wet etching for cleaning a substrate surface. The deep trenches were formed before MOS gate forming, although these were not related to MOS device operation, so the deep trenches, as well as STI, shall be planarized so as not to interfere

Fig. 2.2. Process flow of the 0.18 μm SiGe BiCMOS in this study [4].

with MOS gate fine pattern forming.

On the other hand, if the deep trench was widened, the substrate parasitic capacity could be reduced. However, if the deep trench was widened, the deposited oxide layer should be thickened, and there would be issues in productivity. LP-CVD deposited a total of  $1.0~\mu m$  thick oxide layer to flatten the  $0.4~\mu m$  wide trench. It meant that an oxide layer thickness should be 2.5 times thicker than the trench width. The width of the deep trench was set to  $0.4~\mu m$  also at the viewpoint of productivity.

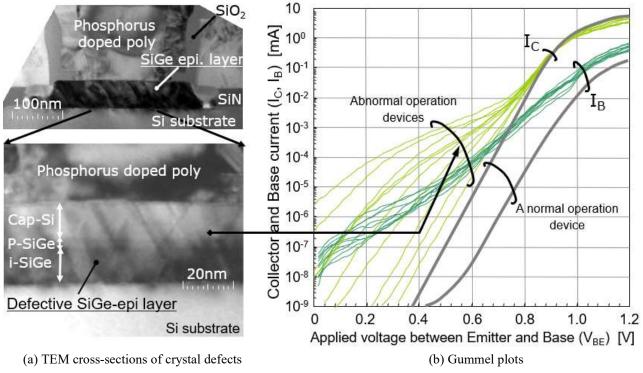

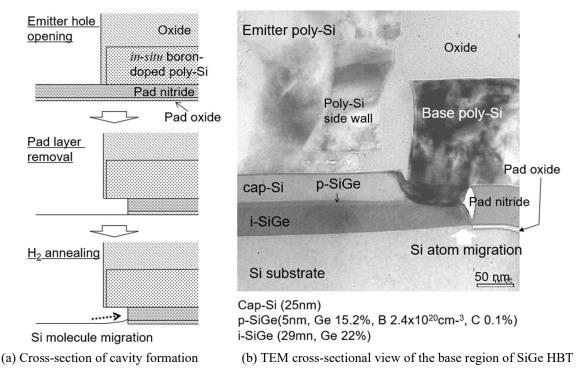

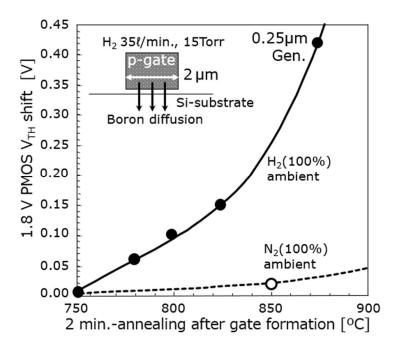

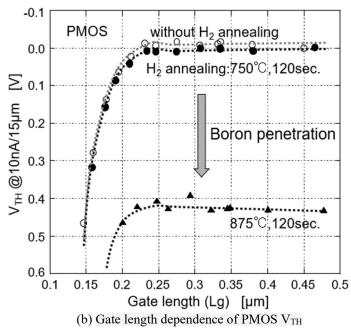

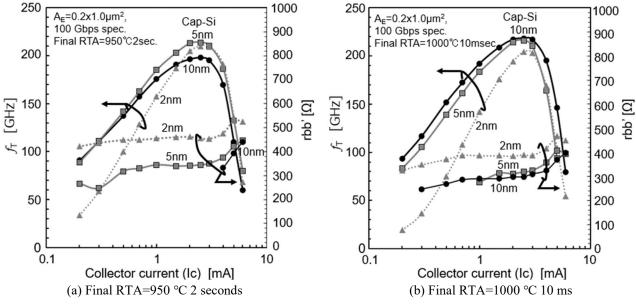

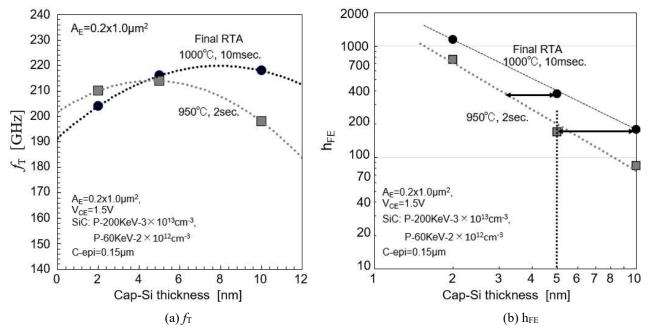

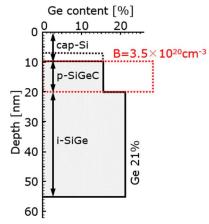

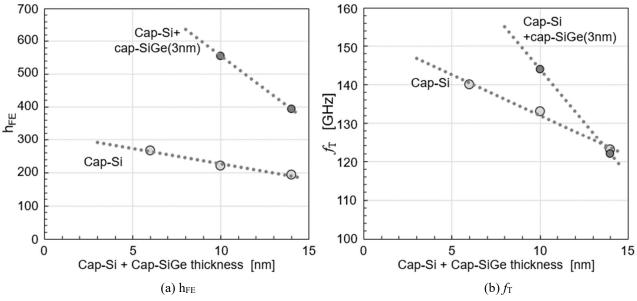

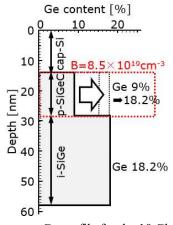

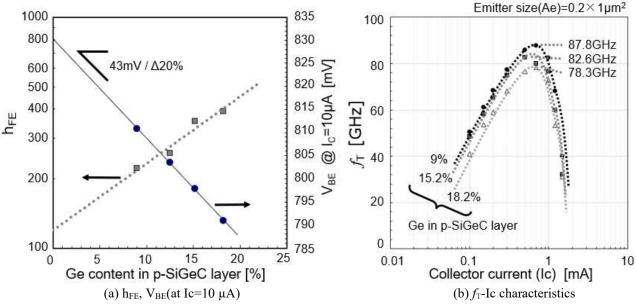

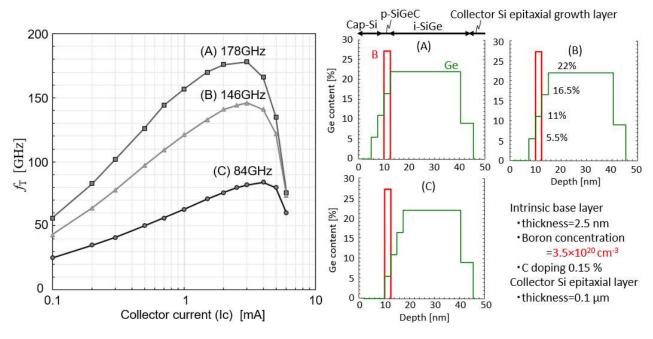

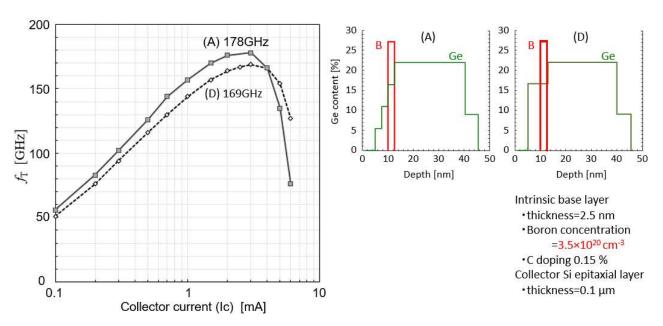

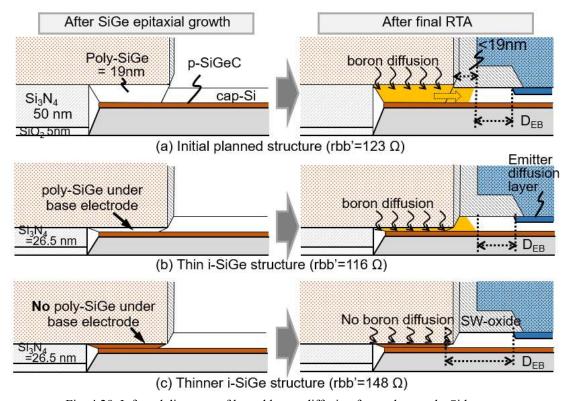

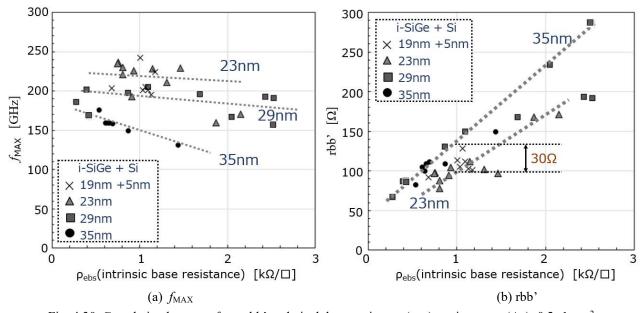

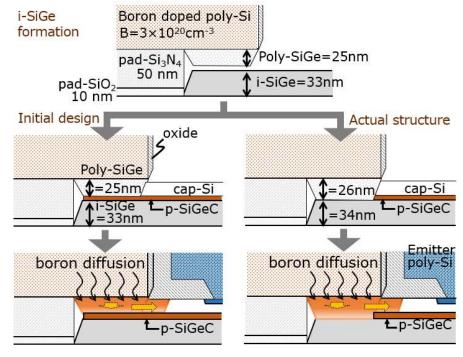

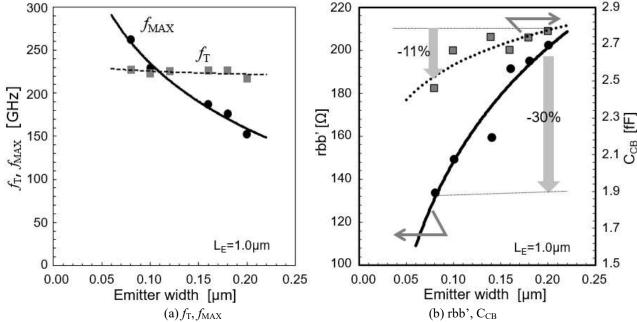

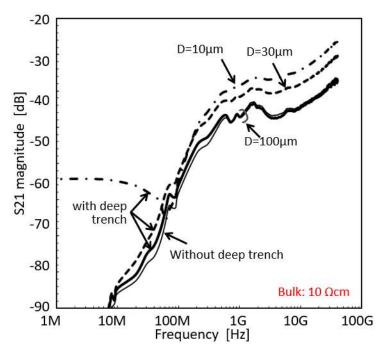

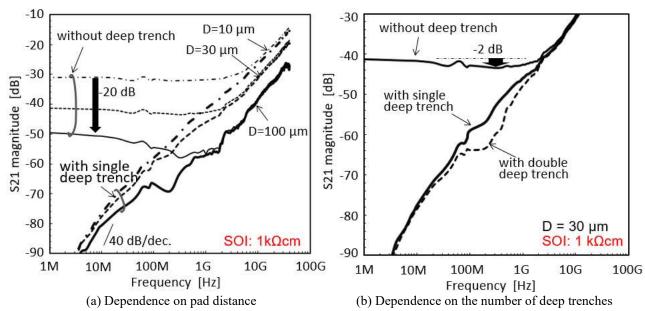

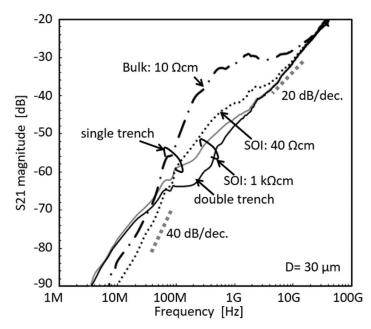

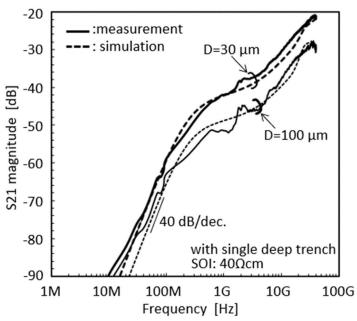

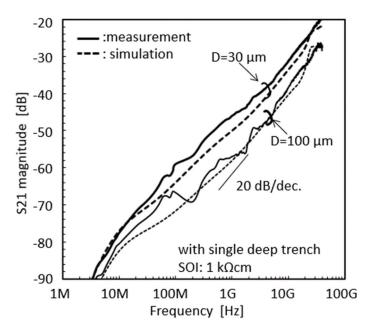

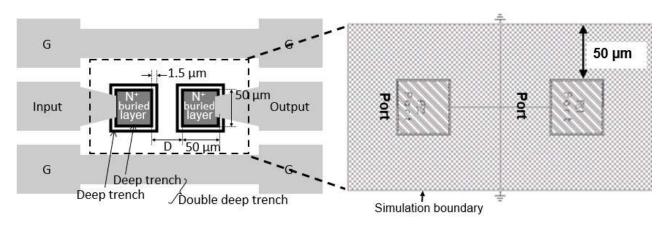

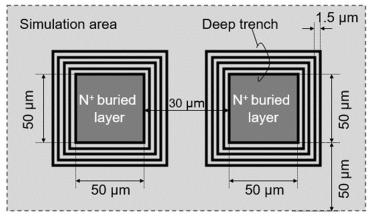

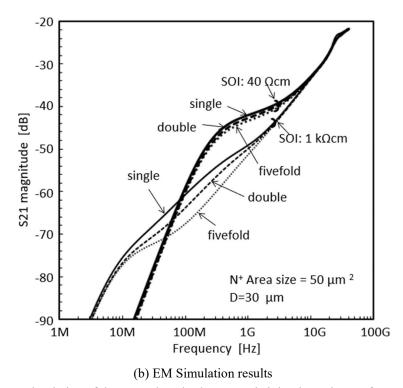

#### (3) Formation of MOS diffusion layers (Figs. 2.2(3), 2.3(3))