# T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

## 論文 / 著書情報 Article / Book Information

| 題目(和文)            | 大規模太陽光発電システムへの適用を目的とした複数の双方向チョッ<br>パを使用した三相インバータの研究                                                                                                                                             |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | Study of Three-phase Inverter Using Multiple Bidirectional Choppers Intended for Utility-scale PV Systems                                                                                       |

| 著者(和文)            | QIAOLinyue                                                                                                                                                                                      |

| Author(English)   | Linyue Qiao                                                                                                                                                                                     |

| 出典(和文)            | 学位:博士(工学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第12540号,<br>授与年月日:2023年9月22日,<br>学位の種別:課程博士,<br>審査員:萩原 誠,千葉 明,藤田 英明,浦壁 隆浩,竹内 希,清田 恭平,柿ヶ野<br>浩明                                                            |

| Citation(English) | Degree:Doctor (Engineering),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第12540号,<br>Conferred date:2023/9/22,<br>Degree Type:Course doctor,<br>Examiner:,,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                            |

| Type(English)     | Doctoral Thesis                                                                                                                                                                                 |

## 東京工業大学 Tokyo Institute of Technology

## 工学院 School of Engineering

電気電子系

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

## Study of Three-phase Inverter Using Multiple Bidirectional Choppers Intended for Utility-scale PV Systems

Author

Linyue QIAO

Supervisor

Makoto Hagiwara

August 1, 2023

## **Dedication**

This dissertation is completed with help from my supervisor and my best friends in my laboratory and support from my family. I did not know why I came so far, but now I feel I can move further. To every important people in my life so far, I appreciate your accompany.

## Abstract

This dissertation presents a detailed study of a novel three-phase inverter for utility-scale PV systems where multiple cascaded bidirectional chopper cells and a three-phase line-frequency transformer with a three-limb core are used. The proposed inverter can achieve a wider MPPT operation voltage range. In addition, the elimination of the high-frequency circulating current under the simultaneous parallel operation of inverters is also achieved. Two different control methods are carried out and tested successively to increase the stability of the entire circuit. Meanwhile, the initial charging of the floating capacitors is also achieved for the inverter operation. Furthermore, the LVRT capability of the proposed inverter under the grid fault is addressed, and the theoretical analysis and the experimental verification are carried out. In the end, the evaluation of chopper-cell number of the proposed inverter is conducted based on experimental verification and mathematical analysis.

## Acknowledgments

If you ask me 'Should I pursue a PhD degree?' for 100 times, I will give you the same answer 'Think carefully. It is not what you think.' every time. This journey is long and lonely. However, I am glad that I am lucky enough to have so many people that will help me when I feel lost.

Associate Professor Makoto Hagiwara (萩原 誠), my first mentor and advisor in Japan. Thank you for accepting me to the Hagiwara Lab even though my major was different from your research topics. I have to say I never know a professor like you that will help the students that much in both life and research. Without you, I will be still wandering and end up in nowhere.

Assistant Professor **Kenichiro Sano** (佐野 憲一朗), offered me many advices when I was doing the job hunting. As an international student, I know nothing about Japanese academy and manufacturers. Thank you for telling me your career path and sharing your experience with me.

Professor **Hideaki Fujita** (藤田 英明), will ask me some difficult questions sometimes to make me realize that I am still far away from understanding the entire research topic. You taught me that a researcher should not only focus on his own research. Instead, a research should learn as much as he can and pay attention to the difference between theory and practice, which is a very useful advice.

Dr. Nikola Krneta, my best friend in the laboratory. We have similar background and interests. During these three years, we helped each other and he helped me more, frankly. Thank you for giving me advices on my research and teaching me many things I did not know. I will miss the days we worked in lab and played games together.

## Contents

| Li | st of                | Abbre   | eviations                                       | xix        |

|----|----------------------|---------|-------------------------------------------------|------------|

| N  | omer                 | ıclatur | e x                                             | xiii       |

| 1  | Intr                 | oducti  | ion                                             | 1          |

|    | 1.1                  | Resear  | rch Background                                  | 1          |

|    |                      | 1.1.1   | Development of PV Energy                        | 1          |

|    |                      | 1.1.2   | Conventional PV Inverter                        | 5          |

|    |                      | 1.1.3   | The MMCC                                        | 8          |

|    |                      |         | 1.1.3.1 Application of the SSBC                 | 8          |

|    |                      |         | 1.1.3.2 Application of the SDBC                 | 10         |

|    |                      |         | 1.1.3.3 Application of the DSCC and the DSBC    | 11         |

|    | 1.2                  | Resear  | rch Objectives                                  | 11         |

|    | 1.3                  | Disser  | tation Outline                                  | 12         |

| 2  | ${ m Lit}\epsilon$   | erature | e Review                                        | 15         |

|    | 2.1                  | Topolo  | ogies of PV Inverters                           | 15         |

|    |                      | 2.1.1   | Single-stage Inverters                          | 16         |

|    |                      | 2.1.2   | Multiple-stage Inverters                        | 17         |

|    |                      | 2.1.3   | Gradational Voltage Inverters                   | 19         |

|    | 2.2                  | LVRT    | Capability of MMCC Topologies                   | 19         |

|    | 2.3                  | Loss a  | and Cost Decreasing of MMCC Topologies          | 22         |

|    | 2.4                  | Concl   | usion                                           | 23         |

| 3  | $\operatorname{Thr}$ | ee-pha  | ase PV Inverter with Conventional d-q-0 Control | <b>2</b> 5 |

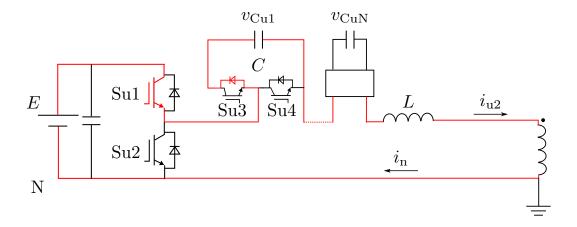

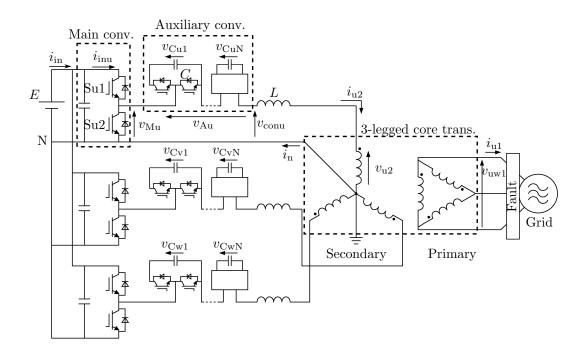

|    | 3.1                  | Propo   | sed Circuit Configuration                       | 25         |

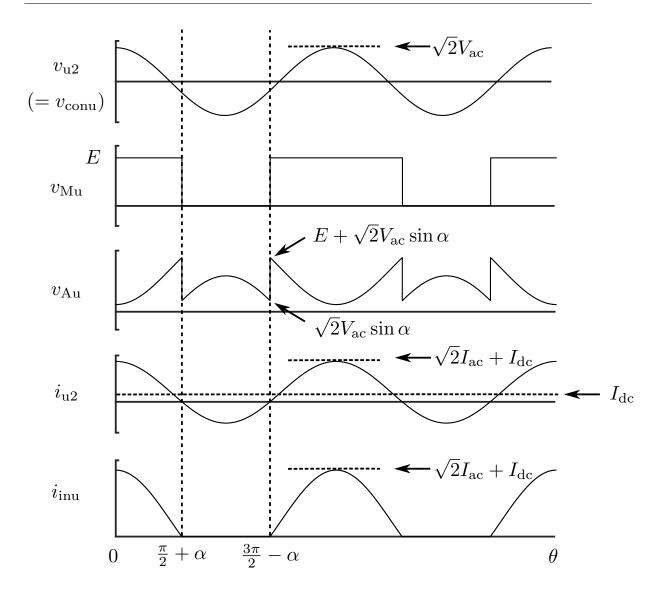

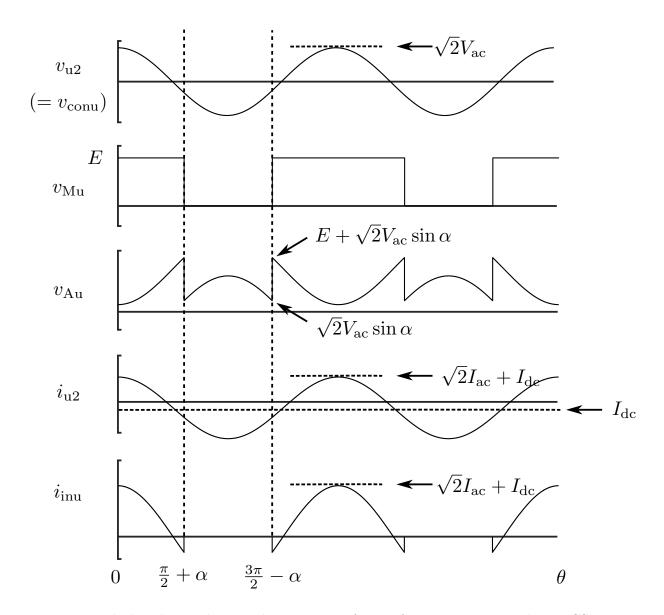

|   | 3.2 | Opera   | tion Principles                                            | 28 |

|---|-----|---------|------------------------------------------------------------|----|

|   |     | 3.2.1   | Operation Principles of Main Converter                     | 29 |

|   |     | 3.2.2   | Operating Principles of Auxiliary Converter                | 31 |

|   |     | 3.2.3   | Derivation of $\alpha$                                     | 33 |

|   |     |         | 3.2.3.1 Case of Low DC Input Voltage                       | 33 |

|   |     |         | 3.2.3.2 Case of High DC Input Voltage                      | 35 |

|   |     |         | 3.2.3.3 Conclusion                                         | 36 |

|   |     | 3.2.4   | Comparison of Minimum DC Input Voltage                     | 36 |

|   | 3.3 | Contro  | ol Method                                                  | 37 |

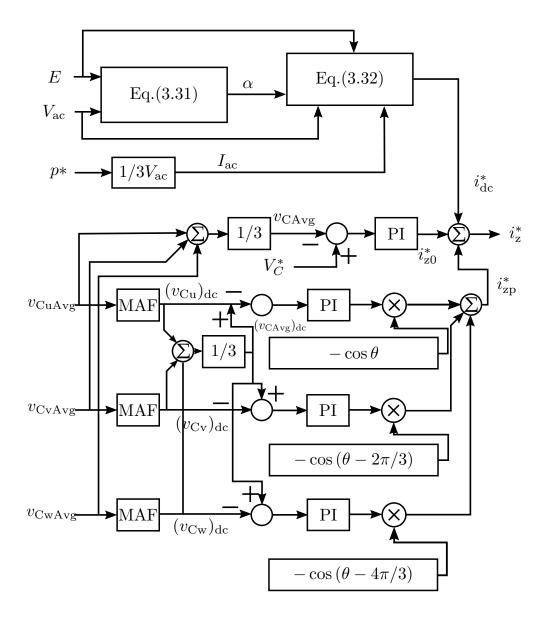

|   |     | 3.3.1   | Feedforward Control of $D_{\mathrm{M}}$                    | 37 |

|   |     | 3.3.2   | DC-capacitor Voltage Control                               | 38 |

|   |     |         | 3.3.2.1 Overall Voltage Control                            | 39 |

|   |     |         | 3.3.2.2 Cluster Balancing Control                          | 40 |

|   |     |         | 3.3.2.3 Individual Balancing Control                       | 40 |

|   |     |         | 3.3.2.4 Inductor Current Control                           | 41 |

|   |     |         | 3.3.2.5 Output Voltage Calculation of Auxiliary Converter  | 42 |

|   | 3.4 | Exper   | imental Verification                                       | 42 |

|   |     | 3.4.1   | Experimental Conditions                                    | 42 |

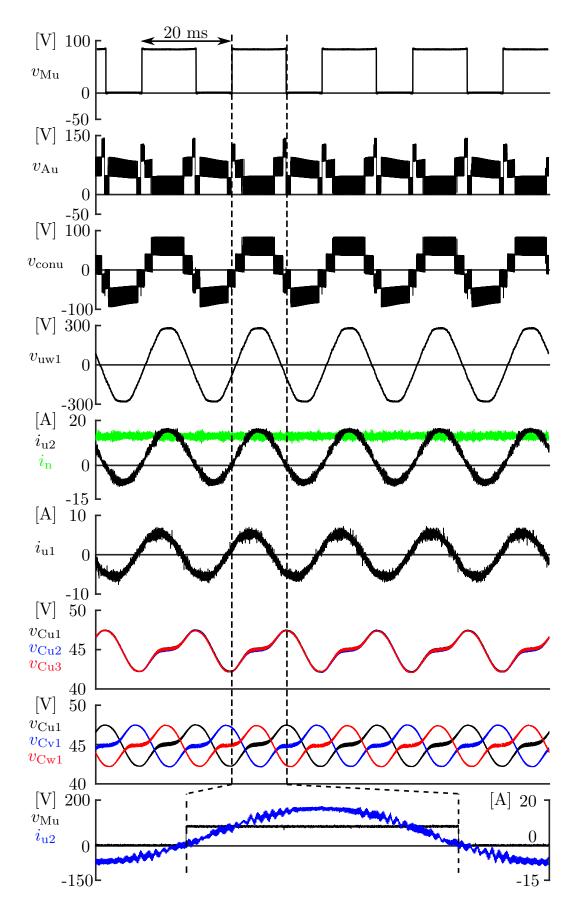

|   |     | 3.4.2   | Steady-state Performance with d-q-0 Control                | 44 |

|   |     | 3.4.3   | Transient-state Performance with d-q-0 Control             | 46 |

|   | 3.5 | Conclu  | usion                                                      | 51 |

| 4 | Ind | ividual | l Current Control and Performance Verification of Proposed | I  |

| _ |     |         | ase PV Inverter                                            | 53 |

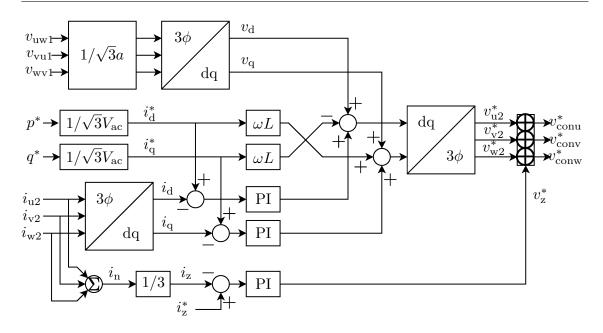

|   | 4.1 | Contro  | ol Method Based On Individual Current Control              | 53 |

|   |     | 4.1.1   | DC-capacitor Voltage Control                               |    |

|   |     |         | 4.1.1.1 Phase DC-capacitor Voltage Control                 |    |

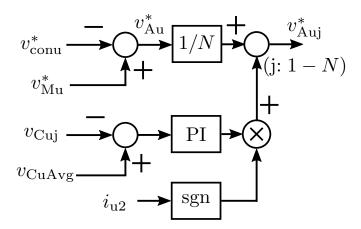

|   |     |         | 4.1.1.2 Individual Balancing Control                       | 56 |

|   |     | 4.1.2   | Inductor Current Control                                   | 56 |

|   |     |         | 4.1.2.1 Phase Compensation                                 |    |

|   |     |         | 4.1.2.2 Output Voltage Calculation of Auxiliary Converter  |    |

|   | 4.2 | Exper   | imental Verification                                       |    |

|   |     |         |                                                            |    |

|   |     | 4.2.1              | Experimental Conditions                                             | . 58         |

|---|-----|--------------------|---------------------------------------------------------------------|--------------|

|   |     | 4.2.2              | Initial Charging of DC-capacitor Voltage                            | . 59         |

|   |     | 4.2.3              | Active Power Control Steady-State Performance                       | . 62         |

|   |     | 4.2.4              | Active Power Control Transient-state Performance                    | . 69         |

|   |     | 4.2.5              | Reactive Power Control Steady-state Performance                     | . 71         |

|   |     | 4.2.6              | THD Performance of Downscaled Model                                 | . 71         |

|   | 4.3 | Loss a             | and Efficiency Analysis                                             | . 71         |

|   | 4.4 | Concl              | usion                                                               | . 79         |

| 5 | LVI | RT Ca <sub>l</sub> | pability Analysis of Proposed PV Inverter                           | 83           |

|   | 5.1 | Theor              | etical Analysis of Capacitor Voltage Fluctuation During SLG Fault   | . 84         |

|   |     | 5.1.1              | Derivation of Line-to-neutral Voltage and Inductor Current          | . 85         |

|   |     | 5.1.2              | Fluctuation of DC-capacitor Voltage                                 | . 87         |

|   |     | 5.1.3              | Derivation of Capacitor Voltage Including AC Component              | . 89         |

|   | 5.2 | Theor              | etical Analysis of Overmodulation and Current Spike During SLG Faul | t 90         |

|   |     | 5.2.1              | Reasons for Overmodulation and Current Spike                        | . 90         |

|   |     | 5.2.2              | Overmodulation Borderline                                           | . 92         |

|   |     | 5.2.3              | Peak Value of Current Spike                                         | . 94         |

|   | 5.3 | Exper              | iment                                                               | . 95         |

|   |     | 5.3.1              | Experimental Conditions                                             | . 95         |

|   |     | 5.3.2              | LVRT Capability Performance During SLG Fault                        | . 98         |

|   |     | 5.3.3              | LVRT Capability Performance During 3P Fault                         | . 103        |

|   |     | 5.3.4              | Evaluation of LVRT Capability of Proposed Inverter                  | . 103        |

|   | 5.4 | Concl              | usion                                                               | . 106        |

| 6 | Eva | luatio             | n of Chopper-cell Number and Performance Comparison o               | $\mathbf{f}$ |

|   | Pro | $\mathbf{posed}$   | PV Inverter                                                         | 109          |

|   | 6.1 | Loss a             | and Efficiency Comparison                                           | . 110        |

|   | 6.2 | Exper              | iment                                                               | . 115        |

|   |     | 6.2.1              | Experimental conditions                                             | . 115        |

|   |     | 6.2.2              | Steady-state performance comparisons                                | . 115        |

|   |     | 6.2.3              | LVRT capability performance comparisons during SLG fault            | . 121        |

|   |     | 6.2.4              | LVRT capability performance comparisons during 3P fault             | . 121        |

### CONTENTS

|               | 6.3          | Conclusion .  |     | <br> | <br> | <br> | <br> | <br> | <br> | <br>. 130 |

|---------------|--------------|---------------|-----|------|------|------|------|------|------|-----------|

| 7             | Con          | nclusion      |     |      |      |      |      |      |      | 131       |

|               | 7.1          | Future Resear | rch | <br> | <br> | <br> | <br> | <br> | <br> | <br>. 132 |

| $\mathbf{Li}$ | ${ m st}$ of | Publications  | 3   |      |      |      |      |      |      | 133       |

# List of Figures

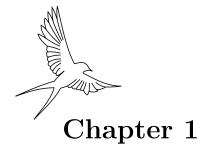

| 1.1 | PV electricity generation of Europe, US, China, and Japan                                | 2  |

|-----|------------------------------------------------------------------------------------------|----|

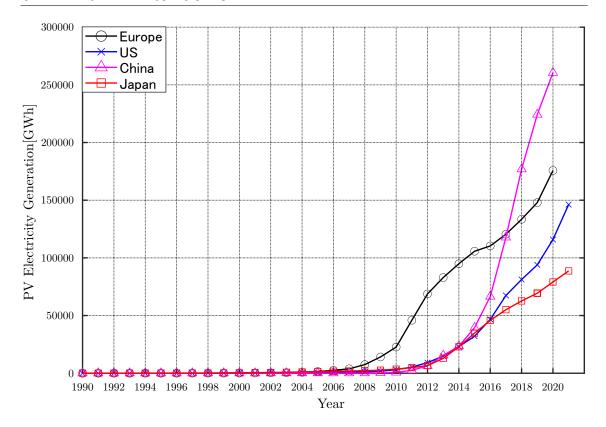

| 1.2 | Utility-scale solar PV auction contract and wholesale prices in four EU                  |    |

|     | countries, quarterly averages from 2016-2022                                             | 3  |

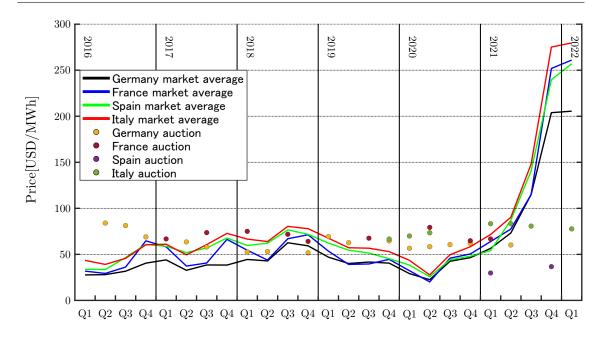

| 1.3 | Global annual investment in energy generation                                            | 4  |

| 1.4 | Conventional two-level PV inverters                                                      | 4  |

| 1.5 | Conventional three-level PV inverters: a) three-level I-type, b) three-level             |    |

|     | T-type                                                                                   | 5  |

| 1.6 | PV array power characteristics obtained from PSCAD simulation: a) $P_{a}\text{-}V_{a}$ , |    |

|     | b) $I_{a}\text{-}V_{a}$                                                                  | 7  |

| 1.7 | Basic circuit configurations of MMCC and their cell circuit configurations:              |    |

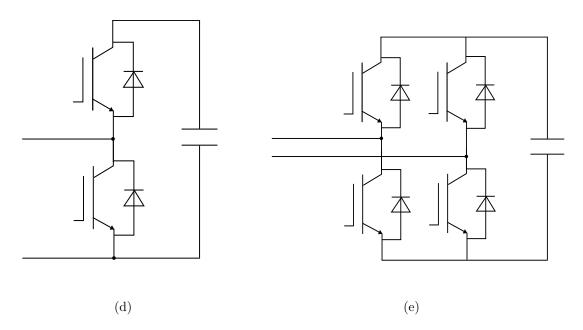

|     | a) SSBC, b) SDBC, c) DSCC or DSBC, d) Chopper cell, e) Bridge cell                       | 10 |

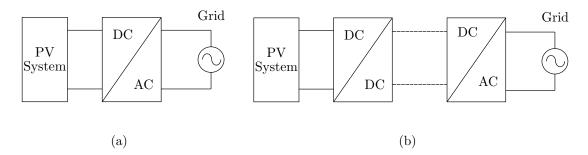

| 2.1 | PV inverter types: a) single-stage inverter, b) multiple-stage inverter                  | 16 |

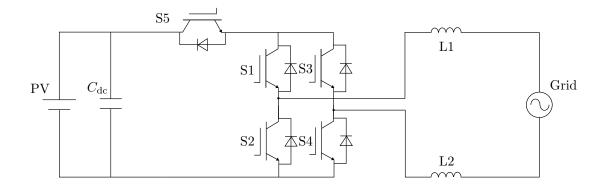

| 2.2 | HERIC topology                                                                           | 16 |

| 2.3 | H5 topology                                                                              | 17 |

| 2.4 | DAB application in PV systems                                                            | 18 |

| 2.5 | Gradational voltage inverter                                                             | 18 |

| 2.6 | HCC topology.                                                                            | 21 |

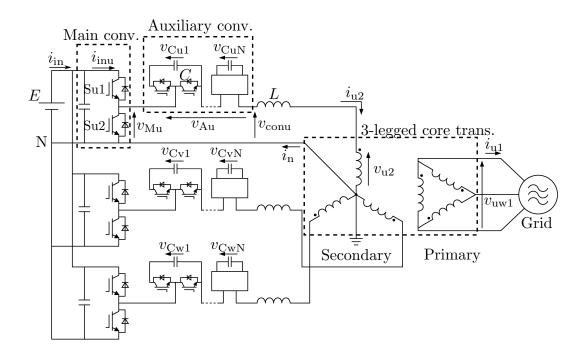

| 3.1 | Circuit configuration of three-phase PV inverter based on multiple bidirec-              |    |

|     | tional choppers for utility-scale PV systems                                             | 26 |

| 3.2 | Ideal u-phase voltage and current waveforms of Fig. 3.1 circuit with ZCS                 | 29 |

| 3.3 | Ideal u-phase voltage and current waveforms of Fig. 3.1 circuit without ZCS.             | 30 |

| 3.4 | Block diagram of overall voltage control and cluster balancing control                   | 38 |

|     |                                                                                          |    |

| 3.5  | Block diagram of output voltage calculation for u-phase cell including indi-                                     |     |

|------|------------------------------------------------------------------------------------------------------------------|-----|

|      | vidual balancing control                                                                                         | 39  |

| 3.6  | Block diagram of current control                                                                                 | 41  |

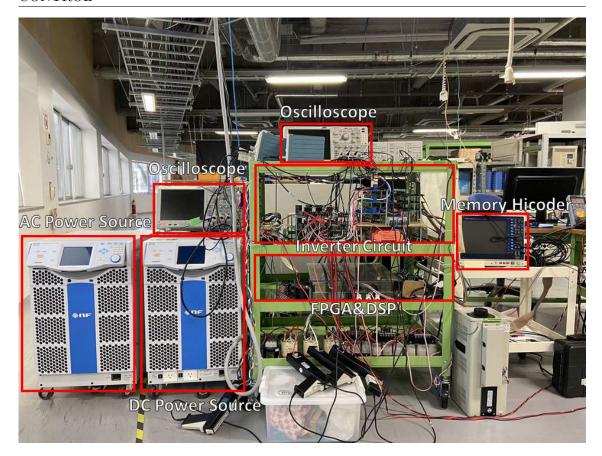

| 3.7  | Photograph of downscaled experiment system                                                                       | 44  |

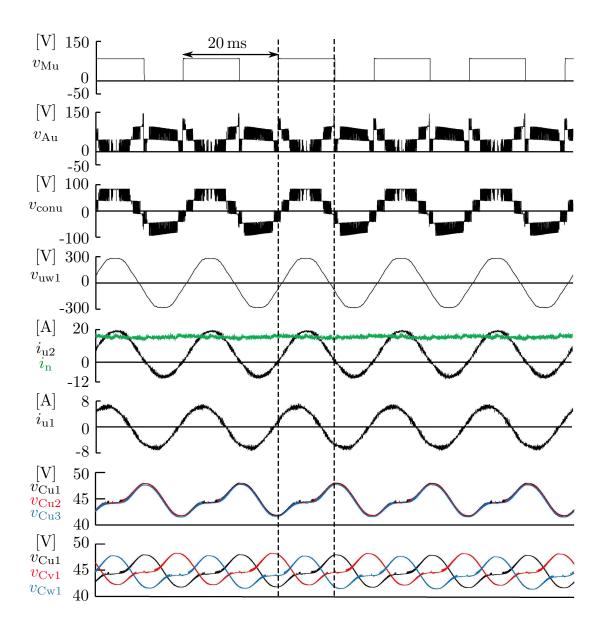

| 3.8  | Experimental waveforms under steady state where $p^* = 1.7 \mathrm{kW.}$                                         | 45  |

| 3.9  | Experimental waveforms where $i_{\rm d}^*$ was changed from 3.3 A to 16.7 A under                                |     |

|      | step change                                                                                                      | 47  |

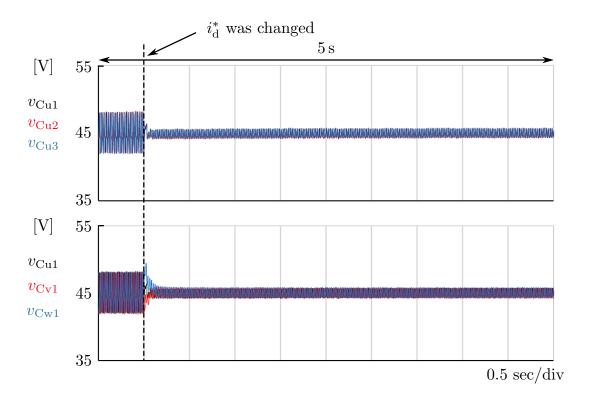

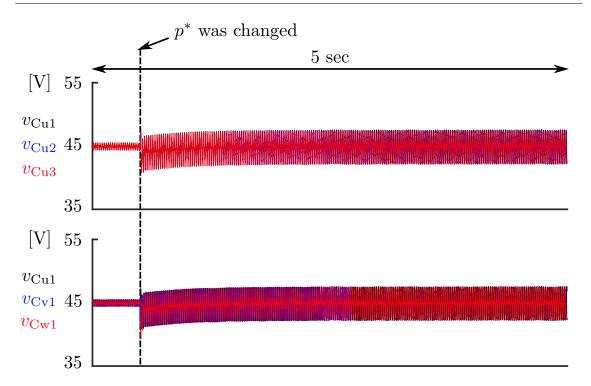

| 3.10 | Experimental DC-capacitor voltage waveforms where $i_{\rm d}^*$ was changed from                                 |     |

|      | 3.3 A to 16.7 A under step change in 5 seconds period                                                            | 48  |

| 3.11 | Experimental waveforms where $i_{\rm d}^*$ was changed from 16.7 A to 3.3 A under                                |     |

|      | step change                                                                                                      | 49  |

| 3.12 | Experimental DC-capacitor voltage waveforms where $i_{\rm d}^*$ was changed from                                 |     |

|      | 16.7 A to 3.3 A under step change in 5 seconds period                                                            | 50  |

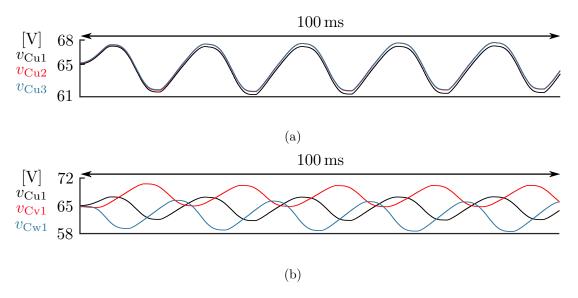

| 3.13 | Experimental DC-capacitor voltage waveforms in steady state where $E=$                                           |     |

|      | $135\mathrm{V}$ and $V_C^*=65\mathrm{V}\colon$ a) DC-capacitor voltage waveforms of three cells of               |     |

|      | u-phase, b) DC-capacitor voltage waveforms of first cell of three phases                                         | 50  |

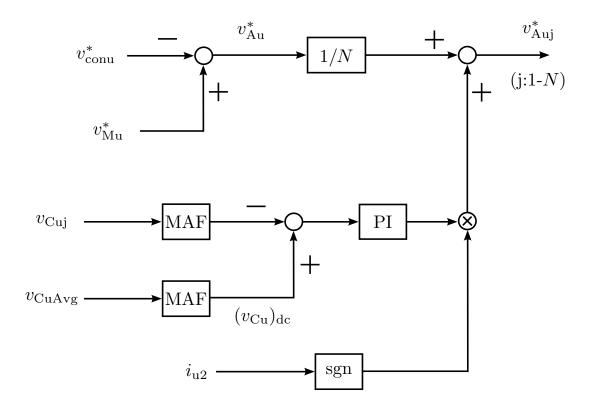

| 4.1  | Block diagram of u-phase DC-capacitor voltage control                                                            | 55  |

| 4.2  | Block diagram of output voltage calculation for u-phase cells including in-                                      |     |

|      | dividual balancing control                                                                                       | 55  |

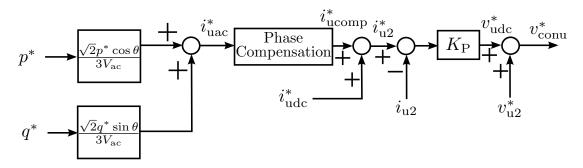

| 4.3  | Block diagram of u-phase inductor current control                                                                | 56  |

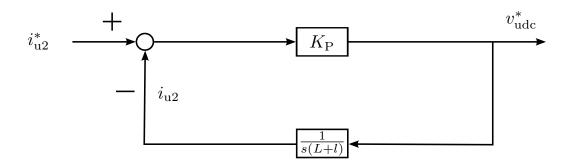

| 4.4  | Relationship between $i_{u2}^*$ and $i_{u2}$                                                                     | 57  |

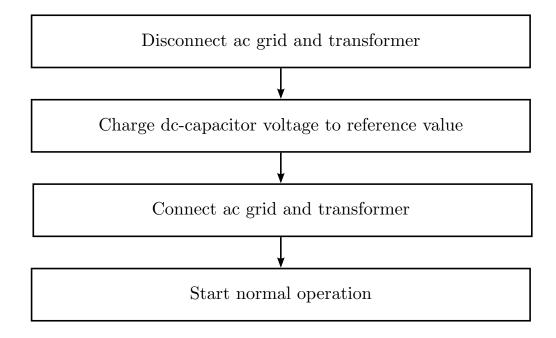

| 4.5  | Flowchart of initial charging process                                                                            |     |

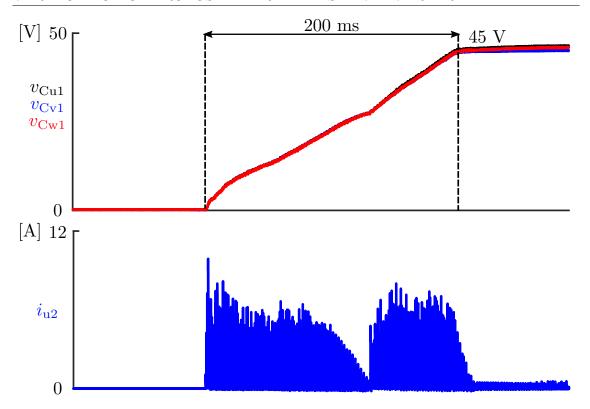

| 4.6  |                                                                                                                  | 61  |

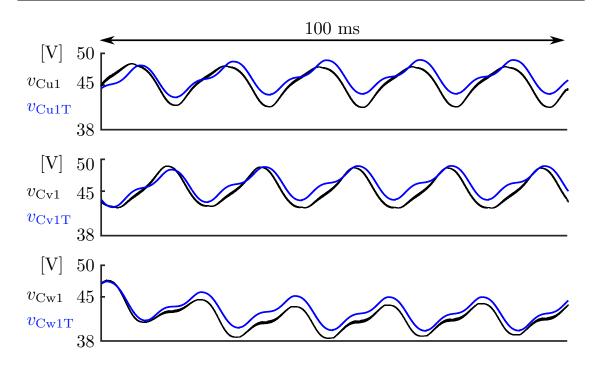

| 4.7  | Experimental waveforms of initial charging where $v_{\text{Cu}1}$ , $v_{\text{Cv}1}$ , and $v_{\text{Cw}1}$ were |     |

|      | charged                                                                                                          | 62  |

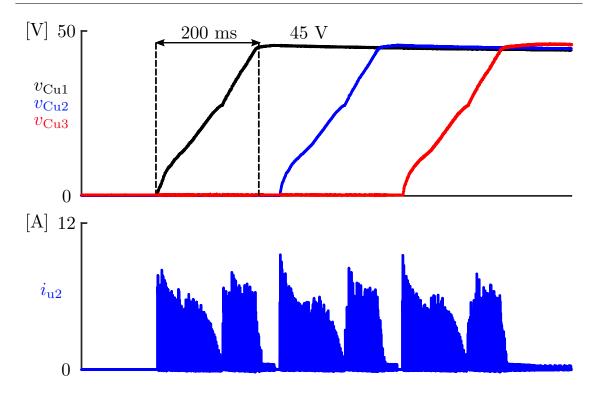

| 4.8  | Experimental waveforms of initial charging where $v_{\text{Cu}1}$ , $v_{\text{Cu}2}$ , and $v_{\text{Cu}3}$ were |     |

|      | charged sequentially                                                                                             | 63  |

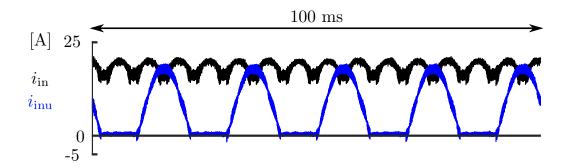

| 4.9  | Experimental waveforms under steady state where $p^* = 1.5 \mathrm{kW}$ and $E = 85 \mathrm{V}$ .                |     |

|      | Experimental waveforms of $i_{\rm in}$ and $i_{\rm inu}$                                                         |     |

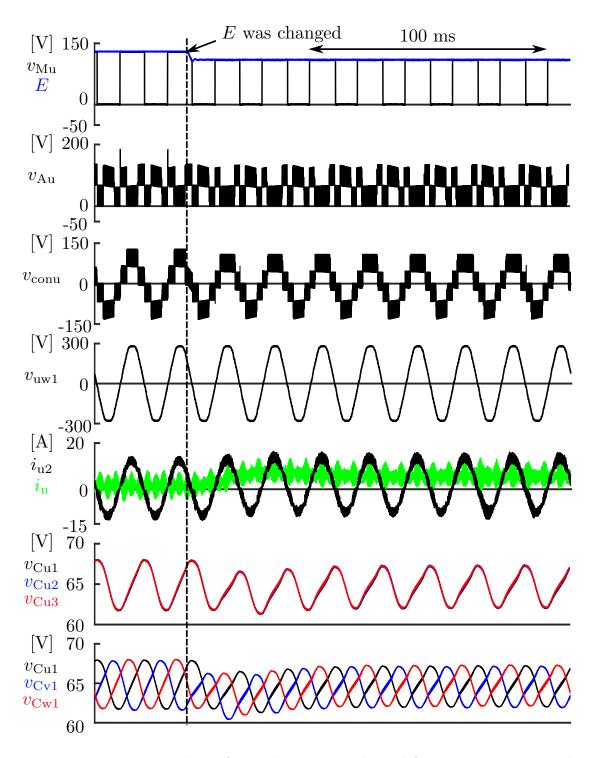

|      | Experimental waveforms under steady state where $p^* = 1.5 \mathrm{kW}$ and $E =$                                | - 3 |

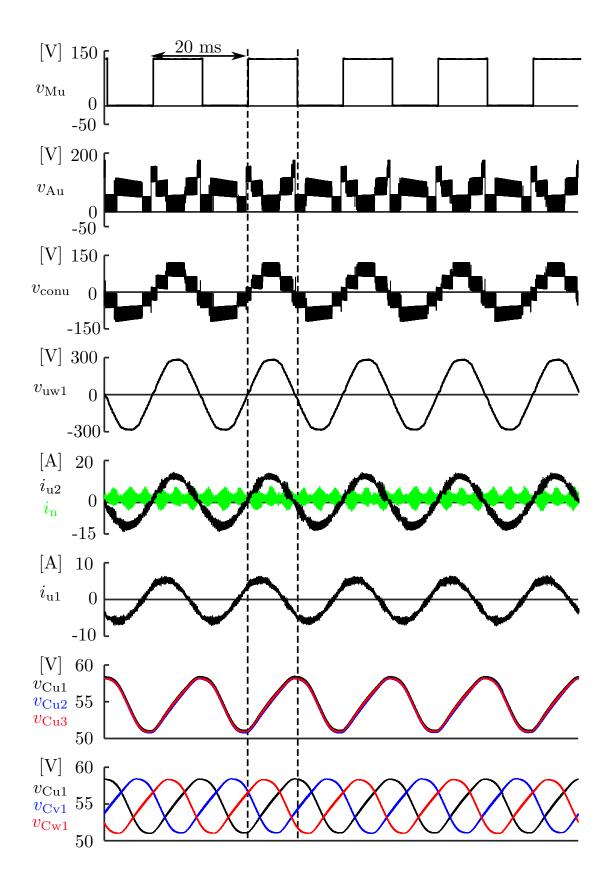

|      | 128 V                                                                                                            | 66  |

| 4.12 | Experimental waveforms under steady state where $p^* = 1.5 \mathrm{kW}$ and $E =$               |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | 135 V                                                                                           | 67 |

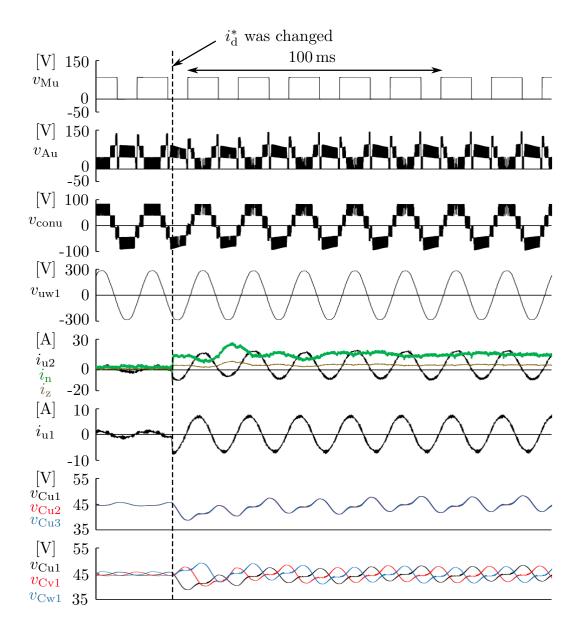

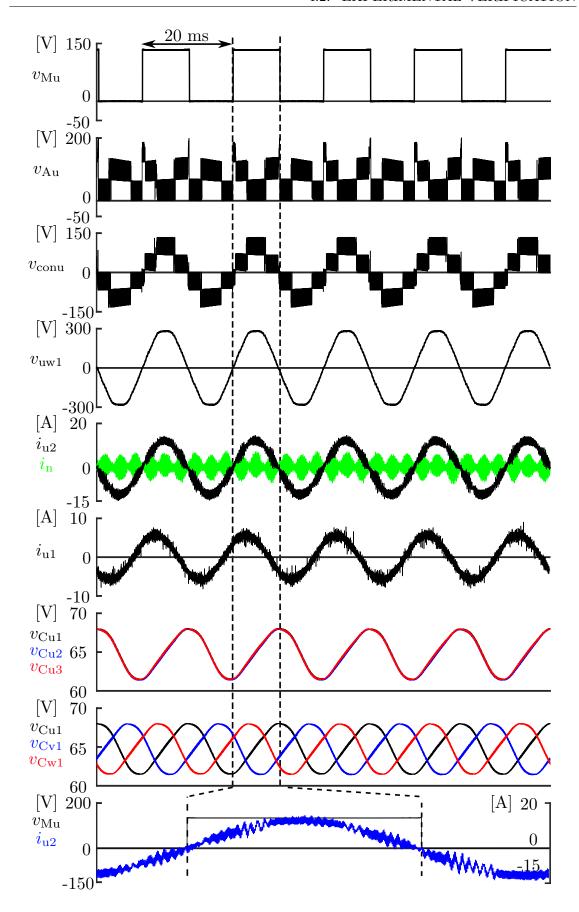

| 4.13 | Experimental waveforms where $p^*$ was changed from $0.3\mathrm{kW}$ to $1.5\mathrm{kW}$ un-    |    |

|      | der ramp change                                                                                 | 68 |

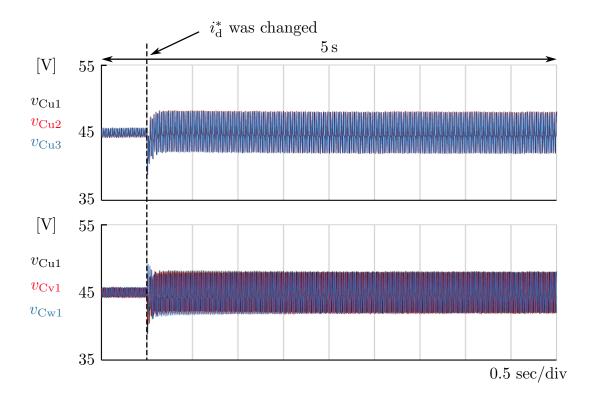

| 4.14 | Experimental DC-capacitor voltage waveforms where $p^*$ was changed from<br>0.3 kV              | W  |

|      | to $1.5\mathrm{kW}$ under ramp change in 5 seconds period                                       | 69 |

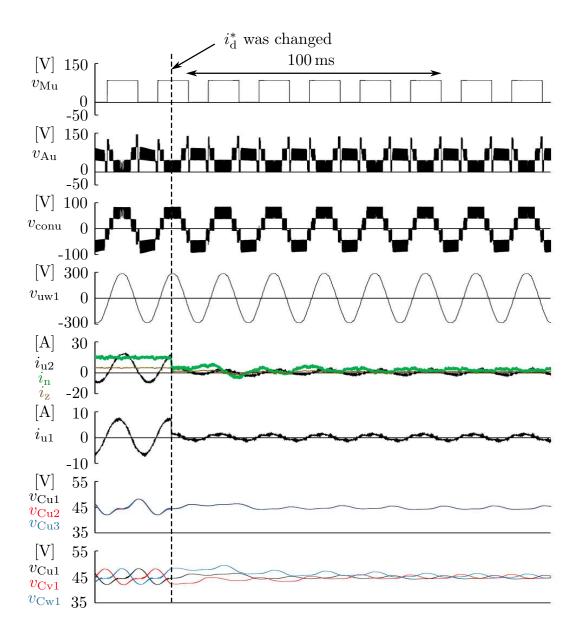

| 4.15 | Experimental waveforms where $E$ was changed from $130\mathrm{V}$ to $110\mathrm{V}$ under      |    |

|      | ramp change                                                                                     | 70 |

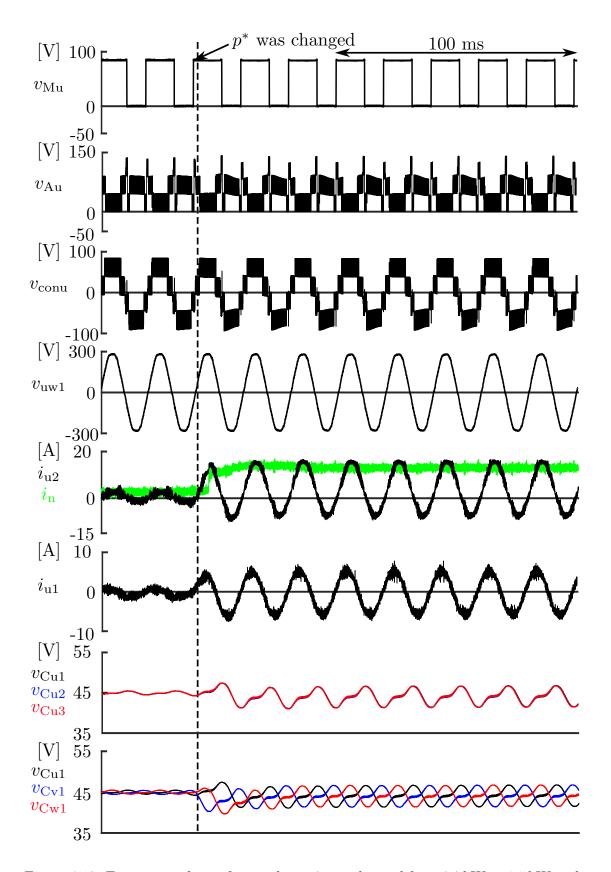

| 4.16 | Experimental waveforms where $1.5\mathrm{kVar}$ reactive power was injected to grid.            | 72 |

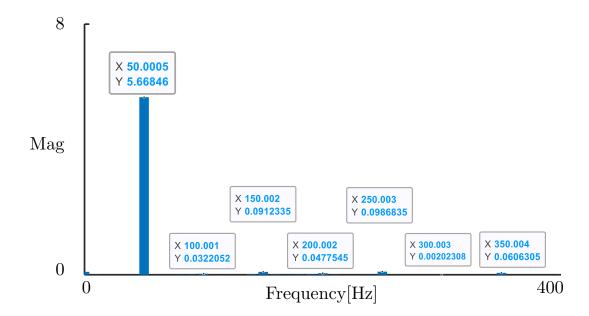

| 4.17 | Spectrum of $i_{\rm u1}$                                                                        | 73 |

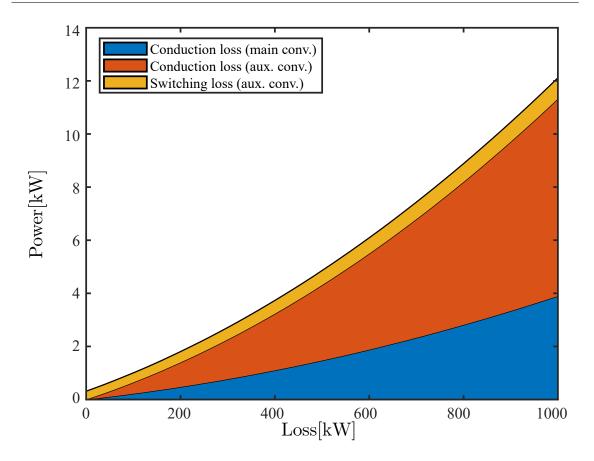

| 4.18 | Loss breakdown of proposed inverter                                                             | 74 |

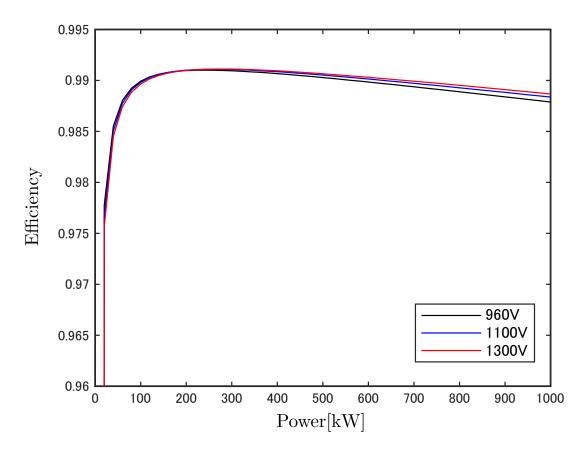

| 4.19 | Efficiency of proposed inverter when $\sqrt{3}V_{\rm ac}=1150\mathrm{V}$ with MPPT range of     |    |

|      | 960–1300 V                                                                                      | 75 |

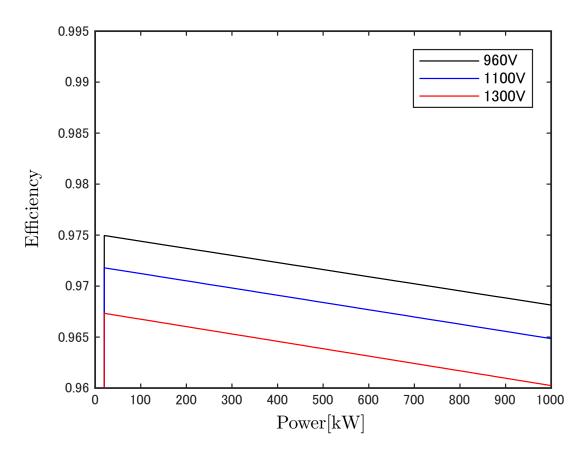

| 4.20 | Efficiency of 3-level T-type inverter circuit when $\sqrt{3}V_{\rm ac}=570\mathrm{V}$ with MPPT |    |

|      | of 960–1300 V                                                                                   | 77 |

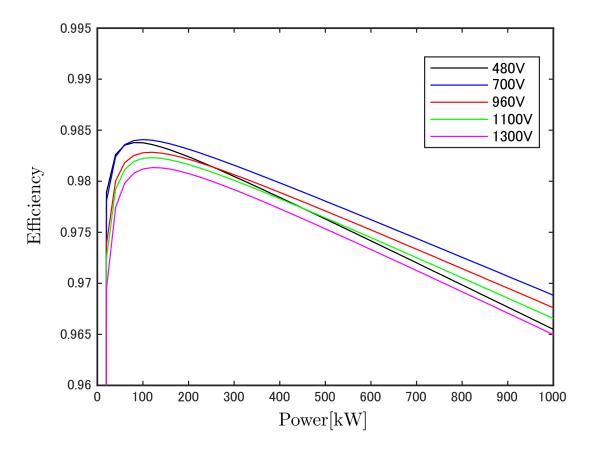

| 4.21 | Efficiency of proposed inverter when $\sqrt{3}V_{\rm ac}=570\mathrm{V}$ with MPPT range of      |    |

|      | 480–1300 V                                                                                      | 78 |

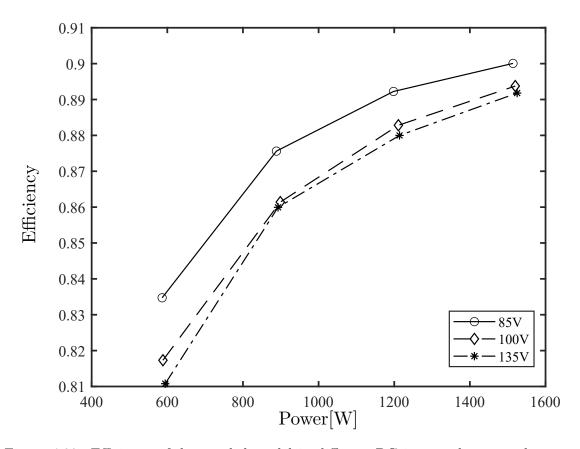

| 4.22 | Efficiency of downscaled model in different DC input voltage steady-state                       |    |

|      | operating cases                                                                                 | 80 |

| 5.1  | Circuit configuration of proposed three-phase PV inverter under grid faults.                    | 84 |

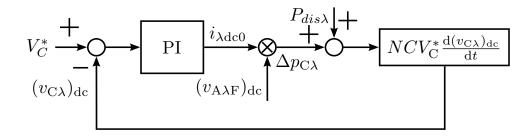

| 5.2  | Block diagram of DC-capacitor voltage control of each phase considering                         |    |

|      | power disturbance during the fault                                                              | 88 |

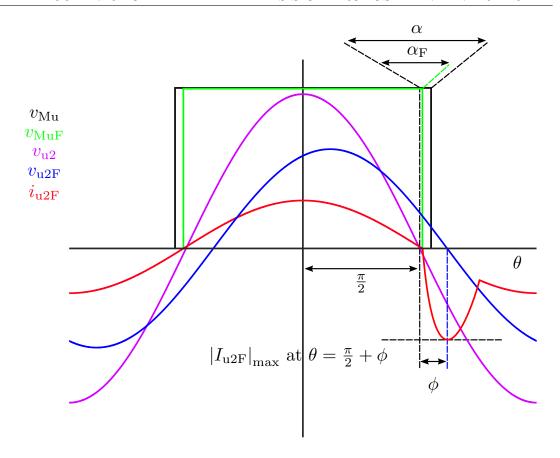

| 5.3  | Theoretical waveforms of u-phase current and voltages                                           | 90 |

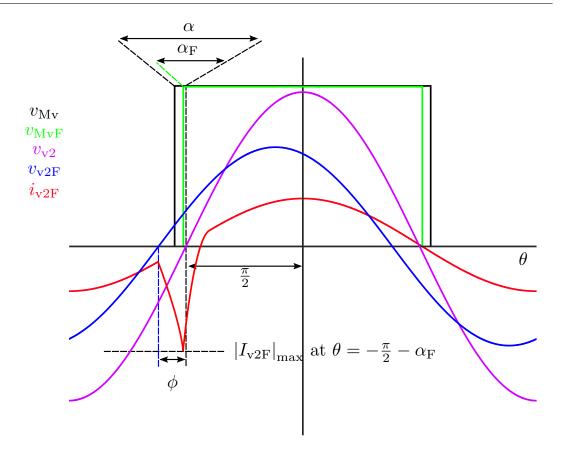

| 5.4  | Theoretical waveforms of v-phase current and voltages                                           | 92 |

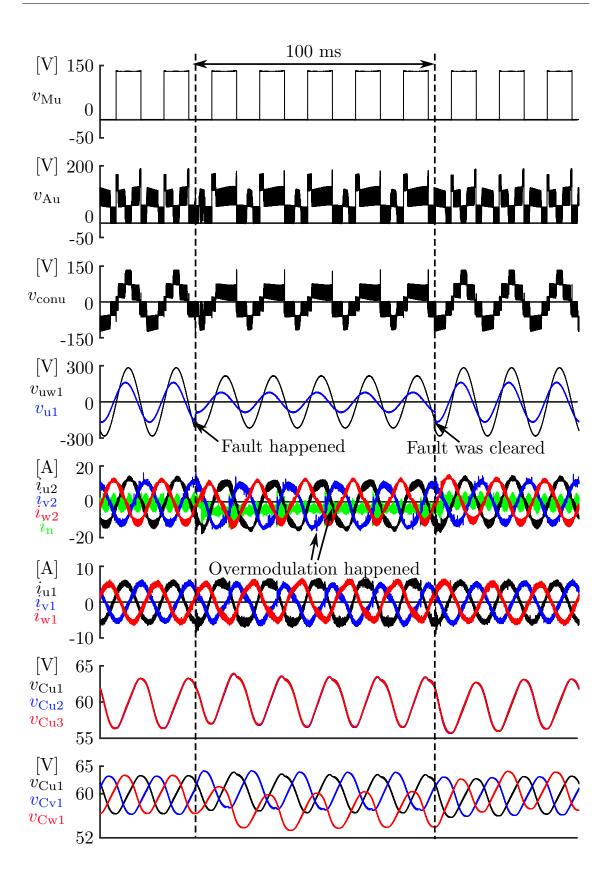

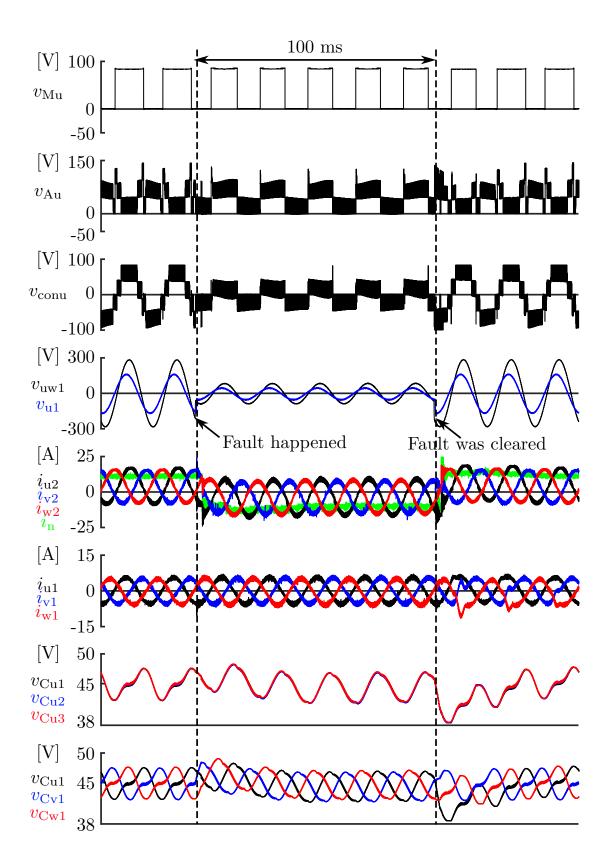

| 5.5  | Experimental waveforms during SLG faults where $E=85\mathrm{V}$ and $v_{\mathrm{u}1}$ dropped   |    |

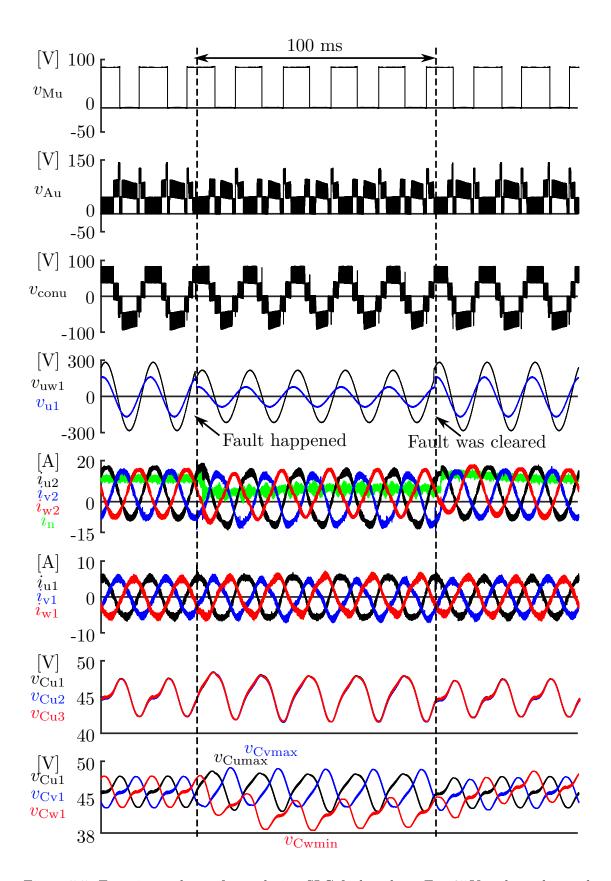

|      | by 50 %                                                                                         | 96 |

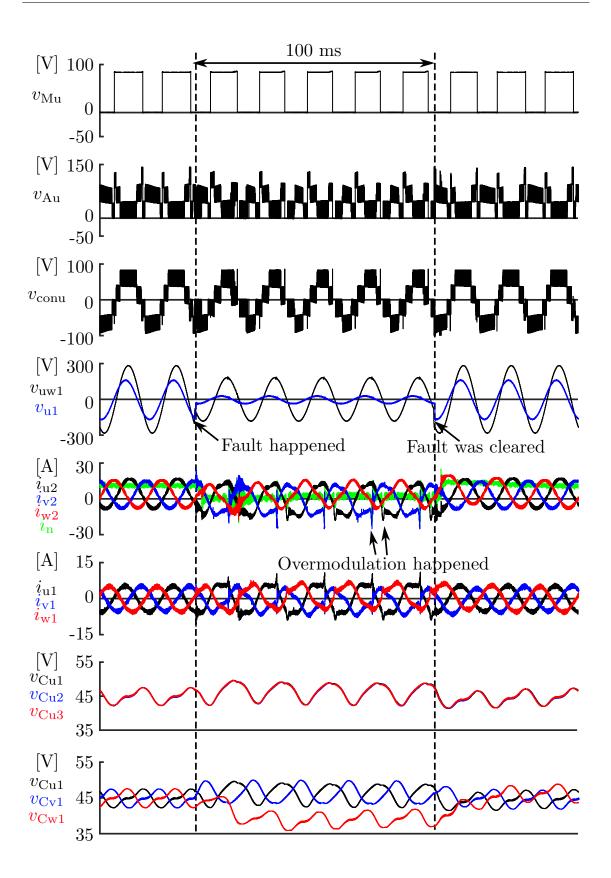

| 5.6  | Experimental waveforms during SLG faults where $E=85\mathrm{V}$ and $v_{\mathrm{u}1}$ dropped   |    |

|      | by 80 %                                                                                         | 97 |

| 5.7  | Comparison of experimental capacitor voltages and theoretical capacitor                         |    |

|      | voltages during SLG fault                                                                       | 98 |

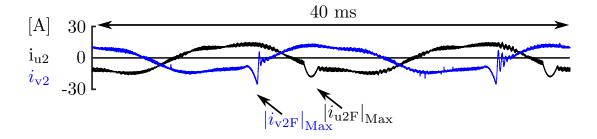

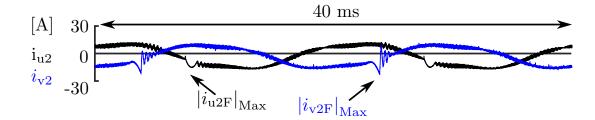

| 5.8  | Zoomed in waveforms of current spikes in u-phase and v-phase of Fig. 5.6                        | 98 |

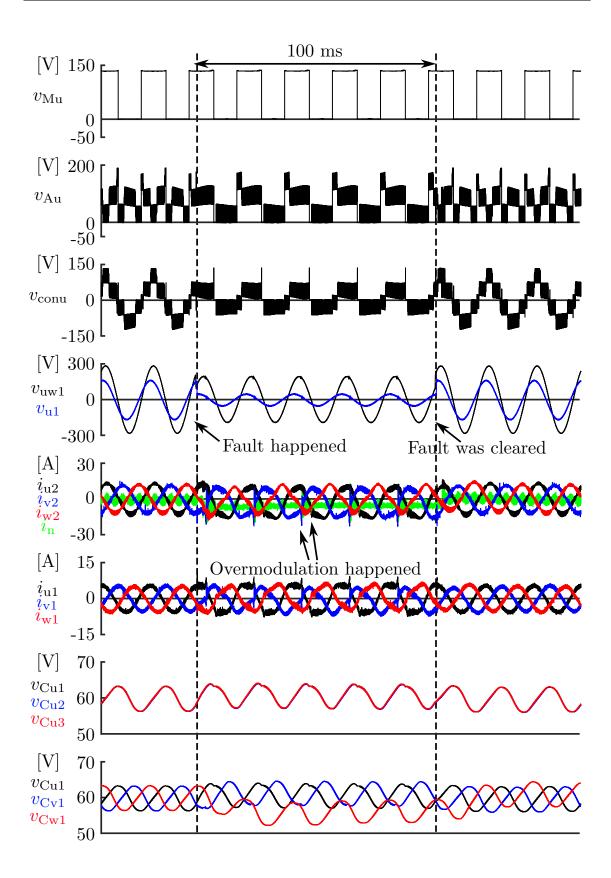

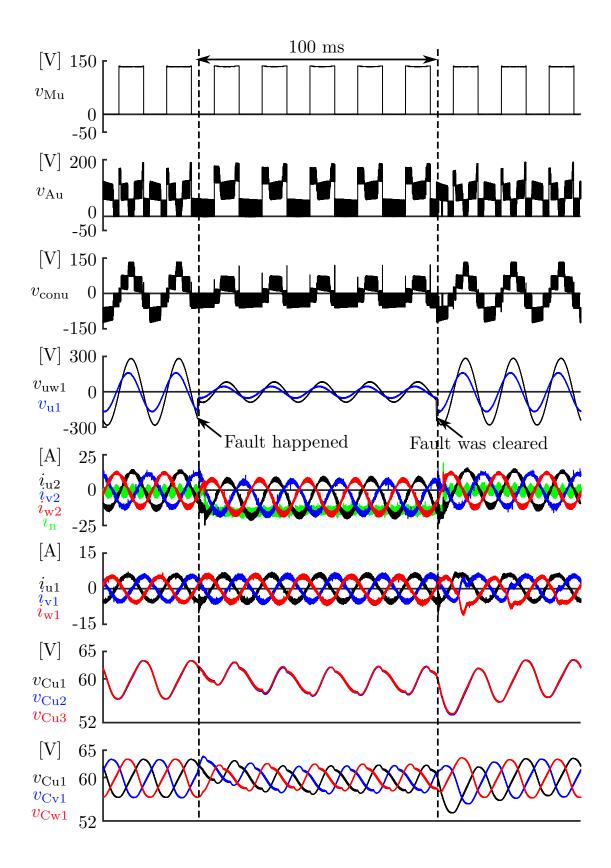

| 5.9  | Experimental waveforms during SLG faults where $E=135\mathrm{V}$ and $v_{\mathrm{u}1}$                       |

|------|--------------------------------------------------------------------------------------------------------------|

|      | dropped by 50 %                                                                                              |

| 5.10 | Experimental waveforms during SLG faults where $E=135\mathrm{V}$ and $v_{\mathrm{u}1}$                       |

|      | dropped by 70 %                                                                                              |

| 5.11 | Zoomed in waveforms of current spikes in u-phase and v-phase of Fig. 5.10. 103                               |

| 5.12 | Experimental waveforms during 3P fault where $E=85\mathrm{V}$ and primary side                               |

|      | line-to-neutral voltage dropped by $70\%$                                                                    |

| 5.13 | Experimental waveforms during 3P fault where $E=135\mathrm{V}$ and primary                                   |

|      | side line-to-neutral voltage dropped by 70 %                                                                 |

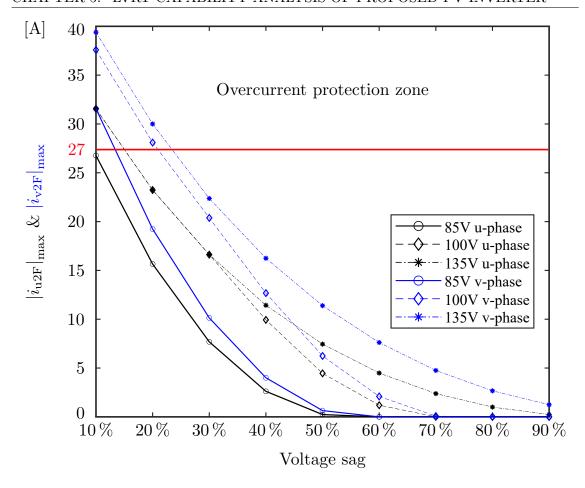

| 5.14 | LVRT capability of the 1.5-kW downscaled system under the SLG fault $106$                                    |

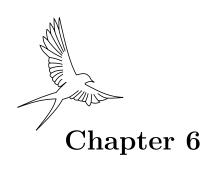

| 6.1  | Loss breakdown of proposed inverter: a) two-cell inverter circuit, b) three-                                 |

| 0.1  | cell inverter circuit                                                                                        |

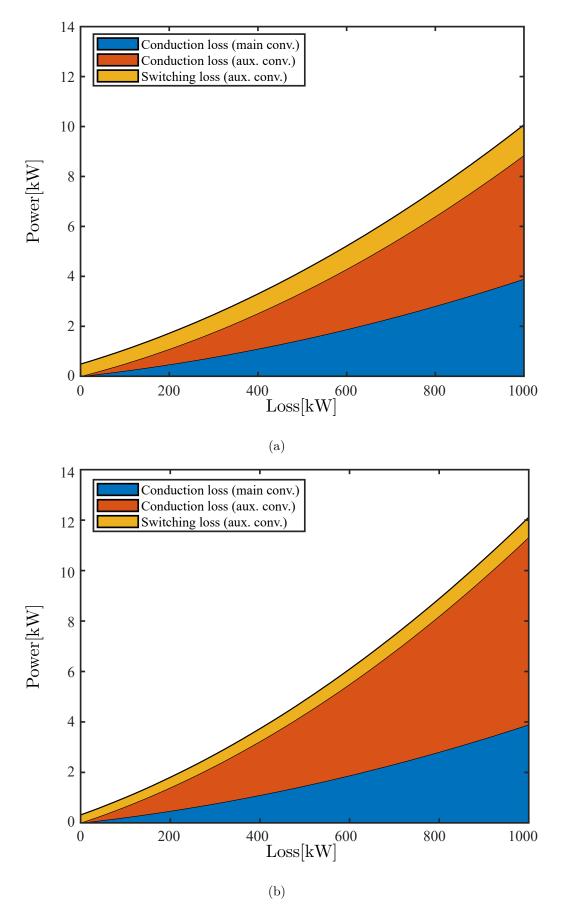

| 6.2  | Efficiency comparisons of proposed inverter when $\sqrt{3}V_{\rm ac} = 1150\mathrm{V}$ with                  |

| 0.2  | MPPT range of 960 – 1300 V: a) $E = 960 \text{ V}$ , b) $E = 1100 \text{ V}$ , 3) $E = 1300 \text{ V}$ . 113 |

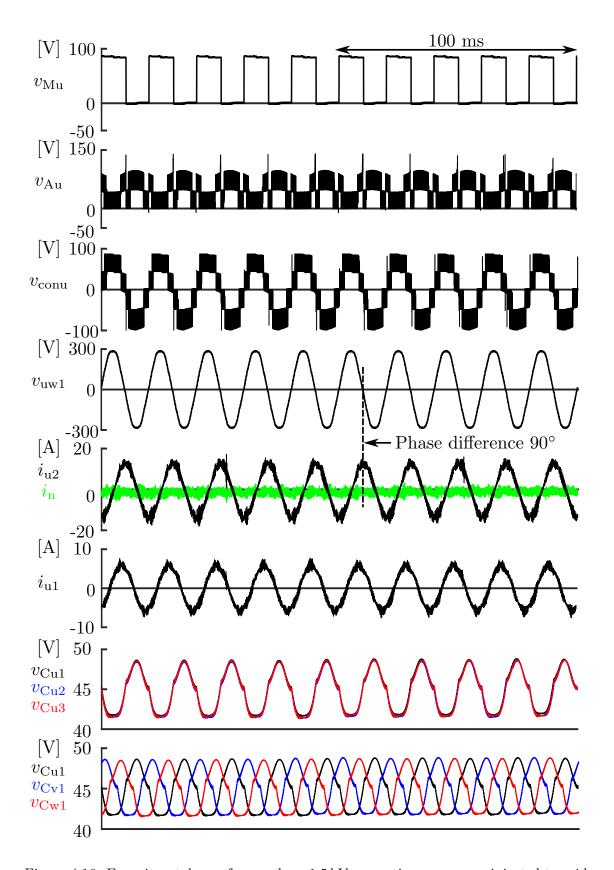

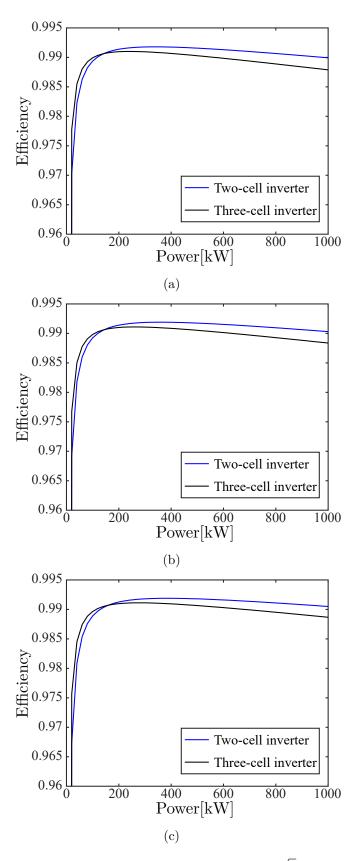

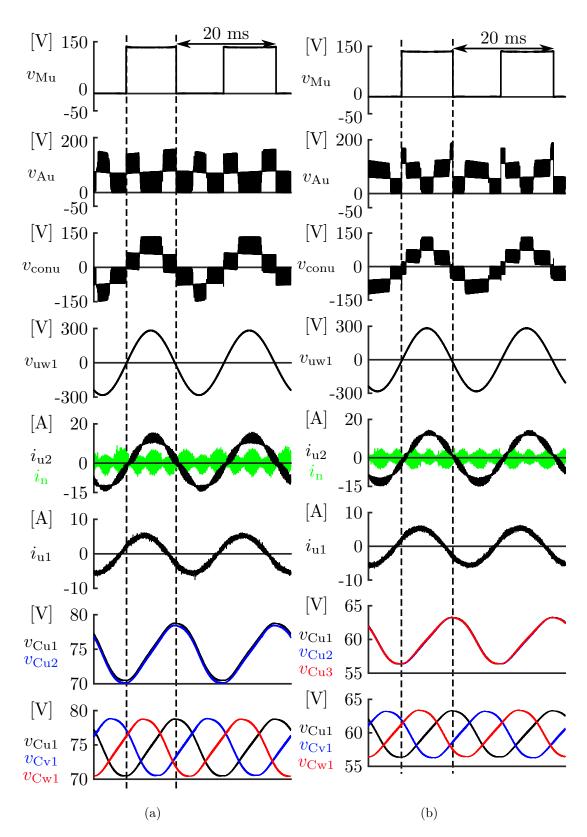

| 6.3  | Experimental waveforms under steady state where $p^* = 1.5 \mathrm{kW}$ and $E =$                            |

| 0.0  | 85 V: a) two-cell inverter circuit, b) three-cell inverter circuit                                           |

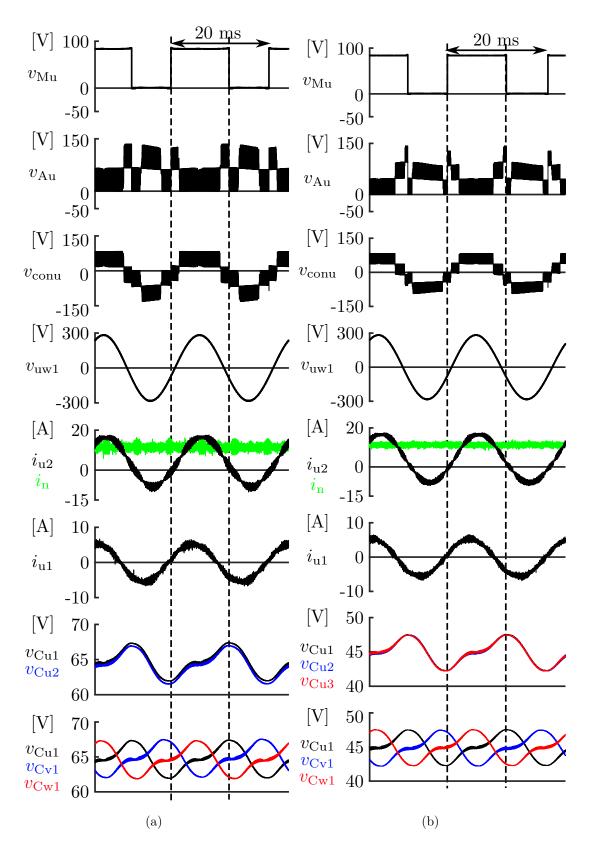

| 6.4  | Experimental waveforms under steady state where $p^* = 1.5 \mathrm{kW}$ and $E =$                            |

| 0.1  | 135 V: a) two-cell inverter circuit, b) three-cell inverter circuit                                          |

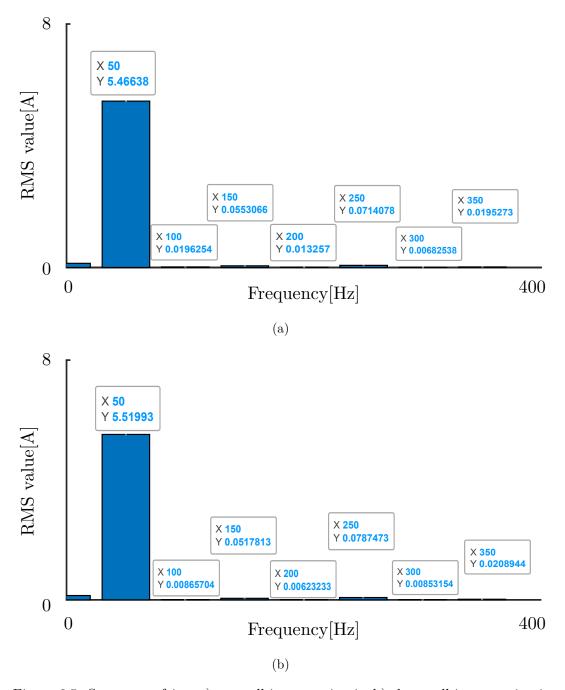

| 6.5  | Spectrum of $i_{u1}$ : a) two-cell inverter circuit, b) three-cell inverter circuit 119                      |

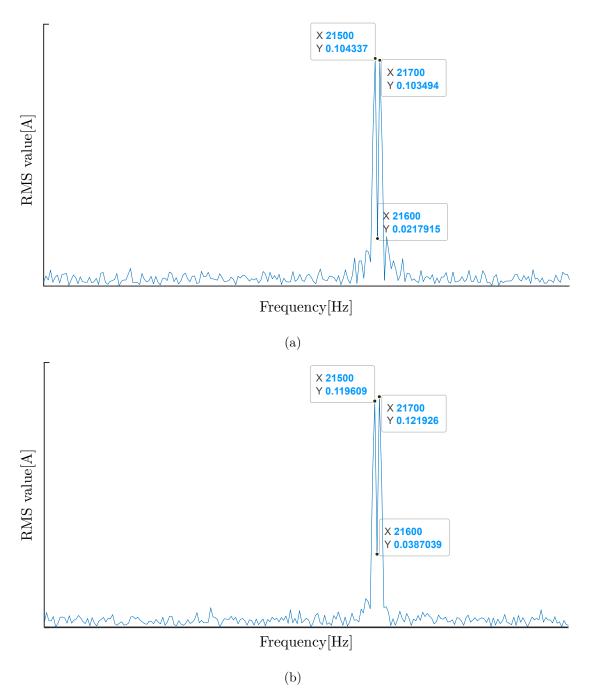

| 6.6  | 21.6 kHz components of $i_{u1}$ : a) two-cell inverter circuit, b) three-cell inverter                       |

|      | circuit                                                                                                      |

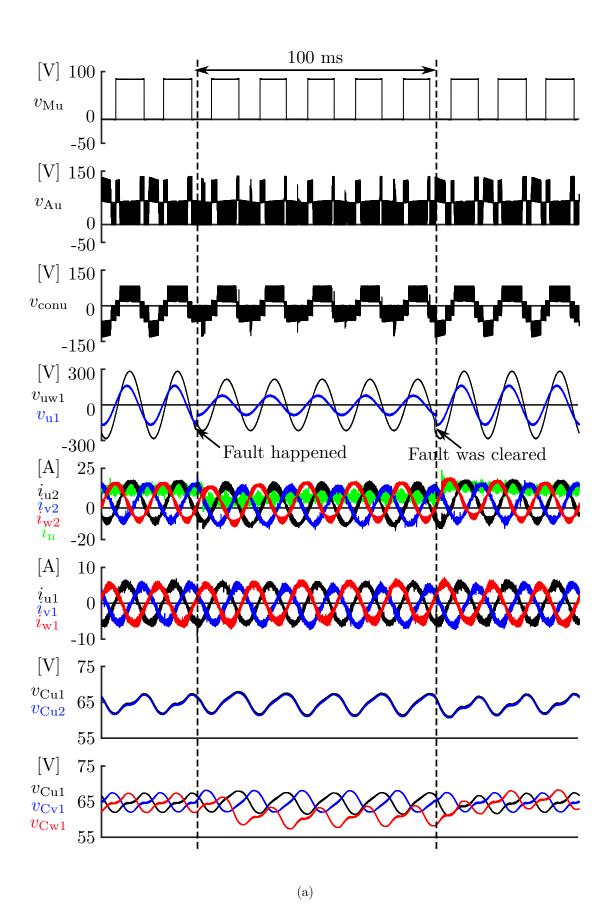

| 6.7  | Experimental waveforms during SLG fault where $E=85\mathrm{V}$ and $v_{\mathrm{u}1}$ dropped                 |

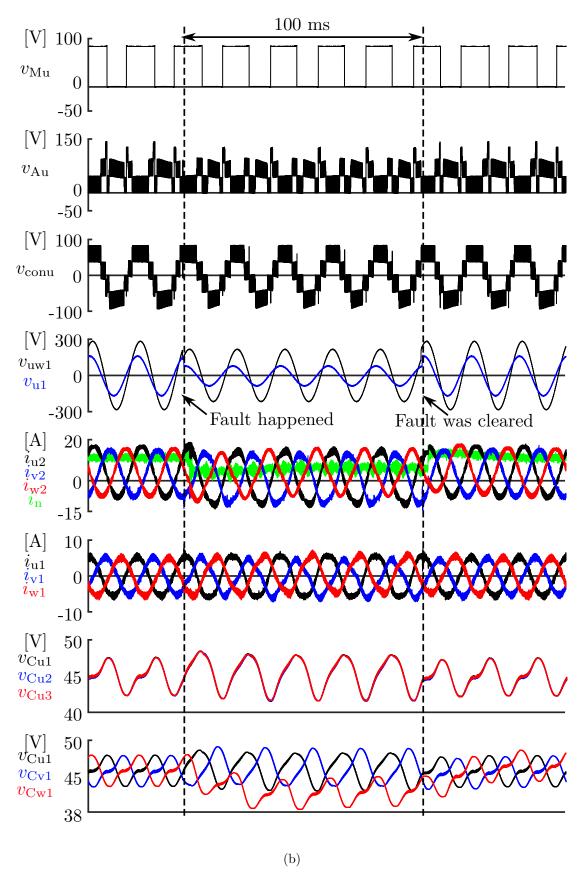

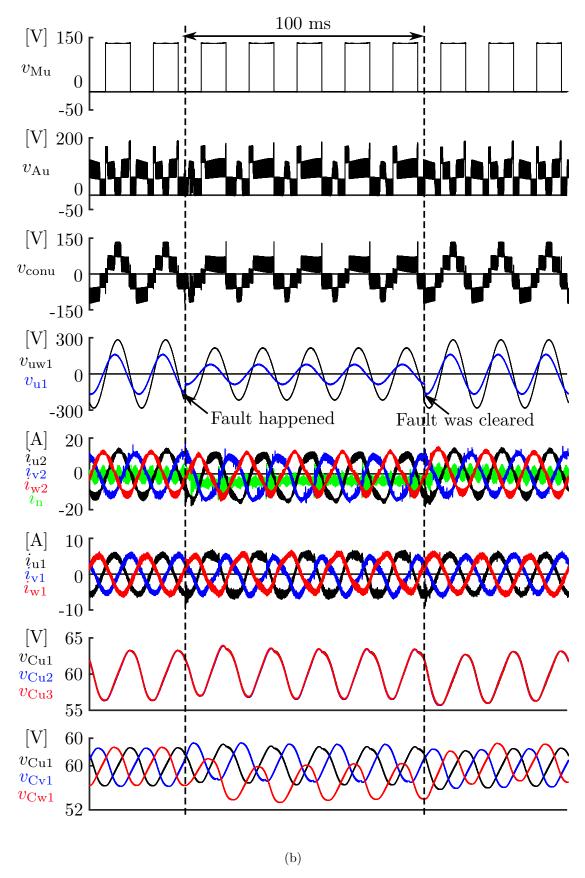

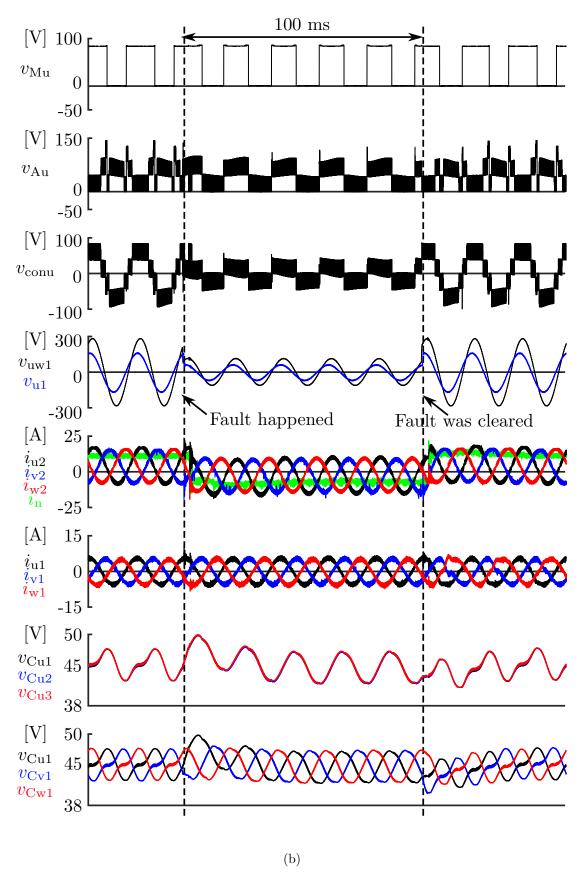

|      | by 50%: a) two-cell inverter circuit, b) three-cell inverter circuit 123                                     |

| 6.8  | Experimental waveforms during SLG fault where $E = 135 \mathrm{V}$ and $v_{\mathrm{u}1}$ dropped             |

|      | by 50%: a) two-cell inverter circuit, b) three-cell inverter circuit 125                                     |

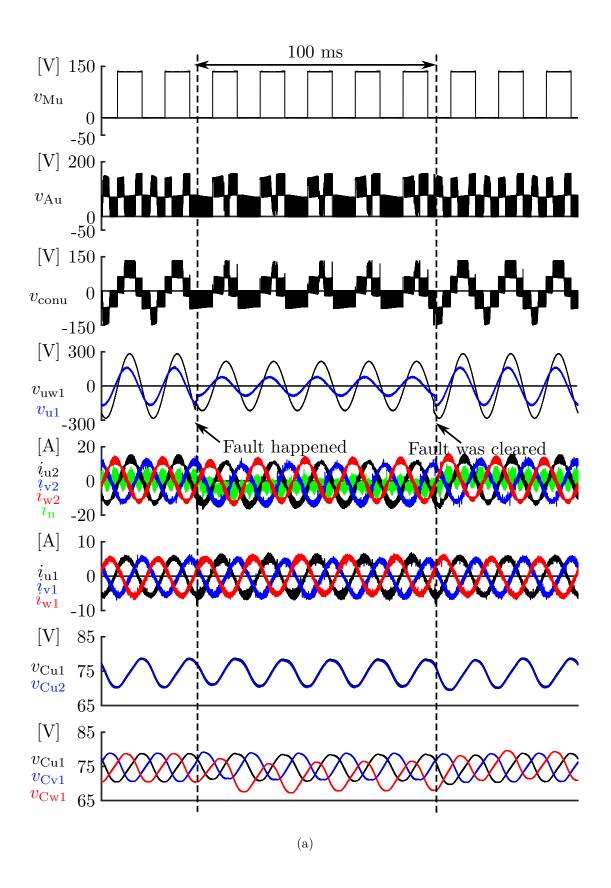

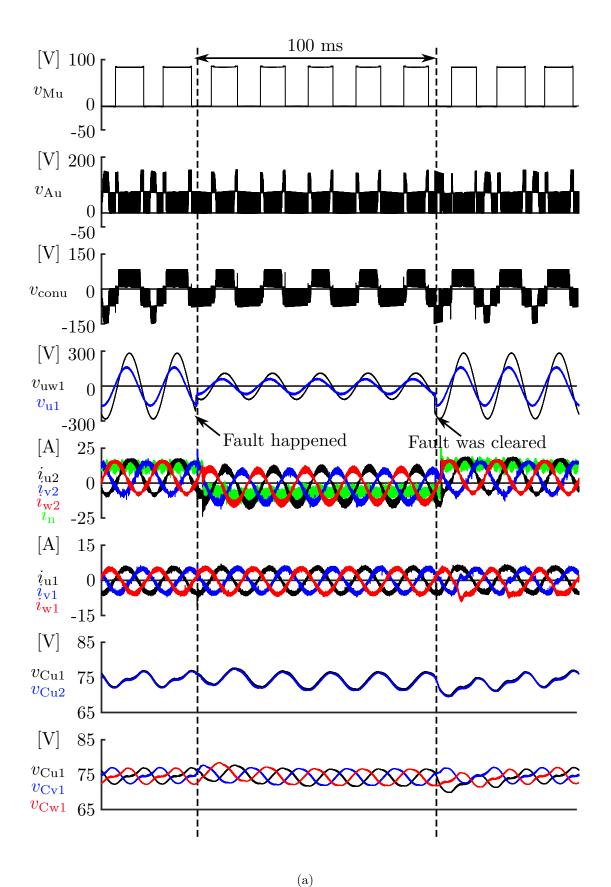

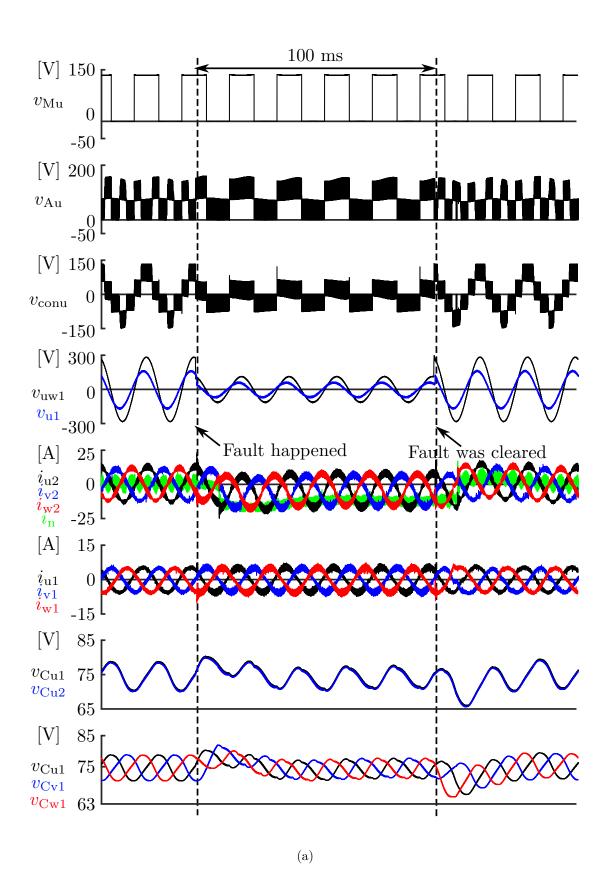

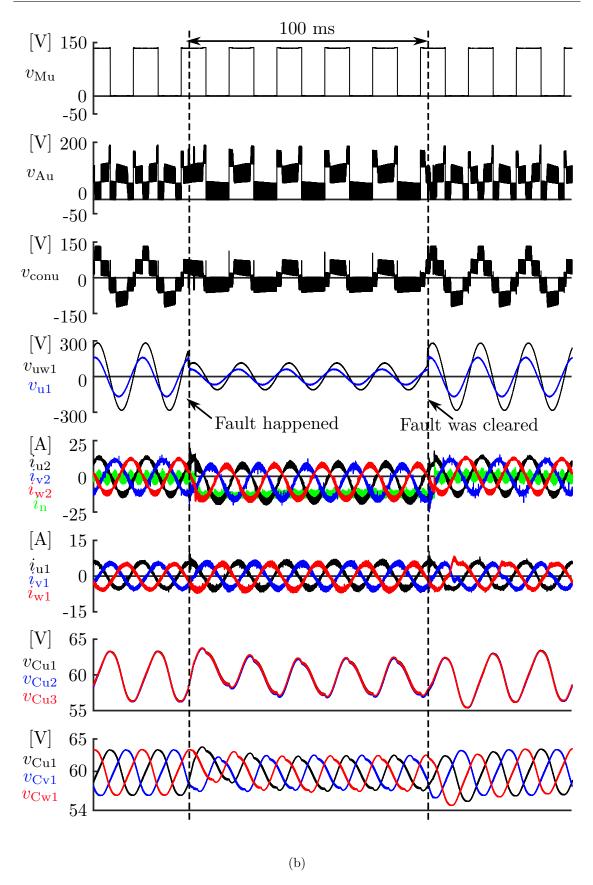

| 6.9  | Experimental waveforms during 3P fault where $E = 85 \mathrm{V}$ and primary                                 |

|      | side line-to-neutral voltage dropped by 60 %: a) two-cell inverter circuit, b)                               |

|      | three-cell inverter circuit                                                                                  |

| 6.10 | Experimental waveforms during 3P fault where $E = 135 \mathrm{V}$ and primary                                |

|      | side line-to-neutral voltage dropped by 60 %: a) two-cell inverter circuit, b)                               |

|      | three-cell inverter circuit                                                                                  |

|      |                                                                                                              |

# List of Tables

| 2.1 | Differences between gradational voltage inverter and proposed PV inverter.  | 19  |

|-----|-----------------------------------------------------------------------------|-----|

| 3.1 | Circuit parameters used for experiments                                     | 43  |

| 4.1 | Circuit parameters used for experiments                                     | 59  |

| 4.2 | Circuit parameters used for loss calculation                                | 73  |

| 4.3 | Parameters of proposed inverter used for comparison with same MPPT range.   | 74  |

| 4.4 | Parameters of 3-level T-type inverter circuit used for comparison with same |     |

|     | MPPT range                                                                  | 75  |

| 4.5 | Parameters of proposed inverter used for comparison with same AC voltage.   | 76  |

| 5.1 | Circuit Parameters Used for Experiments                                     | 95  |

| 6.1 | Circuit parameters used for loss calculation                                | .11 |

| 6.2 | Parameters of proposed inverter used for comparison with same MPPT range.1  | .11 |

| 6.3 | Two-cell inverter circuit parameters used for experiments                   | .14 |

| 6.4 | Three-cell inverter circuit parameters used for experiments                 | 14  |

## List of Abbreviations

3P three-phase xvi, 13, 14, 83, 84, 95, 103–105, 115, 121, 127, 129, 130

AC alternating current xvii, xxiii, xxv, xxvii, 1, 6, 8, 11, 14, 15, 17, 18, 26, 27, 34, 37, 39, 40, 42, 51, 54, 56–58, 63, 76, 83–85, 87–89, 95, 99, 111, 115, 131, 132

BESS battery energy storage system 8, 10

BTB back-to-back 11

CB combiner box 5

DAB dual-active-bridge xiii, 18

DC direct current xiv, xv, xxiii–xxix, 1, 5, 6, 8, 11–13, 16–18, 20, 26, 27, 31–40, 42–44, 46, 48, 50, 51, 53–56, 58–63, 65, 69, 71, 73–76, 79, 80, 83–89, 91, 92, 95, 98–100, 103, 106, 110, 111, 114, 115, 118, 121, 130

DER distributed energy resource 20

DSBC double-star bridge-cells xiii, 8, 10, 11

DSCC double-star chopper-cells xiii, 8, 10, 11

DSP digital signal processor 43, 59

EU European Union xiii, 3

FPGA field-programmable gate array 43, 59

HCC hybrid cascade converter 20, 22

HERIC high efficient and reliable inverter concept xiii, 16

HVDC high-voltage direct current 11, 22, 109

IEA international energy agency 2, 3

IGBT insulated-gate bipolar transistor 5, 11, 20, 22, 73, 74,

110

LVRT low-voltage ride-through v, xvi, 12–15, 19, 20, 23, 83,

94, 103, 106, 121, 131, 132

MAF moving average filter 54, 87, 99

MMCC modular multilevel cascade converter xiii, 8, 10–13, 15,

19, 20, 22, 23, 40, 51, 109, 110

MOSFET metal-oxide-semiconductor field-effect transistor 20

MPPT maximum-power-point-tracking v, xv-xvii, 6, 8, 11,

16–19, 27, 37, 51, 74–78, 81, 110, 111, 113, 131, 132

NSC negative-sequence current 20

PCS power conditioning system 11

PI proportional-integral xxvii, 40, 89, 132

PLL Phase locked loop xxviii, 28, 86, 90

PV photovoltaic v, xiii, xv, xvii, xxiv, xxv, xxvii, 1–8, 11–

19, 22, 23, 25–27, 42, 51, 58, 71, 76, 84, 95, 106, 109,

114, 115, 131, 132

PWM pulse-width modulation 17, 19, 26, 36, 37, 42

RMS root-mean-square xxv, xxvii, 6, 27, 28, 33, 43, 46, 76,

115, 118

SDBC single-delta bridge-cells xiii, 8, 10, 20, 22, 40

SLG single-line-to-ground xv, xvi, xxiii–xxviii, 13, 83–92,

94-103, 106, 115, 121, 123, 125, 130, 131

SSBC single-star bridge-cells xiii, 8, 10, 20, 22

STATCOM static synchronous compensator 8, 10, 20

SVPWM space-vector pulse-width modulation 19

THD total harmonic distortion 13, 14, 71, 118, 130, 132

US United States xiii, 2, 17

ZCS zero-current switching xiii, 29–31, 33–35, 37, 46, 62,

65, 110, 118

ZSC zero-sequence current xxvi, 20, 22, 27, 39, 40, 46, 61

ZSV zero-sequence voltage 20, 36, 37

## Nomenclature

$(v_{\text{AuF}})_{\text{dc}}$  DC component of u-phase auxiliary converter output voltage during SLG

fault

$(v_{\rm Au})_{\rm 50\,Hz}$  Fundamental-frequency component of u-phase auxiliary converter output volt-

age

$(v_{\rm Au})_{\rm dc}$  DC component of u-phase auxiliary converter output voltage

$(v_{\rm Au})_{\rm max}$  Maximum output voltage of u-phase auxiliary converter

$(v_{\rm Au})_{\rm ripple}$  High frequency component of u-phase auxiliary converter output voltage

$(v_{\text{CAvg}})_{\text{dc}}$  DC component of  $v_{\text{CAvg}}$

$(v_{\text{Cu}})_{\text{ac}}$  AC component of  $v_{\text{CuAvg}}$

$(v_{\rm Cu})_{\rm dc}$  DC component of  $v_{\rm CuAvg}$

$(v_{\text{Cv}})_{\text{ac}}$  AC component of  $v_{\text{CvAvg}}$

$(v_{\rm Cv})_{\rm dc}$  DC component of  $v_{\rm CvAvg}$

$(v_{\text{Cw}})_{\text{ac}}$  AC component of  $v_{\text{CwAvg}}$

$(v_{\rm Cw})_{\rm dc}$  DC component of  $v_{\rm CwAvg}$

$(v_{\rm Mu})_{\rm 50\,Hz}$  Fundamental-frequency component of u-phase main converter output voltage

$|i_{u2F}|_{Max}$  Peak value of  $i_{u2F}$  during SLG fault

$|i_{v2F}|_{Max}$  Peak value of  $i_{v2F}$  during SLG fault

$\alpha$  Turn-on (turn-off) angle of the main converter

#### NOMENCLATURE

Turn-on (turn-off) angle of the main converter during SLG fault  $\alpha_{\mathrm{F}}$ Variation of  $i_{u2F}$  during SLG fault  $\Delta i_{\mathrm{u2F}}$  $\Delta i_{\rm udc0}$ DC current introduced for u-phase DC-capacitor voltage control  $\Delta i_{\rm v2F}$ Variation of  $i_{v2F}$  during SLG fault  $\Delta i_{\mathrm{z}0}$ Variation of  $i_{z0}$  $\Delta p_{\mathrm{Cu}}$ Power flows into u-phase auxiliary converter originating from  $(v_{Au})_{dc}$  and  $i_{\rm udc0}$  $\Delta p_{\mathrm{Cv}}$ Power flows into v-phase auxiliary converter originating from  $(v_{Av})_{dc}$  and  $i_{\rm vdc0}$ Power flows into w-phase auxiliary converter originating from  $(v_{Aw})_{dc}$  and  $\Delta p_{\mathrm{Cw}}$  $i_{\rm wdc0}$  $\Delta P_{\rm inu}$ Variation of DC input power of u-phase inverter  $\Delta P_{\rm uac}$ U-phase cluster balancing power Power efficiency of PV array  $\eta$ Radius velocity Phase jump angle during SLG fault  $\theta$ Phase angle of u-phase Transformer voltage ratio aCCell capacitor  $D_{\rm M}$ Duty cycle of main converter EDC input voltage of PV system  $E_{\rm a}$ Voltage of PV array in simulation Minimum input voltage of PV system  $E_{\min}$

Carrier frequency of each chopper cell

$f_{\rm SA}$

| $f_{ m SM}$          | Grid frequency/Carrier frequency of main converter                                   |

|----------------------|--------------------------------------------------------------------------------------|

| $I_{ m ac}$          | RMS value of u-phase inductor current fundamental-frequency component                |

| $I_{\mathrm{a}}$     | Output current of PV array in simulation                                             |

| $I_{ m dcF}$         | DC component of inductor current during SLG fault                                    |

| $I_{ m dc}$          | DC component of inductor current                                                     |

| $i_{ m dc}^*$        | Reference value of $I_{ m dc}$                                                       |

| $i_{ m d}$           | D-axis current in current control                                                    |

| $i_{ m d}^*$         | Reference value of $i_{\rm d}$                                                       |

| $i_{ m inu}$         | DC input current of u-phase                                                          |

| $i_{ m in}$          | DC input current of three phases                                                     |

| $i_{ m n}$           | Neutral current                                                                      |

| $i_{ m q}$           | Q-axis current in current control                                                    |

| $i_{ m q}^*$         | Reference value of $i_{\rm q}$                                                       |

| $i_{ m u1}$          | Grid current of u-phase                                                              |

| $i_{ m u2F}$         | Inductor current of u-phase during SLG fault                                         |

| $i_{ m u2}$          | Inductor current of u-phase                                                          |

| $i_{\mathrm{u2}}^*$  | Reference value of $i_{\mathrm{u}2}$                                                 |

| $i_{\mathrm{uac}}^*$ | Reference value of AC component of u-phase inductor current                          |

| $i_{ m ucomp}^*$     | Reference value of AC component of u-phase inductor current after phase compensation |

| $i_{ m udc0}$        | DC current introduced for u-phase DC-capacitor voltage control                       |

| $i_{ m udc0}^*$      | Reference value of $i_{\rm udc0}$                                                    |

| $i_{ m udc}$         | Total DC current introduced in u-phase                                               |

### NOMENCLATURE

| $i_{ m udc}^*$  | Reference value of $i_{\rm udc}$                                     |

|-----------------|----------------------------------------------------------------------|

| $i_{ m v2F}$    | Inductor current of v-phase during SLG fault                         |

| $i_{ m v2}$     | Inductor current of v-phase                                          |

| $i_{ m v2}^*$   | Reference value of $i_{ m v2}$                                       |

| $i_{ m vdc0}$   | DC current introduced for v-phase DC-capacitor voltage control       |

| $i_{ m vdc0}^*$ | Reference value of $i_{\rm vdc0}$                                    |

| $i_{ m vdc}$    | Total DC current introduced in v-phase                               |

| $i_{ m vdc}^*$  | Reference value of $i_{\text{vdc}}$                                  |

| $i_{ m w2F}$    | Inductor current of w-phase during SLG fault                         |

| $i_{ m w2}$     | Inductor current of w-phase                                          |

| $i_{ m w2}^*$   | Reference value of $i_{ m w2}$                                       |

| $i_{ m wdc0}$   | DC current introduced for w-phase DC-capacitor voltage control       |

| $i^*_{ m wdc0}$ | Reference value of $i_{ m wdc0}$                                     |

| $i_{ m wdc}$    | Total DC current introduced in w-phase                               |

| $i_{ m wdc}^*$  | Reference value of $i_{ m wdc}$                                      |

| $i_{ m z0}$     | ZSC introduced for DC-capacitor overall voltage control              |

| $i_{ m z0}^*$   | Reference value of $i_{\rm z0}$                                      |

| $i_{ m zp}$     | ZSC introduced for DC-capacitor cluster balancing control            |

| $i_{ m zp}^*$   | Reference value of $i_{\rm zp}$                                      |

| $i_{ m z}$      | ZSC introduced in each phase inductor current                        |

| $i_{ m z}^*$    | Reference value of $i_{\rm z}$                                       |

| k               | Ratio of $I_{\rm dc}$ and $I_{\rm ac}$ in high DC input voltage case |

| $K_{ m P}$      | Proportional coefficient of the individual current control           |

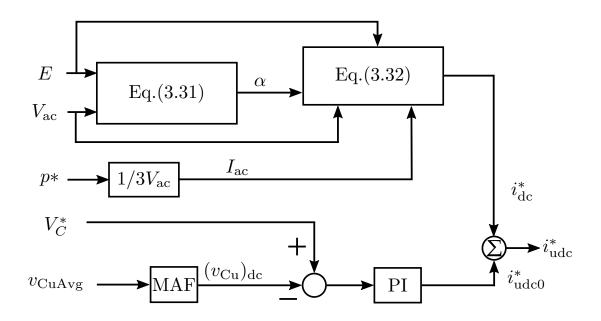

$K_{\rm vI}$ Integral coefficient of the DC-capacitor voltage PI control  $K_{\rm vP}$ Proportional coefficient of the DC-capacitor voltage PI control LInductor Leakage inductance of Transformer Voltage sag coefficient mNChopper-cell number per phase Reference value of three-phase output active power  $P_{\rm a}$ Output power of PV array in simulation  $P_{\rm inu}$ DC input power of u-phase inverter Maximum output of PV array  $p_{\max(t)}$  $P_{\text{outu}}$ AC output power of u-phase inverter Output function of PV array  $p_{\text{out}(t)}$  $P_{disu}$ Power disturbance of u-phase caused by SLG fault  $P_{disv}$ Power disturbance of v-phase caused by SLG fault  $P_{disw}$ Power disturbance of w-phase caused by SLG fault Reference value of three-phase output reactive power  $V_{\rm ac}$ RMS value of the AC side line-to-neutral phase grid voltage Reference value of the output voltage of the j-th cell in u-phase auxiliary  $v_{\text{Aui}}^*$ converter Auxiliary converter output voltage of u-phase  $v_{\mathrm{Au}}$  $v_{\rm Au}^*$ Reference value of  $v_{\rm Au}$ Arithmetic average value of all the DC-capacitor voltage of three phases  $v_{\rm CAvg}$ Minimum DC-capacitor voltage of each cell  $v_{\rm Cmin}$

### NOMENCLATURE

| $v_{ m conu}$        | Inverter line-to-neutral output voltage of u-phase                                              |

|----------------------|-------------------------------------------------------------------------------------------------|

| $v_{ m conu}^*$      | Reference value of $v_{\rm conu}$                                                               |

| $v_{ m conv}$        | Inverter line-to-neutral output voltage of v-phase                                              |

| $v_{\rm conv}^*$     | Reference value of $v_{\rm conv}$                                                               |

| $v_{ m conw}$        | Inverter line-to-neutral output voltage of w-phase                                              |

| $v_{\rm conw}^*$     | Reference value of $v_{\text{conw}}$                                                            |

| $v_{\mathrm{Cu}1}$   | DC-capacitor voltage of the first cell of u-phase                                               |

| $v_{ m CuAvg}$       | Arithmetic average value of all the DC-capacitor voltage of u-phase                             |

| $v_{ m CuN}$         | DC-capacitor voltage of the $N$ -th cell of u-phase                                             |

| $v_{ m Cv1}$         | DC-capacitor voltage of the first cell of v-phase                                               |

| $v_{ m CvAvg}$       | Arithmetic average value of all the DC-capacitor voltage of v-phase                             |

| $v_{ m CvN}$         | DC-capacitor voltage of the $N$ -th cell of v-phase                                             |

| $v_{\mathrm{Cw1}}$   | DC-capacitor voltage of the first cell of w-phase                                               |

| $v_{\mathrm{CwAvg}}$ | Arithmetic average value of all the DC-capacitor voltage of w-phase                             |

| $v_{\mathrm{CwN}}$   | DC-capacitor voltage of the $N$ -th cell of w-phase                                             |

| $V_{ m dF}$          | $\operatorname{D-axis}$ component of transformer secondary voltage used in PLL during SLG fault |

| $V_{ m d}$           | D-axis component of transformer secondary voltage used in PLL                                   |

| $v_{ m d}$           | D-axis voltage in current control                                                               |

| $v_{ m MuF}$         | Main converter output voltage of u-phase during SLG fault                                       |

| $v_{ m Mu}$          | Main converter output voltage of u-phase                                                        |

| $v_{ m Mu}^*$        | Reference value of $v_{ m Mu}$                                                                  |

| $v_{ m MvF}$         | Main converter output voltage of v-phase during SLG fault                                       |

| $v_{ m q}$         | Q-axis voltage in current control                                          |

|--------------------|----------------------------------------------------------------------------|

| $v_{ m u1F}$       | U-phase line-to-neutral primary (grid) voltage of transformer during fault |

| $v_{ m u2F}$       | U-phase line-to-neutral secondary voltage of transformer during fault      |

| $v_{ m u2}$        | U-phase line-to-neutral secondary voltage of transformer                   |

| $v_{ m u2}^*$      | Reference value of $v_{ m u2}$                                             |

| $v_{ m udc}^*$     | Output of proportional regulator in individual current control             |

| $v_{\mathrm{uw}1}$ | Line-to-line (u-w) grid voltage                                            |

| $v_{ m v1F}$       | V-phase line-to-neutral primary (grid) voltage of transformer during fault |

| $v_{ m v2F}$       | V-phase line-to-neutral secondary voltage of transformer during fault      |

| $v_{ m v2}$        | V-phase line-to-neutral secondary voltage of transformer                   |

| $v_{ m v2}^*$      | Reference value of $v_{\rm v2}$                                            |

| $v_{ m vu1}$       | Line-to-line (v-u) grid voltage                                            |

| $v_{ m w1F}$       | U-phase line-to-neutral primary (grid) voltage of transformer during fault |

| $v_{ m w2F}$       | U-phase line-to-neutral secondary voltage of transformer during fault      |

| $v_{ m w2}$        | W-phase line-to-neutral secondary voltage of transformer                   |

| $v_{ m w2}^*$      | Reference value of $v_{ m w2}$                                             |

| $v_{ m wv1}$       | Line-to-line (w-v) grid voltage                                            |

| $V_C^*$            | Reference value of DC-capacitor voltage                                    |

### Introduction

This dissertation presents a detailed study of a novel three-phase inverter for utility-scale PV (photovoltaic) systems where multiple cascaded bidirectional chopper cells and a three-phase line-frequency transformer with a three-limb core are used. With the accelerated development of the PV generation systems, the generation capacity of the PV systems is growing into utility scale, and it brings challenges to conventional PV inverters [1]–[6]. Therefore, new topology structure of PV inverter is required.

### 1.1 Research Background

Nowadays, PV generation system is no more an unfamiliar concept to everyone. It could be as small as several square meters which is able to be put on your rooftop or as large as tens of square kilometers which takes you several hours to walk across it. The former is preferred to be regarded as a PV chargeable battery connected to some electrical furnitures, and the latter is called as utility-scale PV generation system. For existing utility-scale PV generation systems connected to grids, conventional two- or three-level three-phase PV inverters are used as the connection interface between them because it is necessary to convert DC (direct current) power into AC (alternating current) power. However, the fast development of the PV generation systems brings challenges to them.

#### 1.1.1 Development of PV Energy

To reduce the consumption of fossil fuels (coil, gas, oil), which cause more pollution and will be exhausted someday [7], the contribution from the renewable energy sources is being increased. Among them, the PV energy is the fastest developing one. It is reported that

Figure 1.1: PV electricity generation of Europe, US, China, and Japan.

the global PV energy production in 2021 is over 1000 TWh and it is estimated that this number should reach 6970 TWh to achieve long-term carbon neutrality [8], which means the developing speed will be even faster.

Fig. 1.1 shows the contribution of PV electricity generation of four regions, the PV generation technology development of which are boosting in last ten years [9]–[12]. According to Fig. 1.1, it is obvious that China has the most contribution of PV electricity generation, which reached 260.5 TWh in 2020. The fast increase of PV generation contribution of China is the result of following the president's call for an "energy revolution" and the "fight against pollution" [11]. But it is also the result pushed by the large consumption requirement because of its large population. The data from IEA (international energy agency) show that the contribution of PV generation of Europe and US (United States) have similar trend and it is estimated that both regions are in positions to deliver more reliable, more affordable, and more environmental sustainable energy systems. Japan has the lowest relative contribution of PV generation among them. However, this number increased from 4839 GWh to 88 701 GWh in the last decade, which is an 18-fold increase and it will increase even faster to achieve its ambition of carbon-neutrality by 2050.

Figure 1.2: Utility-scale solar PV auction contract and wholesale prices in four EU countries, quarterly averages from 2016-2022.

Meanwhile, the energy market also stimulates the development of PV energy generation. Historically, long-term contract prices from utility-scale PV generation systems have been higher than wholesale prices of fossil fuels in many large EU (European Union) markets. However, significant change happened in 2021 according to the report from IEA [13]. The prices of fossil fuels have risen at an incredible rapid speed since the last quarter of 2021, which broke historic records in many parts of the world and this is caused by the war. Consequently, even the highest price of utility-scale PV generation system contracts over the last five years is much lower than the wholesale prices of fossil fuels nowadays, which is shown in Fig. 1.2 [14].

Because of this dramatic change in the energy market, more and more investment is poured into the PV generation system, which is shown as Fig. 1.3 [15]. It is shown in Fig. 1.3 that the investment in the fossil fuels is kept at a low level compared with the renewable energy, and the investment in the PV generation system is estimated to be over 360 billion dollars in 2023. As a result, more and more utility-scale PV generation systems are built and their capacity are increasing rapidly, which brings challenges to the conventional PV inverters.

Figure 1.3: Global annual investment in energy generation.

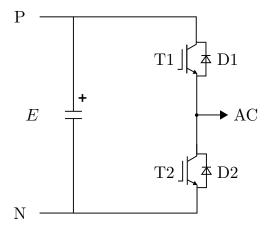

Figure 1.4: Conventional two-level PV inverters.

Figure 1.5: Conventional three-level PV inverters: a) three-level I-type, b) three-level T-type.

#### 1.1.2 Conventional PV Inverter

The utility-scale PV generation system can be divided into the grid-connected system and the stand-alone system [16], [17], where the former uses the conventional two- or three-level inverters for grid connection. With the development of the utility-scale PV generation systems, the DC input voltage has been increasing. Recent studies reveal that the installation cost can be reduced significantly by increasing the DC input voltage from 1 kV to 1.5 kV [18]-[21]. Because of the higher DC input voltage, more PV modules are able to be installed per string, which decreases the conductor mass and the number of CBs (combiner boxs) [22]. In this situation, the conventional two-level inverters shown in Fig. 1.4, which are widely applied to existing 1-kVdc PV systems, cannot satisfy the requirements of the systems because the power losses are large and the filtering requirement is high [23]–[26]. In contrast, the three-level inverters are widely used in the existing 1.5kVdc PV systems, and two well-known topologies of three-level inverters are shown in Figs. 1.5a and 1.5b. Compared to the two-level inverter, the three-level ones have lower total cost and higher efficiency when switching frequency is over 2 kHz. There are two more diodes in the three-level I-type inverter and it is noteworthy that the voltage ratings of the four IGBTs (insulated-gate bipolar transistors) are the same in the three-level I-type inverter, whereas the voltage ratings of T1 and T4 are higher than those of T2 and T3 in the three-level T-type inverter. Specifically, the efficiency performance of three-level T-type inverter is better than that of the three-level I-type one in most of the applications in 1.5-kVdc PV generation systems [1], [27].

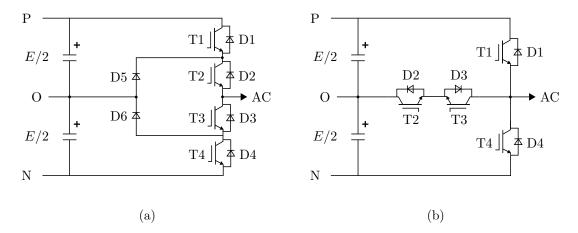

On the other hand, the power rating of the utility-scale PV generation systems has grown into megawatt level [1], [27]–[30] as the consumption requirement increases. Meanwhile, this trend put the conventional three-level inverter in a dilemma because of the power characteristic of the PV array. The relationships between the PV array voltage,  $E_{\rm a}$ , output current,  $I_{\rm a}$ , and the output power,  $P_{\rm a}$ , at different temperatures are shown in Figs. 1.6a and 1.6b. The  $P_a$ - $V_a$  and  $I_a$ - $V_a$  characteristics are obtained from a PSCAD simulation under a irradiation level of 1000 W/s<sup>2</sup>. It is noteworthy that this simulation is not based on reality data and it is only for a brief explanation. It is obvious that the  $P_{\rm a}$ - $V_{\rm a}$  and  $I_{\rm a}$ - $V_{\rm a}$  characteristics are affected by the ambient temperature and the maximum power point fluctuates during the day. In order to keep the PV array output at the maximum point all the time, the PV generation system has an MPPT (maximum-powerpoint-tracking) function to adjust the output voltage of the PV array. The upper limit of the MPPT range is mostly decided by the voltage rating of the power devices, which is not a concern. However, the lower limit of it is decided by the voltage relationship between the DC side and the AC side. In the case of using conventional three-level inverters, this relationship is shown as

$$E \ge \sqrt{6}V_{\rm ac},\tag{1.1}$$

with third-order harmonics component introduced, where E is the input voltage of DC side and  $V_{\rm ac}$  is the RMS (root-mean-square) value of the AC side line-to-neutral phase grid voltage. To operate the PV system throughout the year,  $V_{\rm ac}$  has to be set based on the minimum DC input voltage at the highest temperature in summer, which results in a large AC current and a large conduction loss, especially in a megawatt level PV system. In order to reduce the conduction loss, one of the methods is to increase  $V_{\rm ac}$ . However, this method narrows the range of MPPT. For example, a PV system with an RMS line-to-line AC voltage of 660 V ( $\sqrt{3}V_{\rm ac}=660$  V) with an MPPT range of 960 V to 1300 V was development and this range was narrowed down to 1005 V to 1300 V when the RMS line-to-line AC voltage increased to 690 V [31]. In other words, the available MPPT range will be curtailed if the conventional three-level inverters are applied to utility-scale PV generation systems. When the MPPT range is narrowed, the power efficiency of the PV

Figure 1.6: PV array power characteristics obtained from PSCAD simulation: a)  $P_{\tt a}\text{-}V_{\tt a}$ , b)  $I_{\tt a}\text{-}V_{\tt a}$ .

array will decrease, which is defined as:

$$\eta = \frac{\int p_{\text{out}}(t) \, dt}{\int p_{\text{max}}(t) \, dt}.$$

(1.2)

On the other hand, if the MPPT range can be widened, more output power can be obtained.

Consequently, PV systems based on state-of-the-art MMCC (modular multilevel cascade converter) topologies have drawn attention as the connection interface between the PV systems and the grid in recent years [32]–[35].

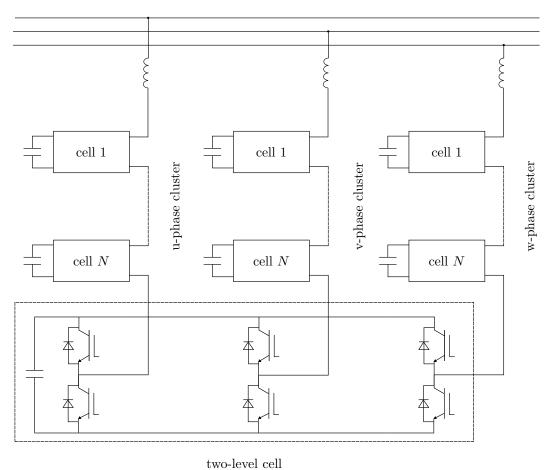

## 1.1.3 The MMCC

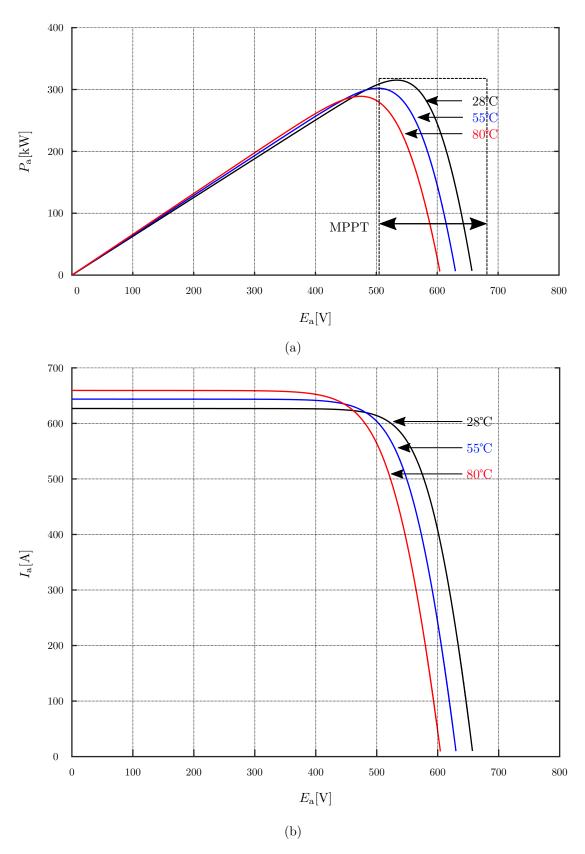

Nowadays, the MMCC technology is well-developed and the MMCCs are more and more used in AC-DC and DC-DC systems. This section will give out a brief introduction of MMCC. Basically, there are four circuit configurations of MMCC [32]:

- 1. SSBC (single-star bridge-cells) (Fig. 1.7a);

- 2. SDBC (single-delta bridge-cells) (Fig. 1.7b);

- 3. DSCC (double-star chopper-cells) (Fig. 1.7c with cell Fig. 1.7d);

- 4. DSBC (double-star bridge-cells) (Fig. 1.7c with cell Fig. 1.7e).

The SSBC is different from the SDBC in the connection topology of three-phase clusters, whereas the DSCC is different from the DSBC in the types of the cells. It is noteworthy that the two non-coupled inductors on the same phase cluster can be replaced by one coupled inductor to reduce the size and the weight. These MMCCs can output multilevel waveforms, which can reduce the size of passive filter in the grid-connected applications. Besides, owing to their different structures, each of them has their unique application cases.

## 1.1.3.1 Application of the SSBC

Because of the star-connection of the three-phase clusters in SSBC, there is no flowing route for the zero-sequence current. Therefore, the SSBC can only control the positive-sequence leading and lagging reactive power. Consequently, the best application case of the SSBC is not STATCOM (static synchronous compensator) but the BESS (battery

Figure 1.7: Basic circuit configurations of MMCC and their cell circuit configurations: a) SSBC, b) SDBC, c) DSCC or DSBC, d) Chopper cell, e) Bridge cell.

energy storage system) [36], [37]. When it comes to the case of grid-level BESS, the SSBC can function as an active power controller at the lowest cost compared with other three MMCCs. Therefore, the cell number of the SSBC, N, is always the minimum among these four MMCCs.

## 1.1.3.2 Application of the SDBC

Compared to the SSBC, the zero-sequence current can flow in the three-phase clusters of SDBC because of the delta-connection. Consequently, the SDBC has the capability of controlling not only the positive-sequence reactive power but also the negative-sequence reactive power, which means that the SDBC can be used as a STATCOM. Even though the DSCC and the DSBC also have the circulating routes for the zero-sequence current, the SDBC has the minimum cell number in the same application case, which leads to a lower cost. As a result, the SDBC is mostly applied to the STATCOM [38]. In addition, the SDBC has the capability to control the positive-sequence reactive power, negative-sequence reactive power, and low-frequency active power at the same time. References [39] and [40] verified the experimental performance of the SDBC used in STATCOM with a downscaled model.

## 1.1.3.3 Application of the DSCC and the DSBC

The DSCC and the DSBC have almost the same circuit configuration and control method except for the types of cells. However, the application of them are different because of the difference in cell types. The DSCC is mainly applied to HVDC (high-voltage direct current) systems for high quality power transmission or to BTB (back-to-back) systems for changing the frequency between two different systems [41]. Also, it could be used as a multilevel inverter for medium-voltage motor drive [42] or for DC energy source grid connection [43].

Theoretically, the DSBC is able to be applied to most of the cases where the DSCC is used. However, the bridge cell has two more IGBT units than the chopper cell, which will increase the cost of the system. Therefore, the DSBC is only applied to some unique systems, such as the wind power systems and the PV systems. These systems are know as the PCS (power conditioning system) system [32], the DC-link voltage of which has a wide range of variation. The buck and boost function of the DSBC owing to the bridge cells is able to deal with this situation [44].

## 1.2 Research Objectives

The purpose of this dissertation is to introduce a novel three-phase PV inverter based on MMCC technologies that could solve the problems that the conventional two- or three-level inverter are facing. The main research objectives of this dissertation are:

• A single-stage three-phase PV inverter with high AC output voltage and wide MPPT range for utility-scale grid-connected PV systems based on the MMCC technologies. As explained in the previous section, the available MPPT range is narrow when the conventional three-level inverter is applied to utility-scale PV systems. Therefore, it is necessary to widen the MPPT range to increase the power efficiency. Even though a front-end boost converter can widen the MPPT range of the conventional three-level inverter, it can also cause more loss. In other words, a single-stage PV inverter is the best choice to decrease the loss. By using inverters based on MMCC technologies, the volume of the passive filters can be decreased. It is noteworthy that the MPPT control can be achieved with a PV simulator and a common method. However, it is not the main topic of this dissertation.

Therefore, a voltage source is used in this dissertation, instead.

- Initial charging of the DC-capacitor voltage in each cell of the MMCC technologies based PV inverter. Without charging the DC-capacitor voltage to a reference value, the MMCC circuit cannot operate the startup process. In the practical application, it is unrealistic to attach additional charging circuits to the capacitors in MMCCs in terms of cost and reliability. Therefore, it is necessary to propose an initial charging method without using additional components.

- Test of the LVRT (low-voltage ride-through) capability of the proposed PV inverter under the common grid faults. Since the proposed PV inverter is based on the MMCC technology, each capacitor may suffer from overvoltage/undervoltage during the fault, which may result in the destruction of power devices and/or operational failures. Similarly, the potential overcurrent during the fault may cause damage to power devices [45], [46]. Therefore, the LVRT capability of the proposed PV inverter should be tested.

- Evaluation of the proposed PV inverter in terms of cost and efficiency. Generally speaking, the selection of the cascaded cell (submodule) number of the MMCCs is crucial. When the MMCCs are applied to high-voltage applications such as high-voltage direct-current systems, the required cell number is mainly determined by the required voltage levels, and the number of cells can reach several hundreds, which eventually increases the cost and volume of the converter [32], [38]. Therefore, performance comparison between the proposed PV inverter using different number of cells may help to find out how to optimize the proposed PV inverter.

## 1.3 Dissertation Outline

The main body of this dissertation is divided into seven Chapters with one Appendix.

The Chapters of the dissertation deal with the main ideas of the research efforts. A list of publications and achievements follows after the last Chapter.

• Chapter 1 provides an introduction of the research topic that is explained in this dissertation. It starts with the research background that describes the development of PV energy, indicates the problems that the conventional two- or three-level PV

inverters are facing, and introduces the concept of MMCC. Research objectives follow the above section, which are carried out to solve the problems describe above. In the end, this Chapter offers an outline of the entire dissertation, where the main content of each Chapter is summarized for the convenience of readers.

- Chapter 2 provides a detailed literature review of all the individual research topics which are discussed in each Chapter, including PV inverters, LVRT capability of MMCC inverters, and decreasing the cost and loss of MMCC inverters. The necessity of the research in this dissertation is revealed by the end of this Chapter.

- Chapter 3 presents the novel three-phase PV inverter for utility-scale PV systems using multiple bidirectional choppers in detail. The circuit configuration, the operation principles, and the current control method based on three-phase d-q-0 transformation are explained with figures and theoretical equations. A new DC-capacitor voltage initial charging method is also proposed in this Chapter. The experimental verification is conducted using a downscaled model and the waveforms of the initial charging and different operational cases are shown. In the end, the remaining problem is discussed.

- Chapter 4 proposes a new individual phase current control instead of the three-phase current control introduced in Chapter 3 to solve the problem describe in the above Chapter. The new current control method is explained with block diagrams and theoretical equations. Similar to Chapter 3, the experimental verification is carried out using the same downscaled model to prove the reliability of the new current control method and the waveforms in different operation situations are shown. In addition, the loss breakdown and the efficiency comparison between the proposed PV inverter and the conventional three-level T-type inverter are also performed theoretically. In the end, the THD (total harmonic distortion) performance and the efficiency of the downscaled model are shown.

- Chapter 5 presents the LVRT capability of the proposed PV inverter under the SLG (single-line-to-ground) and 3P (three-phase) faults. A theoretical analysis focusing on the LVRT behaviors of the proposed inverter, which includes the capacitor voltage fluctuation, the reason for the overmodulation and the current spikes, and the limit of the LVRT capability/safety operation zone under the SLG fault is also provided.

## CHAPTER 1. INTRODUCTION

Since the analysis under the 3P can be done similar, it is left out in this dissertation. The LVRT capability is tested using the same downscaled model with a new AC power supply that can simulate the fault situations. The waveforms under different fault are shown and the comparison with the theoretical analysis results proves the reliability of the theoretical analysis.

- Chapter 6 compares the performance of the proposed PV inverter with two chopper cells and three chopper cells in terms of loss, efficiency, THD performance, and experimental performance during steady and fault states to evaluate the chopper-cell number. The comparisons are based on theoretical calculation and experimental verification. The main purpose of this Chapter is to optimize the performance of the proposed PV inverter in practical application.

- Chapter 7 conclude the entire research work and summarized all the results achieved

in the previous Chapters. In addition, some future works are provided for the convenience of subsequent researchers.

# Literature Review

With the development of PV systems, the conventional two- or three-level inverters introduced in Chapter 1 are facing problems to satisfy the systems requirement. To solve the problems, different kinds of PV inverters have been studied. Each of them has different topology and unique application. However, they are not suitable to the application case in this dissertation, which is a utility-scale (1.5-kVdc) grid-connected PV system with a AC grid voltage of 6.6 kV.

This Chapter will provide a detailed literature review of all the research topics that will be discussed in the following Chapters. Specifically, it will start with a review of different PV inverter topologies to explain the necessity of the PV inverter topology proposed in this dissertation. Afterward, the importance of LVRT capability of the MMCC based inverter will be presented. Finally, some efforts on optimizing the MMCC systems will be demonstrated.

# 2.1 Topologies of PV Inverters

Basically, the PV inverters are classified into two types based on the power processing stages [47]:

- Single-stage inverters;

- Multiple-stage inverters.

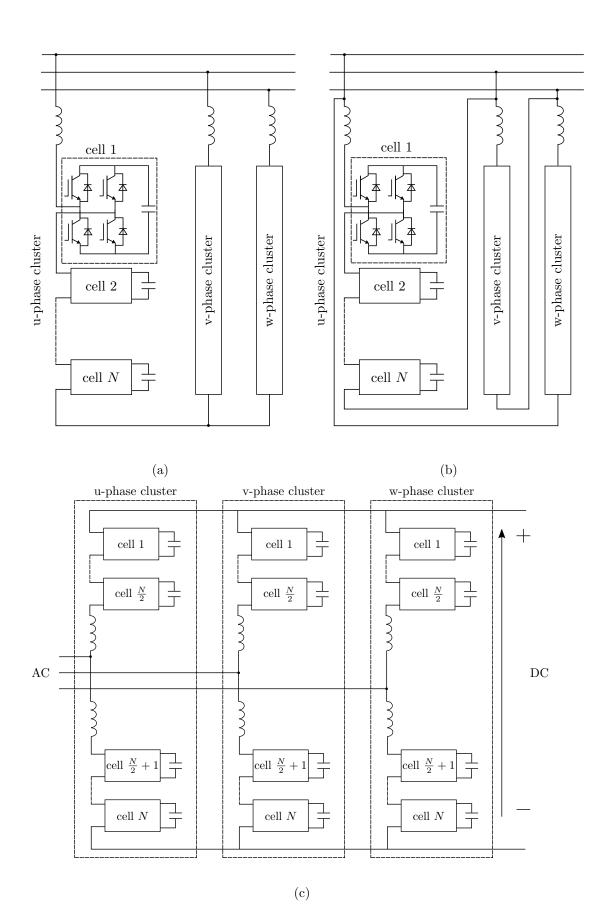

As shown in Fig. 2.1, there is only one power processing stage in the single-stage inverter, whereas there are more than one power processing stage in the multiple-stage inverter. In

Figure 2.1: PV inverter types: a) single-stage inverter, b) multiple-stage inverter.

Figure 2.2: HERIC topology.

addition, surveys reveal that these two types of PV inverters are developed in different ways to adapt the change of the PV systems.

## 2.1.1 Single-stage Inverters

Because most topologies of the single-stage inverters are based on the conventional twoor three-level inverters [48], it is hard for them to widen the range of DC input voltage,

which means it is hard to widen the MPPT range. Even though some single-stage boost

or buck-boost inverter topologies proposed in [49]–[52] can amplify the DC input voltage

for MPPT, these type of single-stage inverters still suffers from narrow range of DC input

voltage, lower power capacity, and low power quality [48]. Therefore, a large amount of

research has been carried out to increase the efficiency and the circuit reliability of the

single-stage inverter. For example, the line frequency transformer is removed from the

single-stage inverter because it accounts for 2% of the total loss at peak efficiency and

a large part of the the inverter's weight [53]. One of the famous single-stage inverter

topologies is known as HERIC (high efficient and reliable inverter concept) topology [54],

which is shown in Fig. 2.2. S5 is on in the positive half cycle of the grid voltage and off in

the negative half cycle of it, whereas S6 is off in the positive half cycle of the grid voltage

Figure 2.3: H5 topology.

and on in the negative half cycle of it. By this operational principle, the output current on the AC (grid) side during the current free-wheeling period will not flow in the diodes of the H-bridge inverter on the DC side, which means that the DC (PV) side is isolated from the AC (grid) side during this period. Another famous single-stage inverter topology is the H5 topology shown in Fig. 2.3 [54]. It is famous for its simple topology and can also isolate the PV system from the grid during the current free-wheeling period. In Fig. 2.3, S1 and S2 switch at grid frequency, while S3, S4, and S5 switch at higher frequency under the PWM (pulse-width modulation) control. It is noteworthy that the switching of S5 is synchronized with S3 and S4, which means that the PV system is isolated from the grid during the current free-wheeling period.

In summary, most of the single-stage inverters have transformerless topologies to achieve a higher frequency [55] and the topologies are of high reliability even without the isolation provided by the transformer. However, these transformerless high-efficiency single-stage PV inverters cannot be applied to the utility-scale PV systems because transformer is necessary to step-up the voltage of the PV systems to the voltage level of the medium-voltage AC grids [56]–[58], e.g., 6.6 kV in Japan or 13.8 kV in US.

## 2.1.2 Multiple-stage Inverters

On the other hand, the multiple-stage inverters attached with front-end boost converters can be applied instead of the single-stage inverters to widen the MPPT range [59]–[61]. The conventional non-isolated boost converters are widely used in utility-scale PV systems (e.g., in [30]), whereas the introduction of the boost converters may result in increased

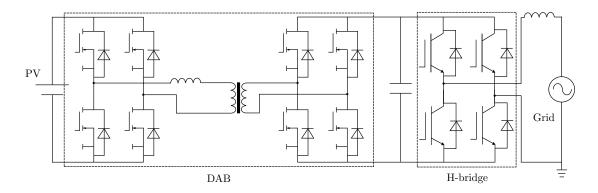

Figure 2.4: DAB application in PV systems.

Figure 2.5: Gradational voltage inverter.

cost and loss. A method of applying string mini-boost converters at the input of the PV inverter was presented to widen the available MPPT range [62]. Specifically, the mini-boost converters are applied to every string of the PV array and boost the different DC input voltages of each PV array to the same voltage, which is acceptable for the PV inverter input. However, this may increase the complexity of the control of the entire system, especially in utility-scale PV systems with many strings. DAB (dual-active-bridge) converters have also been applied to some PV systems owing to their high efficiency, small size, and flexible connection [63]–[65]. However, the DAB converter is also connected with a DC-AC inverter as a part of a multiple-stage inverter as shown in Fig. 2.4, which will sacrifice the high efficiency and the flexibility of the DAB converters. In addition, the implementation would be more difficult as the system scales up.

Table 2.1: Differences between gradational voltage inverter and proposed PV inverter.

|                                | Gradational voltage inverter | Proposed PV inverter   |

|--------------------------------|------------------------------|------------------------|

| Cell structure                 | 1 bridge cell                | Multiple chopper cells |

| Neutral line                   | No                           | Yes                    |

| Main conv. control method      | SVPWM                        | Fixed duty             |

| Aux. conv. control method      | SVPWM                        | Phase-shifted PWM      |

| Main conv. switching frequency | 1 kHz                        | 50 Hz                  |

| Aux. conv. switching frequency | $10\mathrm{kHz}$             | $7.2\mathrm{kHz}$      |

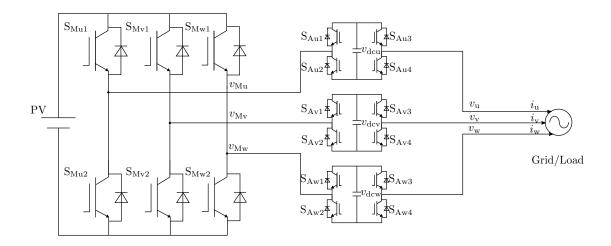

## 2.1.3 Gradational Voltage Inverters

An MMCC based single-stage inverter is proposed by Mitsubishi Electric [66] and the circuit configuration is shown in Fig. 2.5. In this inverter, a bridge cell is cascaded connected to a conventional two-level inverter (main converter) in each phase. The bridge cell works as an auxiliary converter switching at a higher frequency, which can decrease the high frequency harmonics components. In addition, the SVPWM (space-vector pulse-width modulation) control is used. The main idea of the PV inverter proposed in this dissertation is similar to this gradational voltage inverter. However, there are many differences between them, which are concluded in the following table. The detail of the content in Table 2.1 will be illustrated later.

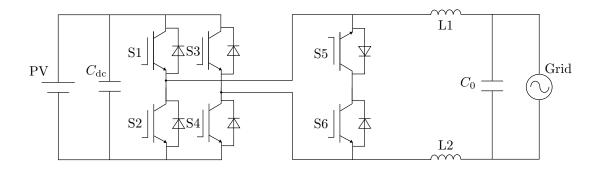

In order to widen the MPPT range and achieve the high efficiency at the same time, a new single-stage three-phase utility-scale MMCC technology based PV inverter is proposed in this dissertation. It is composed of a three-phase inverter and a three-phase line-frequency transformer with a three-limb core working as a step-up transformer for grid connection. The inverter is composed of a main converter, which is a bidirectional chopper, and an auxiliary converter, which is composed of multiple chopper cells. The detail of it will be described in Chapters 3 and 4.

# 2.2 LVRT Capability of MMCC Topologies

The LVRT capability of the MMCC topologies is always an issue for the MMCC rectifiers/inverters because of their complex operation principles and controls. It is required that the MMCC rectifiers/inverters should be able to maintain the grid-connected operation for several fundamental cycles during the fault and restore the normal operation after the fault is cleared. However, the floating capacitor in the cells may suffer from overvoltage/undervoltage during the fault which may result in the destruction of power devices and/or operational failures. Similarly, the potential overcurrent during the fault may cause damage to power devices, especially the MOSFETs (metal-oxide-semiconductor field-effect transistors) and the IGBTs [45], [46]. Among these problems, the unbalance between the DC-capacitor voltages of each phase cluster of the MMCC during the grid faults attracts most concerns [67]–[71].

So far, a significant amount of research has been carried out for verifying the LVRT capability of various MMCC inverters. A combination of ZSV (zero-sequence voltage) injection and NSC (negative-sequence current) injection was proposed in [72] for the MMCC-SSBC to regulate each capacitor voltage during the grid fault. Specifically, the MMCC-SSBC is used as a STATCOM in [72]. By the specific ZSV and NSC injection, the modulation index and the output peak current can be limited so that over-modulation and overcurrent will not happen while the control is trying to balance the DC-capacitor voltages.

In [73], the LVRT capability was studied for MMCC-SDBC. A flexible DC-capacitor voltage balancing control was proposed to improve the LVRT capability of MMCC-SDBC in the DERs (distributed energy resources) systems. By adjusting the proportion of NSC and ZSC (zero-sequence current) in the injection current, the MMCC-SDBC is able to operate under unbalance power condition caused by the grid faults. In addition, it is shown by the comparisons that the LVRT capability of MMCC-SDBC is worse than that of MMCC-SSBC, even though the balancing capability of MMCC-SDBC is better.

In [74], the LVRT capability was studied for HCC (hybrid cascade converter). The HCC topology is shown in Fig. 2.6 and bridge cells shown in Fig. 1.7e are used in the cell blocks. By replacing some of bridge cells in SSBC with a three-phase two-level cell, the switching loss of HCC was reduced significantly compared with that of SSBC. In addition, a new control block was added to the previous control and the LVRT capability of the HCC was proved well.