# T2R2 東京科学大学 リサーチリポジトリ Science Tokyo Research Repository

## 論文 / 著書情報 Article / Book Information

| 題目(和文)            | GPU を用いたコンピュータビジョンの高速化と最適化の研究                                                                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | GPU-Based Acceleration and Optimization Research on Computer Vision                                                                                                                        |

| 著者(和文)            | WANGCHENYU                                                                                                                                                                                 |

| Author(English)   | Chenyu Wang                                                                                                                                                                                |

| 出典(和文)            | 学位:博士(理学),<br>学位授与機関:東京工業大学,<br>報告番号:甲第12513号,<br>授与年月日:2023年9月22日,<br>学位の種別:課程博士,<br>審査員:遠藤 敏夫,坂本 龍一,髙邉 賢史,脇田 建,佐藤 育郎                                                                     |

| Citation(English) | Degree:Doctor (Science),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第12513号,<br>Conferred date:2023/9/22,<br>Degree Type:Course doctor,<br>Examiner:,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                       |

| Type(English)     | Doctoral Thesis                                                                                                                                                                            |

# GPU-Based Acceleration and Optimization Research on Computer Vision

Department of Mathematical and Computing Science School of Computing

Tokyo Institute of Technology

Chenyu Wang

Supervisor: Toshio Endo

Ph.D. Dissertation

June 2023

## Abstract

In this dissertation, we present an in-depth study on GPU-based acceleration and optimization of computer vision task models, pursuing the trade-off between performance and speed of the model, and our research encompasses two primary research.

In our inaugural research, we focus primarily on the acceleration of the Single Shot MultiBox Detector (SSD), a model extensively adopted in object detection tasks. Given the computation-intensive nature of SSDs, we provide a comprehensive analysis of the challenges associated with performing their computations both effectively and efficiently. As a crucial part of our investigation, we proposed and implemented a solution for GPU acceleration. We successfully ported components previously computed on the CPU to the GPU and customized the model's components for optimal utilization of GPU resources. Our efforts particularly target the post-processing layer, which includes critical functions such as non-maximum suppression (NMS) and sorting. These functions, traditionally executed on the CPU, have now been skillfully migrated to the GPU. Our GPU-accelerated SSD model showcases superior detection speed without major sacrifices in object detection accuracy, achieving a superior trade-off between detection speed and model accuracy. This speed enhancement is accomplished by effectively leveraging the GPU's vast parallel processing capabilities and optimized memory management, translating into a substantial reduction in execution time. Our research underscores the significant potential and feasibility of using GPUs to accelerate object detection frameworks.

Next, we turn our focus to Transformer-based models, particularly the Swin Transformer. These architectures have proven to be remarkably effective in a wide range of computer vision tasks. However, their heavy computational requirements necessitate the implementation of efficient computing methods to enable their acceleration. Our objective is to harness the power of the GPU to expedite computations, all the while ensuring performance is preserved. In the original Swin Transformer architecture, we identify limitations, particularly concerning window information interaction when dealing

with large feature scales. To address these issues, we introduce the Pyramid Swin Transformer as an effective resolution. Although this refinement incurs some additional computational overhead, it adeptly manages the window information interaction problem intrinsic to large-scale feature dimensions. Consequently, our Pyramid Swin Transformer demonstrates commendable results across a range of computer vision tasks including image classification, object detection, semantic segmentation, and video recognition. This show-cases the effectiveness, scalability, and versatility of our solution, justifying the computational trade-off involved. we also make research into GPU-based acceleration techniques for the Swin Transformer architecture. We propose innovative parallel processing strategies for window-based multi-head self-attention mechanisms, achieving substantial computational performance improvements. Our parallel computing methods proved to be effective, scalable, and versatile for various computational conditions, offering new insights for GPU-based deep learning acceleration.

Overall, this dissertation presents novel methods for accelerating and improving computer vision tasks on GPUs while demonstrating the adaptability and scalability of these techniques in the context of state-of-the-art computer vision architectures.

## Acknowledgements

I would like to express my deepest gratitude to my esteemed advisor, Professor Endo, for welcoming me into his laboratory and providing invaluable guidance and support throughout my research journey. His mentorship has been a constant source of inspiration, and I am truly grateful for his unwavering belief in my potential. Professor Endo has not only offered his academic expertise but has also been a pillar of support in my personal life. Despite the significant differences between my previous research and my current endeavors, he has consistently offered tremendous help in selecting research topics, acquiring new knowledge, and navigating the challenges that have arisen during the course of my studies.

I would also like to extend my heartfelt appreciation to Professors Hirofuchi and Ikegami for their invaluable contributions to my research. Their insightful advice, constructive feedback, and expertise have greatly helped shape my work, enabling me to publish my research smoothly. The collaborations and discussions with them have enriched my understanding of the field and have fostered a conducive environment for intellectual growth and exploration.

Furthermore, I would like to acknowledge the contributions of my fellow lab members, who have provided a stimulating and supportive atmosphere throughout my research journey. Their camaraderie and encouragement have made my time in the laboratory an enjoyable and rewarding experience. I am grateful for the countless thought-provoking conversations and the shared moments of triumph and challenges that we have encountered together.

Lastly, I would like to express my profound gratitude to my parents for their unwavering love, support, and encouragement throughout my academic journey. Their sacrifices, understanding, and belief in my abilities have been instrumental in my pursuit of excellence in research. Their guidance and constant presence in my life have given me the strength and determination to overcome the obstacles I have faced and continue striving for success.

# Contents

| 1 | Intr | oduction                                                   |

|---|------|------------------------------------------------------------|

|   | 1.1  | Motivation                                                 |

|   | 1.2  | Problem Statement                                          |

|   | 1.3  | Contribution                                               |

|   | 1.4  | Thesis Structure                                           |

| 2 | Bac  | kground 15                                                 |

|   | 2.1  | Computer Vision                                            |

|   |      | 2.1.1 Basic Computer Vision                                |

|   |      | 2.1.2 Machine Learning-based Computer Vision 16            |

|   |      | 2.1.3 Deep Learning-based Computer Vision                  |

|   | 2.2  | GPU                                                        |

|   |      | 2.2.1 GPU Architectures                                    |

|   |      | 2.2.2 CUDA Platform                                        |

|   |      | 2.2.3 High-Performance Computing with GPUs $\dots \dots 3$ |

| 3 | Spe  | ed-up Single Shot Detector on GPU with CUDA 40             |

|   | 3.1  | Introduction                                               |

|   | 3.2  | Related Work                                               |

|   |      | 3.2.1 Object detection                                     |

|   |      | 3.2.2 High Speed of Feature extraction                     |

|   |      | 3.2.3 Single Shot Multibox Detector (SSD) 40               |

|   | 3.3  | Our Implementation and Optimization                        |

|   |      | 3.3.1 Problem of Current Research                          |

|   |      | 3.3.2 Pre-Processing                                       |

|   |      | 3.3.3 Feature Extraction Layer                             |

|   |      | 3.3.4 Proposal Layer                                       |

|   |      | 3.3.5 Post Processing                                      |

|   | 3.4  | Result & Analysis                                          |

|   | 0.1  | 3.4.1 Accuracy                                             |

|   |      | 3.4.2 Speed                                                |

## CONTENTS

|   | 3.5 | Conclusions                                           |

|---|-----|-------------------------------------------------------|

| 4 | Op  | timization for the Swin Transformer 70                |

|   | 4.1 | Introduction                                          |

|   | 4.2 | Related Work                                          |

|   |     | 4.2.1 Feature Pyramid Network                         |

|   |     | 4.2.2 Vision Transformer                              |

|   |     | 4.2.3 Swin Transformer                                |

|   |     | 4.2.4 Mask R-CNN                                      |

|   |     | 4.2.5 UPerNet                                         |

|   |     | 4.2.6 Adam Optimization Algorithm                     |

|   | 4.3 | Pyramid Swin Transformer                              |

|   |     | 4.3.1 Object Detection with FPN                       |

|   |     | 4.3.2 Semantic Segmentation Head                      |

|   |     | 4.3.3 Video Recognition Adaptations                   |

|   |     | 4.3.4 Experiment and Result                           |

|   | 4.4 | High-speed Window-based Multi-head Self-attention 106 |

|   | 1.1 | 4.4.1 Our Method                                      |

|   |     | 4.4.2 Result & Analysis                               |

|   | 4.5 | Conclusion                                            |

| 5 | Cor | nclusion & Future Work 119                            |

| Э |     |                                                       |

|   | 5.1 | Conclusion                                            |

|   | 5.2 | Future Work                                           |

| Α | Puł | olish List 138                                        |

# List of Figures

| 2.1  | Architecture of a Neural Network                                 |

|------|------------------------------------------------------------------|

| 2.2  | A CNN architecture                                               |

| 2.3  | Illustration of a pooling operation                              |

| 2.4  | VGG Net [115]                                                    |

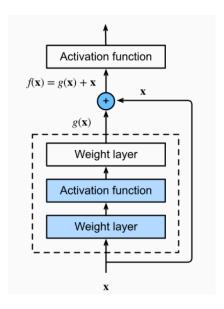

| 2.5  | Residual Block[136]                                              |

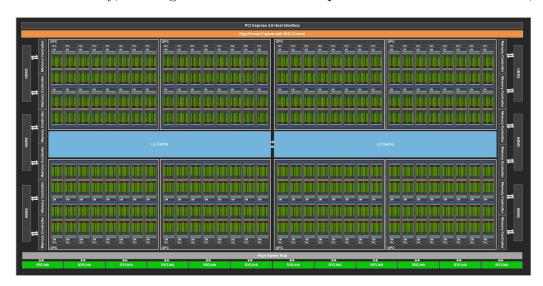

| 2.6  | NVIDIA A100 GPU architecture                                     |

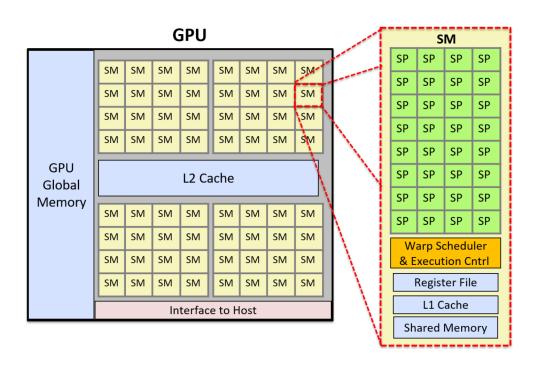

| 2.7  | GPU Architecture Unit[119]                                       |

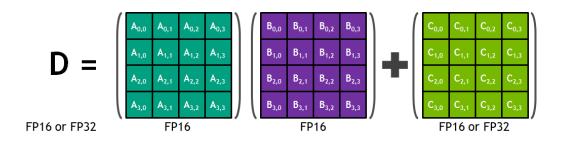

| 2.8  | Matrix Multiplication Operation with Tensor Cores[91] 38         |

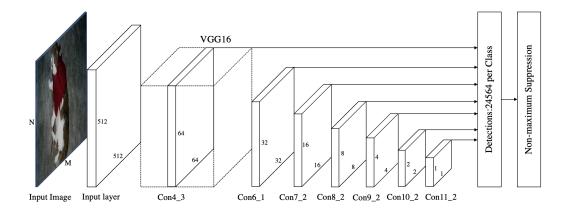

| 3.1  | Single Shot Multibox Detector Model (SSD512) 46                  |

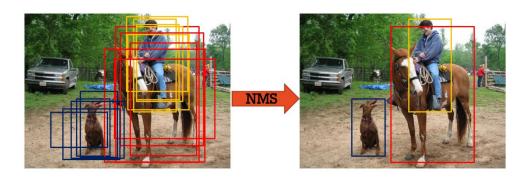

| 3.2  | Non-maximum Suppression algorithm                                |

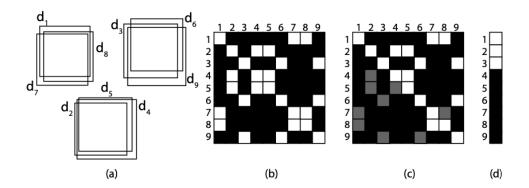

| 3.3  | Visualization of Map-reduce NMS proposal[92] 49                  |

| 3.4  | Post Processing Data Flow                                        |

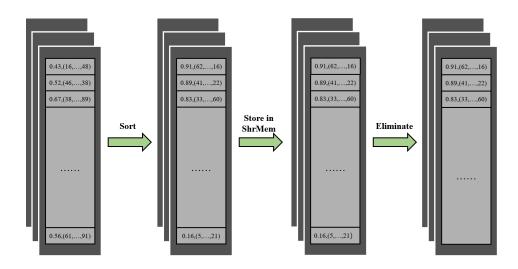

| 3.5  | Illustration of parallel merge sort with CUDA 57                 |

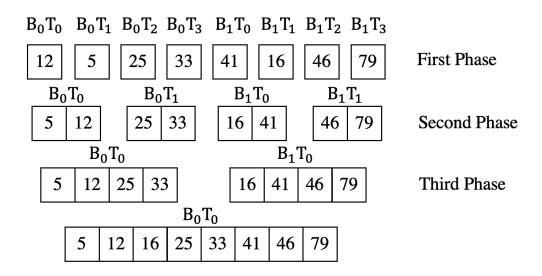

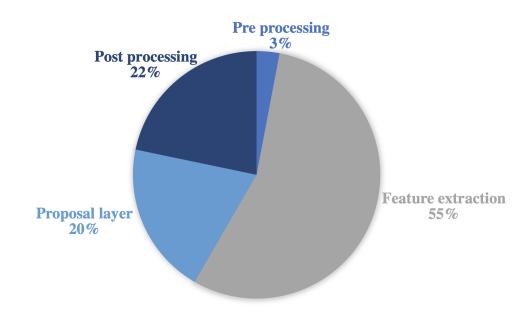

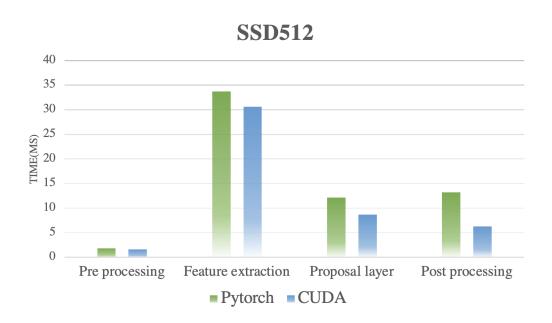

| 3.6  | Pytorch version of SSD512 time ratio 62                          |

| 3.7  | Execution time Comparison Result 63                              |

| 3.8  | Execution time Comparison Result with Other Framework $$ . $$ 68 |

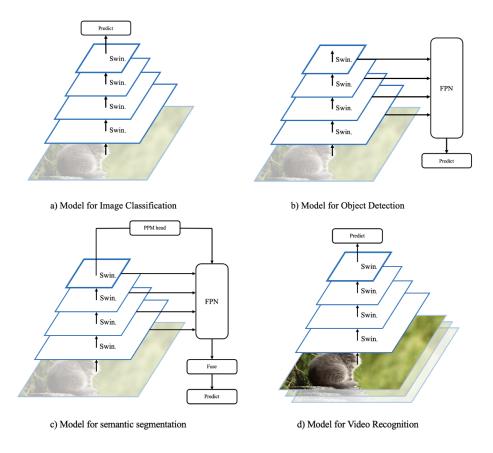

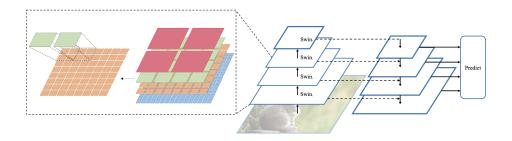

| 4.1  | Pyramid Swin Transformer                                         |

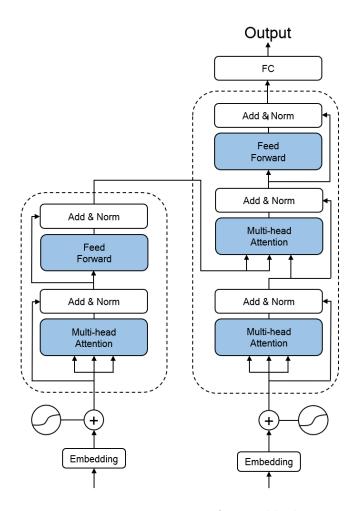

| 4.2  | Transformer block                                                |

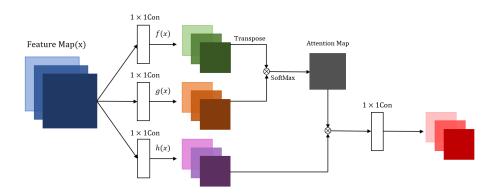

| 4.3  | Self Attention Architecture                                      |

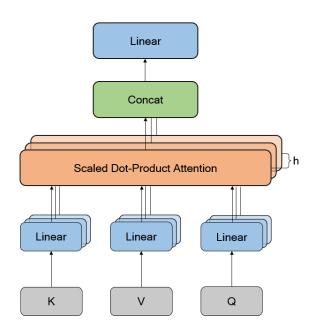

| 4.4  | Multi-head Attention Architecture 80                             |

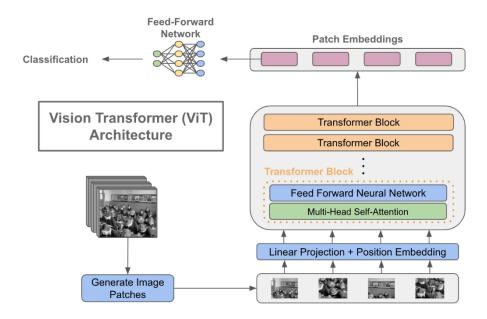

| 4.5  | Vision Transformer[15]                                           |

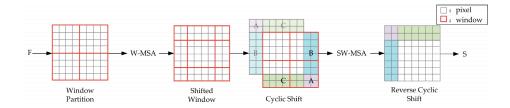

| 4.6  | Shifted Window-based Self-Attention                              |

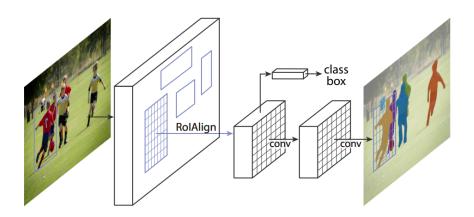

| 4.7  | Mask R-CNN[46]                                                   |

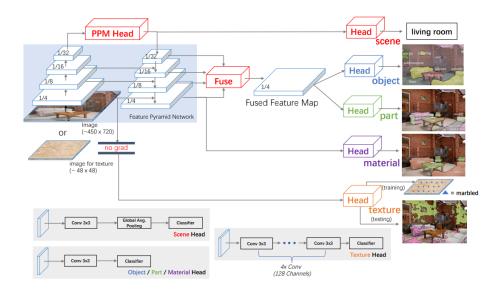

| 4.8  | UPerNet[129]                                                     |

| 4.9  | Swin Transformer architecture problem                            |

| 4.10 | Pyramid Swin Transformer architecture                            |

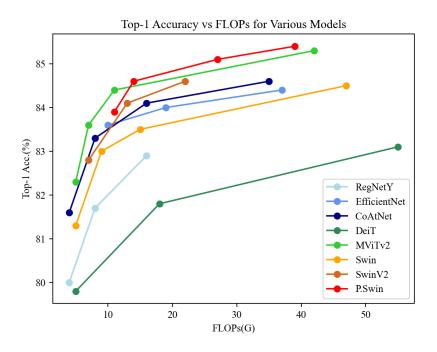

| 4.11 | Top-1 Accuracy vs FLOPs for Various Models                       |

| 4.12 | Object Detection on COCO                                         |

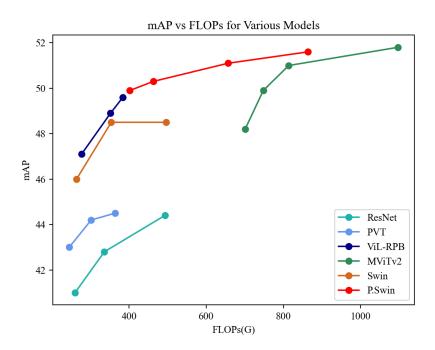

| 4.13 | mAP vs FLOPs for Various Models(Mask R-CNN) 102                  |

## LIST OF FIGURES

| 4.14 | Semantic Segmentation on ADE20K                      |

|------|------------------------------------------------------|

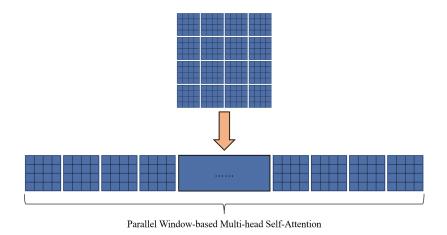

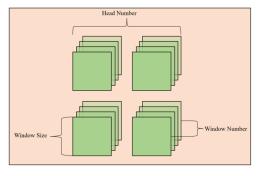

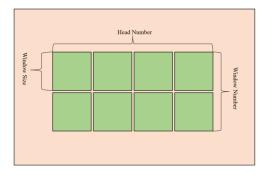

| 4.15 | Parallel Window-based Multi-head Self-Attention 107  |

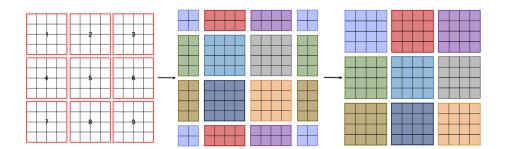

| 4.16 | Parallelization Strategy                             |

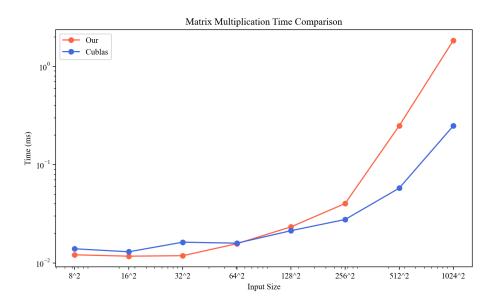

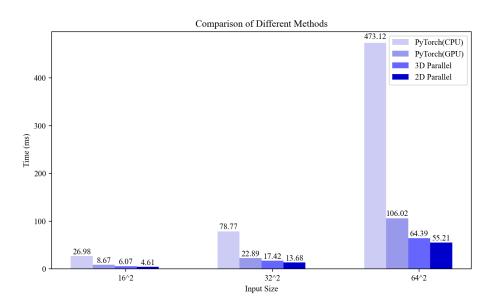

| 4.17 | Comparison of Matrix Multiplication                  |

| 4.18 | Performance comparison with $8 \times 8$ window size |

# List of Tables

| 3.1 | Test Environment                                         | 57  |

|-----|----------------------------------------------------------|-----|

| 3.2 | The mAP comparison of our SSD512 with the original       | 59  |

| 3.3 | Execution time Of NMS and sorting(ms)                    | 64  |

| 3.4 | Execution time of Different NMS(ms)                      | 65  |

| 3.5 | Performances of NMS with different batch size(ms)        | 66  |

| 4.1 | Pyramid Swin Transformer Detailed architecture           | 91  |

| 4.2 | Test Environment                                         | 95  |

| 4.3 | Results on Imagenet Image Classification                 | 97  |

| 4.4 | Results on COCO object detection with Mask R-CNN         | 100 |

| 4.5 | Results on COCO object detection with Cascade Mask R-CNN | 101 |

| 4.6 | Results of ADE20K samantic segmentation with UperNet     | 104 |

| 4.7 | Results of Kinetics-400 video recognition                | 105 |

| 4.8 | Test Environment                                         | 112 |

## Chapter 1

## Introduction

#### 1.1 Motivation

The rapid development of computer vision technologies in recent years has brought significant breakthroughs in various fields, including object detection, image classification, semantic segmentation, and video recognition [66, 105, 48]. These advancements have a wide range of applications, such as autonomous vehicles, robotics, surveillance, and medical imaging, among others. However, the growing complexity and computational requirements of state-of-the-art models pose challenges in terms of processing efficiency, energy consumption, and deployment in resource-constrained environments [44].

Graphics Processing Units (GPUs) have emerged as an effective solution to address the computational demands of deep learning models due to their high parallelism capabilities and superior performance in handling matrix operations [100, 20]. The utilization of GPUs for accelerating computer vision tasks has become increasingly important as researchers and practitioners strive to develop more sophisticated models that can deliver better performance while maintaining reasonable computational costs.

The initial motivation for this research arose from the observation that most existing acceleration-related studies primarily focus on deep neural networks, whereas other computationally-intensive operations in object detection frameworks remain largely unexplored. In particular, we noticed that many of these operations are executed on CPUs, leading to potential performance bottlenecks. This also prompted us to investigate the feasibility of leveraging GPUs to accelerate such operations, with the goal of validating the effectiveness of this approach, facilitating the trade-off between speed and accuracy.

Furthermore, our attention has also been paid to Transformer-based models due to their promising results across a range of computer vision tasks and the computational problems it urgently needs to solve, the Swin Transformer model being a notable example. Our preliminary investigation unveiled a latent parallelizable computation aspect within the Swin Transformer model. This discovery opens the possibility of employing GPUs to expedite the training and detection process of Swin Transformer models, which is promising potential to achieve a superior balance between accuracy and speed. However, in the course of our research, we identified several limitations within the Swin Transformer architecture [80]. This first led us to propose improvements, which produced promising results, further intensifying our curiosity in this domain. Then, we turned our attention towards studying GPU-based acceleration techniques for the Swin Transformer. Our primary objective was to leverage the potential parallelism inherent in the window-based multi-head self-attention mechanism, which is a core component of the Swin Transformer. By implementing GPU-based acceleration, we aim to enhance the processing speed of the Swin Transformer, thereby facilitating its deployment in practical applications. In doing so, we anticipate that our research will inspire new directions for further development and optimization of Transformer models in general, thus making contributions to the field of neural network architectures.

In summary, the motivation of this research lies in exploring and developing GPU-based acceleration and optimization techniques that can effectively enhance the performance of state-of-the-art computer vision models. By investigating efficient parallel processing approaches, optimization strategies, and algorithmic adaptations, we aim to bridge the gap between these advanced models and their real-world applicability, while simultaneously pushing the boundaries of current research in the field.

### 1.2 Problem Statement

Despite the remarkable progress in computer vision tasks, several critical issues hinder the real-world deployment and scalability of state-of-the-art models, particularly in the context of object detection and image classification. This research aims to address the following key problems:

1. Computational Complexity: Advanced computer vision models, such as deep neural networks and Transformer-based architectures, require substantial computational resources to process high-dimensional inputs and perform complex operations[48, 124]. This computational

complexity can lead to high latency and limit the applicability of these models in time-sensitive and resource-constrained scenarios.

- 2. Limited GPU Acceleration Techniques: While GPU-based acceleration has proven to be effective for deep learning tasks, the current literature primarily focuses on the acceleration of deep neural networks, with limited exploration of other computationally-intensive operations in object detection frameworks or other task frameworks. Moreover, the application of GPU-based acceleration techniques for Transformer models remains an underexplored area, further limiting the potential of these powerful architectures in real-world scenarios.

- 3. **Performance Bottlenecks:** Many object detection frameworks rely on CPU-based operations for several critical tasks, which can create performance bottlenecks and hamper the overall efficiency of the system[44]. Identifying and addressing these bottlenecks is crucial for enhancing the performance of object detection frameworks and facilitating their deployment in practice.

- 4. Model Limitations and Improvement: Existing Transformer-based architectures, such as the Swin Transformer [80], exhibit certain limitations that can hinder their performance on various computer vision tasks. Identifying these limitations and proposing improvements to the architecture can further enhance the capabilities of these models, potentially leading to better performance and more effective deployment.

To tackle these problems, this research focuses on the development and evaluation of GPU-based acceleration and optimization techniques for computer vision tasks. By exploring efficient parallel processing approaches, optimization strategies, and algorithmic adaptations, we aim to address the aforementioned challenges and contribute to the advancement of computer vision research and applications.

### 1.3 Contribution

In this dissertation, we present a comprehensive study on GPU-based acceleration of computer vision tasks, focusing on object detection and Transformer-based architectures. Our main contributions are as follows:

1. We propose a GPU-accelerated version of the Single Shot MultiBox Detector (SSD) for object detection, which improves the overall processing

speed and efficiency. By adapting the original algorithm for GPU execution, we demonstrate the feasibility and effectiveness of using GPU acceleration for object detection frameworks.

- 2. We identify limitations in the original Swin Transformer architecture and introduce the Pyramid Swin Transformer as an improved solution. These new architectures achieve superior performance across various vision tasks, including object detection, image classification, semantic segmentation, and video recognition.

- 3. We present a novel GPU-accelerated version of the window-based multihead self-attention, leveraging the parallel capabilities of GPUs to improve the processing speed and efficiency of the computation. Our accelerated window-based multi-head self-attention demonstrates better performance than the original version, making it more suitable for real-world applications.

- 4. Through extensive experiments, we validate the effectiveness of our proposed techniques, showing that they consistently outperform state-of-the-art methods in their respective tasks. Our work provides valuable insights into the design of efficient and high-performing computer vision models, paving the way for future research and practical applications.

- 5. We conduct a thorough analysis of the computational bottlenecks in both object detection frameworks and Transformer-based architectures. This analysis helps to identify the key areas that can benefit the most from GPU acceleration, allowing us to focus our optimization efforts and maximize the performance gains. Our findings can serve as a valuable reference for researchers and engineers looking to optimize and accelerate their own computer vision models.

Our research not only contributes to the improvement of existing computer vision models but also offers new insights into the potential of GPU acceleration for a broader range of tasks. We anticipate that our findings will stimulate further exploration in this area and help drive the development of even more efficient and powerful computer vision solutions.

#### 1.4 Thesis Structure

This thesis is organized into five major chapters, providing a detailed overview of the research undertaken on GPU-based acceleration and optimization of computer vision task models.

Chapter 1 sets the foundation for the research, presenting the motivation for exploring GPU-based acceleration and optimization of computer vision models, formulating the problem statement, and enumerating the contributions of this work. It outlines the fundamental challenges and aims that drive the thesis.

Chapter 2 delves into the background necessary to understand the concepts involved in the research. It starts with the basics of computer vision, progressing to machine learning and deep learning-based computer vision. It also provides an introduction to GPU architectures and the CUDA platform which are key components of the solutions proposed in the thesis.

Chapter 3, titled 'Speed-up Single Shot Detector on GPU with CUDA', delves into the optimization and acceleration of the SSD model, a popular choice for object detection tasks due to its balance of speed and accuracy. Given the computation-intensive nature of SSDs, we provide a comprehensive analysis of the challenges associated with performing their computations both effectively and efficiently. In this chapter, we present our innovative approach to accelerating the SSD model using GPU computation. We detail the process of porting the model's components, traditionally computed on the CPU, to the GPU, and customizing them for optimal utilization of GPU resources. Our efforts particularly target the post-processing layer, which includes critical functions such as non-maximum suppression (NMS) and sorting. By skillfully migrating these functions to the GPU, we are able to significantly reduce the execution time. Our GPU-accelerated SSD model showcases superior detection speed without major sacrifices in object detection accuracy, achieving a superior trade-off between detection speed and model accuracy. This speed enhancement is accomplished by effectively leveraging the GPU's vast parallel processing capabilities and optimized memory management. The results of our research underscore the significant potential and feasibility of using GPUs to accelerate object detection frameworks, paving the way for future advancements in this field.

Chapter 4, titled 'Optimization for the Swin Transformer', we shift our focus to Transformer-based models, specifically Swin Transformer. We provide a comprehensive review of related work including Feature Pyramid Network, Vision Transformer, and Swin Transformer, leading to finding the problem in Swin Transformer architecture and to our proposed methods and adaptations. And we improve the shortcomings of Swin Transformer architecture, presenting the Pyramid Swin Transformer which is based on Swin Transformer. The results and effectiveness of our model across various tasks like image classification, object detection, semantic segmentation, and video recognition are reported. Our novel framework performs better than Swin Transformer and achieves superior accuracy and computational complexity

trade-offs. We also cover our research on High-speed window-based multihead self-attention which is the foundational operation of Swin Transformer. After examining the efficient attention mechanisms and matrix multiplication acceleration techniques from existing research, we detail our proposed methods for efficient matrix multiplication and parallelization strategies using GPU. We further implemented and evaluated this approach, and our findings indicate that leveraging GPU acceleration for window-based multihead self-attention is a viable and effective strategy.

The final chapter, Chapter 5, encapsulates the conclusion of our research and suggests potential future work. It revisits the main findings from the previous chapters and proposes several directions for extending this research further. It marks the end of the main body of the thesis. This structured layout of the thesis will guide readers through the intricate journey of this research, from understanding the basic concepts to appreciating the depth and significance of GPU acceleration in computer vision task models.

# Chapter 2

# Background

## 2.1 Computer Vision

Computer vision is a field of study that focuses on enabling computers to understand and interpret visual information from the surrounding world, such as images and videos. The goal is to teach machines to process and analyze visual data in a way that is similar to how humans perceive their environment. Computer vision has a wide range of applications, including object recognition, image and video analysis, augmented reality, and autonomous driving.

## 2.1.1 Basic Computer Vision

Early computer vision techniques primarily relied on handcrafted features and simple image processing and analysis algorithms. These methods can be categorized into several key areas:

- Edge detection: This involves identifying the boundaries between different regions in an image, often based on changes in intensity or color. Popular edge detection techniques include the Sobel operator, which computes the gradient of the image intensity at each pixel using two 3x3 convolutional masks [116]; the Canny edge detector, which combines non-maximum suppression and hysteresis thresholding to find true edges [16]; and the Laplacian of Gaussian (LoG) operator, which combines Gaussian smoothing and the Laplacian operator to detect both strong and weak edges [86].

- Image segmentation: This is the process of partitioning an image into multiple regions, typically based on similarities in pixel values

or other properties. Common image segmentation techniques include thresholding, where pixels are classified based on their intensity values; region growing, which iteratively merges neighboring pixels with similar properties; and watershed segmentation, which treats image gradients as topographic relief and finds watershed lines separating adjacent regions [45].

• Feature extraction: These methods aim to extract meaningful information from images, such as corners, key points, and descriptors. Some well-known feature extraction techniques are Scale-Invariant Feature Transform (SIFT), which identifies and describes local features in images that are invariant to scale, rotation, and illumination changes [83]; Speeded Up Robust Features (SURF), an improved and faster version of SIFT that uses integral images and Haar-like wavelets for feature detection and description [6]; and Histogram of Oriented Gradients (HOG), which captures the distribution of gradient directions in an image to describe object shapes [28].

Although these approaches were effective for some specific problems, they generally lacked robustness and scalability, as they relied on manual feature engineering and could not adapt to new or more complex tasks.

## 2.1.2 Machine Learning-based Computer Vision

Machine learning-based computer vision methods focus on developing algorithms that can learn to recognize patterns and make decisions based on data without explicit programming. These methods rely on training models using large sets of labeled data, extracting features from images, and making predictions based on the learned patterns. Some of the key machine learning techniques that have been employed in computer vision tasks include:

• Support vector machines (SVMs): SVMs are a widely-used supervised learning method for classification and regression tasks. In computer vision, SVMs have been extensively applied for image classification and object recognition tasks, often combined with hand-crafted features like Histogram of Oriented Gradients (HOG) [28] or Scale-Invariant Feature Transform (SIFT) [83]. SVMs aim to find the optimal decision boundary (i.e., the hyperplane in the high-dimensional feature space) that separates different classes, maximizing the margin between the classes. Despite their effectiveness in many computer vision tasks, SVMs can struggle with large-scale, high-dimensional data and may require complex feature engineering.

- k-Nearest Neighbors (k-NN): The k-NN algorithm [65] is a simple and intuitive method for classification and regression tasks based on the concept of similarity between instances. In the context of computer vision, k-NN has been used for image classification, object recognition, and image retrieval. Given a query image, the k-NN algorithm finds the k most similar images in the training set (based on a chosen distance metric) and assigns the query image to the majority class of its neighbors. Although k-NN is easy to implement and understand, it may suffer from high computational complexity and storage requirements, particularly when dealing with large image datasets.

- Boosting algorithms: Boosting is a family of ensemble learning methods that combine the predictions of multiple weak classifiers to improve classification accuracy. AdaBoost (Adaptive Boosting) [39] is one of the most popular boosting algorithms and has been applied to various computer vision tasks, such as face detection [125] and object recognition. Boosting algorithms can be highly effective for object detection tasks, as they can achieve high detection rates with relatively low computational complexity. However, they may be sensitive to noisy data and may require careful tuning of hyperparameters.

- Random forests: Random forests[13] are ensemble learning methods that construct multiple decision trees and combine their predictions through averaging or majority voting. They have been used in various computer vision tasks, such as image classification[38], object detection, and semantic segmentation[114, 25]. Random forests can efficiently handle large datasets, provide robust and accurate predictions, and offer a degree of interpretability through the decision tree structure, provide robust and accurate predictions, and offer a degree of interpretability through the decision tree structure. However, they may struggle with high-dimensional data and may not be as effective as deep learning methods for certain tasks.

- Graph-based methods: Graphs provide a flexible and powerful representation for modeling complex relationships between image elements, such as pixels, regions, or objects. Graph-based methods have been widely used in computer vision for tasks like image segmentation, where the image is modeled as a graph with nodes representing pixels and edges representing spatial or feature-based similarities [37, 12]. Graph-cut algorithms can then be applied to partition the graph into disjoint regions corresponding to different image segments. For example, max-flow/min-cut can be used to find the cut with the minimum sum of edge

weights that divides the graph into disjoint sub-graphs. Other graph-based techniques, like Markov random fields and conditional random fields, have also been employed for various computer vision tasks, including object recognition, image restoration, and semantic segmentation [67, 106]. Graph-based methods can effectively model the relationships between image elements and incorporate domain-specific knowledge. However, they may suffer from high computational complexity, especially when dealing with large images or complex graphs.

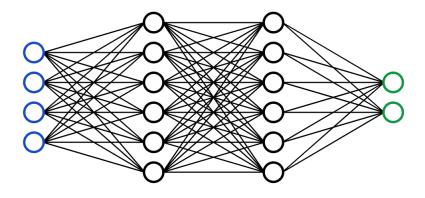

• Neural networks: Before the advent of deep learning, shallow neural networks, like the one illustrated in Figure 2.1, were widely used for computer vision tasks[136]. These networks typically consisted of an input layer, one or two hidden layers, and an output layer. The input layer receives raw pixel data from the images, and each neuron in the hidden layer applies a non-linear transformation to the input data, allowing the network to learn complex patterns. This transformation can be represented as:

$$h_i = \sigma(\sum_j w_{ij} x_j + b_i) \tag{2.1}$$

where  $h_i$  is the output of the *i*th neuron in the hidden layer,  $x_j$  is the *j*th input,  $w_{ij}$  is the weight connecting the *i*th neuron to the *j*th input,  $b_i$  is the bias term for the *i*th neuron, and  $\sigma$  is the activation function [43].

The final output layer uses the transformed inputs from the last hidden layer to generate predictions, often through a softmax function for classification tasks, which can be represented as:

$$y_k = \frac{e^{z_k}}{\sum_j e^{z_j}} \tag{2.2}$$

where  $y_k$  is the output of the kth neuron in the output layer, and  $z_k$  is the input to the kth neuron [9].

Some popular shallow neural network architectures include the multilayer perceptron (MLP) and the radial basis function (RBF) network [9]. The MLP is fully connected, meaning each neuron in a layer is connected to all neurons in the previous and next layers. The RBF network, on the other hand, typically has a single hidden layer and uses radial basis functions as activation functions, which can provide a measure of similarity to a set of exemplars. Shallow neural networks have been applied to tasks such as handwritten digit recognition and face recognition [71]. Despite the success of these early neural network models in some computer vision tasks, they were limited by the lack of depth and the inability to learn hierarchical feature representations, which is a key strength of modern deep learning models. These limitations were addressed by the introduction of deep learning and convolutional neural networks, which we will discuss in the next section.

Figure 2.1: Architecture of a Neural Network

Machine learning-based computer vision techniques have played a significant role in the development of the field, paving the way for the rise of deep learning-based methods. These methods have addressed various challenges, including image classification, object detection, and segmentation, by learning from large labeled datasets and capturing meaningful patterns in the data [66]. However, many of these methods require hand-crafted features or carefully engineered representations, and they may struggle with large-scale, high-dimensional data. The advent of deep learning and convolutional neural networks has largely addressed these limitations, leading to breakthroughs in computer vision performance and enabling the development of more sophisticated models that can learn hierarchical feature representations directly from the raw data [43].

### 2.1.3 Deep Learning-based Computer Vision

Deep learning-based computer vision techniques have significantly advanced the field in recent years. Deep learning models, particularly convolutional

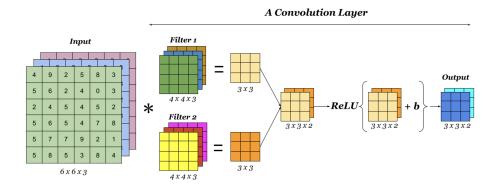

Figure 2.2: A CNN architecture

neural networks (CNNs), have demonstrated remarkable performance in various computer vision tasks, such as image classification [66, 115, 48], object detection [42, 105], semantic segmentation [82, 5], and video recognition [59, 123]. These advancements have led to widespread adoption and continued research in the field, driving the development of even more powerful and efficient computer vision models.

#### Convolutional Neural Networks

Convolutional Neural Networks (CNNs) are a class of deep learning models specifically designed for computer vision tasks[72]. The core concept of a CNN is the convolution operation, which allows the model to learn spatial hierarchies of features by applying a series of filters (also called kernels) to the input image.

The convolution operation is defined as:

$$(I * K)(i,j) = \sum_{m} \sum_{n} I(m,n)K(i-m,j-n),$$

(2.3)

In this formula, I is the input image and K is the kernel. (i,j) are the coordinates of a pixel in the image, and (m,n) are the coordinates of a pixel in the kernel. The operation computes the dot product of the kernel with each region of the input image, producing a new image where each pixel value represents the strength of the detected feature at the corresponding location in the input image.

An essential aspect of CNNs is their architecture, which typically consists of alternating convolutional layers and pooling layers, followed by one or more fully connected layers. The convolutional layers perform the feature extraction, while pooling layers (such as max pooling or average pooling) reduce the spatial dimensions of the feature maps, and fully connected layers combine the learned features for the final classification or regression tasks. Activation functions, such as Rectified Linear Units (ReLU) [88], are applied after each convolutional or fully connected layer to introduce nonlinearity into the model.

CNNs are typically trained using backpropagation [107], which is an algorithm for minimizing the loss function by updating the model's parameters based on the gradient of the loss function with respect to each parameter. The gradient of the loss function is computed using the chain rule of calculus, which allows the gradient to be propagated backward through the layers of the network. The model's parameters are then updated using an optimization algorithm, such as stochastic gradient descent (SGD) [11], Adam [61]. The objective is to minimize the loss function, which measures the difference between the model's predictions and the ground-truth labels. Commonly used loss functions for classification tasks include the cross-entropy loss, while for regression tasks, the mean squared error loss is often used.

To prevent overfitting, various regularization techniques are employed, such as weight decay, dropout, and data augmentation. Weight decay adds a penalty term to the loss function, proportional to the squared norm of the model's weights. This encourages the model to learn simpler functions with smaller weights. Dropout is a technique where, during training, a fraction of the neurons in a layer are randomly "dropped" or deactivated, forcing the model to rely on a diverse set of features for its predictions. Data augmentation involves creating new training samples by applying random transformations, such as rotations, translations, and flips, to the original images. This increases the size of the training dataset and encourages the model to learn more robust features.

CNNs have been proven to be highly effective for various computer vision tasks, and their success can be attributed to their ability to learn hierarchical feature representations directly from raw data, their invariance to translations and other transformations [70], and their efficient use of parameters through weight sharing and pooling operations [115]. The development of advanced CNN architectures, such as VGGNet [115], Inception [120], ResNet [48], DenseNet [55], and MobileNet [53], has further pushed the boundaries of what is possible with deep learning-based computer vision approaches.

In summary, Convolutional Neural Networks have revolutionized the field of computer vision, providing state-of-the-art performance in a wide range of tasks. Their mathematical foundations, including convolution and pooling operations, as well as their efficient and robust learning capabilities, make them a powerful tool for processing and analyzing visual data.

#### Convolutional Layers

The input data is convolved in convolutional layers with a set of learnable filters (or kernels). The output of this operation, known as the feature map, is computed by sliding each filter across the input data and taking the dot product between the filter and the input data at each location.

Activation Functions Activation functions play a crucial role in deep learning architectures by introducing non-linearity into the model, enabling it to learn complex patterns and relationships among input features. These functions are applied element-wise to the neurons' outputs in a layer, transforming the weighted sum of inputs before passing it to the next layer. Several activation functions have been proposed and widely used in the literature, each with its own advantages and drawbacks. We will discuss some of the most popular activation functions below.

• **Sigmoid function:** The sigmoid function, also known as the logistic function, is one of the earliest activation functions used in neural networks. It is defined as:

$$f(x) = \frac{1}{1 + e^{-x}},\tag{2.4}$$

which maps the input value x to the range (0,1). The sigmoid function is smooth and differentiable, making it suitable for gradient-based optimization methods. However, it suffers from the vanishing gradient problem, where the gradients become too small during backpropagation, leading to slow convergence or training stagnation [50].

• Tanh function: The hyperbolic tangent (tanh) function is another widely-used activation function, defined as:

$$f(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}},\tag{2.5}$$

which maps the input value x to the range (-1,1). Similar to the sigmoid function, the tanh function is smooth and differentiable, but it also suffers from the vanishing gradient problem [50].

• Rectified Linear Unit (ReLU): Introduced by Nair and Hinton [88], the ReLU function is currently one of the most popular activation functions in deep learning. It is defined as:

$$f(x) = \max(0, x),\tag{2.6}$$

which maps the input value x to the range  $[0, \infty)$ . ReLU is computationally efficient and mitigates the vanishing gradient problem, enabling the training of deeper networks. However, it can cause some neurons to become inactive during training, a phenomenon known as the "dying ReLU" problem, which may hinder the model's learning capacity.

• Leaky ReLU: To address the dying ReLU issue, Maas et al. [84] proposed the Leaky ReLU function, defined as:

$$f(x) = \max(\alpha x, x), \tag{2.7}$$

where  $\alpha$  is a small positive constant (e.g., 0.01). Leaky ReLU allows small negative values, ensuring that neurons remain active during training and mitigating the dying ReLU problem. The dying ReLU problem refers to the phenomenon where some neurons become permanently inactive and only output 0. This can happen if a large gradient flows through a ReLU neuron, causing a large update to its weights. If the updated weights cause the weighted sum of inputs to that neuron to be negative, then the neuron will output 0. If this happens, then in subsequent iterations, the neuron will still output 0, no matter what values the input takes on.

• Exponential Linear Unit (ELU): Clevert et al. [21] introduced the ELU function to improve the ReLU's performance, defined as:

$$f(x) = \begin{cases} x, & \text{if } x > 0\\ \alpha(e^x - 1), & \text{otherwise} \end{cases}$$

(2.8)

where  $\alpha$  is a positive constant. ELU retains the advantages of ReLU, such as mitigating the vanishing gradient problem, and it allows negative outputs, ensuring that neurons remain active during training. ELU also has a smooth derivative for negative inputs, which can help with gradient-based optimization.

• Swish: Ramachandran et al. [101] proposed the Swish activation function, which is defined as:

$$f(x) = x \cdot \sigma(\beta x),\tag{2.9}$$

where  $\sigma$  is the sigmoid function, and  $\beta$  is a learnable parameter or a fixed constant. Swish is smooth, differentiable, and allows both positive and negative outputs. It has been shown to perform better than ReLU in some deep learning tasks [101].

Activation functions are essential components in neural networks, allowing them to learn complex, non-linear relationships among input features. The choice of activation function depends on the problem, architecture, and specific requirements of the task. Researchers are continually exploring new activation functions to improve the performance, stability, and convergence of deep learning models.

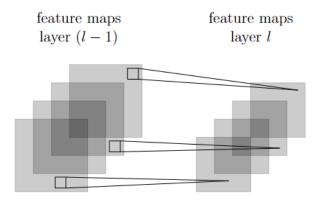

**Pooling Layer** The pooling operation is another key component of convolutional neural networks (CNNs). It is used to reduce the spatial dimensions of the feature maps while retaining the most important information. This operation helps to make the network invariant to small translations and reduces the computational complexity of subsequent layers [43].

The two most common types of pooling are max pooling and average pooling. Max pooling selects the maximum value within a specified window, while average pooling computes the average value within the window. The pooling operation can be defined as:

$$P(i,j) = \max_{m \in W_i, n \in W_j} I(m,n),$$

(2.10)

for max pooling, and

$$P(i,j) = \frac{1}{|W_i||W_j|} \sum_{m \in W_i, n \in W_j} I(m,n), \tag{2.11}$$

for average pooling, where I is the input feature map, P is the output pooled feature map, and  $W_i$  and  $W_j$  represent the pooling window dimensions.

It's worth noting that the pooling operation is applied independently to each input channel, and it does not change the number of channels [43]. This can be represented as:

$$P_c(i,j) = \max_{m \in W_i, n \in W_i} I_c(m,n),$$

(2.12)

for each channel c in the input feature map, where  $I_c$  is the cth channel of the input feature map, and  $P_c$  is the cth channel of the output pooled feature map.

Figure 2.3: Illustration of a pooling operation

Fully Connected Layers Fully connected layers, also known as dense layers, are a fundamental component of various deep learning architectures. In these layers, each neuron is connected to every neuron in the previous layer, forming a complete bipartite graph between the two layers. The fully connected layer's primary function is to learn the final feature representations and perform high-level reasoning based on the features extracted by preceding layers, such as convolutional layers in the case of CNNs.

Given layer l as a fully connected layer, the output of the  $i^{\rm th}$  neuron in layer l can be computed as:

$$y_i^{(l)} = f\left(z_i^{(l)}\right),\tag{2.13}$$

where  $f(\cdot)$  represents the activation function and  $z_i^{(l)}$  is the weighted sum of the input neurons connected to the  $i^{\text{th}}$  neuron in layer l. The weighted sum can be calculated as:

$$z_i^{(l)} = \sum_{j=1}^{m_1^{(l-1)}} w_{i,j}^{(l)} x_j^{(l-1)} + b_i^{(l)}, \qquad (2.14)$$

where  $m_1^{(l-1)}$  is the number of neurons in layer (l-1),  $w_{i,j}^{(l)}$  denotes the weight connecting the  $j^{\text{th}}$  neuron in layer (l-1) to the  $i^{\text{th}}$  neuron in layer l,  $x_j^{(l-1)}$  represents the output of the  $j^{\text{th}}$  neuron in layer (l-1), and  $b_i^{(l)}$  is the bias term for the  $i^{\text{th}}$  neuron in layer l.

Fully connected layers are often employed in the final stages of a deep learning model to combine the features extracted by previous layers and generate the final output, such as class probabilities in classification tasks or continuous values in regression tasks. It is worth noting that a fully connected layer intrinsically includes non-linearities through the activation function  $f(\cdot)$ , enabling the learning of complex patterns and relationships among the input features.

#### Normalization

Normalization techniques play a crucial role in deep learning models, including the Swin Transformer, by ensuring stable and efficient training. In this section, we will discuss the normalization methods used in the Swin Transformer and their underlying mathematical principles.

The two primary normalization techniques used in the Swin Transformer are Layer Normalization (LN) [4] and Batch Normalization (BN) [57]. While both methods aim to stabilize training by normalizing the input data, they differ in terms of the dimensions across which they compute the normalization statistics.

• Layer Normalization: Layer normalization (LN) is a normalization technique that is performed across each individual input or hidden layer of a neural network. Specifically, the mean and variance for normalization are computed across each single input data point, instead of computing across different input data points in the batch (as in batch normalization). For a given layer input  $x = [x_1, x_2, ..., x_m]$ , layer normalization computes the mean  $\mu$  and variance  $\sigma^2$  as follows:

$$\mu = \frac{1}{m} \sum_{i=1}^{m} x_i \quad \text{(mean of the inputs)} \tag{2.15}$$

$$\sigma^2 = \frac{1}{m} \sum_{i=1}^{m} (x_i - \mu)^2 \quad \text{(variance of the inputs)}$$

(2.16)

After which, layer normalization applies the following transformation:

$$y = \frac{x - \mu}{\sqrt{\sigma^2 + \epsilon}} * \gamma + \beta \tag{2.17}$$

Here, x is the original input,  $\mu$  and  $\sigma$  are the mean and standard deviation of the inputs,  $\gamma$  and  $\beta$  are learnable scale and shift parameters,  $\epsilon$  is a small constant added for numerical stability, and y is the normalized output.

This type of normalization is particularly useful for models that need to maintain a consistent hidden state across each layer, as it doesn't normalize across the batch dimension.

• Batch Normalization: Batch normalization (BN) is a normalization technique that normalizes across batches of inputs, rather than across layers. For a given mini-batch  $B = \{x_1, x_2, ..., x_m\}$  of size m, batch normalization computes the mean  $\mu_B$  and variance  $\sigma_B^2$  as follows:

$$\mu_B = \frac{1}{m} \sum_{i=1}^{m} x_i \quad \text{(mean of the batch)} \tag{2.18}$$

$$\sigma_B^2 = \frac{1}{m} \sum_{i=1}^m (x_i - \mu_B)^2 \quad \text{(variance of the batch)}$$

(2.19)

And then normalizes each input in the mini-batch with:

$$y = \frac{x - \mu_B}{\sqrt{\sigma_B^2 + \epsilon}} * \gamma + \beta \tag{2.20}$$

In this formula, x is the original input,  $\mu_B$  and  $\sigma_B$  are the mean and standard deviation of the batch,  $\gamma$  and  $\beta$  are learnable scale and shift parameters,  $\epsilon$  is a small constant added for numerical stability, and y is the normalized output.

The primary difference between BN and LN lies in the dimensions over which they compute the mean and variance. While batch normalization computes it over the batch dimension, layer normalization computes it over the feature dimension. This makes batch normalization dependent on the batch size and requires a large batch size to work effectively. In contrast, layer normalization works independently of batch size, making it more suitable for tasks where batch size might vary.

#### CNN Architectures

Over the years, numerous CNN architectures have been proposed, each improving upon its predecessors and pushing the limits of deep learning-based computer vision. In this section, we will review some of the most popular and influential CNN architectures.

- AlexNet: AlexNet [66], developed by Krizhevsky et al., was a major breakthrough in the field, achieving state-of-the-art performance in the ImageNet Large Scale Visual Recognition Challenge (ILSVRC) in 2012. AlexNet consists of five convolutional layers, followed by three fully connected layers and an output layer for classification. It introduced the use of ReLU activation functions and dropout layers to improve the training process and prevent overfitting.

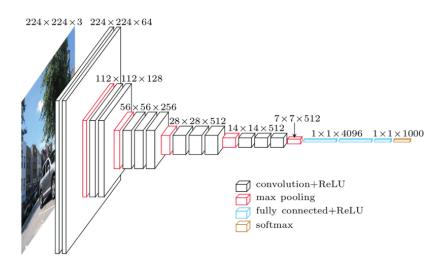

- VGGNet: VGGNet, proposed by Simonyan and Zisserman [115], as shown in figure 2.4, is a significant milestone in the field of deep learning due to its simplicity, depth, and performance. VGGNet is characterized by its homogeneity and depth. It uniformly uses small (3x3) convolutional filters throughout the entire network, which was a shift from the previous architectures that typically used larger filters (e.g., 5x5 or 7x7) in the first convolutional layers. VGGNet demonstrated the importance of depth in neural networks for achieving high performance in computer vision tasks. Its architecture comprises several layers, with the main variants being VGG-16 and VGG-19, which consist of 16 and 19 layers, respectively. The depth of the network allowed it to learn more complex and abstract features, which contributed to its impressive performance. The network's layers follow a simple pattern: convolutional layers with small filters followed by max-pooling layers, with this sequence repeated multiple times to form the whole network. This simplicity and consistency make VGGNet easy to understand, implement, and modify, which has contributed to its wide adoption in the research community. Despite its higher computational cost and larger model size compared to other models like AlexNet or GoogLeNet, VGGNet has been widely adopted in various applications due to its excellent performance and simplicity. Its learned features have been shown to generalize well to other tasks and datasets, and its architecture has served as a foundation or a point of comparison for many subsequent models. Furthermore, the concept of using smaller filters in deeper networks, introduced by VGGNet, has been influential in the design of more recent architectures.

- Inception (GoogLeNet): The Inception architecture, also known as GoogLeNet [120], was developed by Szegedy et al. at Google. Inception introduced the concept of "inception modules," which consist of parallel convolutional layers with different filter sizes, followed by a concatenation of their outputs. This design enables the network to capture features at multiple scales. Inception also uses auxiliary classifiers

Figure 2.4: VGG Net [115]

during training to alleviate the vanishing gradient problem in deeper layers.

• ResNet: Residual Networks (ResNet), developed by Kaiming He et al., revolutionized the field of deep learning by introducing the concept of "residual connections" or "skip connections" [48]. In a traditional deep neural network, each layer learns a new representation of the data, and this new representation is passed on to the next layer. However, this approach becomes less effective as the network depth increases due to the problem of vanishing gradients. During backpropagation, the gradients often get smaller and smaller as they reach the initial layers, leading to slower convergence or the model not learning effectively. To solve this problem, ResNet introduced the idea of "shortcut connections" that allow the gradients to propagate directly through several layers by skipping intermediate layers. These shortcut connections perform identity mapping, and their outputs are added to the outputs of the stacked layers. This allows the stacked layers to fit a residual mapping instead of the original mapping, hence the name Residual Network. This innovative design made it feasible to train very deep networks (e.g., up to 152 layers), which was difficult with previous architectures. ResNet achieved state-of-the-art performance in the ImageNet Large Scale Visual Recognition Challenge (ILSVRC) 2015 competition, significantly reducing the error rate compared to previous models. It has since become a popular choice for many computer vision tasks, such as object detection, segmentation, and face recognition, due to its superior performance and the generalization capability of the learned features. The principles behind ResNet have also influenced the design of subsequent deep learning architectures, making it a milestone in the development of deep learning models.

Figure 2.5: Residual Block[136]

- DenseNet: Dense Convolutional Networks (DenseNet) [55], proposed by Huang et al., extend the idea of skip connections by connecting each layer to every other layer in a feed-forward fashion. This design results in the efficient use of parameters and improved gradient flow. DenseNet has been shown to achieve high performance with fewer parameters compared to other architectures.

- MobileNet: MobileNet [53], developed by Howard et al., is designed for mobile and embedded vision applications, prioritizing efficiency and low computational cost. MobileNet introduces depthwise separable convolutions, which factorize standard convolutions into depthwise convolutions and pointwise convolutions, reducing the number of operations and parameters. MobileNet has multiple versions with varying trade-offs between performance and computational cost.

These popular CNN architectures have made significant contributions to the field of computer vision and have been widely adopted in various applications, ranging from image classification and object detection to semantic segmentation and image generation.

- Capsule Networks: Capsule Networks (CapsNets) [110], introduced by Sabour et al., is a novel architecture designed to address the limitations of traditional CNNs, particularly in regard to preserving spatial relationships between features. CapsNets replace scalar feature activations with vector-valued "capsules" that represent the presence and properties of entities in the input image. CapsNets have shown promise in tasks requiring the preservation of spatial hierarchies and pose estimation.

- EfficientNet: EfficientNet [121], proposed by Tan and Le, is an architecture that focuses on balancing model efficiency and accuracy by using a compound scaling method. The authors found that scaling up the width, depth, and resolution of the network simultaneously results in more efficient use of resources. EfficientNet has several variants (B0 to B7) with different capacities, achieving state-of-the-art performance while maintaining efficiency in terms of the number of parameters and computational cost.

The aforementioned CNN architectures have significantly influenced the field of computer vision, with wide applications in image classification, object detection, semantic segmentation, and image generation, among others. As advancements in CNN architectures continue to emerge and push the boundaries of what's possible in deep learning-based computer vision, researchers and practitioners alike are persistently exploring new techniques to improve these models' efficiency, robustness, and performance. These ongoing developments enable novel applications and the solving of increasingly complex problems within the realm of computer vision.

### 2.2 GPU

Graphics Processing Units (GPUs) have become an essential component in accelerating computer vision and deep learning applications due to their highly parallel architecture and superior computational capabilities compared to traditional Central Processing Units (CPUs). The following sections will provide a more detailed overview of GPU architectures, their components, and how they differ from CPUs.

#### 2.2.1 GPU Architectures

A GPU is a specialized hardware designed to accelerate rendering tasks in graphics applications. However, their highly parallel architecture and pow-

erful computational capabilities make them well-suited for general-purpose parallel computing, including computer vision and deep learning tasks. GPUs are composed of thousands of smaller cores that can execute many threads simultaneously, making them ideal for data-parallel tasks. Unlike CPUs,

Figure 2.6: NVIDIA A100 GPU architecture

which typically have a small number of cores optimized for single-threaded performance and complex control flow, GPUs have a massive number of simpler cores designed for parallelism and throughput-oriented tasks. This architectural difference makes GPUs more suitable for processing large-scale, high-dimensional data common in computer vision and deep learning applications.

NVIDIA is one of the leading manufacturers of GPUs, and their GeForce, Quadro, and Tesla product lines are widely used in research and industry. NVIDIA GPUs are based on several architectures, such as Fermi, Kepler, Maxwell, Pascal, Volta, Turing, and Ampere [93]. Each successive architecture has introduced improvements in performance, energy efficiency, and programmability.

As illustrated in Figure 2.6, a typical GPU architecture consists of several streaming multiprocessors (SMs), each containing multiple CUDA cores (also called streaming processors, or SPs) for arithmetic operations, special function units (SFUs) for complex mathematical functions, and load/store units (LD/ST) for memory access.

GPUs have different types of memory, each with varying access speeds and capacities:

Figure 2.7: GPU Architecture Unit[119]

- Global memory is the largest memory type on a GPU and is accessible by all threads and the host (CPU). It is also known as device memory and is allocated off-chip, which makes it slower compared to other memory types. However, global memory provides high bandwidth and large capacity, making it suitable for storing large data sets.

- Shared memory is a smaller, faster memory type that is shared among the threads within a thread block. It is allocated on-chip, providing low-latency access for threads. Shared memory is used for interthread communication and to cache frequently accessed data, reducing the need for slower global memory accesses.

- Constant memory is a read-only memory type that can be cached for faster access. It is used for storing constant values, such as model parameters or lookup tables, which remain unchanged throughout the execution of a kernel. Constant memory is also allocated off-chip but can be cached on-chip for improved access speed.

- Local memory is a private memory space for each thread, used for storing local variables and temporary values that do not fit into the

thread's registers. Local memory is allocated off-chip and has similar access times as global memory.

• Texture memory and surface memory are specialized memory types for handling 2D and 3D data, such as images and volumes. These memory types offer specific hardware features, such as filtering and boundary handling, which can be useful in computer vision applications. Texture and surface memory are also cached for faster access.

Understanding the characteristics and usage of these different memory types is crucial for optimizing GPU performance in computer vision and deep learning applications. Efficient memory management and access patterns can significantly improve the execution speed and reduce the memory footprint of GPU-accelerated algorithms.

In addition to memory types, other architectural components also play a significant role in GPU performance. For instance, the number of registers per thread, the number of threads per block, and the occupancy of streaming multiprocessors (SMs) can influence the overall throughput and efficiency of a GPU-accelerated application. Balancing these factors to utilize the available hardware resources fully is a key aspect of optimizing GPU-based algorithms[119].

Another important difference between GPUs and CPUs is their approach to instruction execution. While CPUs typically employ complex out-of-order execution and branch prediction mechanisms to optimize single-threaded performance, GPUs use a simpler in-order execution model called Single Instruction Multiple Threads (SIMT). In SIMT, groups of threads, called warps, execute the same instruction simultaneously, which simplifies the control logic and allows for greater parallelism. However, this also means that divergent control flow within a warp can lead to performance degradation, as different execution paths must be serialized.

In summary, GPUs have revolutionized the field of computer vision and deep learning by providing a highly parallel architecture and powerful computational capabilities. Their numerous simpler cores, specialized memory types, and throughput-oriented design make them more suitable for processing large-scale, high-dimensional data than traditional CPUs. Understanding the architectural differences between GPUs and CPUs, as well as the intricacies of GPU memory management and execution models, is essential for developing high-performance computer vision and deep learning applications.

#### 2.2.2 CUDA Platform

The CUDA (Compute Unified Device Architecture) platform, developed by NVIDIA[23], is a parallel computing platform and programming model that allows developers to harness the power of NVIDIA GPUs for general-purpose computing tasks [90]. CUDA has had a significant impact on various fields, including scientific computing, machine learning, and computer vision, by enabling researchers and engineers to leverage GPU acceleration for their applications [94, 66].

CUDA provides a C/C++ programming interface, along with libraries and tools, for writing parallel algorithms that can be executed on the GPU [23]. The CUDA programming model is based on the concept of threads, blocks, and grids. Threads are the smallest execution units and are grouped into blocks, which are further organized into a grid [90]. Each thread in a block can access a shared memory space, enabling efficient communication and data sharing between threads within the same block. The grid is a higher-level abstraction that represents the entire problem domain and is divided into blocks.

In the CUDA programming model, the GPU is treated as a highly parallel co-processor that works in conjunction with the CPU [90]. The CPU, referred to as the host, is responsible for executing the main program, managing memory transfers between the host and the device (GPU), and launching kernels on the device. Kernels are functions that are executed on the GPU by a large number of threads in parallel [90].

The CUDA platform exposes the GPU's hierarchical memory architecture, which includes global memory, shared memory, constant memory, and texture memory [23]. Global memory is the largest and slowest memory space, accessible by all threads in the grid, and can be used to store large data structures. Shared memory, which is faster than global memory, is shared among threads within the same block and can be used for inter-thread communication and data sharing [90]. Constant memory is a read-only memory space that can be used to store constant data used by all threads, while texture memory is a cached memory space optimized for 2D and 3D data access patterns [23].

To optimize the performance of CUDA applications, developers need to carefully manage the memory hierarchy and thread execution [109]. For example, they should minimize global memory access, use shared memory and constant memory to reduce memory latency, and design the kernel to maximize thread-level parallelism and occupancy [126].

CUDA provides a rich set of libraries, such as cuBLAS, and cuDNN [20], which offer GPU-accelerated implementations of commonly used functions in

linear algebra, signal processing, sparse matrix operations, and deep learning. These libraries allow developers to easily integrate GPU acceleration into their applications without having to write custom GPU kernels [94].

The CUDA platform also includes various tools for profiling and debugging, such as the NVIDIA Visual Profiler [91]. These tools enable developers to analyze the performance of their GPU-accelerated applications, identify bottlenecks, and debug their code. They can also help in optimizing memory usage, identifying performance-limiting factors, and ensuring the correctness of the code [23].

To sum up, the CUDA platform has played a crucial role in democratizing GPU computing and has made it accessible to a broad range of developers and researchers. Its programming model, rich set of libraries, and development tools have enabled the rapid development and deployment of GPU-accelerated applications in various fields, including computer vision, deep learning, and scientific computing [94, 66, 23]. By leveraging the powerful capabilities of NVIDIA GPUs, the CUDA platform has significantly contributed to the advancement of these fields and has set the stage for further breakthroughs and innovations.

#### **cuBLAS**

NVIDIA's cuBLAS [91] is a GPU-accelerated library that provides implementations for a wide range of Basic Linear Algebra Subprograms (BLAS). It is an essential component in the matrix multiplication operation, a core computation in deep learning models. By leveraging the vast parallel computing capability inherent to GPU architectures, cuBLAS offers highly optimized routines that significantly enhance the performance of matrix multiplication. The strength of cuBLAS lies in its meticulous design to exploit the capabilities of NVIDIA GPUs. The library includes different versions of matrix multiplication routines tailored for various scenarios, such as small or large matrices, dense or sparse matrices, single or double-precision computations, and more. These routines are highly parameterizable, offering flexibility in how they're used based on the specific requirements of the operation at hand.

The influence of cuBLAS extends to major deep learning frameworks such as TensorFlow and PyTorch, both of which utilize cuBLAS as their backend for executing matrix multiplication operations on NVIDIA GPUs. By doing so, these frameworks can deliver high-performance computation, leading to faster training and inference times for deep learning models. The extensive use of cuBLAS in these frameworks underscores its effectiveness in accelerating matrix multiplication and, in turn, the overall performance of deep learning models. However, as with any library, the performance of

cuBLAS is contingent upon the GPU architecture it's used with, meaning that the specific GPU's features and specifications can influence the acceleration achieved.

#### **Tensor Cores**

Tensor Cores [91] are innovative hardware units developed by NVIDIA and integrated into their Volta, Turing, and subsequent architectures. These units have been explicitly designed to accelerate matrix arithmetic, which is essential for deep learning operations. They allow significantly faster training and inference of neural networks by performing mixed-precision matrix multiply-and-accumulate calculations in a single operation. In more detail, a Tensor Core takes as input two half-precision floating-point matrices (FP16) and one full-precision matrix (FP32), performs a matrix multiplication of the half-precision matrices, and then adds the full-precision matrix to the result. The operation can be written as D = A \* B + C, where A and B are FP16 matrices, C and D are FP32 matrices, C and C are including in convolution and transformer-based architectures.

The ability of Tensor Cores to perform this operation in a single step leads to dramatic speedup in computation. They can deliver up to 125 teraFLOPS of performance for mixed-precision matrix multiplication in a single GPU, making them instrumental in achieving high performance in deep learning tasks. Moreover, using mixed-precision arithmetic, where the bulk of the computation is performed in lower precision, can lead to further acceleration and memory savings without significant loss in model accuracy. NVIDIA provides software support for using Tensor Cores in popular deep learning frameworks, making their power accessible to the deep learning community. Figure 2.8 illustrates the usage of Tensor Cores in a matrix multiplication operation.

## 2.2.3 High-Performance Computing with GPUs

High-performance computing (HPC) stands at the forefront of computational advancement, enabling researchers and industries to tackle complex, data-intensive tasks with unprecedented efficiency and speed. Over the past decade, Graphics Processing Units (GPUs) have emerged as a pivotal tool within the HPC landscape[93].

GPUs, originally designed for rendering images in computer graphics, have expanded their influence far beyond their initial purpose. Their ar-

Figure 2.8: Matrix Multiplication Operation with Tensor Cores[91]

chitecture, comprising hundreds to thousands of cores, allows for efficient parallel processing of computational tasks. This feature is well-aligned with the needs of HPC, where the simultaneous execution of tasks can significantly reduce computational times and improve the handling of large-scale problems.

The GPU's ability to accelerate computational workloads has found wide application in areas such as scientific computing, deep learning, and big data analytics. Compared to traditional Central Processing Units (CPUs), GPUs offer superior throughput and energy efficiency, making them particularly suitable for data-intensive computations in HPC.

Another significant aspect of GPUs in HPC is their compatibility with programming models and languages that have been widely adopted by the scientific community. For instance, NVIDIA's CUDA (Compute Unified Device Architecture) platform[23] provides a software environment that allows developers to use the C programming language to code algorithms directly into GPU instructions. This has greatly eased the implementation of GPU-based computation in HPC. The integration of GPUs into HPC systems has substantially enhanced the capability to handle 'big data.' As the volume of data generated by various fields continues to explode, the need for computational platforms that can quickly process and analyze this data becomes critical. GPUs, with their high-performance computing capabilities, provide a solution to this challenge.

Moreover, the advent of GPU-accelerated supercomputers has set new milestones in HPC. Notably, systems like the Summit at Oak Ridge National Laboratory in the United States and TSUBAME at the Tokyo Institute of Technology in Japan represent this major shift. The Summit supercomputer leverages thousands of GPUs, delivering unprecedented computational capabilities and setting the pace for scientific discovery. Similarly, the TSUBAME series, known for its GPU-accelerated computing power, have been instrumental in pushing the boundaries of HPC. The latest in this series, TSUB-

AME 3.0[112], has garnered international attention for its efficient power usage and significant computational capacity, showcasing the efficacy of GPU utilization in HPC.

These innovative supercomputers underline the critical role GPUs play in modern HPC systems and highlight a significant shift in supercomputer design and utilization. The ability to harness the power of GPUs at this scale opens up unprecedented possibilities for tackling large-scale, complex problems across a multitude of research domains.