# T2R2 東京工業大学リサーチリポジトリ Tokyo Tech Research Repository

## 論文 / 著書情報 Article / Book Information

| Title             | A 20 Gb/s 1:4 DEMUX with Near-Rail-to-Rail Logic Swing in 90 nm CMOS process                                                                                                                                                                                                                                                                      |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author            | A. Mineyama, T. Suzuki, H. Ito, S. Amakawa, N. Ishihara, K. Masu                                                                                                                                                                                                                                                                                  |

| Journal/Book name | 2009 IEEE MTT-S International Microwave Workshop Series on Signal Integrity and High-Speed Interconnects (IMWS2009-R9), , , pp. 119-122                                                                                                                                                                                                           |

| 発行日 / Issue date  | 2009, 2                                                                                                                                                                                                                                                                                                                                           |

| 権利情報 / Copyright  | (c)2009 IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. |

### A 20 Gb/s 1:4 DEMUX with Near-Rail-to-Rail Logic Swing in 90 nm CMOS process

A. Mineyama<sup>1</sup>, T. Suzuki<sup>2</sup>, H. Ito<sup>1</sup>, S. Amakawa<sup>1</sup>, N. Ishihara<sup>1</sup>, and K. Masu<sup>1</sup>

<sup>1</sup>Tokyo Institute of Technology, Yokohama 226-8503, Japan, paper@lsi.pi.titech.ac.jp

<sup>2</sup>Fujitsu Laboratories, Atsugi 243-0197, Japan

Abstract — A 9.5 mW 20 Gb/s  $40 \times 70~\mu m^2$  inductorless 1:4 DEMUX in 90 nm CMOS process is presented. In order to reduce power and area, the DEMUX uses a multi-phase clock architecture that requires a smaller number of latches operating at a slower clock rate than in the conventional tree architecture. To provide low-voltage scalability, the latches operate with a near-tail-to-rail logic swing. It is realized without significant speed penalty by adopting current-sourceless CML-type latches with unconventional settings. It offers a larger noise margin and elimination of logic level converters too. The well-balanced scalable design could possibly broaden the applications of high-speed SerDes in the coming ultralow-voltage many-core era.

Index Terms — DEMUX, CMOS, multi-phase clock architecture, near-rail-to-rail logic swing

#### I. INTRODUCTION

Applications of high-performance demultiplexers (DE-MUXes) [1]-[6] have so far been limited chiefly to those that accept a design trade-off in favor of speed, such as fiberoptic communication systems. In typical optical wavelengthdivision multiplexing (WDM) systems, for example, perwavelength speed of 10 Gb/s or faster is required. The conventional wisdom in gaining or maintaining speed of CML-type circuits, used in [1]-[6], has been to reduce the signal amplitude. A dilemma here is that the noise immunity might have to be traded off. Another problem is that current-mode logic (CML)-type circuits do not go well with the trend of lowering the supply voltage. As regards other factors than the speed, since as many DEMUXes as the wavelength multiplicity are needed in WDM systems, the power and area are also important considerations. We present a 1:4 DEMUX with near-rail-to-rail architecture that could offer a possible solution to the challenges in signal integrity and low-voltage scalability as well as in balancing the speed, power, and area.

#### II. ARCHITECTURE

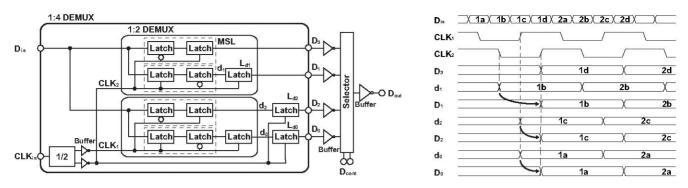

Fig. 1 shows the architecture of the 1:4 DEMUX along with a timing chart. This multi-phase clock architecture was chosen in favor of power and area reductions. The half-rate clock  $\text{CLK}_{\text{in}}$  is halved in frequency by the divider consisting

of 2 latches. Its outputs are quadrature-phase-shifted and are fed into the two 1:2 DEMUXes. In the upper 1:2 DEMUX, a pair of master-slave latches (MSLs) samples every other bit in the input bitstream Din by using rising and falling edges of the quarter-rate clock signal CLK<sub>2</sub>. The latch L<sub>d1</sub> aligns the outputs from the pair of MSLs. The lower 1:2 DEMUX operates likewise. The two 1:2 DEMUXes sample the input bitstream alternately as dictated by the phaseshifted clock signals CLK<sub>1</sub> and CLK<sub>2</sub> and perform the 1:4 DEMUX function. The latches  $L_{d0}$  and  $L_{d2}$  align the outputs from the lower 1:2 DEMUX with those from the upper one. The 1:4 DEMUX uses 12 latches altogether, as opposed to 15 in the conventional tree architecture [3], [4], which uses three 1:2 DEMUXes operating at a half rate. The quarterrate operation of the 1:2 DEMUXes in our design leads to low power dissipation. This design is similar to the 12-latch 1:4 DEMUX proposed in [6]. It thus allows more than 20 % power and area reductions in comparison with the 15-latch DEMUX. The selector circuit in Fig. 1 is for performing measurement with a small number of pads. It is a simple combinational logic circuit consisting of transmission gates and NOR gates.

#### III. CIRCUIT DESIGN

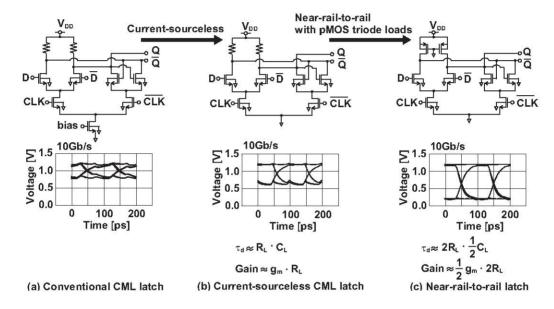

Fig. 2 shows circuit schematics of three different CMLtype latches. The CML has conventionally been the architecture of choice for high-speed digital circuits. However, in 90nm CMOS, the power supply voltage is limited to about 1.2 V and the threshold voltage is about 0.3 V. Each transistor, therefore, cannot enjoy sufficiently high voltage across its drain and source required for high-speed operation. Switching noise degrades the output eye opening as shown in Fig. 2(a). The current-sourceless CML structure was recently proposed for low-voltage operation [4], [7]. The tail transistor is eliminated to give increased voltage headroom. The size of the upper transistors is determined so that the gain of the differential amplifier is as low as 1 dB to 2 dB for high speed latching. The simulated eye diagram (Fig. 2(b)) shows a wider opening than that of the conventional CML (Fig. 2(a)). The signal swing is limited

Fig. 1. 1:4 DEMUX with multi-phase clock architecture and timing chart. Circuit core is enclosed in large rounded rectangle.

Fig. 2. Circuit schematics of latches with CML-type topology and simulated eye diagrams.

to up to 0.6 V, yet the clock has to have a rail-to-rail voltage swing.

In our design, in order to give a larger noise margin and better scalability in light of the ever-lowering supply voltage, near-rail-to-rail architecture is introduced making use of the current-sourceless CML-type topology [4]. To achieve the transition from the 0.6 V swing [4] to a near-1.2 V swing, the resistance  $R_{\rm L}$  of the loads has to be roughly doubled, but the speed might drop as a consequence. However, since the gain goes up with  $R_{\rm L}$ , the transistors can actually be made smaller to keep the gain low. Then, the parasitic capacitance  $C_{\rm L}$  associated with the transistors, including those being driven at the next stage, also becomes smaller, and therefore the cut-off frequency remains high. The signal amplitude thus becomes nearly rail-to-rail without imposing significant speed penalty. It is not quite rail-to-rail because of the small voltage drop across the transistors. In order to make the voltage drop small, the clocked transistors should be enlarged somewhat. Circuit blocks built with the near-rail-to-rail architecture can be freely intermixed with CMOS digital blocks without logic level conversion. In Fig. 1, the divider, the 1:2 DEMUXes, and the latches  $L_{\rm d0}$  and  $L_{\rm d2}$  are near-rail-to-rail, and the rest are built of CMOS logic gates and transmission gates.

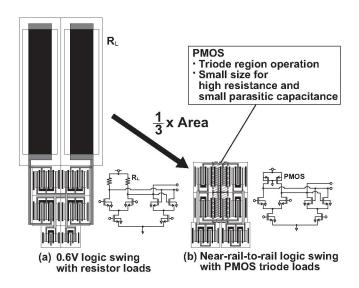

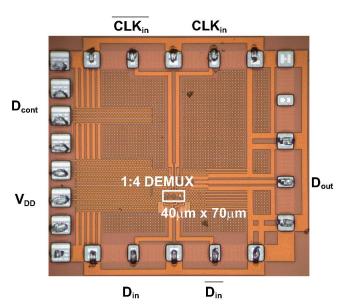

Fig. 3(a) schematically shows the layout of the current-sourceless CML latch in Fig. 2(b). The polysilicon load resistors cover a significant area. To reduce the area, PMOS loads operating in the triode (or linear) region are adopted as was done in [1], as shown in Figs. 2(c) and 3(b). This is a technique used in the pseudo-NMOS logic [8]. The area of the latch is estimated to become about a third of the current-sourceless CML architecture's, as illustrated in Fig. 3. The use of the PMOS triode loads instead of polysilicon resistors has no adverse effect on the signal integrity when the signal amplitude is near-rail-to-rail. A micrograph of the test chip is shown in Fig. 4. The circuit core area is  $40 \times 70 \ \mu m^2$ .

Fig. 3. Area reduction with the use of PMOS loads.

Fig. 4. Micrograph of 1:4 DEMUX.

#### IV. MEASUREMENT RESULTS

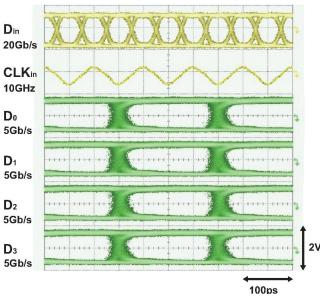

Fig. 5 shows measured output eye diagrams. The input was  $20\,\text{Gb/s}$  non-return-to-zero (NRZ)  $2^{31}-1$  pseudorandom binary sequence (PRBS). A half-rate sinusoidal clock signal of  $10\,\text{GHz}$  was also supplied. Each of the four output data streams was observed using a sampling oscilloscope and an error detector by selecting a channel. Wide eye openings were observed at an error rate of less than  $10^{-12}$ . The output jitter was  $20\,\text{ps}$  (p-p). The input data phase margin was 100 degrees for the input data mentioned. The power dissipation was  $9.5\,\text{mW}$  with the supply voltage of  $1.2\,\text{V}$ . Measurement was made also with

Fig. 5. Measured eye diagrams of 1:4 DEMUX.

lower supply voltages of down to 0.9 V. When the supply voltage was 0.9 V, the operation speed was 13 Gb/s and the power dissipation was 3.3 mW.

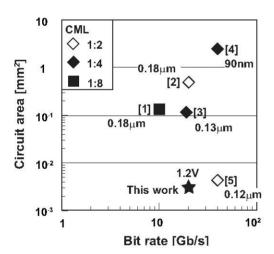

Comparisons are made in Fig. 6 of area and speed of CMOS DEMUXes [1]–[5]. Further details of the DEMUXes are given in Table I. All the earlier DEMUXes used CMLtype architecture with a small logic swing. The power dissipation values of our circuit, listed in Table I, are those of the circuit core (Fig. 1). This is because a DEMUX usually is connected to digital circuits on the same chip. But [2]–[5] only showed power dissipation values including output buffers, and those values are listed in Table I. While this prevents a strict comparison of power dissipation, we believe that the multi-phase clock architecture contributed to the low power. With respect to the area, ours is well over an order of magnitude smaller than the next smallest 1:4 DEMUX [3] and is still smaller than the 1:2 DEMUX [5]. Our inductorless DEMUX offers a good balance of speed, power, and area.

#### V. CONCLUSIONS

In conclusion, a  $9.5\,\mathrm{mW}$   $20\,\mathrm{Gb/s}$  near-rail-to-rail 1:4 DEMUX occupying the area of  $40\times70\,\mu\mathrm{m}^2$  is demonstrated in 90nm CMOS process. When the supply voltage is lowered from  $1.2\,\mathrm{V}$  to  $0.9\,\mathrm{V}$ , it operates at  $13\,\mathrm{Gb/s}$  and  $3.3\,\mathrm{mW}$ . The near-rail-to-rail architecture offers larger noise margin, better scalability with supply-voltage reduction than the existing CML-type architecture, and elimination of logic level converters for interfacing with CMOS digital blocks. The

TABLE I

SUMMARY OF HIGH-SPEED CMOS DEMUXES.

|                   |                        |                                 |                          |                               |                                | W                  | **      |

|-------------------|------------------------|---------------------------------|--------------------------|-------------------------------|--------------------------------|--------------------|---------|

|                   | [1]                    | [2]                             | [3]                      | [4]                           | [5]                            | This work          |         |

| DEMUX             | 1:8                    | 1:2                             | 1:4                      | 1:4                           | 1:2                            | 1:4                |         |

| Circiut topology  | feedback<br>MOS<br>CML | capacitive-<br>splitting<br>CML | coupled-<br>latch<br>CML | current-<br>sourceless<br>CML | CML                            | near-rail-to-rail  |         |

| Load              | PMOS<br>triode         | R+L                             | R                        | R+L                           | R                              | PMOS<br>triode     |         |

| Data rate         | 10 Gb/s                | 20 Gb/s                         | 19 Gb/s                  | 40 Gb/s                       | 40 Gb/s                        | 20 Gb/s            | 13 Gb/s |

| Power consumption | 48 mW                  | 105 mW*                         | 210 mW*                  | 62mW*                         | 108 mW*                        | 9.5 mW             | 3.3 mW  |

| Supply voltage    | 2.0 V                  | 2.0 V                           | 1.2 V                    | 1.2 V                         | 1.5 V                          | 1.2 V              | 0.9 V   |

| Voltage swing     | 0.2 V                  | 1.0 V                           | 0.25 V                   | 0.5 V                         | 0.6 V                          | 1.0 V              | 0.8 V   |

| Core circiut area | 300 x 420<br>μm²       | 650 x 770<br>μm²                | 280 x 410<br>μm²         | 1400 x 1800<br>μm²            | <b>60 x 70</b><br>μ <b>m</b> ² | <b>40 x 70</b> μm² |         |

| Technology        | 0.18 μm                | 0.18 μm                         | <b>0.13</b> μm           | 90 nm                         | 0.12 μm                        | 90 nm              |         |

\*Includes output buffer

Fig. 6. Comparison of areas of high-speed CMOS DEMUXes.

small footprint, the low power, and the manifold advantages brought by the near-rail-to-rail operation could possibly broaden the applications of high-speed serializer/deserializer (SerDes) to, for example, communication between subsystems constituting a complex system in a package (SiP) or system on a chip (SoC) in the coming ultralow-voltage many-core era.

#### ACKNOWLEDGMENTS

This work was partially supported by JSPS.KAKENHI, MEXT.KAKENHI, MIC.SCOPE, STARC, and VDEC in

collaboration with Agilent Technologies Japan, Ltd., Cadence Design Systems, Inc., and Mentor Graphics, Inc.

#### REFERENCES

- [1] A. Tanabe, M. Umetani, I. Fujiwara, T. Ogura, K. Kataoka, M. Okihara, H. Sakuraba, T. Endoh, and F. Masuoka, "A 10Gb/s demultiplexer IC in 0.18μm CMOS using current mode logic with tolerance to the threshold voltage fluctuation," ISSCC Dig. Tech. Papers, pp. 62-63, Feb. 2000.

- [2] J.-C. Chien and L.-H. Lu, "A 20-Gb/s 1:2 demultiplexer with capacitive-splitting current-mode-logic latches," *IEEE Trans. Mi*crowave Theory Tech., vol. 55, no. 8, pp. 1624-1632, Aug., 2007.

- [3] B.-G. Kim, L.-S. Kim, S. Byun, and H.-K. Yu, "A 20Gb/s 1:4 DEMUX without inductors in 0.13μm CMOS," ISSCC Dig. Tech. Papers, pp. 528-529, Feb. 2006.

- [4] K. Kanda, D. Yamazaki, T. Yamamoto, M. Horinaka, J. Ogawa, H. Tamura, and H. Onodera, "40Gb/s 4:1 MUX/1:4 DEMUX in 90nm standard CMOS," ISSCC Dig. Tech. Papers, pp. 152-153, Feb., 2005.

- [5] D. Kehrer, H.-D. Wohlmuth, H. Knapp, M. Wurzer, and A. L. Scholtz, "40-Gb/s 2:1 multiplexer and 1:2 demultiplexer in 120-nm standard CMOS," *IEEE J. Solid-State Circuits*, pp. 344-345, Feb., 2003.

- [6] K. Sano, K. Murata, H. Kitabayashi, S. Sugitani, H. Sugahara, and T. Enoki, "1.4-W 50-Gb/s InP HEMT 1:4 demultiplexer IC with a multi-phase clock architecture," *IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 1181-1184, June, 2003.

- [7] K. Kanda, D. Yamazaki, T. Yamamoto, M. Horinaka, J. Ogawa, H. Tamura, and H. Onodera, "40Gb/s 4:1 MUX/1:4 DEMUX in 90nm standard CMOS technology," *IEICE Tech. Rep.*, VLD2005-55, pp. 7-14, 2005 (in Japanese).

- [8] J. P. Uyemura, CMOS Logic Circuit Design, Kluwer Academic Publishers, 2001.