# T2R2 東京工業大学リサーチリポジトリ Tokyo Tech Research Repository

### 論文 / 著書情報 Article / Book Information

| 論題(和文)            |                                                                                                                                            |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | A Study of Inverter-based RF CMOS Low Noise Amplifier Scalability in CMOS Process                                                          |

| 著者(和文)            | DAYANG NUR SALMI D, 大鶴 基格, 中島 智也, 田野井 聡, 天川 修平, 伊藤 浩之, 石原 昇, 益 一哉                                                                          |

| Authors(English)  | Dayang Nur Salmi Dharmiza, Mototada Oturu, Tomoya Nakajima,<br>Satoru Tanoi, Shuhei Amakawa, Hiroyuki Ito, Noboru Ishihara, Kazuya<br>Masu |

| 出典(和文)            | 2011 年 電子情報通信学会総合大会,,,p. 95                                                                                                                |

| Citation(English) | ,,,p. 95                                                                                                                                   |

| 発行日 / Pub. date   | 2011, 3                                                                                                                                    |

| URL               | http://www.ieice.org/jpn/books/t_g.html                                                                                                    |

| 権利情報 / Copyright  | 本著作物の著作権は電子情報通信学会に帰属します。<br>Copyright (c) 2011 Institute of Electronics, Information and<br>Communication Engineers.                       |

## A Study of Inverter-based RF CMOS Low Noise Amplifier Scalability in CMOS Process

Dayang Nur Salmi Dharmiza, Mototada Oturu, Tomoya Nakajima, Satoru Tanoi, Shuhei Amakawa, Hiroyuki Ito, Noboru Ishihara, and Kazuya Masu

Solutions Research Laboratory, Tokyo Institute of Technology

#### 1 Introduction

Recently, small-sized and wide-band low noise amplifier (LNA) with low power consumption in RF circuits have been immensely developed. Today, electronic devices contain multiple RF front-end chips for various kind of wireless communications. Proportionally with the CMOS technology scaling, smaller size, higher cut-off frequency and lower power consumption are among the advantages obtained. However, passive devices such as inductors and capacitances consume large area despite of the developing scaling technology. Therefore, we study the scalability of CMOS inverter-based LNA.

#### 2 Scalable Wideband LNA Design

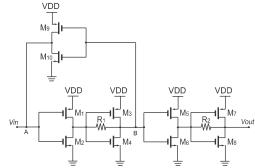

Figure 1 shows the schematic of our LNA circuit. We applied Cherry-Hooper technique and active gain peaking technique to our inverter based LNA to enhance the bandwidth. With Cherry-Hooper technique, Miller effect that usually limits bandwidth is reduced, and effective input capacitance for the first stage is defined as

$$C_{\text{in}} = C_{\text{gs1}} + C_{\text{gs2}} + (C_{\text{gd1}} + C_{\text{gd2}})[1 + (g_{\text{m1}} + g_{\text{m2}})Z_{\text{x}}]$$

(1)

Moreover, as CMOS gate width is scaled down, parasitic capacitances such as  $C_{\rm gs}$  and  $C_{\rm gd}$  are reduced and this further enables improvement in the bandwidth expansion.

Second method for bandwidth enhancement is by implementing inverter feedback to the cascaded inverters. Instead of implementing the commonly used capacitance or inductive peaking technique to broaden the bandwidth, we used an active peaking technique using scalable CMOS inverter. With feedback inverter, the feedback is negative at low frequency, and as the frequency increases, the feedback changes to positive.

Finally, in the end of the proposed design, an additional low-resistance feedback amplifier is added to provide high load impedance to the voltage amplifier and better  $50\,\Omega$  output matching. Since no passive device was used in the entire circuit, this design promises scalability in size.

#### 3 Scalability Results

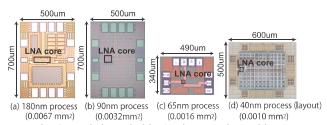

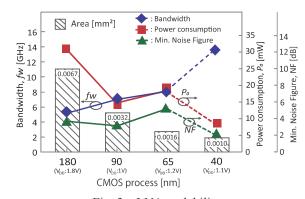

The circuit was fabricated with 40 nm, 65 nm, 90 nm and 180 nm CMOS process. Chip micrographs (65 nm, 90 nm 180 nm) and layout (40 nm) of our designed LNAs are shown in Fig 2 with size comparison. The scalability of the circuit in size, power consumption, noise figure, and bandwidth of each process when gain is above 15 dB and S11<-10 dB are shown in Fig 3. 40 nm LNA is currently under fabrication, thus simulation result is presented.

#### 4 Conclusion

In this work, we proposed wideband scalable inverterbased RF CMOS LNA. Based on the results obtained, our LNA is highly potential in scalability as we achieved higher bandwidth and smaller size accordingly to the CMOS scaling. For future work, we are going to investigate methods on how to improve circuit linearity and minimize noise figure for our designed LNA.

#### Acknowledgments

This work was partially supported by STARC, MIC.SCOPE, JSPS.KAKENHI, NEDO, and VDEC in collaboration with Agilent Technologies, Cadence Design Systems, Inc., and Mentor Graphics, Inc.

Fig. 1 Proposed LNA schematic

Fig. 2 Fabricated chips' micrographs and layout

Fig. 3 LNA scalability