T2R2 東京工業大学リサーチリポジトリ Tokyo Tech Research Repository

### 論文 / 著書情報 Article / Book Information

| 題目(和文)            |                                                                                                                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title(English)    | Millimeter-Wave CMOS Transceiver Toward 100Gb/s Communication Systems                                                                                                                        |

| 著者(和文)            | TokgozKorkutKaan                                                                                                                                                                             |

| Author(English)   | Korkut Kaan Tokgoz                                                                                                                                                                           |

| 出典(和文)            | 学位:博士(学術),<br>学位授与機関:東京工業大学,<br>報告番号:甲第10891号,<br>授与年月日:2018年3月26日,<br>学位の種別:課程博士,<br>審査員:岡田 健一,松澤 昭,益 一哉,髙木 茂孝,伊藤 浩之,川野 陽一                                                                  |

| Citation(English) | Degree:Doctor (Academic),<br>Conferring organization: Tokyo Institute of Technology,<br>Report number:甲第10891号,<br>Conferred date:2018/3/26,<br>Degree Type:Course doctor,<br>Examiner:,,,,, |

| 学位種別(和文)          | 博士論文                                                                                                                                                                                         |

| Type(English)     | Doctoral Thesis                                                                                                                                                                              |

# Millimeter-Wave CMOS Transceiver Toward 100Gb/s Communication Systems

by

Korkut Kaan Tokgoz

A Ph. D. dissertation submitted in partial satisfaction of the requirements for the degree of

# **Department of Physical Electronics**

in the

## **Graduate School of Science and Engineering**

of

## **Tokyo Institute of Technology**

Supervised by

Prof. Kenichi Okada and Prof. Akira Matsuzawa

Winter 2017

To my family,

# Acknowledgment

First of all, I would like to thank Prof. Kenichi Okada, and Prof. Akira Matsuzawa for giving me this wonderful opportunity to be a part of Matsuzawa&Okada Laboratory, and Tokyo Institute of Technology.

I would like to express my sincere thanks to Prof. Kenichi Okada, for his valuable guidance till now starting from the day of enrollment. Even with his very busy schedule, he always spent his valuable time on not only technical issues, but also on writing, presentation skills, and daily life talks. I am thankful for his advices, comments, and suggestions on every issue. For sure, without his guidance this work could not be done. In short, I appreciate his trust in me.

I am very grateful to Prof. Akira Matsuzawa for his help and support from the day I arrived in Japan. His advices on every issue is very valuable and I always tried to follow them.

I would like to thank Yoshino Kasuga and Makiko Tsunashima for their valuable helps and time on applications, documents, registrations and monthly reports for several different topics. Their advices and explanations on these issues are always very helpful.

I am also grateful to Prof. Kazuya Masu, Prof. Shigetaka Takagi, Prof. Hiroyuki Ito, from Tokyo Institute of Technology, Tokyo, Japan; and Dr. Yoichi Kawano from Fujitsu Lab., Atsugi, Japan for their valuable time for examining my thesis.

I, also, would like to thank Shotaro Maki, Jian Pang, Noriaki Nagashima, Seitarou Kawai, Ibrahim Abdo, Takuya Fujimura, Yuuki Seo, Nurul Fajri, and Kimsrun Lim for their contributions on the works that we have conducted. I am thankful to all of the past and present members of our laboratory for daily conversations and talks.

I am grateful to my parents, Hatice&Serdar Tokgoz, for their endless love, support, prayers and encouragement. I thank my sister Emel (Tokgoz) Yildiz and my brother-inlaw Alparslan Yildiz for making Japan homelike being together in Tokyo, and sharing great moments. I thank my little brother Baybars Baturalp Tokgoz for being the joy of our family.

## Abstract

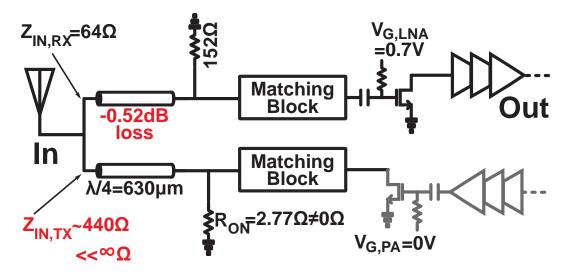

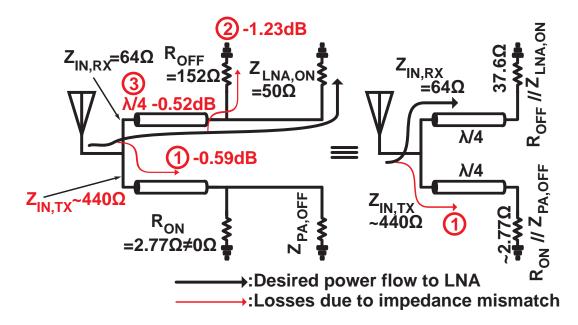

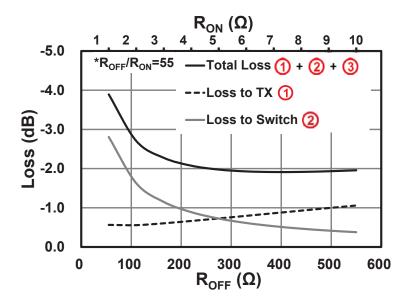

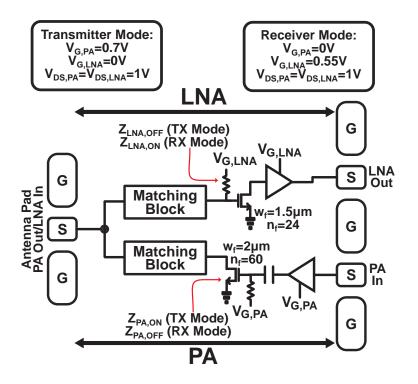

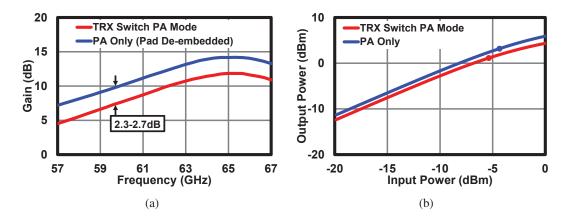

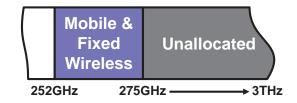

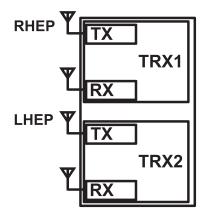

In this thesis, millimeter-wave CMOS wireless transceivers are proposed to achieve data-rates of more than 100Gb/s. An ultra-wideband 70-to-105GHz wireless transceiver is implemented on 65nm CMOS technology based on frequency-interleaving architecture. This work achieves the world fastest data-rate of 120Gb/s. Additionally, a 60GHz low-loss transmit/receive switch circuitry is proposed based on re-using LNA and PA transistors as switching elements with matching block design for TDD transceivers. Switch architecture has no area consumption with 1.1dB minimum loss in RX mode and 2.3dB minimum loss in TX mode. Accurate methods on device layout optimization, de-embedding, characterization and modeling are done for both active and passive devices to achieve robust and accurate wireless transceivers. The characterization of devices is done up to 320GHz. A 16-stage 273-to-301GHz amplifier is designed in 65nm CMOS achieving a peak gain of 21dB with a power consumption of 35mW from a 1.2V DC supply.

# Contents

| A  | cknow  | ledgme    | nt                                                              | iii |

|----|--------|-----------|-----------------------------------------------------------------|-----|

| Al | bstrac | :t        |                                                                 | iv  |

| 1  | Intr   | oductio   | n                                                               | 1   |

|    | 1.1    | Expect    | ations from Wireless Technology                                 | 1   |

|    | 1.2    | Metho     | ds and Approaches to Increase Wireless Data-Rate                | 3   |

|    | 1.3    | Millim    | eter-Wave Research and CMOS                                     | 6   |

|    | 1.4    | Organi    | zation of Thesis                                                | 7   |

| 2  | Mill   | imeter-`  | Wave Transceiver Design                                         | 9   |

|    | 2.1    | Device    | Characterization and Tile-Based Design                          | 9   |

|    | 2.2    | Optim     | um Carrier Frequency and Moduation                              | 10  |

|    | 2.3    | Transis   | stor Gain Definitions                                           | 13  |

|    |        | 2.3.1     | Maximum Available Gain                                          | 13  |

|    |        | 2.3.2     | Unilateral Gain                                                 | 14  |

|    |        | 2.3.3     | Maximum Achiavable Gain                                         | 15  |

| 3  | Mod    | leling ar | nd Characterization of Devices                                  | 18  |

|    | 3.1    | Introdu   | action                                                          | 18  |

|    | 3.2    | Conver    | ntional Device Models                                           | 19  |

|    |        | 3.2.1     | Pad Parasitic De-Embedding and Transmission Line Models         | 19  |

|    |        | 3.2.2     | Transistor Model                                                | 30  |

|    |        | 3.2.3     | Passive Device Model                                            | 31  |

|    |        | 3.2.4     | Application of Conventional Device Models on a V-Band Amplifier | 40  |

|    |        | 3.2.5     | Application of Conventional Device Models on a W-Band Amplifier | 41  |

|    | 3.3    | Propos    | ed Device Models                                                | 48  |

|    |        | 3.3.1     | Improved Pad Parasitic De-Embedding and Transmission Line       |     |

|    |        |           | Models                                                          | 48  |

|   |      | 3.3.2   | Corner Characterization                                          | 48  |

|---|------|---------|------------------------------------------------------------------|-----|

|   |      | 3.3.3   | Tee-Junction Characterization                                    | 50  |

|   |      | 3.3.4   | Metal-Insulator-Metal Transmission Line                          |     |

|   |      |         | Characterization                                                 | 54  |

|   |      | 3.3.5   | Application of Updated Device Models on a W-Band Amplifier .     | 60  |

|   | 3.4  | Differe | ential Device Characterizations and Applications on Differential |     |

|   |      | Ampli   | fiers                                                            | 63  |

|   |      | 3.4.1   | Four-Port Ground-Signal-Signal-Ground De-Embedding               | 63  |

|   |      | 3.4.2   | Cross-Line Structure and Characterization Method                 | 67  |

|   |      | 3.4.3   | Application on a 60GHz Differential Amplifier                    | 69  |

|   | 3.5  | Multi-  | Port Passive Device Characterization                             |     |

|   |      | Appro   | aches Based on Two-Port VNA Measurements                         | 75  |

|   |      | 3.5.1   | Introduction                                                     | 75  |

|   |      | 3.5.2   | Previous Works on Multi-Port Device Characterization Techniques  | 76  |

|   |      | 3.5.3   | Cross-Line Characterization Based on                             |     |

|   |      |         | Two-Port VNA Measurements                                        | 77  |

|   |      | 3.5.4   | Crossing Transmission Line (CTL) Characterization Based on       |     |

|   |      |         | Two-Port VNA Measurements                                        | 84  |

|   |      | 3.5.5   | Crossing Transmission Line (CTL) Modeling Based on Two-Port      |     |

|   |      |         | VNA Measurements                                                 | 95  |

|   |      | 3.5.6   | Crossing Transmission Line (CTL) Application on                  |     |

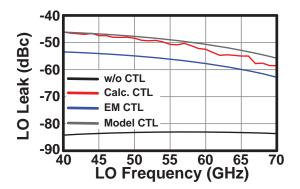

|   |      |         | Millimeter-Wave Mixer                                            | 100 |

|   |      | 3.5.7   | e                                                                | 102 |

|   | 3.6  | Conclu  | usions on Device Modeling Chapter                                | 109 |

| 4 | Mill | imeter- | Wave and Sub-Terahertz Amplifier Design                          | 111 |

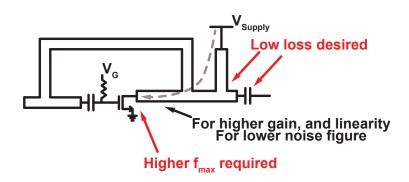

| - | 4.1  |         | n of Ultra-Wideband (UWB) W-band Low-Noise Amplifier             |     |

|   |      | 0       | Introduction                                                     |     |

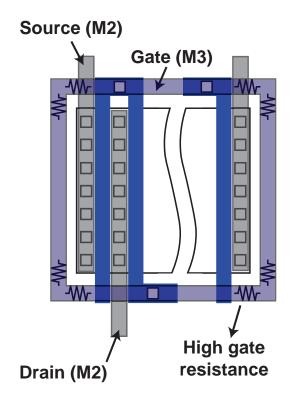

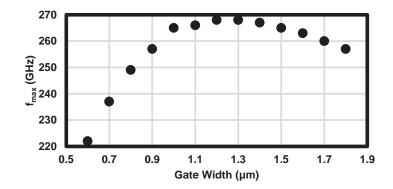

|   |      | 4.1.2   | Transistor Size Considerations                                   |     |

|   |      | 4.1.3   | Design and Simulation Results of Amplifier                       |     |

|   |      | 4.1.4   | Small Signal Measurement Results                                 |     |

|   | 4.2  | Sub-Te  | erahertz Amplifiers                                              |     |

|   |      | 4.2.1   | Introduction                                                     |     |

|   |      | 4.2.2   | Sub-Terahertz Amplifier Considerations                           |     |

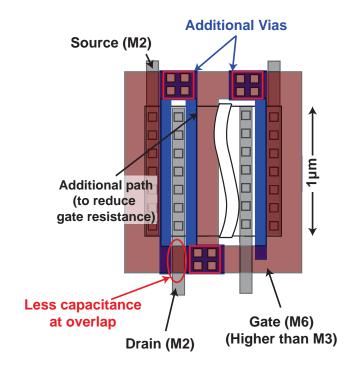

|   |      | 4.2.3   | Device Considerations                                            |     |

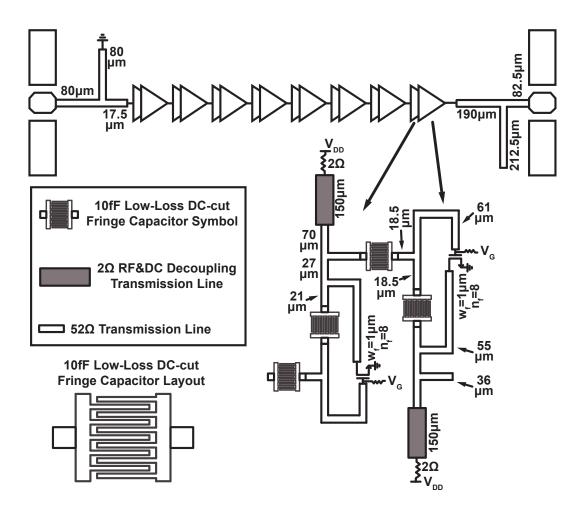

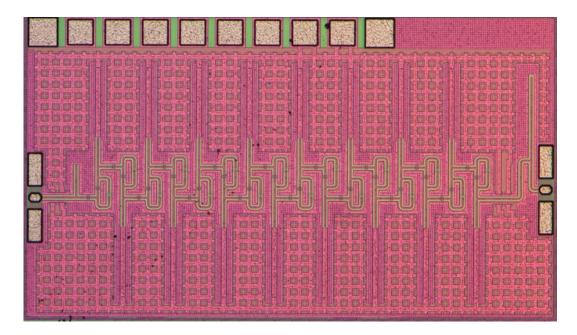

|   |      | 4.2.4   | Design of Sub-Terahertz CMOS Amplifier                           |     |

|   |      | 4.2.5   | Measurement Results                                              |     |

|   |      | 4.2.6 Conclusions                                       | 36 |

|---|------|---------------------------------------------------------|----|

|   | 4.3  | Asymmetrical Bi-Directional LNA/PA                      | 12 |

| 5 | Ultr | a-High Data-Rate Frequency-Interleave Transceiver 14    | 15 |

|   | 5.1  | Introduction                                            | 15 |

|   | 5.2  | Frequency-Interleave Transceiver                        | 15 |

|   | 5.3  | W-Band Transceiver                                      | 54 |

|   | 5.4  | Building Block Circuitry Design and Results             | 56 |

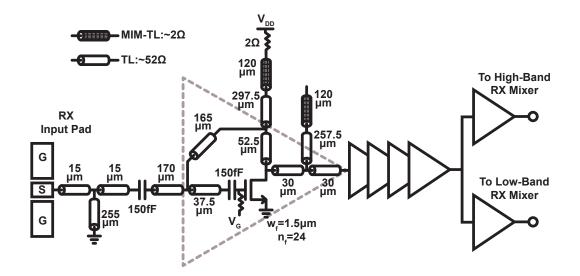

|   |      | 5.4.1 Millimeter-Wave Amplifiers                        | 56 |

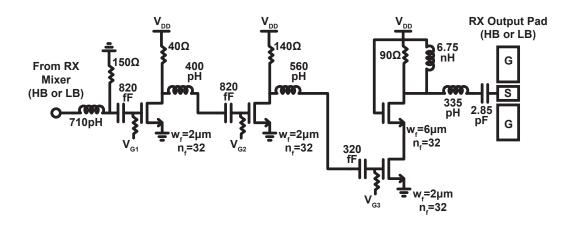

|   |      | 5.4.2 Receiver Wideband IF Amplifier                    | 56 |

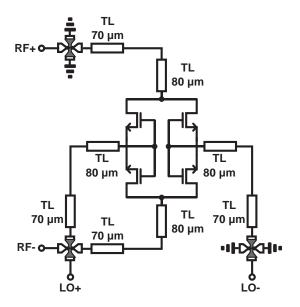

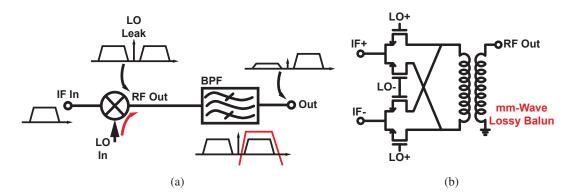

|   |      | 5.4.3 Single-IF Balanced Mixer                          | 57 |

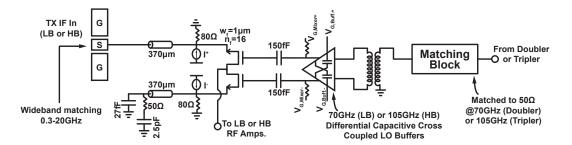

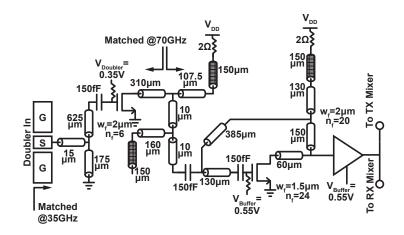

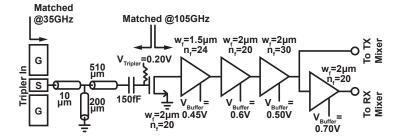

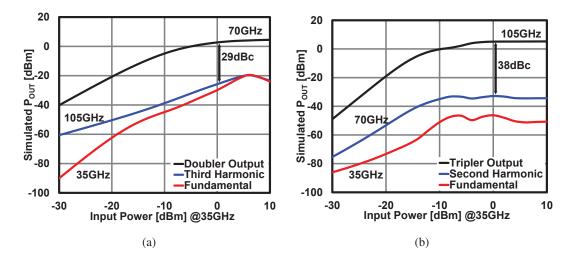

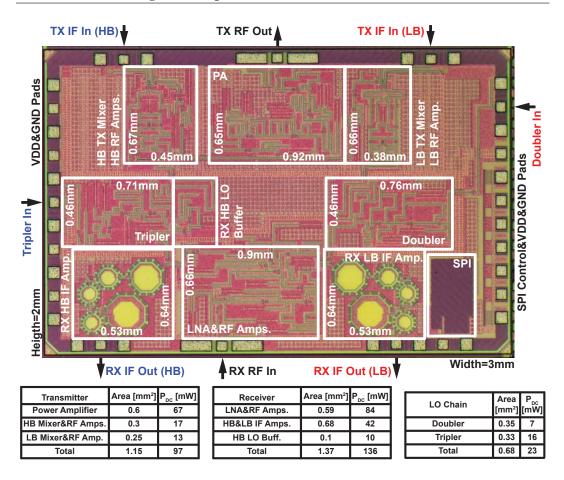

|   |      | 5.4.4 Doubler and Tripler Design                        | ;9 |

|   | 5.5  | Test Module Design and Implementation                   | 52 |

|   | 5.6  | Measurement Results                                     | 6  |

|   | 5.7  | Conclusion                                              | 32 |

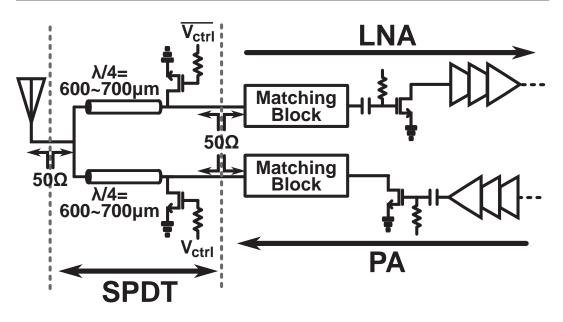

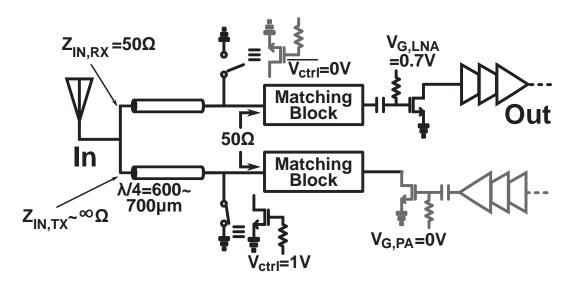

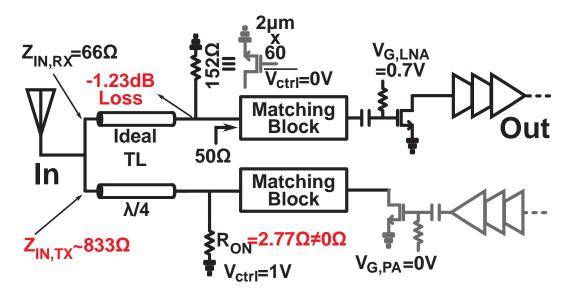

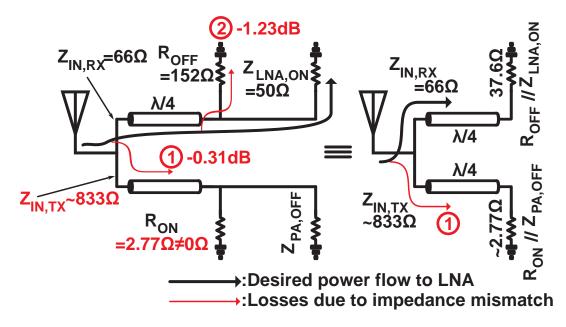

| 6 | Trai | nsmitter-Receiver Switch 18                             | 34 |

|   | 6.1  | Introduction                                            | 34 |

|   | 6.2  | Conventional SPDT Switch Architecture                   | 36 |

|   | 6.3  | Proposed Integrated Antenna Switch                      | )3 |

|   | 6.4  | Measurement Structures and Results                      | )3 |

|   | 6.5  | Conclusions                                             | )8 |

| 7 | Con  | clusions and Future Directions 21                       | 0  |

|   | 7.1  | Conclusions                                             | 0  |

|   | 7.2  | Future Directions                                       | .2 |

| A | Pub  | lication List 22                                        | 27 |

|   | A.1  | Journal Papers                                          | 27 |

|   | A.2  | International Conferences and Workshops (Peer-Reviewed) |    |

|   | A.3  | International Conferences and Workshops (Not Reviewed)  | 29 |

|   | A.4  | Domestic Conferences and Workshops                      |    |

|   | A.5  | Co-Author                                               | 31 |

|   |      | A.5.1 Journals and Letters                              | 31 |

|   |      | A.5.2 Conferences                                       | 32 |

# **List of Figures**

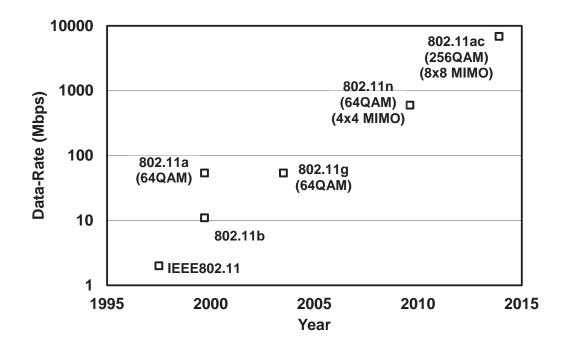

| 1.1 | Wireless communication standard IEEE802.11, 11a, 11b, 11g, 11n, and                                                                                      |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 11ac data-rates.                                                                                                                                         | 4  |

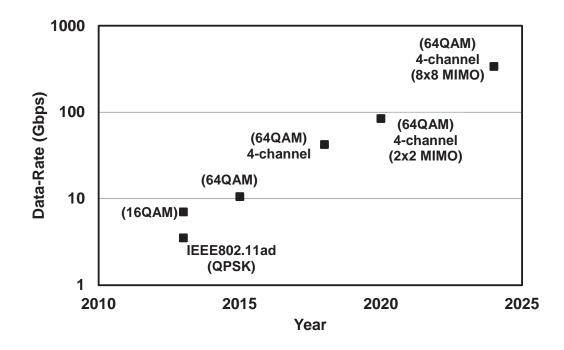

| 1.2 | Wireless communication standard IEEE802.11ad data-rates.                                                                                                 | 5  |

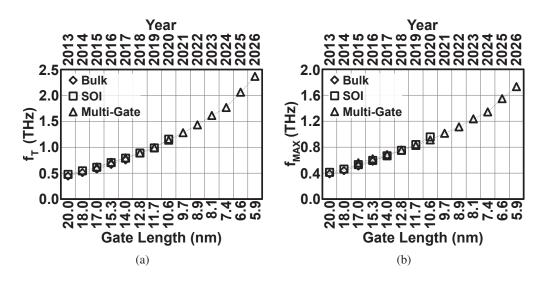

| 1.3 | Transistors expected performances in terms of (a) Cut-off frequency (THz) vs. gate length (nm) and years, and (b) maximum oscillation                    |    |

|     | frequency (THz) vs. gate length (nm) and years based on ITRS Roadmap                                                                                     |    |

|     | of 2013                                                                                                                                                  | 7  |

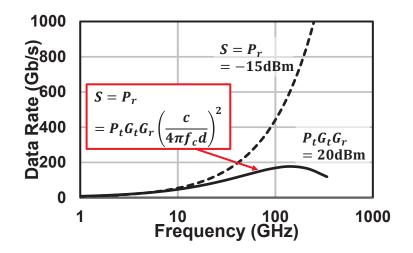

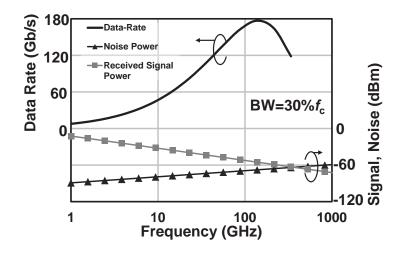

| 2.1 | Channel capacity vs. $f_c$ when the bandwidth is 30% of $f_c$ , the dashed line                                                                          |    |

|     | represents the data rate when received power is assumed to be constant at                                                                                |    |

|     | -15dBm, and the solid line represents the data rate as the received power                                                                                | 11 |

| 2.2 | is changing as center frequency changes ( $S = P_{eff} = 20 \text{ dBm}$ )                                                                               | 11 |

| 2.2 | Channel capacity vs. $f_c$ (solid black line) when $P_{eff} = 20$ dBm, and $d = 1$ m. Signal power (square marked line) and noise power (triangle marked |    |

|     | line) plotted on the secondary vertical axis.                                                                                                            | 12 |

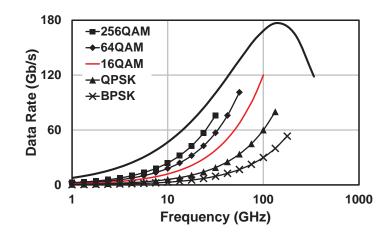

| 2.3 | Channel capacity vs. $f_c$ for different modulation schemes when $P_{eff}$ =                                                                             | 12 |

| 2.5 | 20dBm, and BW= $30%$ .                                                                                                                                   | 13 |

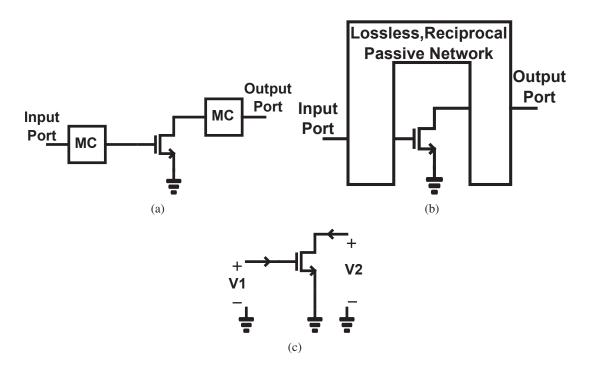

| 2.4 | Gain definitions (a) maximum available gain, (b) unilateral gain, and (c)                                                                                |    |

|     | additional conditions for maximum achievable gain                                                                                                        | 14 |

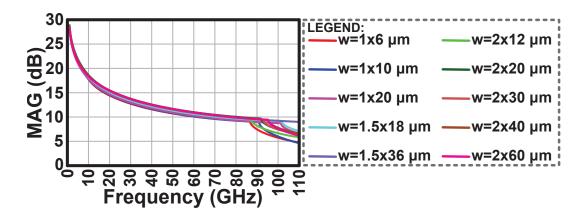

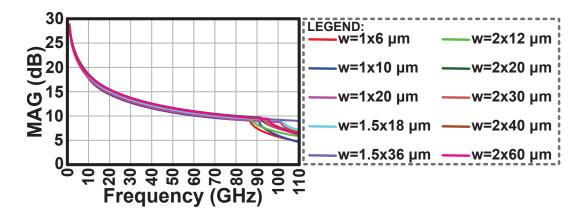

| 2.5 | Maximum available gain comparisons for different transistor sizes                                                                                        |    |

|     | (AxBµm means that A is one finger width, and B is the total width).<br>                                                                                  | 15 |

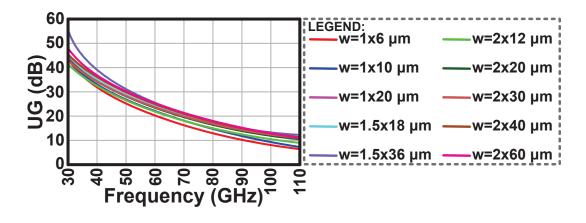

| 2.6 | Unilateral gain comparisons for different transistor sizes (AxBµm means                                                                                  |    |

|     | that A is one finger width, and B is the total width)                                                                                                    | 16 |

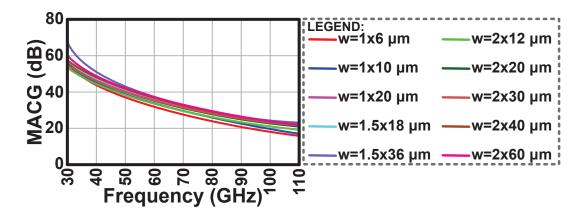

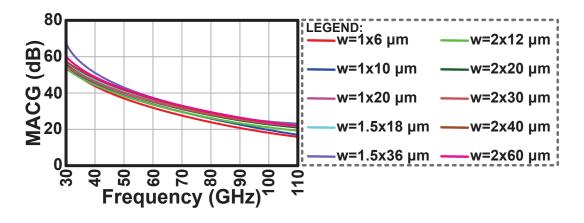

| 2.7 | Maximum achievable gain comparisons for different transistor sizes                                                                                       |    |

|     | (AxBµm means that A is one finger width, and B is the total width)                                                                                       | 17 |

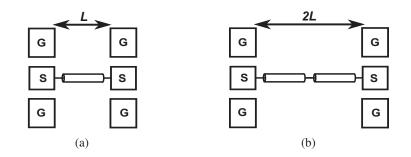

| 3.1 | Transmission line structures used for de-embedding (a) with length "L",                                                                                  |    |

|     | and (b) with length "2L" (Note that two transmission line structures are                                                                                 |    |

|     | connected in series for illustration purposes regarding lengths)                                                                                         | 20 |

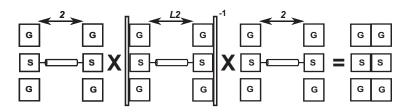

| 3.2  | Illustration of calculation to obtain virtual-thru response of pads                      | 20 |

|------|------------------------------------------------------------------------------------------|----|

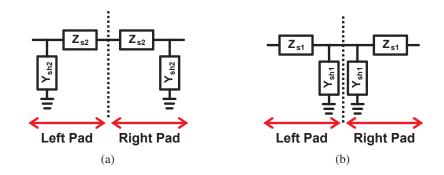

| 3.3  | Representation of pad parasitics in terms of lumped models (a) II-model                  |    |

|      | and (b) T-model when the pads are assumed to be connected back-to-back.                  | 21 |

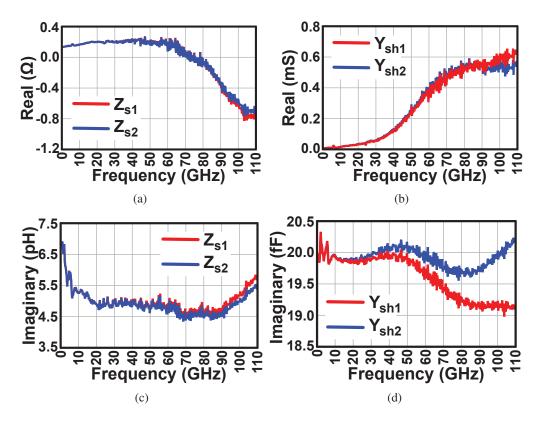

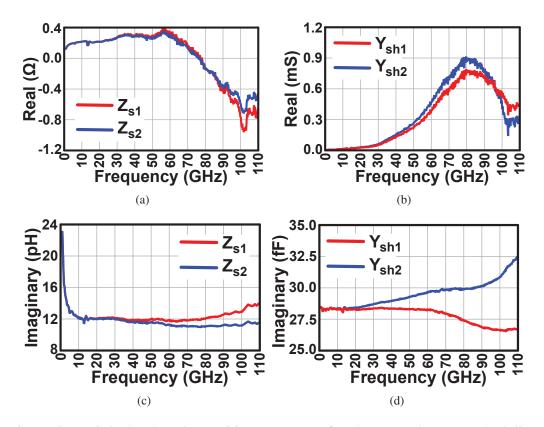

| 3.4  | Calculated pad parasitic parameters (red lines represent parasitic                       |    |

|      | components calculated from T-Model and blue lines represent parasitic                    |    |

|      | components calculated from II-Model) for two different calculation                       |    |

|      | method (a) real part of series parasitic components ( $\Omega$ ), (b) real part of       |    |

|      | shunt components (mS), (c) imaginary part of series components (pH),                     |    |

|      | and (d) imaginary part of shunt components (fF).                                         | 22 |

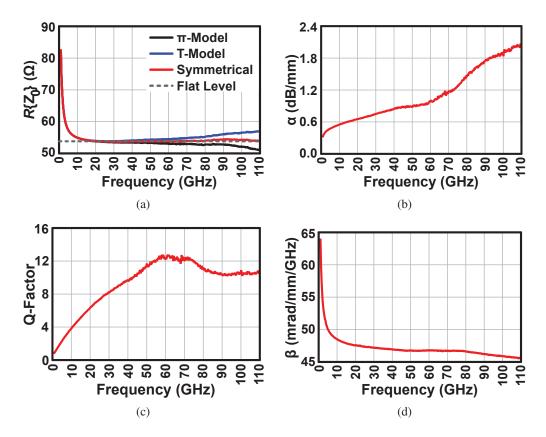

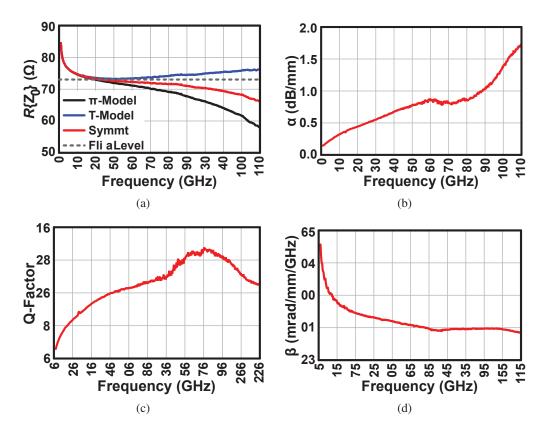

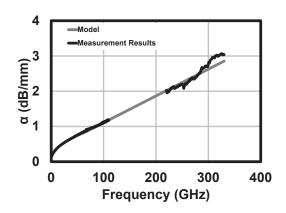

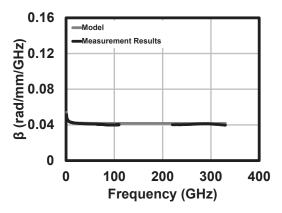

| 3.5  | Obtained transmission line characteristics using above equations (a) real                |    |

|      | part of characteristic impedance ( $\Omega$ )(black line is from $\Pi$ -model, blue line |    |

|      | is from T-model, red line is from symmetry assumption, dashed gray line                  |    |

|      | is for flat leveling), (b) loss term $\alpha$ (dB/mm), (c) quality-factor, and (d)       |    |

|      | propagation constant $\beta$ (mrad/mm/GHz)                                               | 24 |

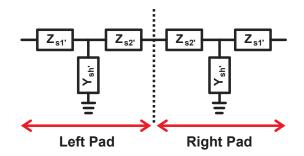

| 3.6  | Illustration of a more general pad model (Double-T type)                                 | 25 |

| 3.7  | Calculated pad parasitic parameters for the second process (red lines                    |    |

|      | represent parasitic components calculated from T-Model and blue lines                    |    |

|      | represent parasitic components calculated from Π-Model) for two                          |    |

|      | different calculation method (a) real part of series parasitic components                |    |

|      | $(\Omega)$ , (b) real part of shunt components (mS), (c) imaginary part of series        |    |

|      | components (pH), and (d) imaginary part of shunt components (fF). $\ldots$               | 27 |

| 3.8  | Obtained transmission line characteristics for the second process (a) real               |    |

|      | part of characteristic impedance ( $\Omega$ )(black line is from $\Pi$ -model, blue line |    |

|      | is from T-model, red line is from symmetry assumption, dashed gray line                  |    |

|      | is for flat leveling), (b) loss term $\alpha$ (dB/mm), (c) quality-factor, and (d)       |    |

|      | propagation constant $\beta$ (mrad/mm/GHz)                                               | 28 |

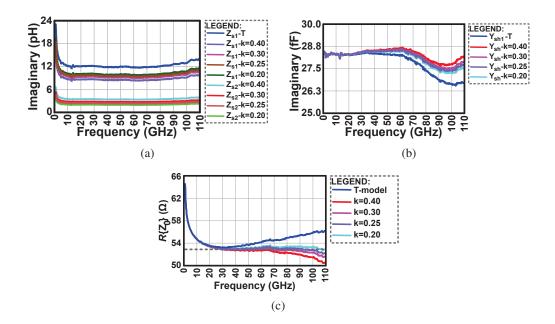

| 3.9  | Pad parasitics variation and related de-embedding results (a) imaginary                  |    |

|      | part of series components variations in terms of k compared with T-model                 |    |

|      | series parasitic (b) imaginary part of shunt component variations in terms               |    |

|      | of $k$ compared with T-model shunt parasitic, and (c) related transmission               |    |

|      | line characteristic response after de-embedding for different k values                   | 29 |

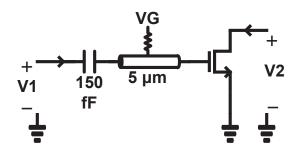

| 3.10 | Simple transistor characerization structure. Gate bias is provided from                  |    |

|      | the port connected to gate of transistor and DC feed is provided from the                |    |

|      | port connected to drain of transistor.                                                   | 31 |

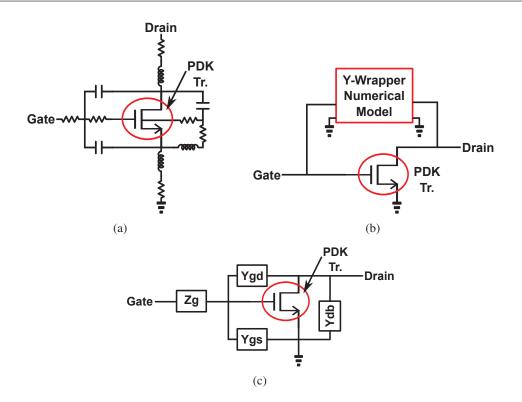

| 3.11 | Transistor models (a) lumped model, (b) "Y-wrapper" Model, and (c)                       |    |

|      | parasitics model including gate impedance.                                               | 32 |

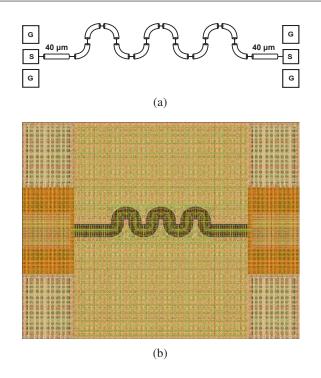

| 3.12 | Illustration of corner characterization TEG (a) schematic, and (b) layout                | 33 |

| 3.13 Simple corner model based on transmission line sections                                                                               | 33  |

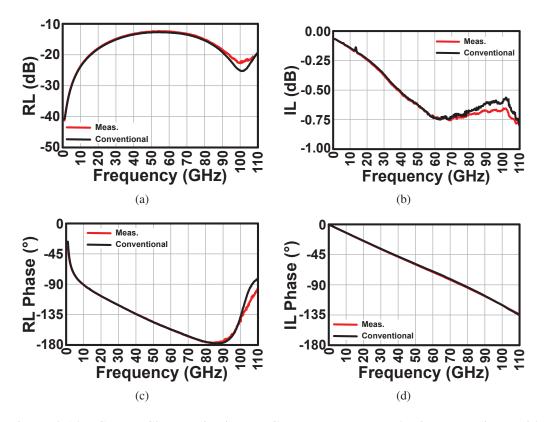

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.14 Corner Characterization TEG measurement results in comparison w<br>device models (red lines present measurement results and black lin |     |

| present model results) (a) magnitude of return loss comparisons,                                                                           | (b) |

| magnitude of insertion loss comparisons, (c) phase of return le                                                                            | oss |

| comparisons, and (d) phase of insertion loss comparisons                                                                                   | 34  |

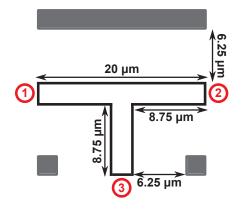

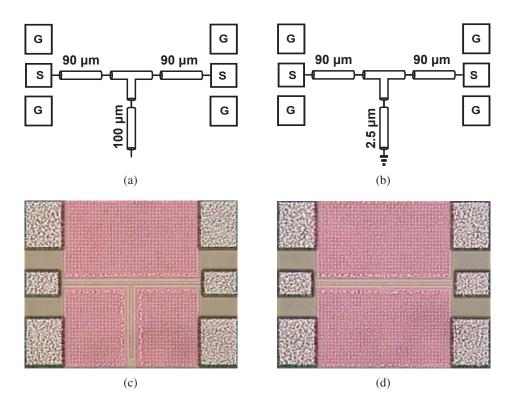

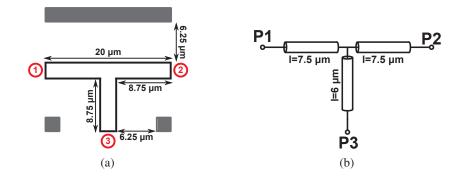

| 3.15 Illustration of used tee-junction geometry                                                                                            | 35  |

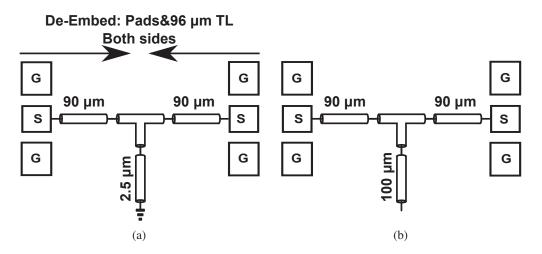

| 3.16 Tee-junction modeling TEGs (a) port 3 is terminated with open circuit                                                                 | ted |

| 100 $\mu$ m transmission line (b) port 3 is terminated with short circuited                                                                | 2.5 |

| $\mu$ m transmission line, (c) chip micrographs of (a), and (d) chip microgra                                                              | ^   |

| of (b)                                                                                                                                     | 36  |

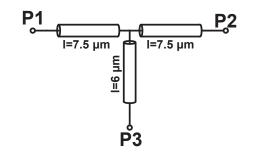

| 3.17 Simple tee-junction model based on transmission lines                                                                                 | 37  |

| 3.18 Tee-junction characterization TEG measurement results in comparis                                                                     | son |

| with device models (red lines present measurement results and bla                                                                          |     |

| lines present model results) (a) magnitude of return loss comparisons                                                                      |     |

| tee-junction terminated with open circuited transmission line,                                                                             |     |

| magnitude of return loss comparisons for tee-junction terminated w                                                                         |     |

| short circuited transmission line, (c) magnitude of insertion le                                                                           |     |

| comparisons for tee-junction terminated with open circui transmission line, and (d) magnitude of insertion loss comparisons                |     |

| tee-junction terminated with short circuited transmission line                                                                             |     |

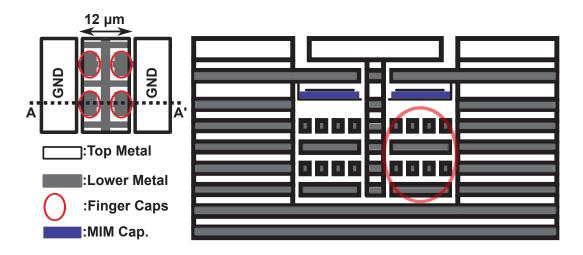

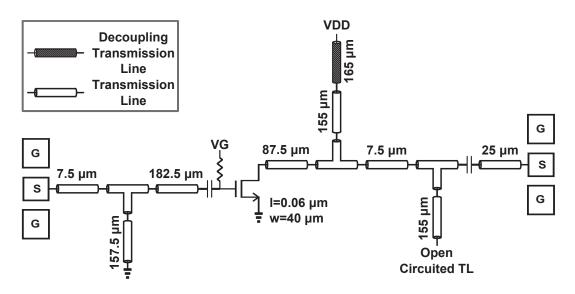

| 3.19 Illustration of metal layers and MIM capacitor layers for M                                                                           |     |

| transmission line.                                                                                                                         |     |

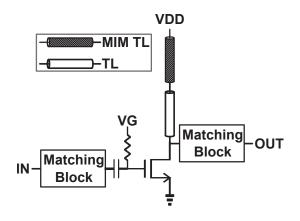

| 3.20 Representation of a simple and general common-source amplifier sta                                                                    |     |

| with matching blocks and other components. MIM TL is used for DC                                                                           | -   |

| RF decoupling.                                                                                                                             |     |

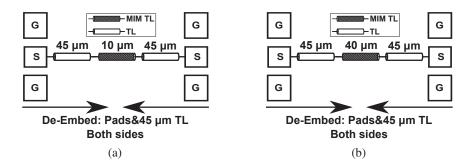

| 3.21 Direct two-port characterization TEGs for MIM TL (a) 10µm MIM TI                                                                      |     |

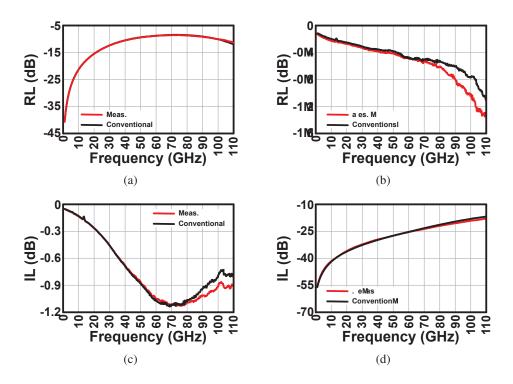

| placed, and (b) 40μm MIM TL is placed                                                                                                      |     |

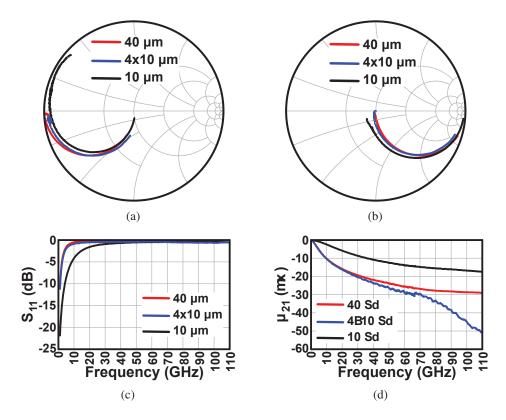

| 3.22 Comparison of 10μm, four times cascaded 10μm, and 40μm MIM                                                                            |     |

| (a) return loss on smith chart from 1 to 110 GHz, (b) insertion loss                                                                       |     |

| smith chart from 1 to 110 GHz, (c) magnitude (dB) of return loss, and                                                                      |     |

| magnitude (dB) of insertion loss.                                                                                                          |     |

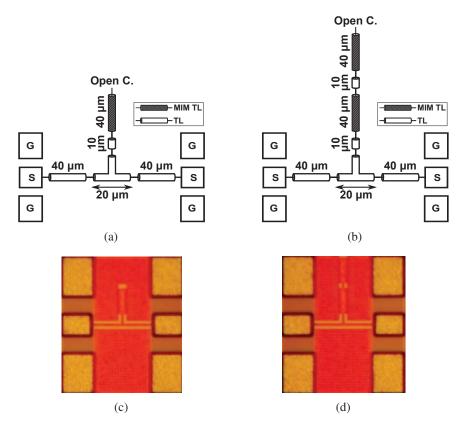

| 3.23 Shunt characterization TEGs for MIM TL (a) 40 µm MIM TL is place                                                                      |     |

| on the third port of tee-junction, (b) two 40 $\mu$ m MIM TL is placed on                                                                  |     |

| third port of tee-junction, (c) chip photo of (a), and (d) chip photo of (                                                                 |     |

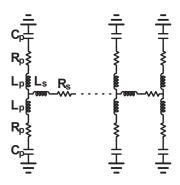

| 3.24 Assumed lumped model for MIM TL characterization                                                                                      | 42  |

| 3.25 | S-parameter comparison results of model and measurements on smith             |    |

|------|-------------------------------------------------------------------------------|----|

|      | charts from 1 to 110 GHz (a) 40 $\mu m$ MIM TL connected TEG return           |    |

|      | loss, (b) two 40 $\mu m$ MIM TL connected TEG return loss, (c) 40 $\mu m$ MIM |    |

|      | TL connected TEG insertion loss, and (d) two 40 $\mu m$ MIM TL connected      |    |

|      | TEG insertion loss.                                                           | 43 |

| 3.26 | Schematic of the designed V-Band Amplifier.                                   | 44 |

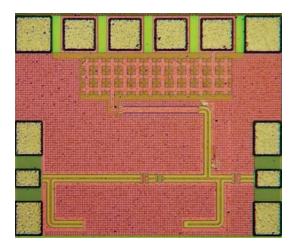

| 3.27 | Chip photo of the designed V-Band Amplifier                                   | 44 |

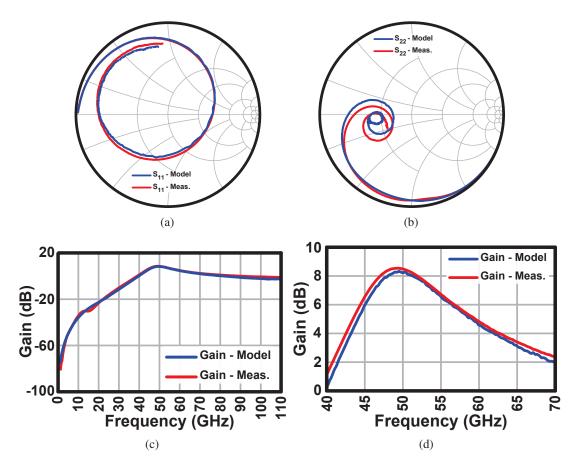

| 3.28 | S-parameter comparison results of model and measurements for V-Band           |    |

|      | one-stage amplifier. (a) Input reflection parameters comparison on Smith      |    |

|      | Chart, (b) Output reflection parameters comparison on Smith Chart, (c)        |    |

|      | Gain comparison up to 110GHz, and (d) zoomed in version of the Gain.          | 45 |

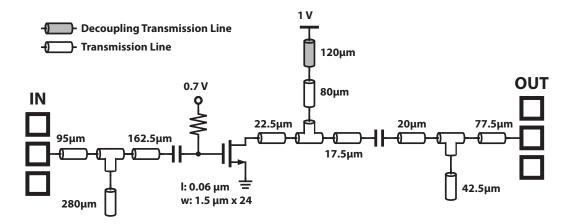

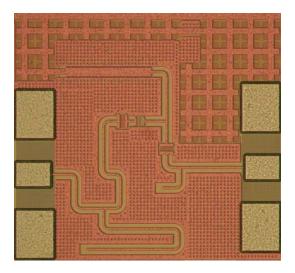

| 3.29 | Schematic of the designed W-Band Amplifier                                    | 45 |

| 3.30 | Chip photo of the designed W-Band Amplifier.                                  | 46 |

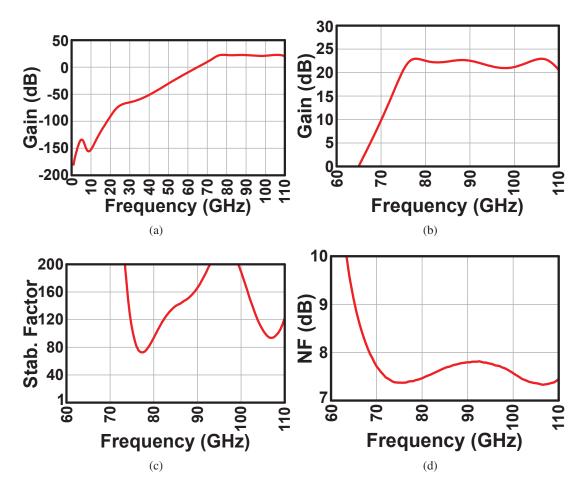

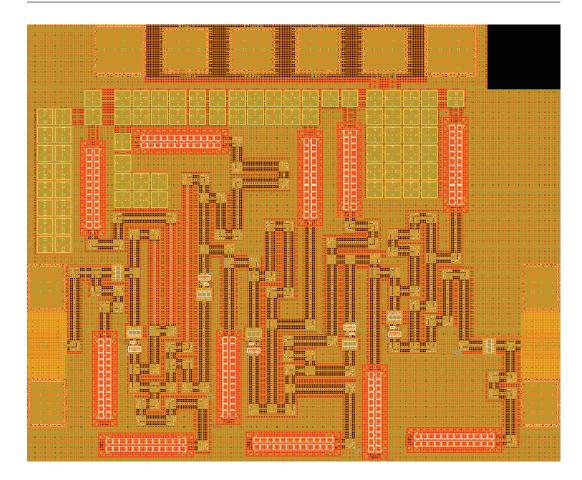

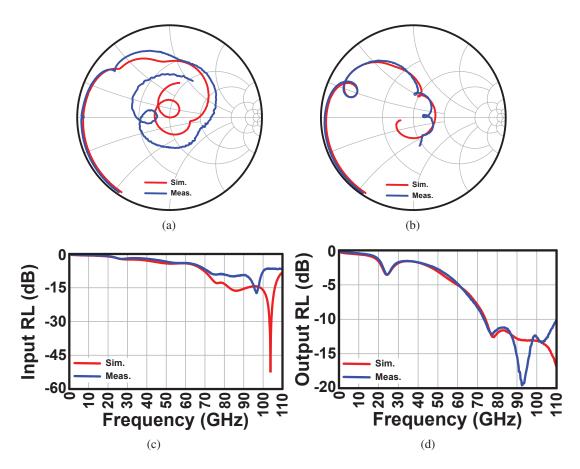

| 3.31 | S-parameter comparison results of model and measurements for W-Band           |    |

|      | one-stage amplifier. (a) Input reflection parameters comparison on Smith      |    |

|      | Chart, (b) Output reflection parameters comparison on Smith Chart, (c)        |    |

|      | Gain comparison up to 110GHz, and (d) zoomed in version of the Gain.          | 47 |

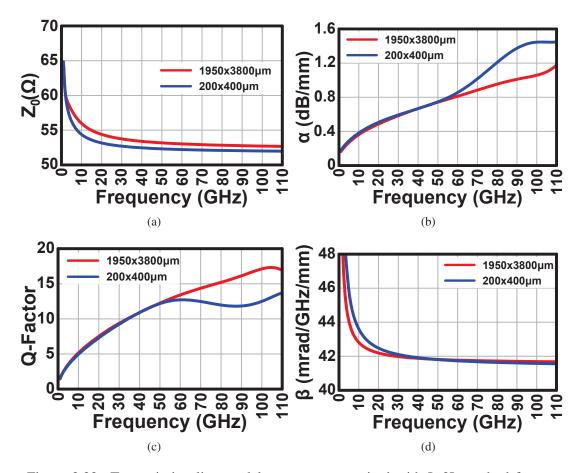

| 3.32 | Transmission line model parameters acquired with L-2L method for two          |    |

|      | cases of 200x400µm, and 1950x3800µm. (a) Transmission line                    |    |

|      | characteristic impedance magnitude, (b) loss factor, (c) quality factor,      |    |

|      | and (d) propagation constant.                                                 | 49 |

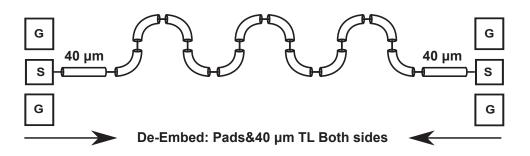

| 3.33 | Corner characterization TEG, and de-embedding of additional fixtures          | 50 |

| 3.34 | S-parameter comparison of corner between direct characterization (red         |    |

|      | lines) and conventional model (black lines) (a) return loss in magnitude      |    |

|      | (dB), (b) return loss phase (°), (c) insertion loss in magnitude (dB), and    |    |

|      | (d) insertion loss phase (°).                                                 | 51 |

| 3.35 | Tee-junction (a) geometry revisited, and (b) conventional model revisited.    | 52 |

| 3.36 | Tee-junction TEGs (a) TEG for characterization, and (b) TEG for               |    |

|      | verification.                                                                 | 52 |

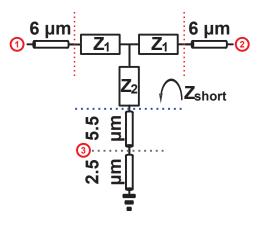

| 3.37 | Proposed tee-junction model                                                   | 53 |

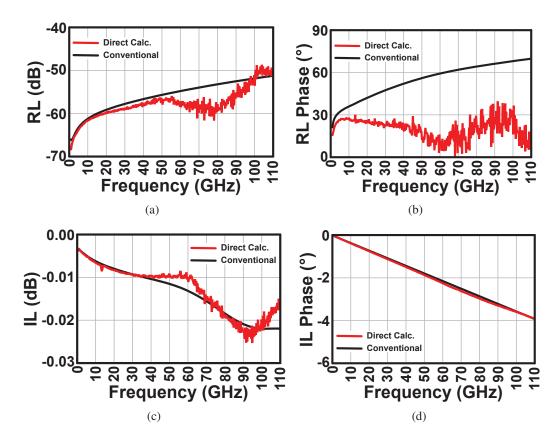

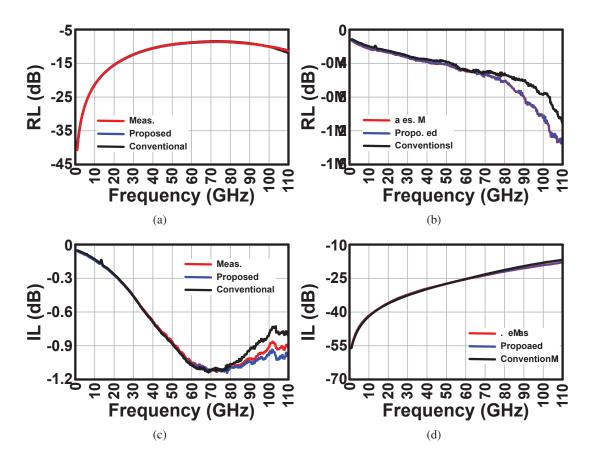

| 3.38 | S-parameters comparison results between proposed model (blue lines),          |    |

|      | conventional model (black lines), and measurement results (red lines) (a)     |    |

|      | open circuited transmission line terminated TEG return loss magnitude         |    |

|      | (dB), (b) short circuited transmission line terminated TEG return loss        |    |

|      | magnitude (dB), (c) open circuited transmission line terminated TEG           |    |

|      | insertion loss magnitude (dB), and (d) short circuited transmission line      |    |

|      | terminated TEG insertion loss magnitude (dB).                                 | 54 |

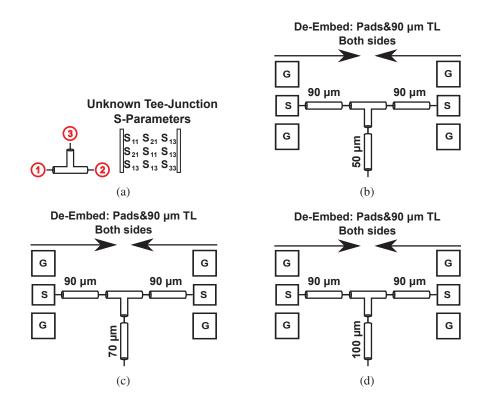

| 3.39 | Proposed full characterization method (a) tee-junction port definitions   |    |

|------|---------------------------------------------------------------------------|----|

|      | and unknown S-parameters, (b) characterization TEG with open              |    |

|      | circuited 50 µm transmission line terminated at port 3, (c)               |    |

|      | characterization TEG with open circuited 70 µm transmission line          |    |

|      | terminated at port 3, (d) characterization TEG with open circuited 100    |    |

|      | μm transmission line terminated at port 3                                 | 55 |

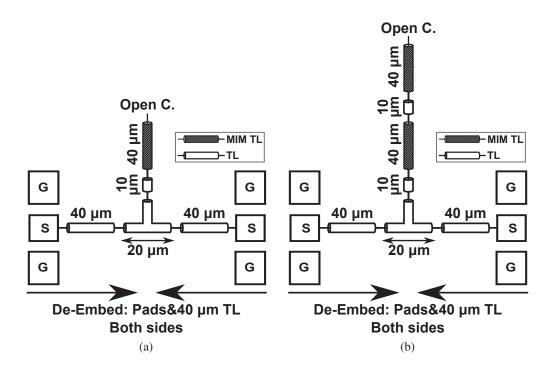

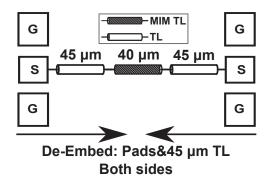

| 3.40 | MIM TL characterization TEGs and related de-embedding illustration (a)    |    |

|      | 40µm MIM TL shunt connected to third port of tee-junction, and (b) two    |    |

|      | 40µm MIM TLs shunt connected to third port of tee-junction a 10µm TL      |    |

|      | in between.                                                               | 56 |

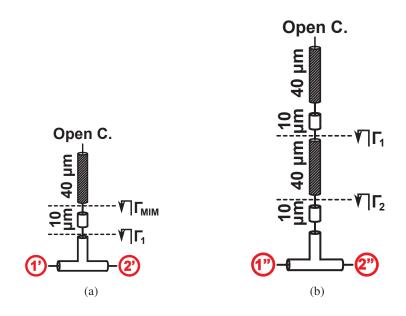

| 3.41 | Remaining structure after de-embedded of additional fixtures from TEGs    |    |

|      | (a) 40µm MIM TL shunt connected, and (b) two 40µm MIM TLs shunt           |    |

|      | connected                                                                 | 57 |

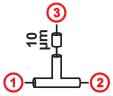

| 3.42 | Used common structure in the above presented characterization TEGs for    |    |

|      | MIM TL                                                                    | 57 |

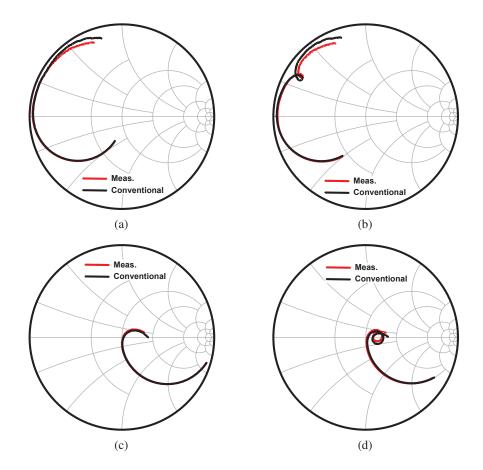

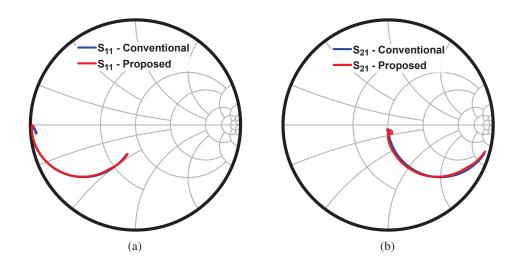

| 3.43 | Found S-parameters of MIM TL illustrated on smith charts (red lines       |    |

|      | present proposed method results and blue lines present drom direct two    |    |

|      | port measurement results from 1 to 110 GHz) (a) return loss, (b)          |    |

|      | insertion loss.                                                           | 59 |

| 3.44 | Direct series connected characterization TEG.                             | 60 |

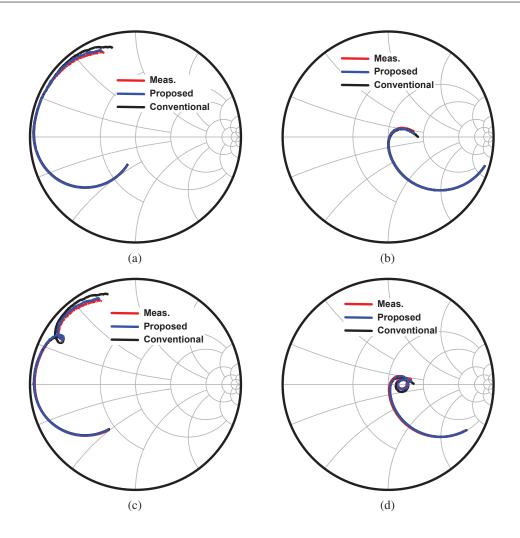

| 3.45 | Shunt characterization TEGs comparison for proposed (blue lines),         |    |

|      | conventional models (black lines), and measurement results (red lines)    |    |

|      | from 1 to 110 GHz on smith charts (a) 40µm MIM TL shunt connected         |    |

|      | TEG return losses, (b) 40µm MIM TL shunt connected TEG insertion          |    |

|      | losses, (c) two 40 $\mu$ m MIM TLs shunt connected TEG return losses, and |    |

|      | (d) two 40 $\mu$ m MIM TLs shunt connected TEG insertion losses           | 61 |

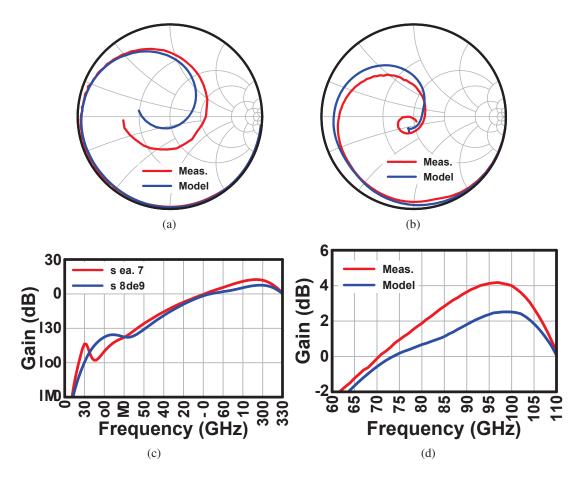

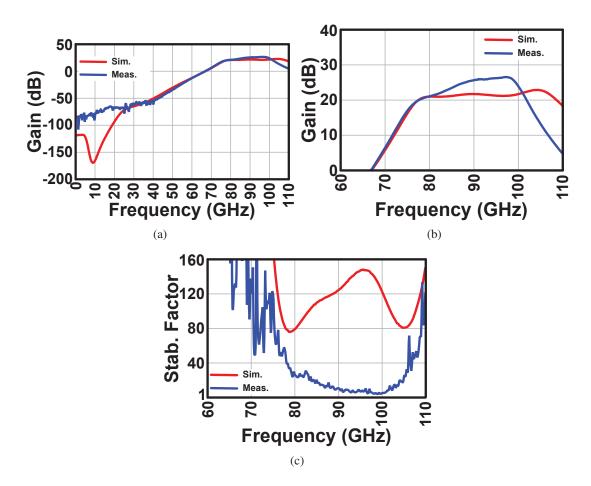

| 3.46 | S-parameter comparison results of conventional model, updated model       |    |

|      | and measurements for W-Band one-stage amplifier. (a) Input reflection     |    |

|      | parameters comparison on Smith Chart, (b) Output reflection parameters    |    |

|      | comparison on Smith Chart, (c) Gain comparison up to 110GHz, and (d)      |    |

|      | zoomed in version of the Gain.                                            | 62 |

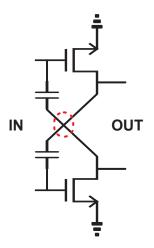

| 3.47 | An example capacitive cross coupled differential amplifier (crossing part |    |

|      | is shown with red dashed circle)                                          | 64 |

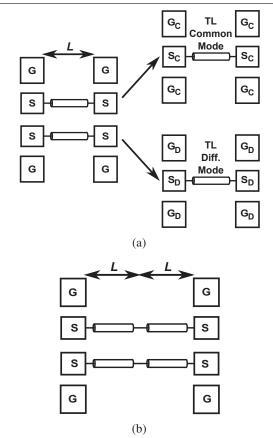

| 3.48 | Four-port TL structures used for de-embedding (a) with length "L" and     |    |

|      | illustration of common and differential mode separation, and (b) with     |    |

|      | length "2L" (Note that two TLs are connected in series for illustration   |    |

|      | purposes regarding lengths).                                              | 65 |

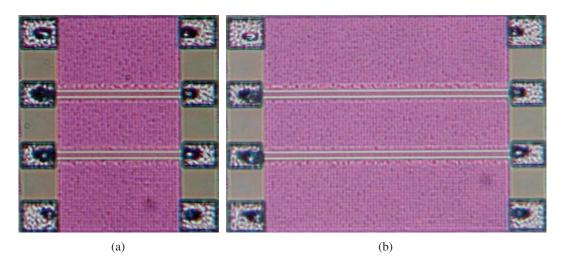

| 3.49 | Chip micrographs for four-port TL structures (a) with length "L", and (b) with length "2L".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

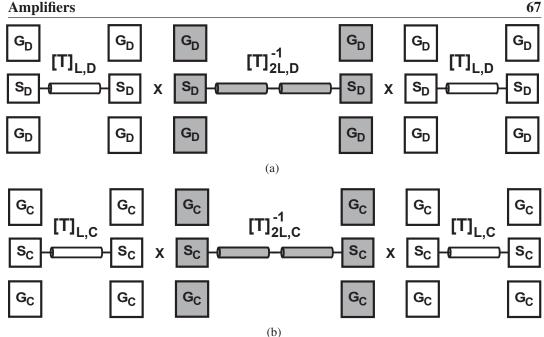

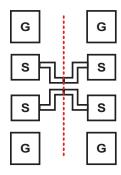

| 3.50 | Illustration of virtual-thru method application on mixed-mode S-parameters (a) application on differential mode, and (b) application on common mode (gray figures presents inverse T-parameters of the corresponding network).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 67 |

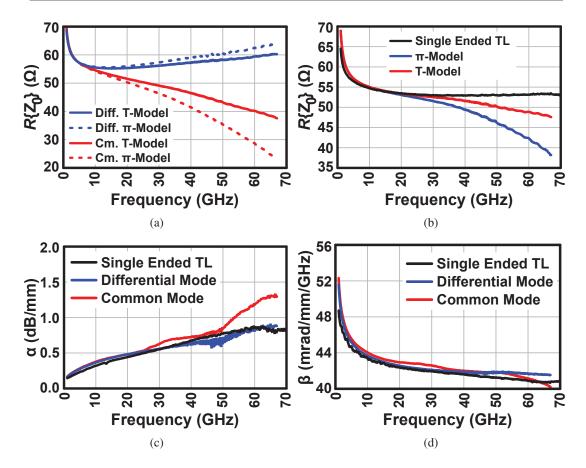

| 3.51 | Calculated TL characteristics for differential and common mode after de-<br>embedding (a) calculated characteristic impedance for differential mode<br>(blue lines) and common mode (red lines) considering Π-model for pads<br>(dashed lines) and T-model for pads (solid lines), (b) mean characteristic<br>values for both modes considering Π-model (blue line) and T-model (red<br>line) in comparison with two-port transmission line (black line), (c) loss<br>term of differential (blue line) and common mode (red line) in comparison<br>with two-port TL (black line), and (d) propagation constant of differential<br>(blue line) and common mode (red line) in comparison the two-port TL<br>(black line) | 70 |

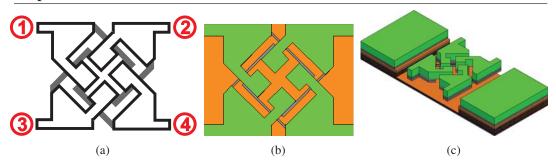

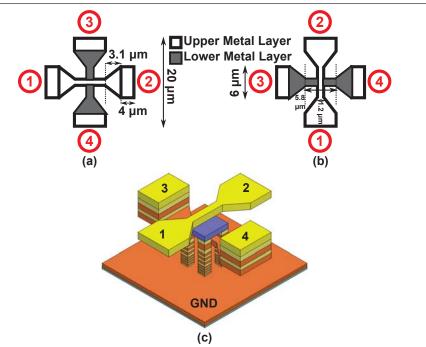

| 3.52 | Illustration of symmetrical cross line (a) with port numbering, (b) top view of cross-line (green areas are top metal layer, gray areas are for lower metal layer, and orange areas are for ground connections first two metal layers), and (c) bird-eye-view of the structure                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71 |

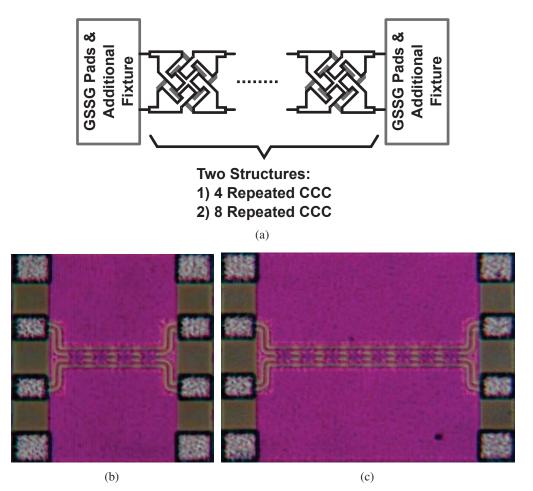

| 3.53 | Illustration of characterization structures (a) a general representation of characterization TEGs, (b) four repeated cross-line is connected in series and fixture transmission lines with probing pads are added to left and right                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

| 3.54 | sides, and (c) eight repeated cross-line characterization structure Obtained virtual-thru connection of left and right fixtures used in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71 |

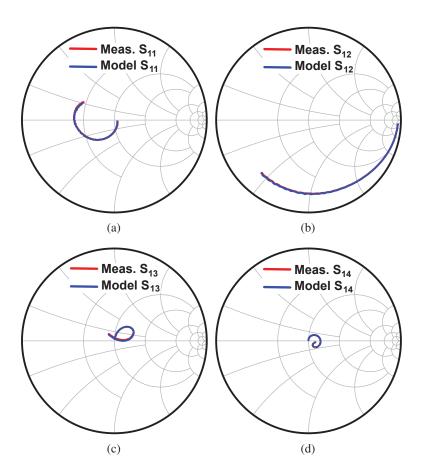

| 3.55 | characterization structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72 |

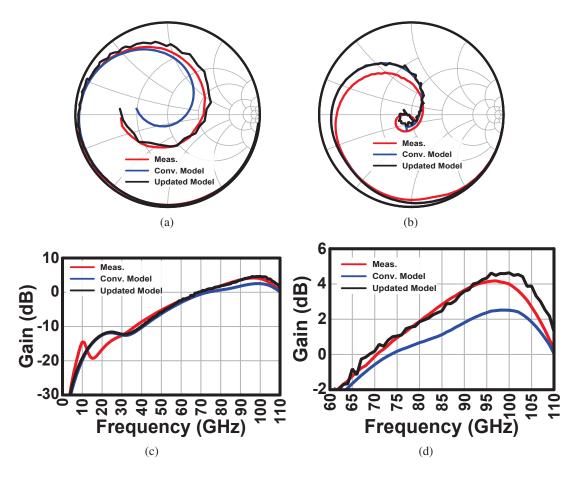

| 250  | $S_{12}$ , (c) $S_{13}$ , and (d) $S_{14}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72 |

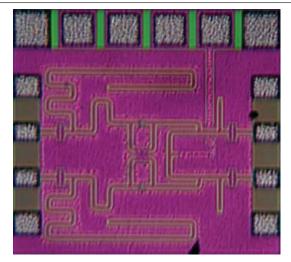

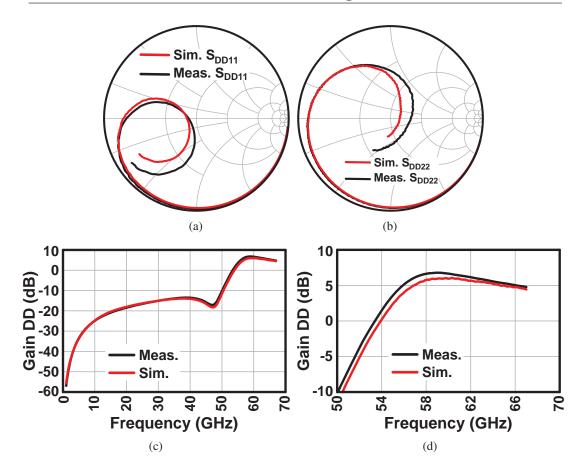

|      | A 60GHz differential amplifier chip photo in 65nm standard bulk CMOS.<br>S-parameter comparison between model simulation results (red lines) and<br>measurement (black lines) results of a 60GHz differential amplifier (a)<br>differential $S_{11}$ up to 67GHz on Smith Chart, (b) differential $S_{22}$ up to<br>67GHz on Smith Chart, (c) differential $S_{21}$ (Gain in dB) up to 67GHz,<br>and (d) Zoomed in version of gain from 50 to 67GHz in frequency axis<br>-10 to 10dB in gain axis.                                                                                                                                                                                                                     | 73 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

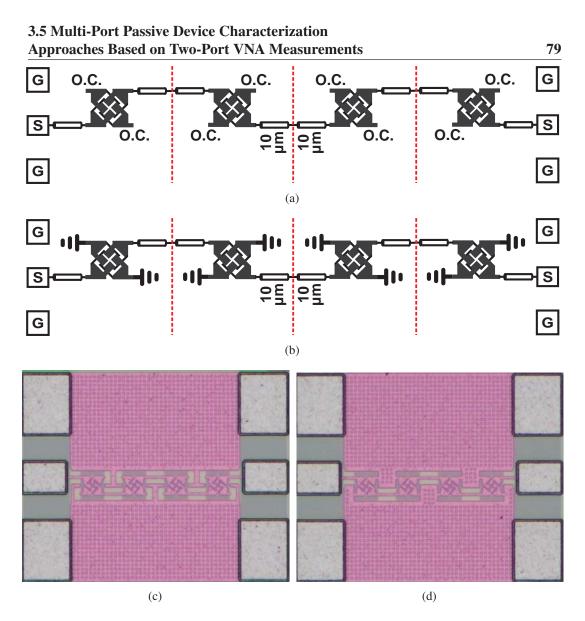

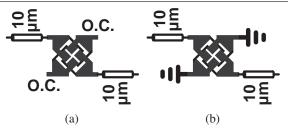

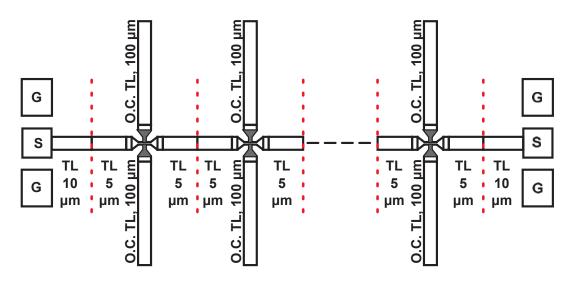

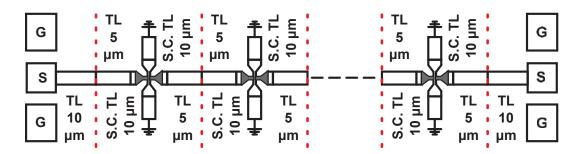

| Characterization structures for cross-line in each structure cross-line is     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| repeated four times, and either ports 2 and 3 are terminated or ports 1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| and 4 are terminated (a) characterization structure with open circuited        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (O.C.) terminations used, (b) characterization structure with short            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| circuited terminations used, (c) chip photo of (a), and (d) chip photo of (b). | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Remaining responses after de-embedding and solving for one structure (a)       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| cross-line terminated ports with open circuit, and (b) cross-line terminated   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| ports with short circuit.                                                      | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

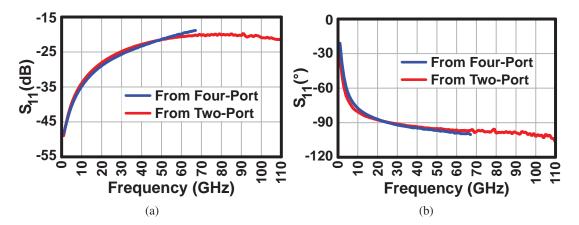

| Cross-line S-parameter comparison between calculated from four-port            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| measurements (blue lines), and from two-port measurements of the               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| proposed method (red lines), (a)magnitude of (return loss) $S_{11}$ , (b)phase |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| of <i>S</i> <sub>11</sub>                                                      | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

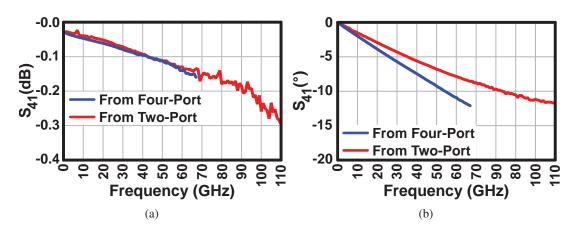

| Cross-line S-parameter comparison between calculated from four-port            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| measurements (blue lines), and from two-port measurements of the               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| proposed method (red lines), (a)magnitude of (insertion loss) $S_{41}$ ,       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (b)phase of $S_{41}$ .                                                         | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

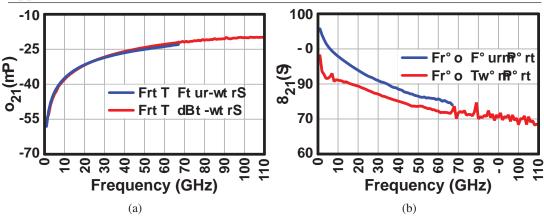

| Cross-line S-parameter comparison between calculated from four-port            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| measurements (blue lines), and from two-port measurements of the               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| proposed method (red lines), (a)magnitude of $S_{21}$ , (b)phase of $S_{21}$   | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

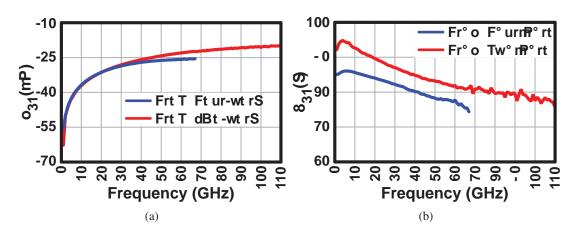

| Cross-line S-parameter comparison between calculated from four-port            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| measurements (blue lines), and from two-port measurements of the               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| proposed method (red lines), (a)magnitude of $S_{31}$ , (b)phase of $S_{31}$   | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

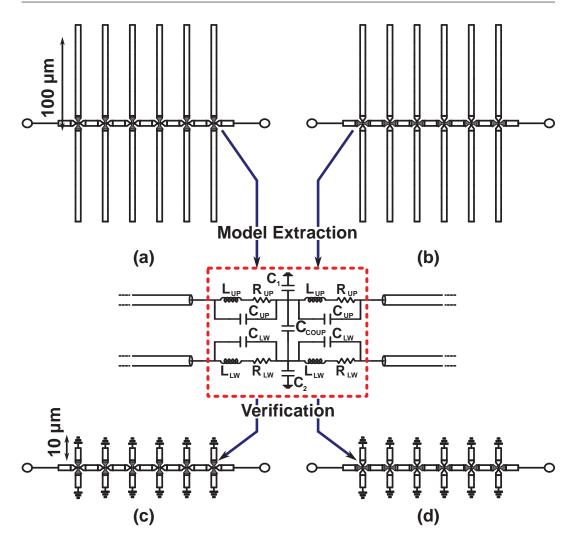

| Detailed structure of crossing TL, and orientations of (a) upper layer thru    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| connected, (b) lower layer thru connected, and (c) 3-D illustration of the     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CTL device.                                                                    | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

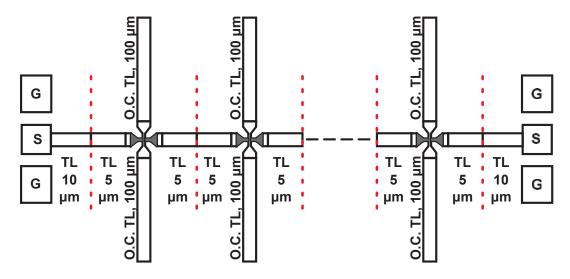

| An illustration of the manufactured TEG: six of the structures Fig. 3.69(a)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| are interconnected with 10µm length TLs. Connected to pads with 15µm           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| length TLs.                                                                    | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| An illustration of the manufactured TEG: six of the structures Fig. 3.69(b)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| are interconnected with 10µm length TLs. Connected to pads with 15µm           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| length TLs.                                                                    | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| An illustration of the manufactured TEG: six of the structures Fig. 3.69(c)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| are interconnected with 10µm length TLs. Connected to pads with 15µm           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| length TLs.                                                                    | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| An illustration of the manufactured TEG: six of the structures Fig. 3.69(d)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| are interconnected with 10µm length TLs. Connected to pads with 15µm           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| length TLs.                                                                    | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                | repeated four times, and either ports 2 and 3 are terminated or ports 1 and 4 are terminated (a) characterization structure with open circuited (O.C.) terminations used, (b) characterization structure with short circuited terminations used, (c) chip photo of (a), and (d) chip photo of (b). Remaining responses after de-embedding and solving for one structure (a) cross-line terminated ports with open circuit, and (b) cross-line terminated ports with short circuit |

XV

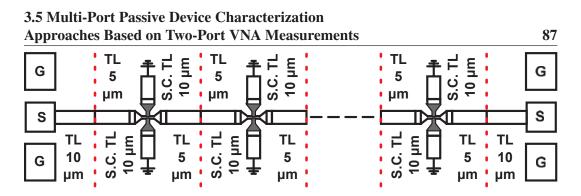

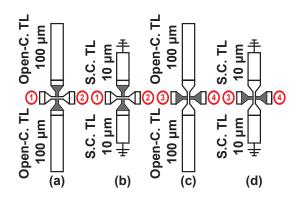

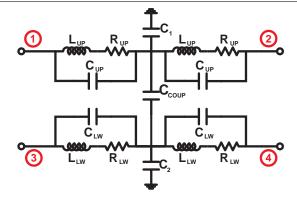

| 3.69 | Illustrations of terminated CTLs. (a) Orientation Fig. 3.64(a) is                            |            |

|------|----------------------------------------------------------------------------------------------|------------|

|      | connected through, ports 3 and 4 are terminated with open-circuited TLs,                     |            |

|      | (b) orientation Fig. 3.64(a) is connected through, ports 3 and 4 are                         |            |

|      | terminated with short-circuited TLs, (c) orientation Fig. 3.64(b) is                         |            |

|      | connected through, ports 1 and 2 are terminated with open-circuited TLs,                     |            |

|      | (d) orientation Fig. 3.64(b) is connected through, ports 1 and 2 are                         |            |

|      | terminated with short-circuited TLs.                                                         | 88         |

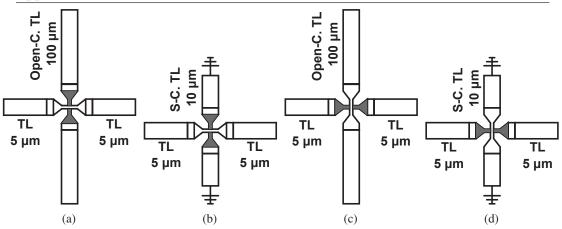

| 3.70 | An illustration of the symmetrical and reciprocal networks including                         |            |

|      | CTLs (a)-(d), constructed as Fig. 3.69(a)-(d) connected with TLs on the                      |            |

|      | left and right sides.                                                                        | 89         |

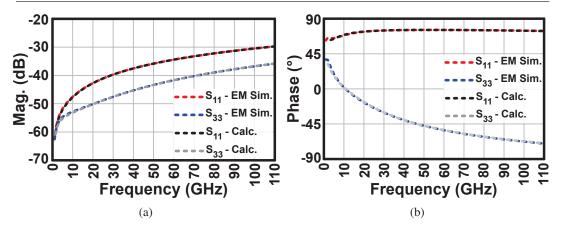

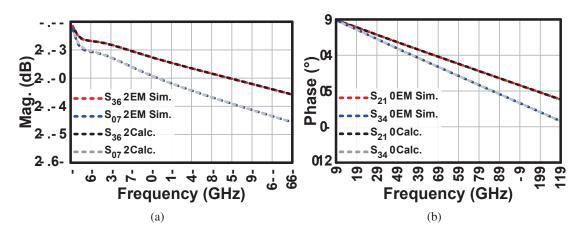

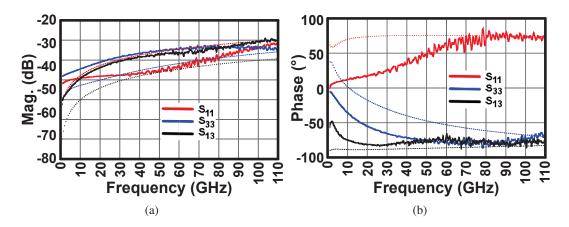

| 3.71 | EM simulated and calculated using the method S-parameters of CTL : (a)                       |            |

| 0.71 | magnitude (dB) $S_{11}$ , and $S_{33}$ , (b) phase (degree) $S_{11}$ (red and blue lines     |            |

|      | represents the EM simulation results, and black and gray lines represents                    |            |

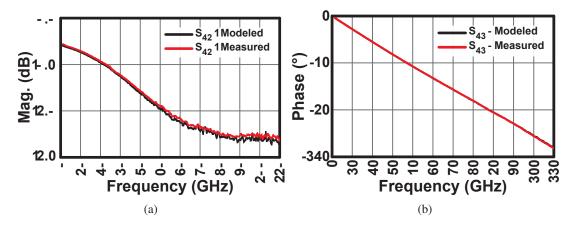

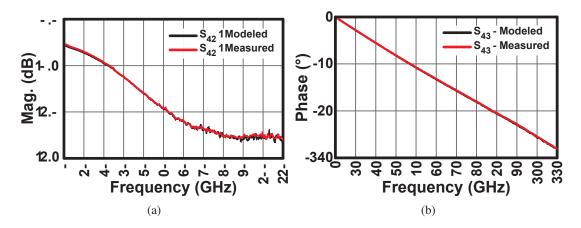

|      | the calculated results using the proposed method)                                            | 93         |

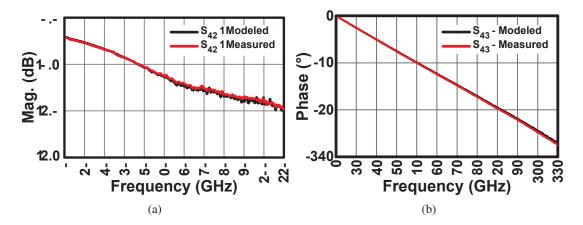

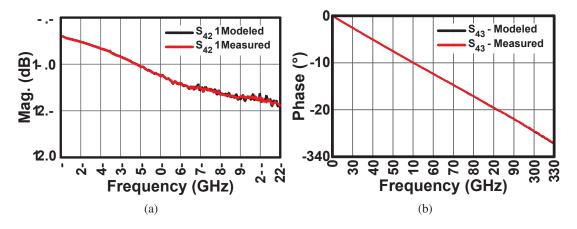

| 3 72 | EM simulated and calculated using the method S-parameters of CTL :(a)                        | 10         |

| 5.72 | magnitude (dB) $S_{21}$ , and $S_{43}$ , (b) phase (degree) $S_{21}$ , and $S_{43}$ (red and |            |

|      | blue lines represents the EM simulation results, and black and gray lines                    |            |

|      | represents the calculated results using the proposed method)                                 | 94         |

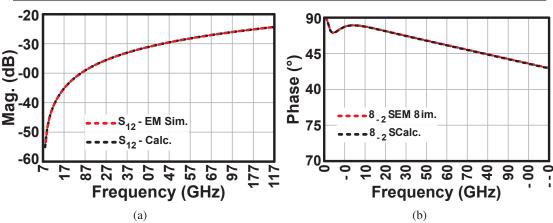

| 3 73 | EM simulated and calculated using the method S-parameters of CTL :(a)                        | 1          |

| 5.15 | magnitude (dB) $S_{13}$ , and (b) phase (degree) $S_{13}$ (red and blue lines                |            |

|      | represents the EM simulation results, and black and gray lines represents                    |            |

|      | the calculated results using the proposed method)                                            | 95         |

| 3 74 | S-Parameter comparison between monolithically EM simulated six-stage                         | ))         |

| 5.74 | of Fig. 3.70(a)(red lines) and three times cascaded of EM simulated                          |            |

|      | two-stage of Fig. $3.71(a)$ (black lines):(a)magnitude (dB) $S_{11}$ , (b)phase              |            |

|      | (degree) $S_{11}$                                                                            | 96         |

| 3 75 | S-Parameter comparison between monolithically EM simulated six-stage                         | 70         |

| 5.15 | of Fig. 3.70(a)(red lines) and three times cascaded of EM simulated two-                     |            |

|      | stage of Fig. $3.71(a)$ (black lines):(a)magnitude (dB) $S_{21}$ , and (b)phase              |            |

|      | (degree) $S_{21}$                                                                            | 97         |

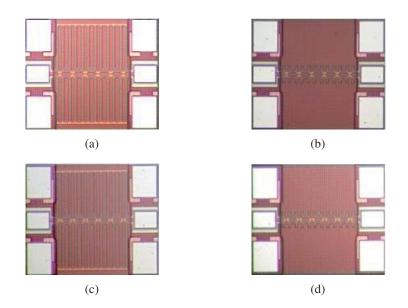

| 3 76 | Chip micrograph (a)-(d), respectively for Fig. 3.65-3.68.                                    | 98         |

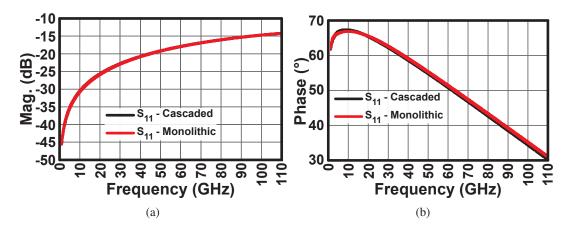

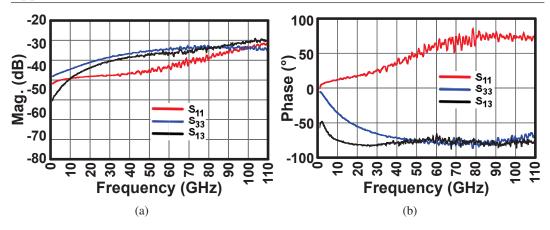

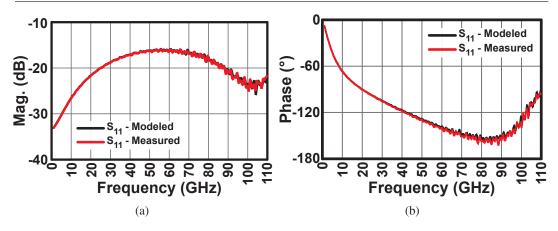

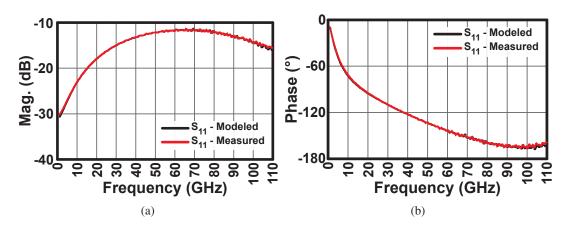

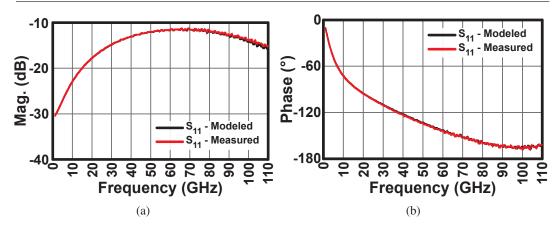

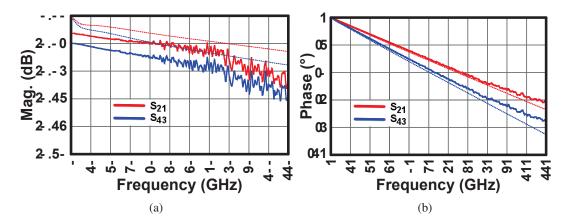

|      | Characterized S-parameters of CTL: (a)magnitude (dB) $S_{11}$ , $S_{13}$ , and $S_{33}$ ,    | 70         |

| 5.11 | (b)phase (degree) $S_{11}$ , $S_{13}$ , and $S_{33}$                                         | 99         |

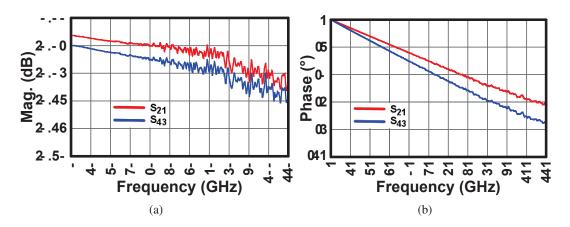

| 3 78 | Characterized S-parameters of CTL:(a)magnitude (dB) $S_{21}$ , and $S_{43}$ ,                | "          |

| 5.70 | (b)phase (degree) $S_{21}$ , and $S_{43}$ .                                                  | 99         |

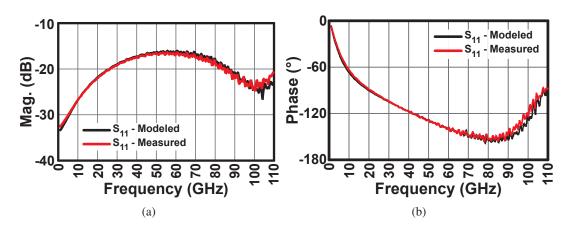

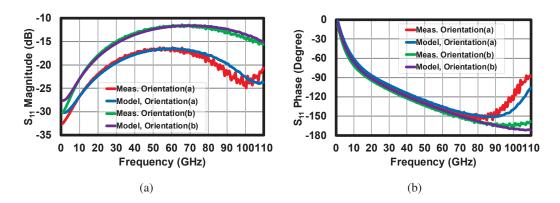

| 3 70 | Comparison between measurements and characterized of Fig. $3.65$ :                           | <u>I</u> I |

| 5.19 |                                                                                              | 100        |

|      | (a)magnitude of $S_{11}$ in dB, (b)phase of $S_{11}$ in degrees                              | 100        |

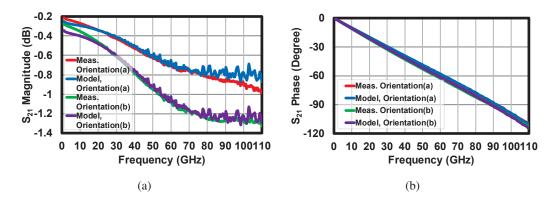

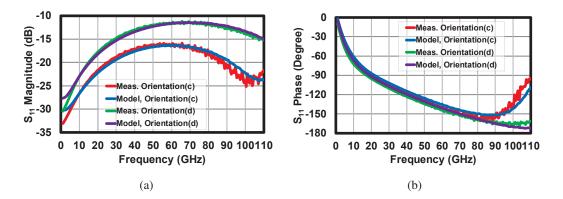

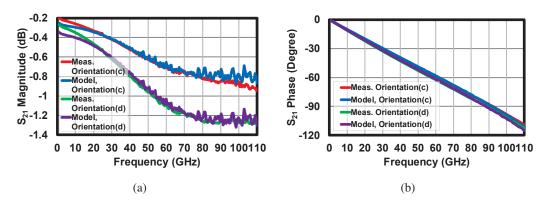

| 3.80         | Comparison between measurements and characterized of Fig. 3.65:(a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | magnitude of $S_{21}$ in dB, and (b) phase $S_{21}$ in degrees                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

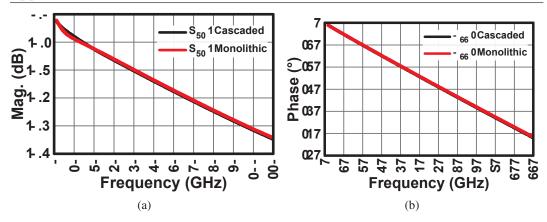

| 3.81         | Comparison between measurements and characterized of Fig.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | 3.66:(a)magnitude of $S_{11}$ in dB, (b)phase of $S_{11}$ in degrees 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.82         | Comparison between measurements and characterized of Fig.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | 3.66:(a)magnitude of $S_{21}$ in dB, (b)phase $S_{21}$ in degrees 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.83         | Comparison between measurements and characterized of Fig.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | 3.67:(a)magnitude of $S_{11}$ in dB, (b)phase of $S_{11}$ in degrees 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.84         | Comparison between measurements and characterized of Fig.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | 3.67:(a)magnitude of $S_{21}$ in dB, (b)phase $S_{21}$ in degrees                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.85         | Comparison between measurements and characterized of Fig.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              | 3.68:(a)magnitude of $S_{11}$ in dB, (b)phase of $S_{11}$ in degrees 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.86         | Comparison between measurements and characterized of Fig.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

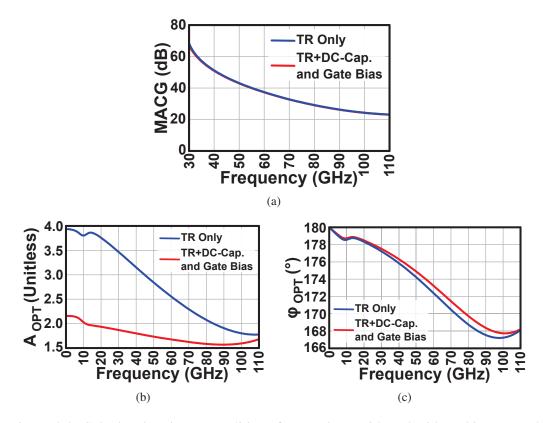

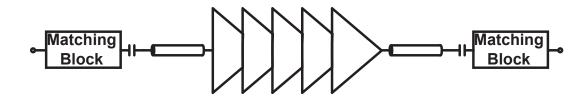

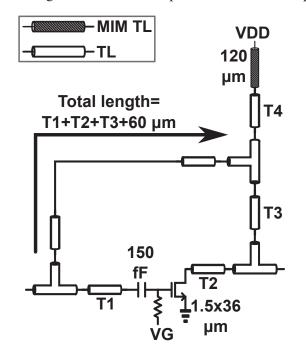

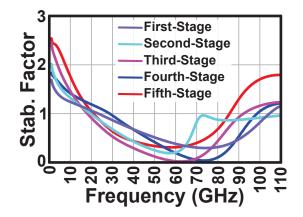

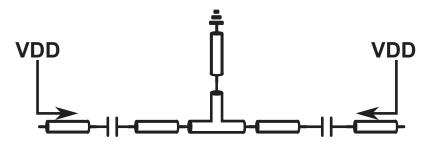

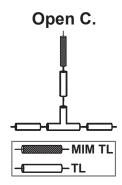

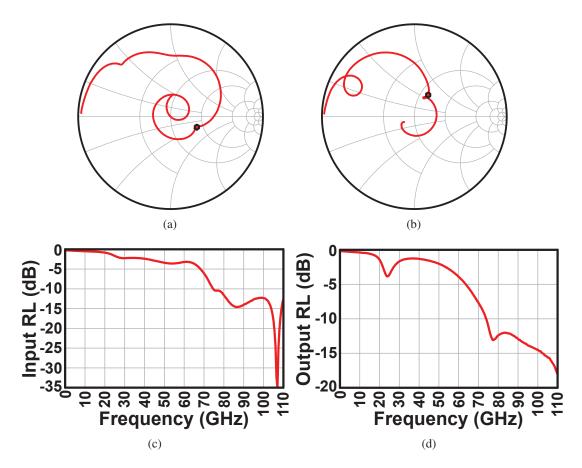

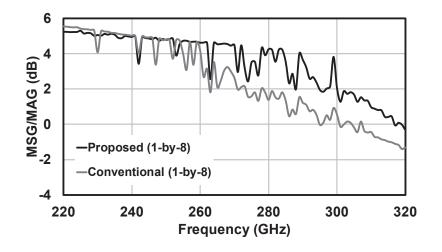

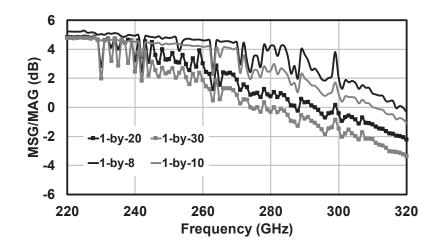

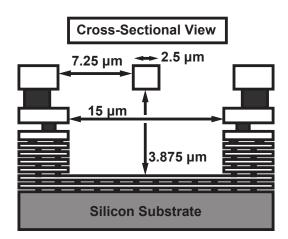

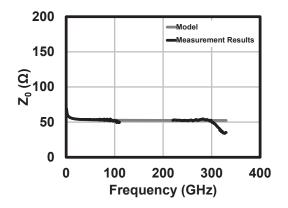

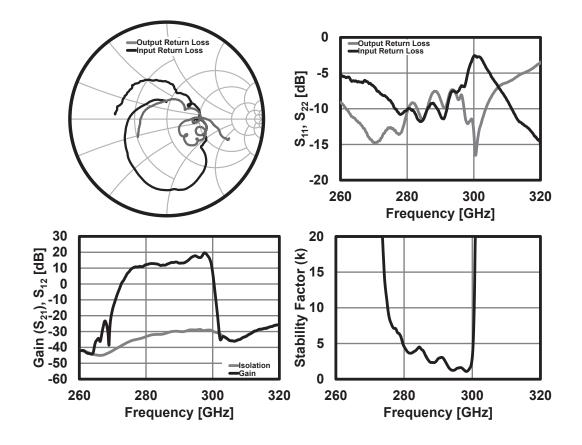

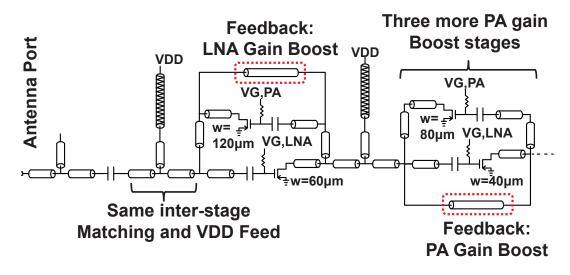

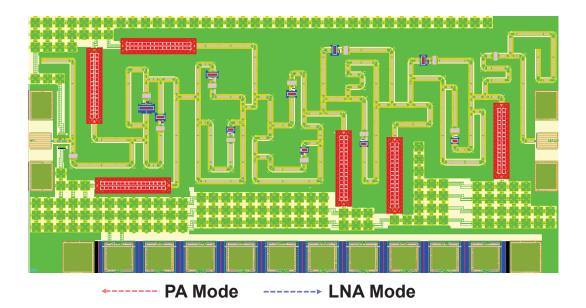

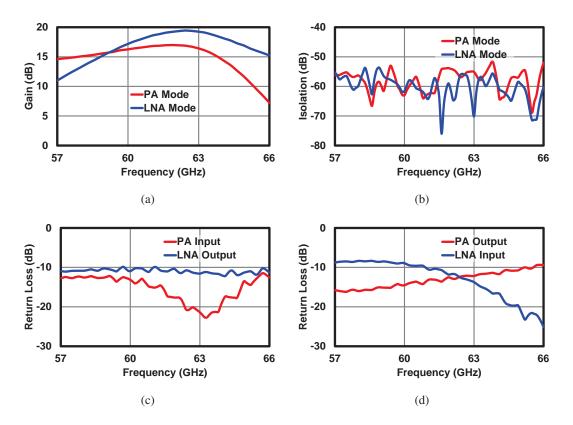

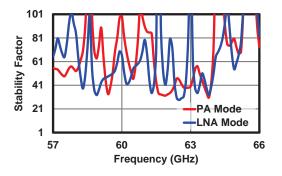

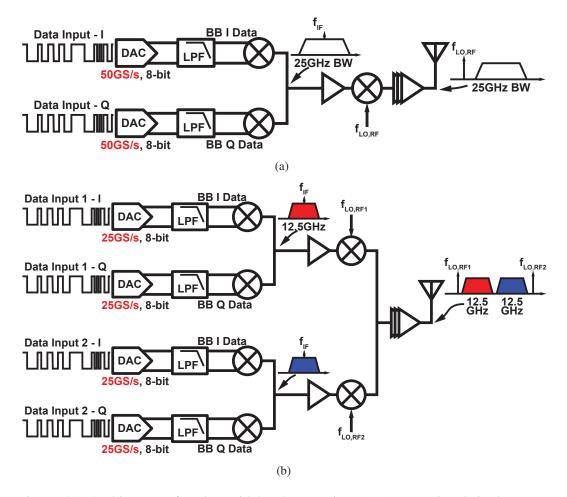

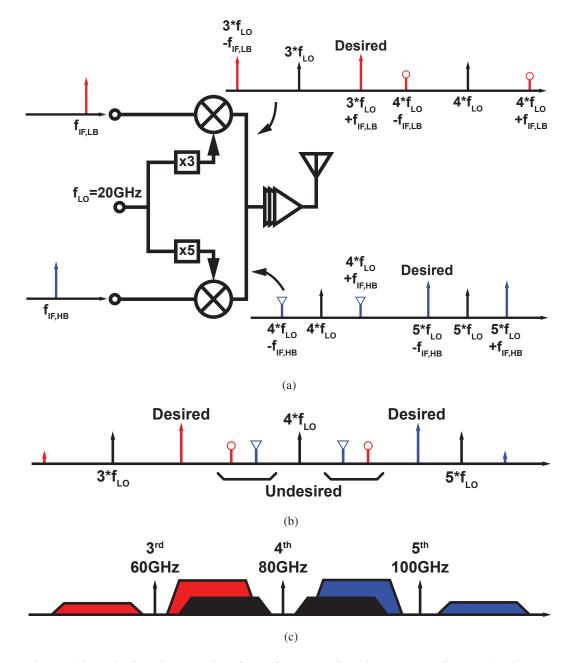

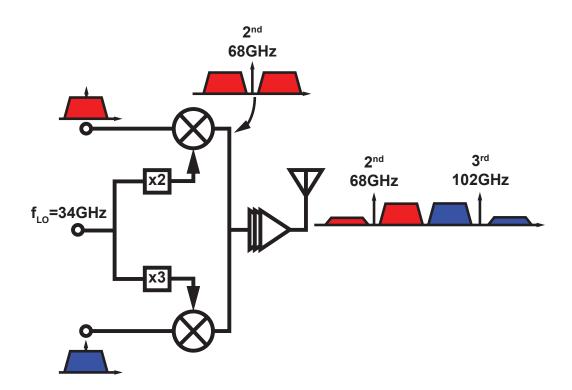

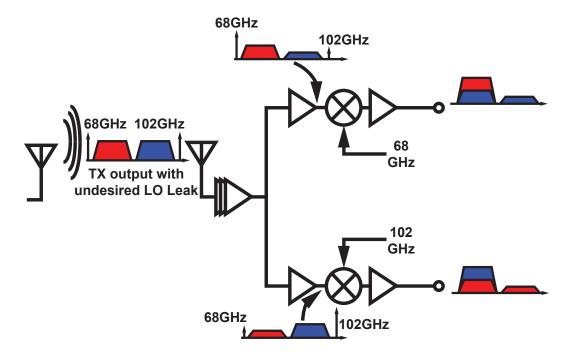

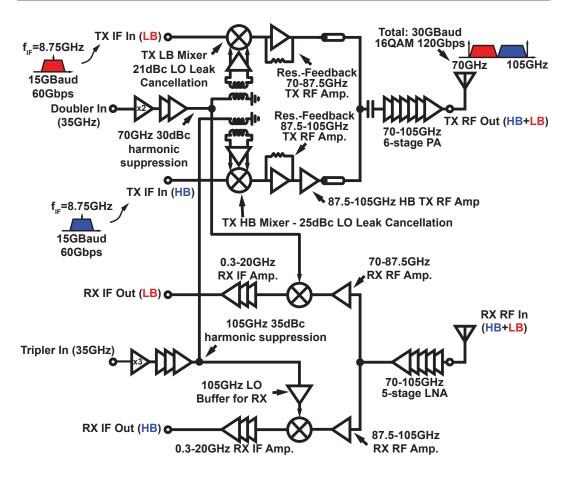

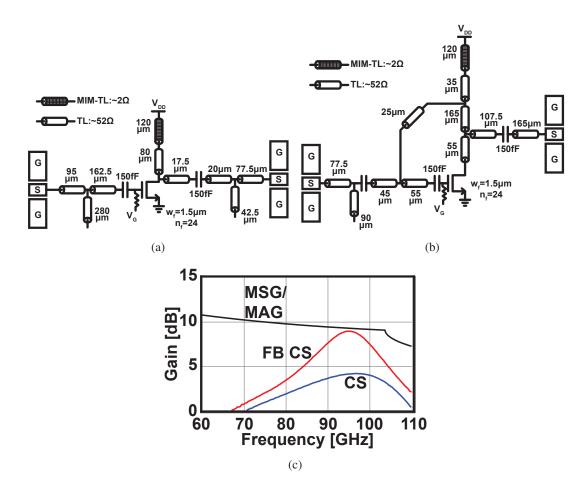

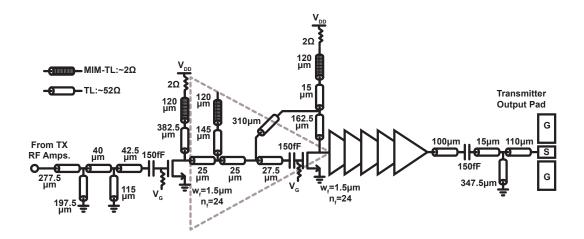

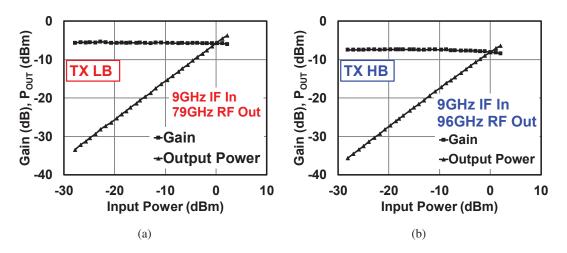

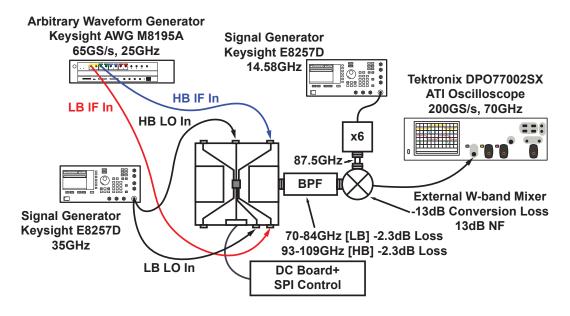

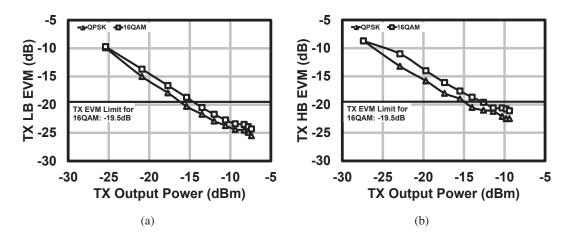

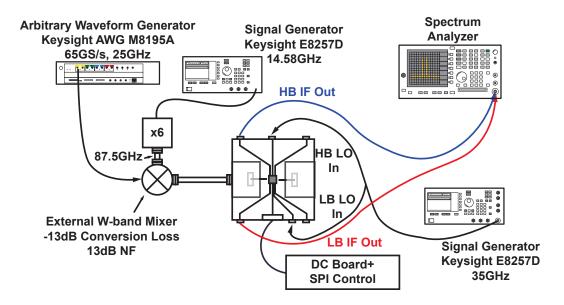

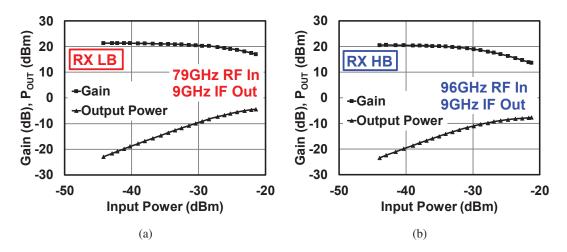

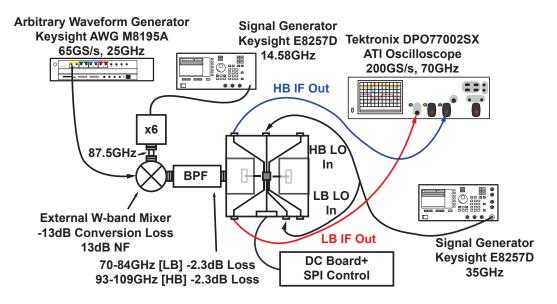

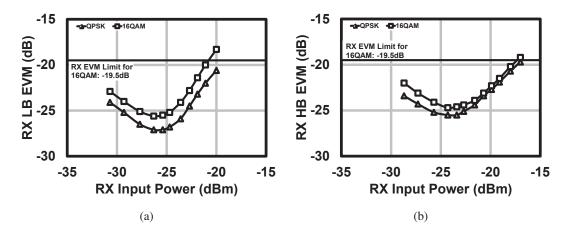

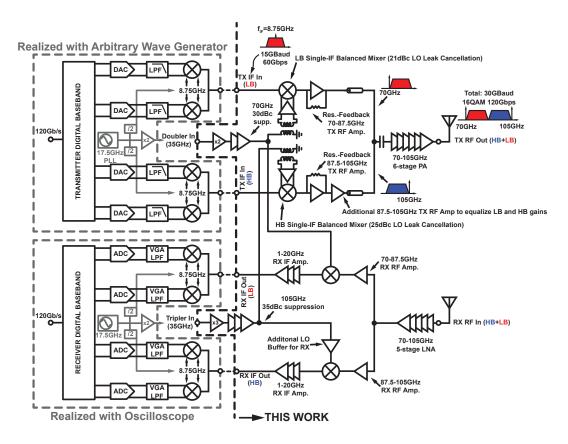

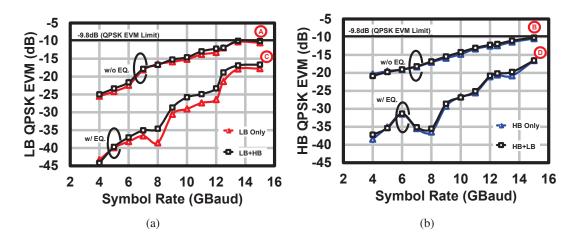

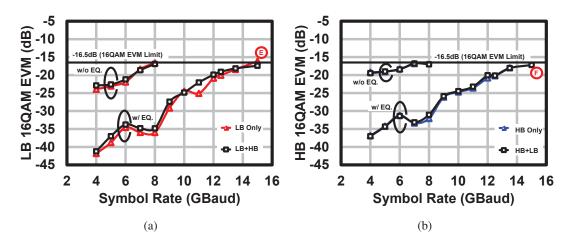

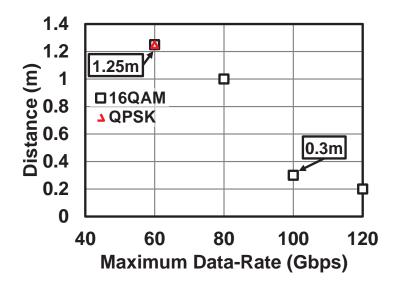

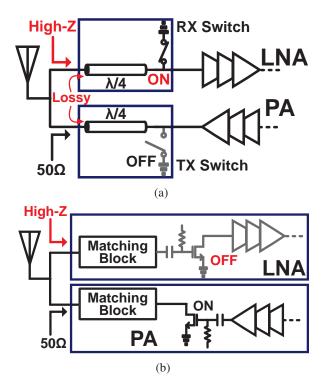

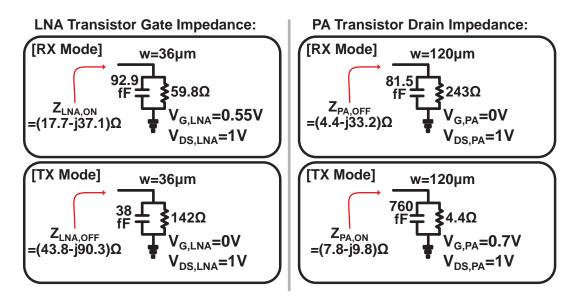

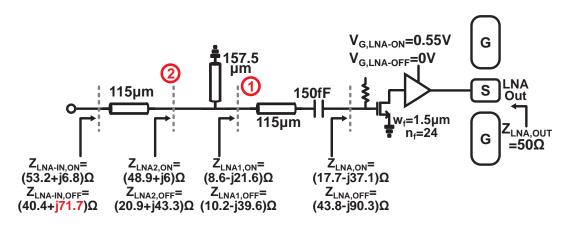

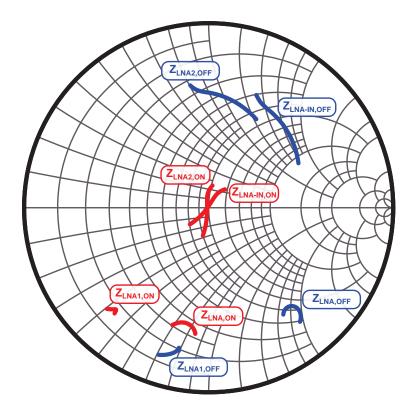

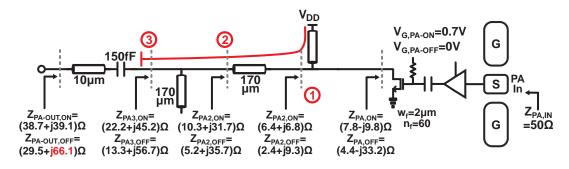

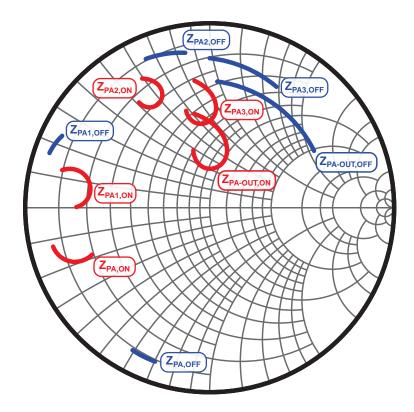

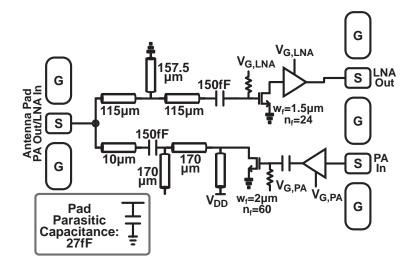

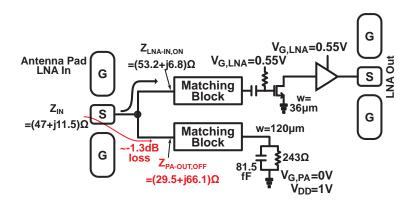

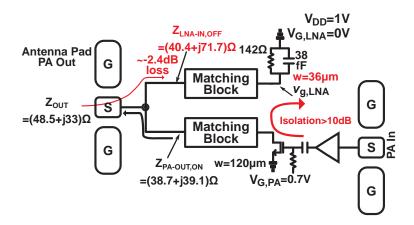

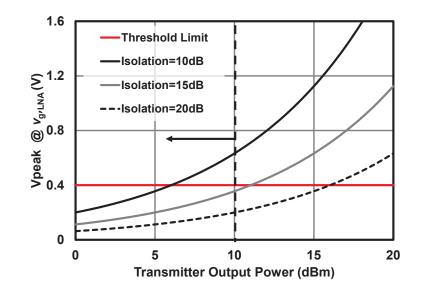

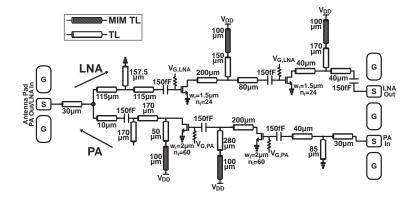

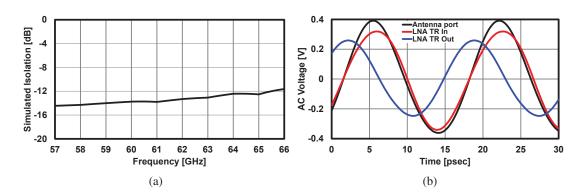

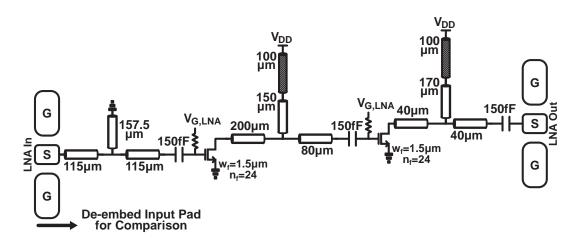

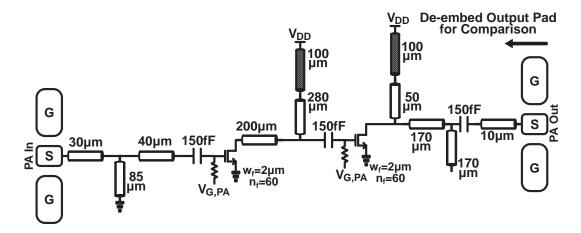

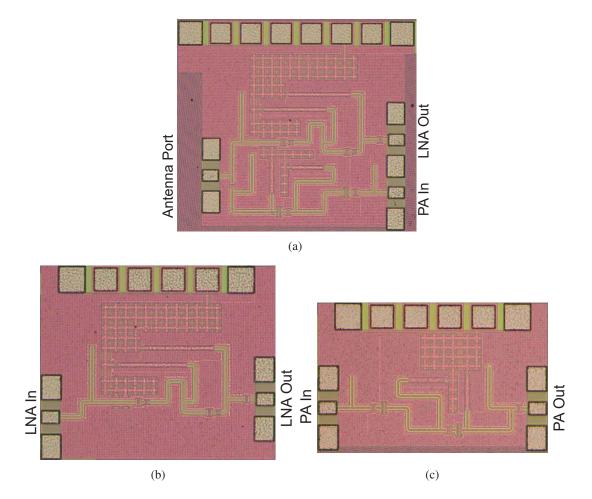

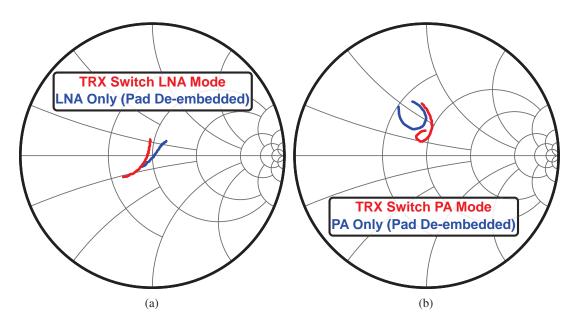

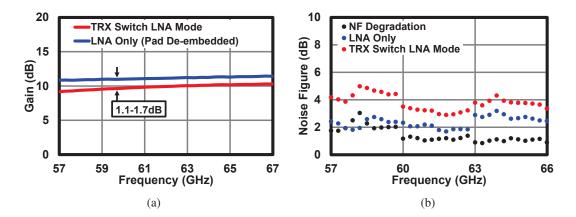

|              | 3.68:(a)magnitude of $S_{21}$ in dB, (b)phase $S_{21}$ in degrees 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |